Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4704                                                        |

| Number of Logic Elements/Cells | 21168                                                       |

| Total RAM Bits                 | 1146880                                                     |

| Number of I/O                  | 556                                                         |

| Number of Gates                | 254016                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 900-BBGA                                                    |

| Supplier Device Package        | 900-FBGA (31x31)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv812e-7fg900c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 2: Performance for Common Circuit Functions

| Function              | Bits    | Virtex-E -7 |

|-----------------------|---------|-------------|

| Register-to-Register  |         |             |

| Adder                 | 16      | 4.3 ns      |

| Addel                 | 64      | 6.3 ns      |

| Pipelined Multiplier  | 8 x 8   | 4.4 ns      |

| r ipelined Muniplier  | 16 x 16 | 5.1 ns      |

| Address Decoder       | 16      | 3.8 ns      |

| Address Decoder       | 64      | 5.5 ns      |

| 16:1 Multiplexer      |         | 4.6 ns      |

|                       | 9       | 3.5 ns      |

| Parity Tree           | 18      | 4.3 ns      |

|                       | 36      | 5.9 ns      |

| Chip-to-Chip          |         |             |

| HSTL Class IV         |         |             |

| LVTTL,16mA, fast slew |         |             |

| LVDS                  |         |             |

| LVPECL                |         |             |

## Virtex-E Extended Memory Device/Package Combinations and Maximum I/O

Table 3: Virtex-EM Family Maximum User I/O by Device/Package (Excluding Dedicated Clock Pins)

| Package | XCV405E | XCV812E |

|---------|---------|---------|

| BG560   | 404     | 404     |

| FG676   | 404     |         |

| FG900   |         | 556     |

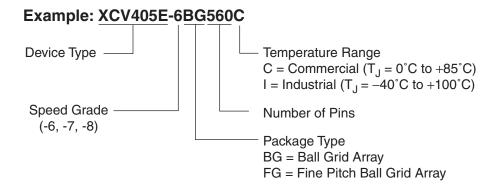

## **Virtex-E Extended Memory Ordering Information**

DS025\_001\_112000

Figure 1: Virtex Ordering Information

IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

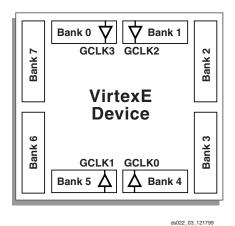

Eight I/O banks result from separating each edge of the FPGA into two banks, as shown in Figure 3. Each bank has multiple  $V_{CCO}$  pins, all of which must be connected to the same voltage. This voltage is determined by the output standards in use.

Figure 3: Virtex-E I/O Banks

Within a bank, output standards can be mixed only if they use the same  $V_{CCO}$ . Compatible standards are shown in Table 2. GTL and GTL+ appear under all voltages because their open-drain outputs do not depend on  $V_{CCO}$ .

Table 2: Compatible Output Standards

| V <sub>cco</sub> | Compatible Standards                                       |

|------------------|------------------------------------------------------------|

| 3.3 V            | PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL+, LVPECL |

| 2.5 V            | SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+,<br>BLVDS, LVDS      |

| 1.8 V            | LVCMOS18, GTL, GTL+                                        |

| 1.5 V            | HSTL I, HSTL III, HSTL IV, GTL, GTL+                       |

Some input standards require a user-supplied threshold voltage,  $V_{REF}$  In this case, certain user-I/O pins are automatically configured as inputs for the  $V_{REF}$  voltage. Approximately one in six of the I/O pins in the bank assume this role.

The  $V_{REF}$  pins within a bank are interconnected internally and consequently only one  $V_{REF}$  voltage can be used within each bank. All  $V_{REF}$  pins in the bank, however, must be connected to the external voltage source for correct operation.

Within a bank, inputs that require  $V_{REF}$  can be mixed with those that do not. However, only one  $V_{REF}$  voltage can be used within a bank.

In Virtex-E, input buffers with LVTTL, LVCMOS2, LVCMOS18, PCI33\_3, PCI66\_3 standards are supplied by  $V_{\rm CCO}$  rather than  $V_{\rm CCINT}$ . For these standards, only input and output buffers that have the same  $V_{\rm CCO}$  can be mixed together.

The  $V_{CCO}$  and  $V_{REF}$  pins for each bank appear in the device pin-out tables and diagrams. The diagrams also show the bank affiliation of each I/O.

Within a given package, the number of  $V_{REF}$  and  $V_{CCO}$  pins can vary depending on the size of device. In larger devices, more I/O pins convert to  $V_{REF}$  pins. Since these are always a super set of the  $V_{REF}$  pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device if necessary. All the  $V_{REF}$  pins for the largest device anticipated must be connected to the  $V_{REF}$  voltage, and not used for I/O.

In smaller devices, some  $V_{CCO}$  pins used in larger devices do not connect within the package. These unconnected pins can be left unconnected externally, or they can be connected to the  $V_{CCO}$  voltage to permit migration to a larger device, if necessary.

## **Configurable Logic Block**

The basic building block of the Virtex-E CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and a storage element. The output from the function generator in each LC drives both the CLB output and the D input of the flip-flop. Each Virtex-E CLB contains four LCs, organized in two similar slices, as shown in Figure 4. Figure 5 shows a more detailed view of a single slice.

bined to create a 16 x 2-bit or 32 x 1-bit synchronous RAM, or a 16 x 1-bit dual-port synchronous RAM.

The Virtex-E LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data in applications such as Digital Signal Processing.

## Storage Elements

The storage elements in the Virtex-E slice can be configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The D inputs can be driven either by the function generators within the slice or directly from slice inputs, bypassing the function generators.

In addition to Clock and Clock Enable signals, each Slice has synchronous set and reset signals (SR and BY). SR forces a storage element into the initialization state specified for it in the configuration. BY forces it into the opposite state. Alternatively, these signals can be configured to operate asynchronously. All of the control signals are independently invertible, and are shared by the two flip-flops within the slice.

## Additional Logic

The F5 multiplexer in each slice combines the function generator outputs. This combination provides either a function generator that can implement any 5-input function, a 4:1 multiplexer, or selected functions of up to nine inputs.

Similarly, the F6 multiplexer combines the outputs of all four function generators in the CLB by selecting one of the F5-multiplexer outputs. This permits the implementation of any 6-input function, an 8:1 multiplexer, or selected functions of up to 19 inputs.

Each CLB has four direct feedthrough paths, two per slice. These paths provide extra data input lines or additional local routing that does not consume logic resources.

#### Arithmetic Logic

Dedicated carry logic provides fast arithmetic carry capability for high-speed arithmetic functions. The Virtex-E CLB supports two separate carry chains, one per Slice. The height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a 2-bit full adder to be implemented within a slice. In addition, a dedicated AND gate improves the efficiency of multiplier implementation.

The dedicated carry path can also be used to cascade function generators for implementing wide logic functions.

#### **BUFTs**

Each Virtex-E CLB contains two 3-state drivers (BUFTs) that can drive on-chip busses. See "Dedicated Routing" on page 7. Each Virtex-E BUFT has an independent 3-state control pin and an independent input pin.

#### Block SelectRAM+ Memory

Virtex-E FPGAs incorporate large block SelectRAM memories. These complement the Distributed SelectRAM memories that provide shallow RAM structures implemented in CLBs.

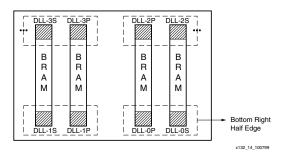

Block SelectRAM memory blocks are organized in columns, starting at the left (column 0) and right outside edges and inserted every four CLB columns (see notes for smaller devices). Each memory block is four CLBs high, and each memory column extends the full height of the chip, immediately adjacent (to the right, except for column 0) of the CLB column locations indicated in Table 3.

Table 3: CLB/Block RAM Column Locations

| Virtex-E Device | 0 | 4 | 8 | 12 | 16 | 20 | 24 | 28 | 32 | 36 | 40 | 44 | 48 | 52 | 56 | 60 | 64 | 68 | 72 | 76 | 80 | 84 |

|-----------------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| XCV405E         | V | 1 | V | √  | √  | √  | 1  |    |    | √  | √  | 1  | √  | √  | √  | √  |    |    |    |    |    |    |

| XCV812E         | 1 | 1 | 1 | √  | √  | √  | √  | √  | √  | √  |    |    | √  | √  | √  | √  | √  | √  | √  | √  | √  | √  |

Table 4 shows the amount of block SelectRAM memory that is available in each Virtex-E device.

Table 4: Virtex-E Block SelectRAM Amounts

| Virtex-E Device | # of Blocks | Block SelectRAM Bits |  |  |  |  |

|-----------------|-------------|----------------------|--|--|--|--|

| XCV405E         | 140         | 573,440              |  |  |  |  |

| XCV812E         | 280         | 1,146,880            |  |  |  |  |

Each block SelectRAM cell, as illustrated in Figure 6, is a fully synchronous dual-ported (True Dual Port) 4096-bit RAM with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

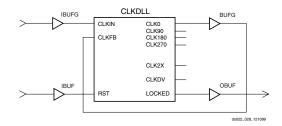

Figure 26: Virtex Series DLLs

## **Design Factors**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

#### Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

#### Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL produces an unreliable lock signal and output clock.

It is possible to stop the input clock with little impact to the DLL. Stopping the clock should be limited to less than 100  $\mu s$  to keep device cooling to a minimum. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED stays High and remains High when the clock is restored.

When the clock is stopped, one to four more clocks are still observed as the delay line is flushed. When the clock is restarted, the output clocks are not observed for one to four clocks as the delay line is filled. The most common case is two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift propagates one to four clocks to the output after the original shift, with no disruption to the CLKDLL control.

#### **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or they can route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). In addition, the CLK2X output of the secondary DLL can connect directly to the CLKIN of the primary DLL in the same quadrant.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

## **Useful Application Examples**

The Virtex-E DLL can be used in a variety of creative and useful applications. The following examples show some of the more common applications. The Verilog and VHDL example files are available at:

ftp://ftp.xilinx.com/pub/applications/xapp/xapp132.zip

## Standard Usage

The circuit shown in Figure 27 resembles the BUFGDLL macro implemented to provide access to the RST and LOCKED pins of the CLKDLL.

Figure 27: Standard DLL Implementation

## Board Level De-Skew of Multiple Non-Virtex-E Devices

The circuit shown in Figure 28 can be used to de-skew a system clock between a Virtex-E chip and other non-Virtex-E chips on the same board. This application is commonly used when the Virtex-E device is used in conjunction with other standard products such as SRAM or DRAM devices. While designing the board level route, ensure that the return net delay to the source equals the delay to the other chips involved.

#### **Conflict Resolution**

The block SelectRAM+ memory is a true dual-read/write port RAM that allows simultaneous access of the same memory cell from both ports. When one port writes to a given memory cell, the other port must not address that memory cell (for a write or a read) within the clock-to-clock setup window. The following lists specifics of port and memory cell write conflict resolution.

- If both ports write to the same memory cell simultaneously, violating the clock-to-clock setup requirement, consider the data stored as invalid.

- If one port attempts a read of the same memory cell the other simultaneously writes, violating the clock-to-clock setup requirement, the following occurs.

- The write succeeds

- The data out on the writing port accurately reflects the data written.

- The data out on the reading port is invalid.

Conflicts do not cause any physical damage.

#### Single Port Timing

Figure 33 shows a timing diagram for a single port of a block SelectRAM+ memory. The block SelectRAM+ AC switching characteristics are specified in the data sheet. The block SelectRAM+ memory is initially disabled.

At the first rising edge of the CLK pin, the ADDR, DI, EN, WE, and RST pins are sampled. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location, 0x00, as indicated by the ADDR bus.

At the second rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN and WE pins are High indicating a write operation. The DO bus mirrors the DI bus. The DI bus is written to the memory location 0x0F.

At the third rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is High

and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location 0x7E as indicated by the ADDR bus.

At the fourth rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is Low indicating that the block SelectRAM+ memory is now disabled. The DO bus retains the last value.

#### **Dual Port Timing**

Figure 34 shows a timing diagram for a true dual-port read/write block SelectRAM+ memory. The clock on port A has a longer period than the clock on Port B. The timing parameter T<sub>BCCS</sub>, (clock-to-clock set-up) is shown on this diagram. The parameter, T<sub>BCCS</sub> is violated once in the diagram. All other timing parameters are identical to the single port version shown in Figure 33.

T<sub>BCCS</sub> is only of importance when the address of both ports are the same and at least one port is performing a write operation. When the clock-to-clock set-up parameter is violated for a WRITE-WRITE condition, the contents of the memory at that location are invalid. When the clock-to-clock set-up parameter is violated for a WRITE-READ condition, the contents of the memory are correct, but the read port has invalid data. At the first rising edge of CLKA, memory location 0x00 is to be written with the value 0xAAAA and is mirrored on the DOA bus. The last operation of Port B was a read to the same memory location 0x00. The DOB bus of Port B does not change with the new value on Port A, and retains the last read value. A short time later, Port B executes another read to memory location 0x00, and the DOB bus now reflects the new memory value written by Port A.

At the second rising edge of CLKA, memory location 0x7E is written with the value 0x9999 and is mirrored on the DOA bus. Port B then executes a read operation to the same memory location without violating the  $T_{BCCS}$  parameter and the DOB reflects the new memory values written by Port A.

#### IOB Flip-Flop/Latch Property

The Virtex-E series I/O block (IOB) includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. The design implementation software automatically takes advantage of these registers when the following option for the Map program is specified.

```

map -pr b <filename>

```

Alternatively, the IOB = TRUE property can be placed on a register to force the mapper to place the register in an IOB.

#### **Location Constraints**

Specify the location of each SelectI/O symbol with the location constraint LOC attached to the SelectI/O symbol. The external port identifier indicates the value of the location constrain. The format of the port identifier depends on the package chosen for the specific design.

The LOC properties use the following form.

LOC=A42 LOC=P37

#### **Output Slew Rate Property**

As mentioned above, a variety of symbol names provide the option of choosing the desired slew rate for the output buffers. In the case of the LVTTL output buffers (OBUF, OBUFT, and IOBUF), slew rate control can be alternatively programed with the SLEW= property. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. The SLEW= property has one of the two following values.

SLEW=SLOW SLEW=FAST

#### **Output Drive Strength Property**

The desired output drive strength can be additionally specified by choosing the appropriate library symbol. The Xilinx library also provides an alternative method for specifying this feature. For the LVTTL output buffers (OBUF, OBUFT, and IOBUF, the desired drive strength can be specified with the DRIVE= property. This property could have one of the following seven values.

DRIVE=2

DRIVE=4

DRIVE=6

DRIVE=8

DRIVE=12 (Default)

DRIVE=16

DRIVE=24

## **Design Considerations**

## Reference Voltage (V<sub>REF</sub>) Pins

Low-voltage I/O standards with a differential amplifier input buffer require an input reference voltage ( $V_{REF}$ ). Provide the  $V_{REF}$  as an external signal to the device.

The voltage reference signal is "banked" within the device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 38 for a representation of the Virtex-E I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input. After placing a differential amplifier input signal within a given  $V_{REF}$  bank, the same external source must drive all I/O pins configured as a  $V_{REF}$  input.

Within each  $V_{REF}$  bank, any input buffers that require a  $V_{REF}$  signal must be of the same type. Output buffers of any type and input buffers can be placed without requiring a reference voltage within the same  $V_{REF}$  bank.

## Output Drive Source Voltage (V<sub>CCO</sub>) Pins

Many of the low voltage I/O standards supported by SelectI/O devices require a different output drive source voltage ( $V_{\rm CCO}$ ). As a result each device can often have to support multiple output drive source voltages.

The Virtex-E series supports eight banks for the HQ and PQ packages. The CS package supports four  $V_{CCO}$  banks.

Output buffers within a given  $V_{CCO}$  bank must share the same output drive source voltage. Input buffers for LVTTL, LVCMOS2, LVCMOS18, PCI33\_3, and PCI 66\_3 use the  $V_{CCO}$  voltage for Input  $V_{CCO}$  voltage.

#### Transmission Line Effects

The delay of an electrical signal along a wire is dominated by the rise and fall times when the signal travels a short distance. Transmission line delays vary with inductance and capacitance, but a well-designed board can experience delays of approximately 180 ps per inch.

Transmission line effects, or reflections, typically start at 1.5" for fast (1.5 ns) rise and fall times. Poor (or non-existent) termination or changes in the transmission line impedance cause these reflections and can cause additional delay in longer traces. As system speeds continue to increase, the effect of I/O delays can become a limiting factor and therefore transmission line termination becomes increasingly more important.

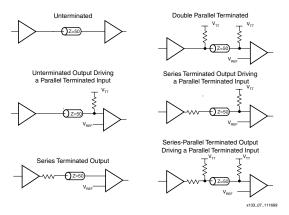

#### Termination Techniques

A variety of termination techniques reduce the impact of transmission line effects.

The following are output termination techniques:

- None

- Series

- Parallel (Shunt)

- Series and Parallel (Series-Shunt)

Input termination techniques include the following:

- None

- Parallel (Shunt)

These termination techniques can be applied in any combination. A generic example of each combination of termination methods appears in Figure 43.

Figure 43: Overview of Standard Input and Output Termination Methods

#### Simultaneous Switching Guidelines

Ground bounce can occur with high-speed digital ICs when multiple outputs change states simultaneously, causing undesired transient behavior on an output, or in the internal logic. This problem is also referred to as the Simultaneous Switching Output (SSO) problem.

Ground bounce is primarily due to current changes in the combined inductance of ground pins, bond wires, and ground metallization. The IC internal ground level deviates from the external system ground level for a short duration (a few nanoseconds) after multiple outputs change state simultaneously.

Ground bounce affects stable Low outputs and all inputs because they interpret the incoming signal by comparing it to the internal ground. If the ground bounce amplitude exceeds the actual instantaneous noise margin, then a non-changing input can be interpreted as a short pulse with a polarity opposite to the ground bounce.

Table 21 provides the guidelines for the maximum number of simultaneously switching outputs allowed per output power/ground pair to avoid the effects of ground bounce. Refer to Table 22 for the number of effective output power/ground pairs for each Virtex-E device and package combination.

Table 21: Guidelines for Maximum Number of Simultaneously Switching Outputs per Power/Ground Pair

|                                   | Package  |

|-----------------------------------|----------|

| Standard                          | BGA, FGA |

| LVTTL Slow Slew Rate, 2 mA drive  | 68       |

| LVTTL Slow Slew Rate, 4 mA drive  | 41       |

| LVTTL Slow Slew Rate, 6 mA drive  | 29       |

| LVTTL Slow Slew Rate, 8 mA drive  | 22       |

| LVTTL Slow Slew Rate, 12 mA drive | 17       |

| LVTTL Slow Slew Rate, 16 mA drive | 14       |

| LVTTL Slow Slew Rate, 24 mA drive | 9        |

| LVTTL Fast Slew Rate, 2 mA drive  | 40       |

| LVTTL Fast Slew Rate, 4 mA drive  | 24       |

| LVTTL Fast Slew Rate, 6 mA drive  | 17       |

| LVTTL Fast Slew Rate, 8 mA drive  | 13       |

| LVTTL Fast Slew Rate, 12 mA drive | 10       |

| LVTTL Fast Slew Rate, 16 mA drive | 8        |

| LVTTL Fast Slew Rate, 24 mA drive | 5        |

| LVCMOS                            | 10       |

| PCI                               | 8        |

| GTL                               | 4        |

| GTL+                              | 4        |

| HSTL Class I                      | 18       |

| HSTL Class III                    | 9        |

| HSTL Class IV                     | 5        |

| SSTL2 Class I                     | 15       |

| SSTL2 Class II                    | 10       |

| SSTL3 Class I                     | 11       |

| SSTL3 Class II                    | 7        |

| СТТ                               | 14       |

| AGP                               | 9        |

Note: This analysis assumes a 35 pF load for each output.

Table 22: Virtex-E Extended Memory Family Equivalent Power/Ground Pairs

| Pkg/Part | XCV405E | XCV812E |

|----------|---------|---------|

| BG560    |         | 56      |

| FG676    | 56      |         |

| FG900    |         |         |

## **Application Examples**

Creating a design with the SelectI/O features requires the instantiation of the desired library symbol within the design code. At the board level, designers need to know the termination techniques required for each I/O standard.

This section describes some common application examples illustrating the termination techniques recommended by each of the standards supported by the SelectI/O features.

#### Termination Examples

Circuit examples involving typical termination techniques for each of the SelectI/O standards follow. For a full range of accepted values for the DC voltage specifications for each standard, refer to the table associated with each figure.

The resistors used in each termination technique example and the transmission lines depicted represent board level components and are not meant to represent components on the device.

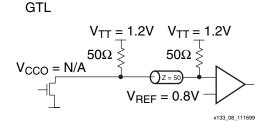

#### **GTL**

A sample circuit illustrating a valid termination technique for GTL is shown in Figure 44. Table 23 lists DC voltage specifications.

Figure 44: Terminated GTL

Table 23: GTL Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | N/A  | -    |

| $V_{REF} = N \times V_{TT}^{1}$                 | 0.74 | 0.8  | 0.86 |

| V <sub>TT</sub>                                 | 1.14 | 1.2  | 1.26 |

| $V_{IH} = V_{REF} + 0.05$                       | 0.79 | 0.85 | -    |

| $V_{IL} = V_{REF} - 0.05$                       | -    | 0.75 | 0.81 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | -    | 0.2  | 0.4  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.4V | 32   | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.2V | -    | -    | 40   |

Note: N must be greater than or equal to 0.653 and less than or equal to 0.68.

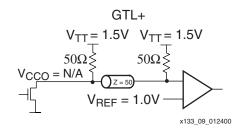

#### GTL+

A sample circuit illustrating a valid termination technique for GTL+ appears in Figure 45. DC voltage specifications appear in Table 24.

Figure 45: Terminated GTL+

Table 24: GTL+ Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | -    | -    |

| $V_{REF} = N \times V_{TT}^{1}$                 | 0.88 | 1.0  | 1.12 |

| V <sub>TT</sub>                                 | 1.35 | 1.5  | 1.65 |

| $V_{IH} = V_{REF} + 0.1$                        | 0.98 | 1.1  | -    |

| $V_{IL} = V_{REF} - 0.1$                        | -    | 0.9  | 1.02 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | 0.3  | 0.45 | 0.6  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.6V | 36   | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.3V | -    | -    | 48   |

Note: N must be greater than or equal to 0.653 and less than or equal to 0.68.

## **Creating LVDS Output 3-State Buffers**

LVDS output 3-state buffers can be placed in a wide number of IOB locations. The exact locations are dependent on the package used. The Virtex-E package information lists the possible locations as IO\_L#P for the P-side and IO\_L#N for the N-side, where # is the pair number.

#### HDL Instantiation

Both output 3-state buffers are required to be instantiated in the design and placed on the correct IO\_L#P and IO\_L#N locations. The IOB must have the same net source the following pins, clock (C), set/reset (SR), 3-state (T), 3-state clock enable (TCE), output (O), output clock enable (OCE). In addition, the output (O) pins must be inverted with respect to each other, and if output registers are used, the INIT states must be opposite values (one High and one Low). If 3-state registers are used, they must be initialized to the same state. Failure to follow these rules leads to DRC errors in the software

#### **VHDL** Instantiation

```

data0_p: OBUFT_LVDS port map

(I=>data_int(0), T=>data_tri,

0=>data_p(0));

data0_inv: INV port map

(I=>data_int(0), O=>data_n_int(0));

data0_n: OBUFT_LVDS port map

(I=>data_n_int(0), T=>data_tri,

0=>data_n(0));

```

#### **Verilog Instantiation**

#### **Location Constraints**

All LVDS buffers must be explicitly placed on a device. For the output buffers this can be done with the following constraint in the UCF or NCF file.

```

NET data_p<0> LOC = D28; # IO_LOP

NET data n<0> LOC = B29; # IO LON

```

#### Synchronous vs. Asynchronous 3-State Outputs

If the outputs are synchronous (registered in the IOB), then any IO\_L#PIN pair can be used. If the outputs are asynchronous (no output register), then they must use one of the pairs that are part of the same IOB group at the end of a ROW or at the top/bottom of a COLUMN in the device. This applies for either the 3-state pin or the data out pin.

LVDS pairs that can be used as asynchronous outputs are listed in the Virtex-E pinout tables. Some pairs are marked as "asynchronous capable" for all devices in that package, and others are marked as available only for that device in the package. If the device size might be changed at some point in the product lifetime, then only the common pairs for all packages should be used.

#### Adding Output and 3-State Registers

All LVDS buffers can have an output register in the IOB. The output registers must be in both the P-side and N-side IOBs. All the normal IOB register options are available (FD, FDE, FDC, FDCE, FDP, FDPE, FDR, FDRE, FDS, FDSE, LD, LDE, LDC, LDCE, LDP, LDPE). The register elements can be inferred or explicitly instantiated in the HDL code.

Special care must be taken to insure that the D pins of the registers are inverted and that the INIT states of the registers are opposite. The 3-state (T), 3-state clock enable (CE), clock pin (C), output clock enable (CE) and set/reset (CLR/PRE or S/R) pins must connect to the same source. Failure to do this leads to a DRC error in the software.

The register elements can be packed in the IOB using the IOB property to TRUE on the register or by using the "map-pr [ilolb]" where "i" is inputs only, "o" is outputs only and "b" is both inputs and outputs.

To improve design coding times VHDL and Verilog synthesis macro libraries have been developed to explicitly create these structures. The input library macros are listed below. The 3-state is configured to be 3-stated at GSR and when the PRE,CLR,S or R is asserted and shares it's clock enable with the output register. If this is not desirable, the library can be updated by the user for the desired functionality. The O and OB inputs to the macros are the external net connections.

## **Creating LVDS Bidirectional Buffer**

LVDS bidirectional buffers can be placed in a wide number of IOB locations. The exact locations are dependent on the package used. The Virtex-E package information lists the possible locations as IO\_L#P for the P-side and IO\_L#N for the N-side, where # is the pair number.

## **HDL Instantiation**

Both bidirectional buffers are required to be instantiated in the design and placed on the correct IO\_L#P and IO\_L#N locations. The IOB must have the same net source the following pins, clock (C), set/reset (SR), 3-state (T), 3-state clock enable (TCE), output (O), output clock enable (OCE). In addition, the output (O) pins must be inverted with respect to each other, and if output registers are used, the INIT states must be opposite values (one HIGH and one LOW). If 3-state registers are used, they must be initialized to the same state. Failure to follow these rules leads to DRC errors in the software.

## **IOB Output Switching Characteristics Standard Adjustments**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown.

|                                                                       |                         |                                          |       | Speed    | Grade    |          |       |

|-----------------------------------------------------------------------|-------------------------|------------------------------------------|-------|----------|----------|----------|-------|

| Description                                                           | Symbol                  | Standard                                 | Min   | -8       | -7       | -6       | Units |

| Output Delay Adjustments                                              |                         |                                          |       | <u> </u> | <u>'</u> | <u> </u> |       |

| Standard-specific adjustments for                                     | T <sub>OLVTTL_S2</sub>  | T <sub>OLVTTL_S2</sub> LVTTL, Slow, 2 mA |       | +14.7    | +14.7    | +14.7    | ns    |

| output delays terminating at pads (based on standard capacitive load, | T <sub>OLVTTL_S4</sub>  | 4 mA                                     | 2.5   | +7.5     | +7.5     | +7.5     | ns    |

| Csl)                                                                  | T <sub>OLVTTL_S6</sub>  | 6 mA                                     | 1.8   | +4.8     | +4.8     | +4.8     | ns    |

|                                                                       | T <sub>OLVTTL_S8</sub>  | 8 mA                                     | 1.2   | +3.0     | +3.0     | +3.0     | ns    |

|                                                                       | T <sub>OLVTTL_S12</sub> | 12 mA                                    | 1.0   | +1.9     | +1.9     | +1.9     | ns    |

|                                                                       | T <sub>OLVTTL_S16</sub> | 16 mA                                    | 0.9   | +1.7     | +1.7     | +1.7     | ns    |

|                                                                       | T <sub>OLVTTL_S24</sub> | 24 mA                                    | 0.8   | +1.3     | +1.3     | +1.3     | ns    |

|                                                                       | T <sub>OLVTTL_F2</sub>  | LVTTL, Fast, 2 mA                        | 1.9   | +13.1    | +13.1    | +13.1    | ns    |

|                                                                       | T <sub>OLVTTL_F4</sub>  | 4 mA                                     | 0.7   | +5.3     | +5.3     | +5.3     | ns    |

|                                                                       | T <sub>OLVTTL_F6</sub>  | 6 mA                                     | 0.20  | +3.1     | +3.1     | +3.1     | ns    |

|                                                                       | T <sub>OLVTTL_F8</sub>  | 8 mA                                     | 0.10  | +1.0     | +1.0     | +1.0     | ns    |

|                                                                       | T <sub>OLVTTL_F12</sub> | 12 mA                                    | 0.0   | 0.0      | 0.0      | 0.0      | ns    |

|                                                                       | T <sub>OLVTTL_F16</sub> | 16 mA                                    | -0.10 | -0.05    | -0.05    | -0.05    | ns    |

|                                                                       | T <sub>OLVTTL_F24</sub> | 24 mA                                    | -0.10 | -0.20    | -0.20    | -0.20    | ns    |

|                                                                       | T <sub>OLVCMOS_2</sub>  | LVCMOS2                                  | 0.10  | +0.09    | +0.09    | +0.09    | ns    |

|                                                                       | T <sub>OLVCMOS_18</sub> | LVCMOS18                                 | 0.10  | +0.7     | +0.7     | +0.7     | ns    |

|                                                                       | T <sub>OLVDS</sub>      | LVDS                                     | -0.39 | -1.2     | -1.2     | -1.2     | ns    |

|                                                                       | T <sub>OLVPECL</sub>    | LVPECL                                   | -0.20 | -0.41    | -0.41    | -0.41    | ns    |

|                                                                       | T <sub>OPCI33_3</sub>   | PCI, 33 MHz, 3.3 V                       | 0.50  | +2.3     | +2.3     | +2.3     | ns    |

|                                                                       | T <sub>OPCI66_3</sub>   | PCI, 66 MHz, 3.3 V                       | 0.10  | -0.41    | -0.41    | -0.41    | ns    |

|                                                                       | T <sub>OGTL</sub>       | GTL                                      | 0.6   | +0.49    | +0.49    | +0.49    | ns    |

|                                                                       | T <sub>OGTLP</sub>      | GTL+                                     | 0.7   | +0.8     | +0.8     | +0.8     | ns    |

|                                                                       | T <sub>OHSTL_I</sub>    | HSTL I                                   | 0.10  | -0.51    | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OHSTL_IIII</sub> | HSTL III                                 | -0.10 | -0.91    | -0.91    | -0.91    | ns    |

|                                                                       | T <sub>OHSTL_IV</sub>   | HSTL IV                                  | -0.20 | -1.01    | -1.01    | -1.01    | ns    |

|                                                                       | T <sub>OSSTL2_I</sub>   | SSTL2 I                                  | -0.10 | -0.51    | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OSSTL2_II</sub>  | SSTL2 II                                 | -0.20 | -0.91    | -0.91    | -0.91    | ns    |

|                                                                       | T <sub>OSSTL3_I</sub>   | SSTL3 I                                  | -0.20 | -0.51    | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OSSTL3_II</sub>  | SSTL3 II                                 | -0.30 | -1.01    | -1.01    | -1.01    | ns    |

|                                                                       | T <sub>OCTT</sub>       | CTT                                      | 0.0   | -0.61    | -0.61    | -0.61    | ns    |

|                                                                       | T <sub>OAGP</sub>       | AGP                                      | -0.1  | -0.91    | -0.91    | -0.91    | ns    |

## **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                             |                                      | Speed Grade |          |         |         |         |

|---------------------------------------------|--------------------------------------|-------------|----------|---------|---------|---------|

| Description <sup>(1)</sup>                  | Symbol                               | Min         | -8       | -7      | -6      | Units   |

| Combinatorial Delays                        |                                      |             |          |         |         |         |

| F operand inputs to X via XOR               | T <sub>OPX</sub>                     | 0.32        | 0.68     | 0.8     | 0.8     | ns, max |

| F operand input to XB output                | T <sub>OPXB</sub>                    | 0.35        | 0.65     | 0.8     | 0.9     | ns, max |

| F operand input to Y via XOR                | T <sub>OPY</sub>                     | 0.59        | 1.07     | 1.4     | 1.5     | ns, max |

| F operand input to YB output                | T <sub>OPYB</sub>                    | 0.48        | 0.89     | 1.1     | 1.3     | ns, max |

| F operand input to COUT output              | T <sub>OPCYF</sub>                   | 0.37        | 0.71     | 0.9     | 1.0     | ns, max |

| G operand inputs to Y via XOR               | T <sub>OPGY</sub>                    | 0.34        | 0.72     | 0.8     | 0.9     | ns, max |

| G operand input to YB output                | T <sub>OPGYB</sub>                   | 0.47        | 0.78     | 1.2     | 1.3     | ns, max |

| G operand input to COUT output              | T <sub>OPCYG</sub>                   | 0.36        | 0.60     | 0.9     | 1.0     | ns, max |

| BX initialization input to COUT             | T <sub>BXCY</sub>                    | 0.19        | 0.36     | 0.51    | 0.57    | ns, max |

| CIN input to X output via XOR               | T <sub>CINX</sub>                    | 0.27        | 0.50     | 0.6     | 0.7     | ns, max |

| CIN input to XB                             | T <sub>CINXB</sub>                   | 0.02        | 0.04     | 0.07    | 0.08    | ns, max |

| CIN input to Y via XOR                      | T <sub>CINY</sub>                    | 0.26        | 0.45     | 0.7     | 0.7     | ns, max |

| CIN input to YB                             | T <sub>CINYB</sub>                   | 0.16        | 0.28     | 0.38    | 0.43    | ns, max |

| CIN input to COUT output                    | T <sub>BYP</sub>                     | 0.05        | 0.10     | 0.14    | 0.15    | ns, max |

| Multiplier Operation                        |                                      |             |          |         |         |         |

| F1/2 operand inputs to XB output via AND    | T <sub>FANDXB</sub>                  | 0.10        | 0.30     | 0.35    | 0.39    | ns, max |

| F1/2 operand inputs to YB output via AND    | T <sub>FANDYB</sub>                  | 0.28        | 0.56     | 0.7     | 0.8     | ns, max |

| F1/2 operand inputs to COUT output via AND  | T <sub>FANDCY</sub>                  | 0.17        | 0.38     | 0.46    | 0.51    | ns, max |

| G1/2 operand inputs to YB output via AND    | T <sub>GANDYB</sub>                  | 0.20        | 0.46     | 0.55    | 0.7     | ns, max |

| G1/2 operand inputs to COUT output via AND  | T <sub>GANDCY</sub>                  | 0.09        | 0.28     | 0.30    | 0.34    | ns, max |

| Setup and Hold Times before/after Clock CLK |                                      | _           |          |         | •       |         |

| CIN input to FFX                            | T <sub>CCKX</sub> /T <sub>CKCX</sub> | 0.47 / 0    | 1.0 / 0  | 1.2 / 0 | 1.3 / 0 | ns, min |

| CIN input to FFY                            | T <sub>CCKY</sub> /T <sub>CKCY</sub> | 0.49 / 0    | 0.92 / 0 | 1.2 / 0 | 1.3 / 0 | ns, min |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

## **Virtex-E Pin-to-Pin Output Parameter Guidelines**

All devices are 100% functionally tested. Listed below are representative values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted.

## Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, with DLL

|                                                                                                                                                                    |                       |                       | Speed Grade <sup>(2)</sup> |     |     |     |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------------|-----|-----|-----|-------|

| Description <sup>(1)</sup>                                                                                                                                         | Symbol                | Device <sup>(3)</sup> | Min                        | -8  | -7  | -6  | Units |

| LVTTL Global Clock Input to Output Delay using                                                                                                                     | T <sub>ICKOFDLL</sub> | XCV405E               | 1.0                        | 3.1 | 3.1 | 3.1 | ns    |

| Output Flip-flop, 12 mA, Fast Slew Rate, with DLL.                                                                                                                 |                       | XCV812E               | 1.0                        | 3.1 | 3.1 | 3.1 | ns    |

| For data <i>output</i> with different standards, adjust the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8. |                       |                       |                            |     |     |     |       |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 50% V<sub>CC</sub> threshold with 35 pF external capacitive load. For other I/O standards and different loads, see Table 2 and Table 3.

- 3. DLL output jitter is already included in the timing calculation.

## Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, without DLL

|                                                              |                                                                                                                                                                    |                    |         |     | Speed | Grade <sup>(2)</sup> |     |       |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-----|-------|----------------------|-----|-------|--|

|                                                              | Description <sup>(1)</sup>                                                                                                                                         | Symbol             | Device  | Min | -8    | -7                   | -6  | Units |  |

|                                                              | LVTTL Global Clock Input to Output Delay using                                                                                                                     | T <sub>ICKOF</sub> | XCV405E | 1.6 | 4.5   | 4.7                  | 4.9 | ns    |  |

| Output Flip-flop, 12 mA, Fast Slew Rate, <i>without</i> DLL. |                                                                                                                                                                    |                    | XCV812E | 1.8 | 4.8   | 5.0                  | 5.2 | ns    |  |

|                                                              | For data <i>output</i> with different standards, adjust the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8. |                    |         |     |       |                      |     |       |  |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 50% V<sub>CC</sub> threshold with 35 pF external capacitive load. For other I/O standards and different loads, see Table 2 and Table 3.

## **Virtex-E Pin-to-Pin Input Parameter Guidelines**

All devices are 100% functionally tested. Listed below are representative values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted.

## Global Clock Set-Up and Hold for LVTTL Standard, with DLL

|                                                                                                                                                                   |                                        |                       | Speed Grade <sup>(2)</sup> |            |            |            |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------|----------------------------|------------|------------|------------|-------|

| Description <sup>(1)</sup> Symbol Description                                                                                                                     |                                        | Device <sup>(3)</sup> | Min                        | -8         | -7         | -6         | Units |

| Input Setup and Hold Time Rela for LVTTL Standard.                                                                                                                |                                        |                       |                            |            |            |            |       |

| For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Switching Characteristics Standard Adjustments" on page 6. |                                        |                       |                            |            |            |            |       |

| No Delay                                                                                                                                                          | T <sub>PSDLL</sub> /T <sub>PHDLL</sub> | XCV405E               | 1.5 / -0.4                 | 1.5 / -0.4 | 1.6 / -0.4 | 1.7 / -0.4 | ns    |

| Global Clock and IFF, with DLL                                                                                                                                    |                                        | XCV812E               | 1.5 / -0.4                 | 1.5 / -0.4 | 1.6 / -0.4 | 1.7 / -0.4 | ns    |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. DLL output jitter is already included in the timing calculation.

## Global Clock Set-Up and Hold for LVTTL Standard, without DLL

|                                                                                                                                                                   |                                      |                       | Speed Grade <sup>(2)</sup> |         |         |         |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|----------------------------|---------|---------|---------|-------|

| Description <sup>(1)</sup>                                                                                                                                        | Symbol                               | Device <sup>(3)</sup> | Min                        | -8      | -7      | -6      | Units |

| Input Setup and Hold Time Relative for LVTTL Standard.                                                                                                            |                                      |                       |                            |         |         |         |       |

| For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Switching Characteristics Standard Adjustments" on page 6. |                                      |                       |                            |         |         |         |       |

| Full Delay                                                                                                                                                        | T <sub>PSFD</sub> /T <sub>PHFD</sub> | XCV405E               | 2.3 / 0                    | 2.3 / 0 | 2.3 / 0 | 2.3 / 0 | ns    |

| Global Clock and IFF, without DLL                                                                                                                                 |                                      | XCV812E               | 2.5 / 0                    | 2.5 / 0 | 2.5 / 0 | 2.5 / 0 | ns    |

#### Notes:

- IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

| Table 1: | BG560 BGA — XCV405E and XCV812E |

|----------|---------------------------------|

| iabic i. | Bacco Bax XCV+00E and XCVC12E   |

|      | Dadoo Bar Roving Land Rove 122 |                  |  |  |  |

|------|--------------------------------|------------------|--|--|--|

| Bank | Pin Description                | Pin#             |  |  |  |

| 2    | IO_L61N_Y                      | N3               |  |  |  |

| 2    | IO_L62P_Y                      | N2               |  |  |  |

| 2    | IO_L62N_Y                      | P5               |  |  |  |

| 2    | IO_VREF_L63P_YY                | P4               |  |  |  |

| 2    | IO_D3_L63N_YY                  | P3               |  |  |  |

| 2    | IO_L64P_Y                      | P2               |  |  |  |

| 2    | IO_L64N_Y                      | R5               |  |  |  |

| 2    | IO_L65P_Y                      | R4               |  |  |  |

| 2    | IO_L65N_Y                      | R3               |  |  |  |

| 2    | IO_VREF_L66P_Y                 | R1               |  |  |  |

| 2    | IO_L66N_Y                      | T4               |  |  |  |

| 2    | IO_L67P_Y                      | T5               |  |  |  |

| 2    | IO_L67N_Y                      | Т3               |  |  |  |

| 2    | IO_L68P_YY                     | T2               |  |  |  |

| 2    | IO_L68N_YY                     | U3               |  |  |  |

|      |                                |                  |  |  |  |

| 3    | 10                             | U4               |  |  |  |

| 3    | 10                             | AE3              |  |  |  |

| 3    | 10                             | AF3              |  |  |  |

| 3    | 10                             | AH3              |  |  |  |

| 3    | 10                             | AK3              |  |  |  |

| 3    | IO_L69P_Y                      | U1               |  |  |  |

| 3    | IO_L69N_Y                      | U2               |  |  |  |

| 3    | IO_L70P_Y                      | V2               |  |  |  |

| 3    | IO_VREF_L70N_Y                 | V4               |  |  |  |

| 3    | IO_L71P_Y                      | V5               |  |  |  |

| 3    | IO_L71N_Y                      | V3               |  |  |  |

| 3    | IO_L72P                        | W1               |  |  |  |

| 3    | IO_L72N                        | W3               |  |  |  |

| 3    | IO_D4_L73P_YY                  | W4               |  |  |  |

| 3    | IO_VREF_L73N_YY                | W5               |  |  |  |

| 3    | IO_L74P_Y                      | Y3               |  |  |  |

| 3    | IO_L74N_Y                      | Y4               |  |  |  |

| 3    | IO_L75P                        | AA1              |  |  |  |

| 3    | IO_L75N                        | Y5               |  |  |  |

| 3    | IO_L76P_Y                      | AA3              |  |  |  |

| 3    | IO_VREF_L76N_Y                 | AA4 <sup>1</sup> |  |  |  |

Table 1: BG560 BGA — XCV405E and XCV812E

| 74010 11 |                 |                  |

|----------|-----------------|------------------|

| Bank     | Pin Description | Pin#             |

| 3        | IO_L77P         | AB3              |

| 3        | IO_L77N         | AA5              |

| 3        | IO_L78P         | AC1              |

| 3        | IO_L78N         | AB4              |

| 3        | IO_L79P_YY      | AC3              |

| 3        | IO_D5_L79N_YY   | AB5              |

| 3        | IO_D6_L80P_YY   | AC4              |

| 3        | IO_VREF_L80N_YY | AD3              |

| 3        | IO_L81P_Y       | AE1              |

| 3        | IO_L81N_Y       | AC5              |

| 3        | IO_L82P_YY      | AD4              |

| 3        | IO_VREF_L82N_YY | AF1 <sup>1</sup> |

| 3        | IO_L83P_Y       | AF2              |

| 3        | IO_L83N_Y       | AD5              |

| 3        | IO_L84P_Y       | AG2              |

| 3        | IO_L84N_Y       | AE4              |

| 3        | IO_L85P_YY      | AH1              |

| 3        | IO_VREF_L85N_YY | AE5              |

| 3        | IO_L86P_Y       | AF4              |

| 3        | IO_L86N_Y       | AJ1              |

| 3        | IO_L87P_Y       | AJ2              |

| 3        | IO_L87N_Y       | AF5              |

| 3        | IO_L88P_Y       | AG4              |

| 3        | IO_VREF_L88N_Y  | AK2              |

| 3        | IO_L89P_Y       | AJ3              |

| 3        | IO_L89N_Y       | AG5              |

| 3        | IO_L90P_Y       | AL1              |

| 3        | IO_L90N_Y       | AH4              |

| 3        | IO_D7_L91P_YY   | AJ4              |

| 3        | IO_INIT_L91N_YY | AH5              |

|          |                 |                  |

| 4        | GCK0            | AL17             |

| 4        | Ю               | AJ8              |

| 4        | 10              | AJ11             |

| 4        | Ю               | AK6              |

| 4        | IO              | AK9              |

| 4        | IO_L92P_YY      | AL4              |

|          | 1               | 1                |

| Table | 1. | BCECO I | BC A  | VCV/105E a | nd XCV812E |

|-------|----|---------|-------|------------|------------|

| iabie | 1: | BGSSU   | BGA — | ALV4USE a  | na xuvoize |

| Table 1. | CVOIZL           |                   |

|----------|------------------|-------------------|

| Bank     | Pin Description  | Pin#              |

| 4        | IO_L92N_YY       | AJ6               |

| 4        | IO_L93P          | AK5               |

| 4        | IO_L93N          | AN3               |

| 4        | IO_L94P_YY       | AL5               |

| 4        | IO_L94N_YY       | AJ7               |

| 4        | IO_VREF_L95P_YY  | AM4               |

| 4        | IO_L95N_YY       | AM5               |

| 4        | IO_L96P_Y        | AK7               |

| 4        | IO_L96N_Y        | AL6               |

| 4        | IO_L97P_YY       | AM6               |

| 4        | IO_L97N_YY       | AN6               |

| 4        | IO_VREF_L98P_YY  | AL7               |

| 4        | IO_L98N_YY       | AJ9               |

| 4        | IO_L99P          | AN7               |

| 4        | IO_L99N          | AL8               |

| 4        | IO_L100P_YY      | AM8               |

| 4        | IO_L100N_YY      | AJ10              |

| 4        | IO_VREF_L101P_YY | AL9 <sup>1</sup>  |

| 4        | IO_L101N_YY      | AM9               |

| 4        | IO_L102P_Y       | AK10              |

| 4        | IO_L102N_Y       | AN9               |

| 4        | IO_VREF_L103P_YY | AL10              |

| 4        | IO_L103N_YY      | AM10              |

| 4        | IO_L104P_YY      | AL11              |

| 4        | IO_L104N_YY      | AJ12              |

| 4        | IO_L105P         | AN11              |

| 4        | IO_L105N         | AK12              |

| 4        | IO_L106P_YY      | AL12              |

| 4        | IO_L106N_YY      | AM12              |

| 4        | IO_VREF_L107P_YY | AK13 <sup>1</sup> |

| 4        | IO_L107N_YY      | AL13              |

| 4        | IO_L108P_Y       | AM13              |

| 4        | IO_L108N_Y       | AN13              |

| 4        | IO_L109P_YY      | AJ14              |

| 4        | IO_L109N_YY      | AK14              |

| 4        | IO_VREF_L110P_YY | AM14              |

| 4        | IO_L110N_YY      | AN15              |

|          |                  |                   |

Table 1: BG560 BGA — XCV405E and XCV812E

|      | Table 1: BG360 BGA — XCV403E and XCV812E |                   |  |  |  |

|------|------------------------------------------|-------------------|--|--|--|

| Bank | Pin Description                          | Pin#              |  |  |  |

| 4    | IO_L111P                                 | AJ15              |  |  |  |

| 4    | IO_L111N                                 | AK15              |  |  |  |

| 4    | IO_L112P_YY                              | AL15              |  |  |  |

| 4    | IO_L112N_YY                              | AM16              |  |  |  |

| 4    | IO_VREF_L113P_YY                         | AL16              |  |  |  |

| 4    | IO_L113N_YY                              | AJ16              |  |  |  |

| 4    | IO_L114P_Y                               | AK16              |  |  |  |

| 4    | IO_L114N_Y                               | AN17              |  |  |  |

| 4    | IO_LVDS_DLL_L115P                        | AM17              |  |  |  |

|      |                                          |                   |  |  |  |

| 5    | GCK1                                     | AJ17              |  |  |  |

| 5    | 10                                       | AL18              |  |  |  |

| 5    | 10                                       | AL25              |  |  |  |

| 5    | 10                                       | AL28              |  |  |  |

| 5    | 10                                       | AL30              |  |  |  |

| 5    | 10                                       | AN28              |  |  |  |

| 5    | IO_LVDS_DLL_L115N                        | AM18              |  |  |  |

| 5    | IO_L116P_YY                              | AK18              |  |  |  |

| 5    | IO_VREF_L116N_YY                         | AJ18              |  |  |  |

| 5    | IO_L117P_YY                              | AN19              |  |  |  |

| 5    | IO_L117N_YY                              | AL19              |  |  |  |

| 5    | IO_L118P                                 | AK19              |  |  |  |

| 5    | IO_L118N                                 | AM20              |  |  |  |

| 5    | IO_L119P_YY                              | AJ19              |  |  |  |

| 5    | IO_VREF_L119N_YY                         | AL20              |  |  |  |

| 5    | IO_L120P_YY                              | AN21              |  |  |  |

| 5    | IO_L120N_YY                              | AL21              |  |  |  |

| 5    | IO_L121P_Y                               | AJ20              |  |  |  |

| 5    | IO_L121N_Y                               | AM22              |  |  |  |

| 5    | IO_L122P_YY                              | AK21              |  |  |  |

| 5    | IO_VREF_L122N_YY                         | AN23 <sup>1</sup> |  |  |  |

| 5    | IO_L123P_YY                              | AJ21              |  |  |  |

| 5    | IO_L123N_YY                              | AM23              |  |  |  |

| 5    | IO_L124P                                 | AK22              |  |  |  |

| 5    | IO_L124N                                 | AM24              |  |  |  |

| 5    | IO_L125P_YY                              | AL23              |  |  |  |

| 5    | IO_L125N_YY                              | AJ22              |  |  |  |

| Table | 1. | BG560 | BGA — | XCV405E | and XCV   | 812F |

|-------|----|-------|-------|---------|-----------|------|

| iabic |    | Dasou | DUA   | AC TOUL | alla AU V |      |

| Bank         Pin Description         Pin#           NA         VCCINT         B18           NA         VCCINT         C22           NA         VCCINT         C24           NA         VCCINT         E9           NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         M3           NA         VCCINT         M3           NA         VCCINT         N1           NA         VCCINT         N29           NA         VCCINT         N33           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         AB2           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AG3           NA         VCCINT         AG3           NA         VCCINT         AK8           NA         VCCINT         AK8           NA                                  | Danie 1. |                 |      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|------|--|--|--|

| NA         VCCINT         B28           NA         VCCINT         C22           NA         VCCINT         E9           NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         M3           NA         VCCINT         M3           NA         VCCINT         M3           NA         VCCINT         N29           NA         VCCINT         N29           NA         VCCINT         U5           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         AB2           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AG31           NA         VCCINT         AK11           NA                                            | Bank     | Pin Description | Pin# |  |  |  |

| NA         VCCINT         C22           NA         VCCINT         E9           NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         H30           NA         VCCINT         H30           NA         VCCINT         H30           NA         VCCINT         M3           NA         VCCINT         M30           NA         VCCINT         N29           NA         VCCINT         N33           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         Y2           NA         VCCINT         AB2           NA         VCCINT         AB2           NA         VCCINT         AD32           NA         VCCINT         AG3           NA         VCCINT         AG3           NA         VCCINT         AK1           NA         VCCINT         AK1           NA         VCCINT         AK20           NA                                           |          |                 |      |  |  |  |

| NA         VCCINT         E9           NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         M3           NA         VCCINT         M3           NA         VCCINT         N29           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         Y31           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AD32           NA         VCCINT         AG31           NA         VCCINT         AG31           NA         VCCINT         AK31           NA         VCCINT         AK8           NA         VCCINT         AK11           NA         VCCINT         AK20           NA         VCCINT         AK20           NA         VCCINT         AL27           NA         VCCINT         AL27           NA </td <td></td> <td></td> <td></td> |          |                 |      |  |  |  |

| NA         VCCINT         E9           NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         K32           NA         VCCINT         M3           NA         VCCINT         N1           NA         VCCINT         N29           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AD32           NA         VCCINT         AG31           NA         VCCINT         AG31           NA         VCCINT         AK13           NA         VCCINT         AK8           NA         VCCINT         AK11           NA         VCCINT         AK20           NA         VCCINT         AL24           NA         VCCINT         AL27           NA <td></td> <td></td> <td></td>       |          |                 |      |  |  |  |

| NA         VCCINT         E12           NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         K32           NA         VCCINT         M3           NA         VCCINT         N1           NA         VCCINT         N29           NA         VCCINT         N33           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y31           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AD32           NA         VCCINT         AG3           NA         VCCINT         AG31           NA         VCCINT         AK31           NA         VCCINT         AK11           NA         VCCINT         AK11           NA         VCCINT         AK20           NA         VCCINT         AL214           NA         VCCINT         AL22           NA         VCCINT         AL27           N                                  |          |                 |      |  |  |  |

| NA         VCCINT         F2           NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         K32           NA         VCCINT         M3           NA         VCCINT         N1           NA         VCCINT         N29           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         Y31           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AD32           NA         VCCINT         AG3           NA         VCCINT         AG3           NA         VCCINT         AK1           NA         VCCINT         AK8           NA         VCCINT         AK11           NA         VCCINT         AK20           NA         VCCINT         AL22           NA         VCCINT         AL22           NA         VCCINT         AL22           NA         VCCINT         AN25                                                  |          |                 |      |  |  |  |

| NA         VCCINT         H30           NA         VCCINT         J1           NA         VCCINT         K32           NA         VCCINT         M3           NA         VCCINT         N1           NA         VCCINT         N29           NA         VCCINT         N33           NA         VCCINT         U5           NA         VCCINT         U30           NA         VCCINT         Y2           NA         VCCINT         Y31           NA         VCCINT         AB2           NA         VCCINT         AB32           NA         VCCINT         AD32           NA         VCCINT         AG3           NA         VCCINT         AG3           NA         VCCINT         AK8           NA         VCCINT         AK11           NA         VCCINT         AK20           NA         VCCINT         AL22           NA         VCCINT         AL27           NA         VCCINT         AL27           NA         VCCINT         AN25                                                                                         |          |                 | E12  |  |  |  |