Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4704                                                        |

| Number of Logic Elements/Cells | 21168                                                       |

| Total RAM Bits                 | 1146880                                                     |

| Number of I/O                  | 404                                                         |

| Number of Gates                | 254016                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 560-LBGA Exposed Pad, Metal                                 |

| Supplier Device Package        | 560-MBGA (42.5x42.5)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv812e-8bg560c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                    |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/23/00 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                     |

| 08/01/00 | 1.1     | Accumulated edits and fixes. Upgrade to Preliminary. Preview -8 numbers added. Reformatted to adhere to corporate documentation style guidelines. Minor changes in BG560 pin-out table.                                                     |

| 09/19/00 | 1.2     | <ul> <li>In Table 3 (Module 4), FG676 Fine-Pitch BGA — XCV405E, the following pins are no longer labeled as VREF: B7, G16, G26, W26, AF20, AF8, Y1, H1.</li> <li>Min values added to Virtex-E Electrical Characteristics tables.</li> </ul> |

| 11/20/00 | 1.3     | <ul> <li>Updated speed grade -8 numbers in Virtex-E Electrical Characteristics tables<br/>(Module 3).</li> </ul>                                                                                                                            |

|          |         | • Updated minimums in Table 11 (Module 2), and added notes to Table 12 (Module 2).                                                                                                                                                          |

|          |         | Added to note 2 of Absolute Maximum Ratings (Module 3).                                                                                                                                                                                     |

|          |         | • Changed all minimum hold times to -0.4 for Global Clock Set-Up and Hold for LVTTL Standard, with DLL (Module 3).                                                                                                                          |

|          |         | • Revised maximum T <sub>DLLPW</sub> in -6 speed grade for <b>DLL Timing Parameters</b> (Module 3).                                                                                                                                         |

| 04/02/01 | 1.4     | <ul> <li>In Table 4, FG676 Fine-Pitch BGA — XCV405E, pin B19 is no longer labeled as VREF, and pin G16 is now labeled as VREF.</li> <li>Updated values in Virtex-E Switching Characteristics tables.</li> </ul>                             |

|          |         | Converted data sheet to modularized format. See Virtex-E Extended Memory Data Sheet, below.                                                                                                                                                 |

| 07/17/02 | 1.5     | Data sheet designation upgraded from Preliminary to Production.                                                                                                                                                                             |

# **Virtex-E Extended Memory Data Sheet**

The Virtex-E Extended Memory Data Sheet contains the following modules:

- DS025-1, Virtex-E 1.8V Extended Memory FPGAs: Introduction and Ordering Information (Module 1)

- DS025-2, Virtex-E 1.8V Extended Memory FPGAs: Functional Description (Module 2)

- DS025-3, Virtex-E 1.8V Extended Memory FPGAs:

DC and Switching Characteristics (Module 3)

- DS025-4, Virtex-E 1.8V Extended Memory FPGAs: <u>Pinout Tables (Module 4)</u>

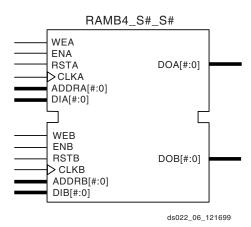

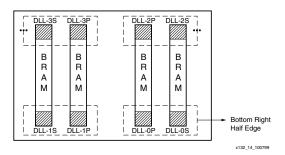

Figure 6: Dual-Port Block SelectRAM

Table 5 shows the depth and width aspect ratios for the block SelectRAM. The Virtex-E block SelectRAM also includes dedicated routing to provide an efficient interface with both CLBs and other block SelectRAM modules. Refer to XAPP130 for block SelectRAM timing waveforms.

Table 5: Block SelectRAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

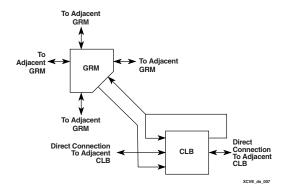

# **Programmable Routing Matrix**

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Virtex-E routing architecture and its place-and-route software were defined in a joint optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

### Local Routing

The VersaBlock, shown in Figure 7, provides local routing resources with the following types of connections:

- Interconnections among the LUTs, flip-flops, and GRM

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the

#### delay of the GRM

Figure 7: Virtex-E Local Routing

### General Purpose Routing

Most Virtex-E signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the CLB rows and columns. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 72 buffered Hex lines route GRM signals to another GRMs six-blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines are driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are uni-directional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

#### I/O Routing

Virtex-E devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

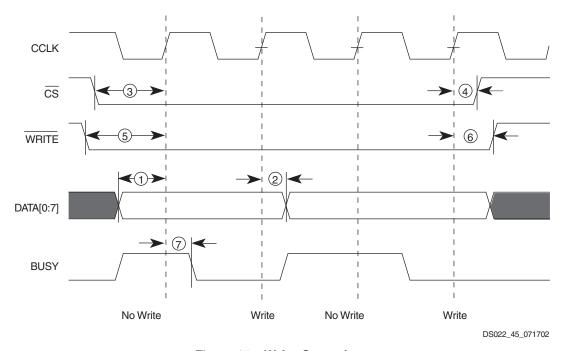

- either asserted or de-asserted. Otherwise an abort is initiated, as described below.

- 2. Drive data onto D[7:0]. Note that to avoid contention, the data source should not be enabled while  $\overline{CS}$  is Low and  $\overline{WRITE}$  is High. Similarly, while  $\overline{WRITE}$  is High, no more that one  $\overline{CS}$  should be asserted.

- At the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance instead occurs on the first clock after BUSY goes Low, and the data must be held until this has happened.

- 4. Repeat steps 2 and 3 until all the data has been sent.

- De-assert CS and WRITE.

Table 11: SelectMAP Write Timing Characteristics

|      | Description                         |     | Symbol                                   | Values    | Units    |

|------|-------------------------------------|-----|------------------------------------------|-----------|----------|

|      | D <sub>0-7</sub> Setup/Hold         | 1/2 | $T_{SMDCC}/T_{SMCCD}$                    | 5.0 / 1.7 | ns, min  |

|      | CS Setup/Hold                       | 3/4 | T <sub>SMCSCC</sub> /T <sub>SMCCCS</sub> | 7.0 / 1.7 | ns, min  |

| CCLK | WRITE Setup/Hold                    | 5/6 | T <sub>SMCCW</sub> /T <sub>SMWCC</sub>   | 7.0 / 1.7 | ns, min  |

| OOLK | BUSY Propagation Delay              | 7   | T <sub>SMCKBY</sub>                      | 12.0      | ns, max  |

|      | Maximum Frequency                   |     | F <sub>CC</sub>                          | 66        | MHz, max |

|      | Maximum Frequency with no handshake |     | F <sub>CCNH</sub>                        | 50        | MHz, max |

Figure 17: Write Operations

A flowchart for the write operation appears in Figure 18. Note that if CCLK is slower than  $f_{CCNH}$ , the FPGA never asserts BUSY, In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

#### Abort

During a given assertion of  $\overline{CS}$ , the user cannot switch from a write to a read, or vice-versa. This action causes the cur-

rent packet command to be aborted. The device remains BUSY until the aborted operation has completed. Following an abort, data is assumed to be unaligned to word boundaries, and the FPGA requires a new synchronization word prior to accepting any new packets.

To initiate an abort during a write operation, de-assert  $\overline{\text{WRITE}}$ . At the rising edge of CCLK, an abort is initiated, as shown in Figure 19.

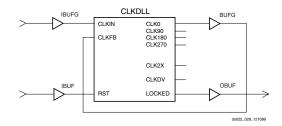

Figure 26: Virtex Series DLLs

# **Design Factors**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

### Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

#### Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL produces an unreliable lock signal and output clock.

It is possible to stop the input clock with little impact to the DLL. Stopping the clock should be limited to less than 100  $\mu s$  to keep device cooling to a minimum. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED stays High and remains High when the clock is restored.

When the clock is stopped, one to four more clocks are still observed as the delay line is flushed. When the clock is restarted, the output clocks are not observed for one to four clocks as the delay line is filled. The most common case is two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift propagates one to four clocks to the output after the original shift, with no disruption to the CLKDLL control.

#### **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or they can route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). In addition, the CLK2X output of the secondary DLL can connect directly to the CLKIN of the primary DLL in the same quadrant.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

# **Useful Application Examples**

The Virtex-E DLL can be used in a variety of creative and useful applications. The following examples show some of the more common applications. The Verilog and VHDL example files are available at:

ftp://ftp.xilinx.com/pub/applications/xapp/xapp132.zip

# Standard Usage

The circuit shown in Figure 27 resembles the BUFGDLL macro implemented to provide access to the RST and LOCKED pins of the CLKDLL.

Figure 27: Standard DLL Implementation

# Board Level De-Skew of Multiple Non-Virtex-E Devices

The circuit shown in Figure 28 can be used to de-skew a system clock between a Virtex-E chip and other non-Virtex-E chips on the same board. This application is commonly used when the Virtex-E device is used in conjunction with other standard products such as SRAM or DRAM devices. While designing the board level route, ensure that the return net delay to the source equals the delay to the other chips involved.

# **Port Signals**

Each block SelectRAM+ port operates independently of the others while accessing the same set of 4096 memory cells.

Table 15 describes the depth and width aspect ratios for the block SelectRAM+ memory.

Table 15: Block SelectRAM+ Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

# Clock—CLK[AIB]

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The data output bus has a clock-to-out time referenced to the CLK pin.

# Enable—EN[A/B]

The enable pin affects the read, write and reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells.

#### Write Enable—WE[A|B]

Activating the write enable pin allows the port to write to the memory cells. When active, the contents of the data input bus are written to the RAM at the address pointed to by the address bus, and the new data also reflects on the data out bus. When inactive, a read operation occurs and the contents of the memory cells referenced by the address bus reflect on the data out bus.

#### Reset—RST[A|B]

The reset pin forces the data output bus latches to zero synchronously. This does not affect the memory cells of the RAM and does not disturb a write operation on the other port.

### Address Bus—ADDR[A|B]<#:0>

The address bus selects the memory cells for read or write. The width of the port determines the required width of this bus as shown in Table 15.

#### Data In Bus-DI[A/B]<#:0>

The data in bus provides the new data value to be written into the RAM. This bus and the port have the same width, as shown in Table 15.

# Data Output Bus-DO[A|B]<#:0>

The data out bus reflects the contents of the memory cells referenced by the address bus at the last active clock edge. During a write operation, the data out bus reflects the data in bus. The width of this bus equals the width of the port. The allowed widths appear in Table 15.

# **Inverting Control Pins**

The four control pins (CLK, EN, WE and RST) for each port have independent inversion control as a configuration option.

# **Address Mapping**

Each port accesses the same set of 4096 memory cells using an addressing scheme dependent on the width of the port. The physical RAM location addressed for a particular width are described in the following formula (of interest only when the two ports use different aspect ratios).

$$Start = ((ADDR_{port} + 1) * Width_{port}) - 1$$

End = ADDR<sub>port</sub> \* Width<sub>port</sub>

Table 16 shows low order address mapping for each port width.

Table 16: Port Address Mapping

| Port  |      | Port   |        |   |        |   |        |        |    |        |   |        |        |   |        |   |   |

|-------|------|--------|--------|---|--------|---|--------|--------|----|--------|---|--------|--------|---|--------|---|---|

| Width |      |        |        |   |        | A | dd     | res    | se | S      |   |        |        |   |        |   |   |

| 1     | 4095 | 1<br>5 | 1<br>4 | 1 | 1<br>2 | 1 | 1<br>0 | 0<br>9 | 0  | 0<br>7 | 0 | 0<br>5 | 0<br>4 | 0 | 0<br>2 | 0 | 0 |

| 2     | 2047 | 0      | 7      | 0 | 6      | 0 | 5      | 0      | 4  | 0      | 3 | 0      | 2      | 0 | 1      | 0 | 0 |

| 4     | 1023 |        | 0      | 3 |        |   | 02 01  |        |    |        |   | 00     |        |   |        |   |   |

| 8     | 511  |        | 01     |   |        |   |        |        |    | 0      | 0 |        |        |   |        |   |   |

| 16    | 255  |        |        |   |        |   |        |        | 0  | 0      |   |        |        |   |        |   |   |

### Creating Larger RAM Structures

The block SelectRAM+ columns have specialized routing to allow cascading blocks together with minimal routing delays. This achieves wider or deeper RAM structures with a smaller timing penalty than when using normal routing channels.

#### **Location Constraints**

Block SelectRAM+ instances can have LOC properties attached to them to constrain the placement. The block SelectRAM+ placement locations are separate from the CLB location naming convention, allowing the LOC properties to transfer easily from array to array.

The LOC properties use the following form.

LOC = RAMB4\_R#C#

RAMB4\_R0C0 is the upper left RAMB4 location on the device.

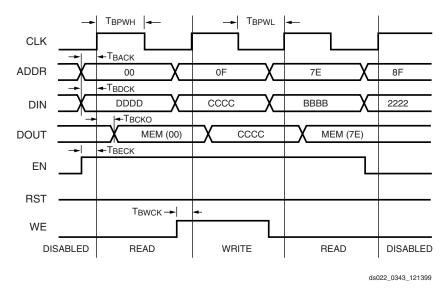

Figure 33: Timing Diagram for Single Port Block SelectRAM+ Memory

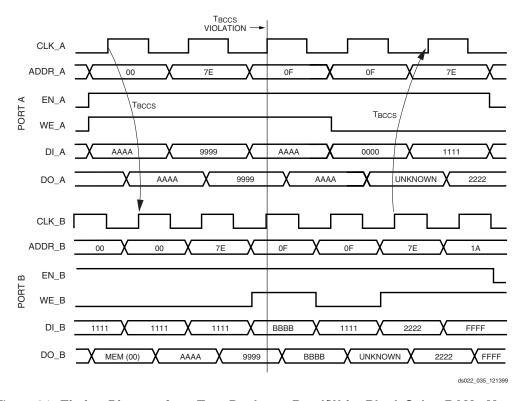

Figure 34: Timing Diagram for a True Dual-port Read/Write Block SelectRAM+ Memory

At the third rising edge of CLKA, the  $T_{BCCS}$  parameter is violated with two writes to memory location 0x0F. The DOA and DOB busses reflect the contents of the DIA and DIB busses, but the stored value at 0x0F is invalid.

At the fourth rising edge of CLKA, a read operation is performed at memory location 0x0F and invalid data is present

on the DOA bus. Port B also executes a read operation to memory location 0x0F and also reads invalid data.

At the fifth rising edge of CLKA a read operation is performed that does not violate the  $T_{BCCS}$  parameter to the previous write of 0x7E by Port B. THe DOA bus reflects the recently written value by Port B.

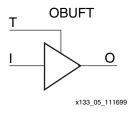

The LVTTL OBUFT additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL 3-state output buffers have selectable drive strengths.

The format for LVTTL OBUFT symbol names is as follows.

<slew\_rate> can be either F (Fast), or S (Slow) and

<drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16,

or 24).

Figure 41: 3-State Output Buffer Symbol (OBUFT)

The following list details variations of the OBUFT symbol.

- OBUFT

- OBUFT S 2

- OBUFT S 4

- OBUFT\_S\_6

- OBUFT\_S\_8

- OBUFT S 12

- OBUFT\_S\_16

- OBUFT S 24

- OBUFT\_F\_2

- OBUFT F 4

- OBUFT\_F\_6

- OBUFT F 8

- OBUFT F 12

- OBUFT F 16

- OBUFT\_F\_24

- OBUFT LVCMOS2

- OBUFT\_PCI33\_3

- OBUFT PCI66 3

- OBUFT GTL

- OBUFT GTLP

- OBUFT HSTL I

- OBUFT\_HSTL\_III

- OBUFT\_HSTL\_IV

- OBUFT\_SSTL3\_I

- OBUFT\_SSTL3\_II

- OBUFT\_SSTL2\_I

- OBUFT\_SSTL2\_II

- OBUFT\_CTT

- OBUFT AGP

- OBUFT\_LVCMOS18

- OBUFT\_LVDS

- OBUFT\_LVPECL

The Virtex-E series supports eight banks for the HQ and PQ packages. The CS package supports four  $V_{CCO}$  banks.

The SelectI/O OBUFT placement restrictions require that within a given  $V_{CCO}$  bank each OBUFT share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank.

The LOC property can specify a location for the OBUFT.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate symbol to the output net of the OBUFT (PULLUP, PULLDOWN, or KEEPER).

The weak "keeper" circuit requires the input buffer within the IOB to sample the I/O signal. So, OBUFTs programmed for an I/O standard that requires a  $V_{REF}$  have automatic placement of a  $V_{REF}$  in the bank with an OBUFT configured with a weak "keeper" circuit. This restriction does not affect most circuit design as applications using an OBUFT configured with a weak "keeper" typically implement a bidirectional I/O. In this case the IBUF (and the corresponding  $V_{REF}$ ) are explicitly placed.

The LOC property can specify a location for the OBUFT.

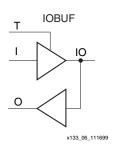

#### **IOBUF**

Use the IOBUF symbol for bidirectional signals that require both an input buffer and a 3-state output buffer with an active high 3-state pin. The generic input/output buffer IOBUF appears in Figure 42.

The extension to the base name defines which I/O standard the IOBUF uses. With no extension specified for the generic IOBUF symbol, the assumed standard is LVTTL input buffer and slew rate limited LVTTL with 12 mA drive strength for the output buffer.

The LVTTL IOBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL bidirectional buffers have selectable output drive strengths.

The format for LVTTL IOBUF symbol names is as follows.

<slew\_rate> can be either F (Fast), or S (Slow) and

<drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16,

or 24).

Figure 42: Input/Output Buffer Symbol (IOBUF)

The following list details variations of the IOBUF symbol.

- IOBUF

- IOBUF S 2

- IOBUF\_S\_4

- IOBUF S 6

- IOBUF\_S\_8

- IOBUF\_S\_12

- IOBUF S 16

- IOBUF\_S\_24

- IOBUF F 2

- IOBUF F 4

- IOBUF\_F\_6

- IOBUF\_F\_8

- IOBUF\_F\_12

- IOBUF\_F\_16

- IOBUF\_F\_24

- IOBUF\_LVCMOS2

- IOBUF PCI33 3

- IOBUF\_PCI66\_3

- IOBUF\_GTL

- IOBUF GTLP

- IOBUF\_HSTL\_I

- IOBUF\_HSTL\_III

- IOBUF\_HSTL\_IV

- IOBUF\_SSTL3\_I

- IOBUF\_SSTL3\_II

- IOBUF\_SSTL2\_I

- IOBUF\_SSTL2\_II

- IOBUF\_CTT

- IOBUF\_AGP

- IOBUF\_LVCMOS18

- IOBUF\_LVDS

- IOBUF\_LVPECL

When the IOBUF symbol used supports an I/O standard that requires a differential amplifier input, the IOBUF automatically configures with a differential amplifier input buffer. The low-voltage I/O standards with a differential amplifier input require an external reference voltage input  $V_{\rm REF}$

The voltage reference signal is "banked" within the Virtex-E device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 38 on page 34 for a representation of the Virtex-E I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input. After placing a differential amplifier input signal within a given  $V_{REF}$  bank, the same external source must drive all I/O pins configured as a  $V_{REF}$  input.

IOBUF placement restrictions require any differential amplifier input signals within a bank be of the same standard.

The Virtex-E series supports eight banks for the HQ and PQ packages. The CS package supports four V<sub>CCO</sub> banks.

Additional restrictions on the Virtex-E SelectI/O IOBUF placement require that within a given  $V_{CCO}$  bank each IOBUF must share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank. The LOC property can specify a location for the IOBUF.

An optional delay element is associated with the input path in each IOBUF. When the IOBUF drives an input flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Override this default with the NODELAY=TRUE property.

In the case when the IOBUF does not drive an input flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate symbol to the output net of the IOBUF (PULLUP, PULLDOWN, or KEEPER).

### **SelectI/O Properties**

Access to some of the Selectl/O features (for example, location constraints, input delay, output drive strength, and slew rate) is available through properties associated with these features.

#### Input Delay Properties

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Use the NODELAY=TRUE property to override this default.

In the case when the IBUF does not drive a flip-flop within the IOB, the delay element by default de-activates to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

# **Creating LVDS Output Buffers**

LVDS output buffer can be placed in wide number of IOB locations. The exact location are dependent on the package that is used. The Virtex-E package information lists the possible locations as IO\_L#P for the P-side and IO\_L#N for the N-side where # is the pair number.

#### HDL Instantiation

Both output buffers are required to be instantiated in the design and placed on the correct IO\_L#P and IO\_L#N locations. The IOB must have the same net source the following pins, clock (C), set/reset (SR), output (O), output clock enable (OCE). In addition, the output (O) pins must be inverted with respect to each other, and if output registers are used, the INIT states must be opposite values (one HIGH and one LOW). Failure to follow these rules leads to DRC errors in software.

#### **VHDL** Instantiation

#### **Verilog Instantiation**

#### **Location Constraints**

All LVDS buffers must be explicitly placed on a device. For the output buffers this can be done with the following constraint in the UCF or NCF file.

```

NET data_p<0> LOC = D28; # IO_LOP

NET data n<0> LOC = B29; # IO LON

```

#### Synchronous vs. Asynchronous Outputs

If the outputs are synchronous (registered in the IOB), then any IO\_L#PIN pair can be used. If the outputs are asynchronous (no output register), then they must use one of the pairs that are part of the same IOB group at the end of a ROW or at the top/bottom of a COLUMN in the device.

The LVDS pairs that can be used as asynchronous outputs are listed in the Virtex-E pinout tables. Some pairs are marked as asynchronous-capable for all devices in that package, and others are marked as available only for that device in the package. If the device size might change at

some point in the product lifetime, then only the common pairs for all packages should be used.

#### Adding an Output Register

All LVDS buffers can have an output register in the IOB. The output registers must be in both the P-side and N-side IOBs. All the normal IOB register options are available (FD, FDE, FDC, FDCE, FDP, FDPE, FDR, FDRE, FDS, FDSE, LD, LDE, LDC, LDCE, LDP, LDPE). The register elements can be inferred or explicitly instantiated in the HDL code.

Special care must be taken to insure that the D pins of the registers are inverted and that the INIT states of the registers are opposite. The clock pin (C), clock enable (CE) and set/reset (CLR/PRE or S/R) pins must connect to the same source. Failure to do this leads to a DRC error in the software.

The register elements can be packed in the IOB using the IOB property to TRUE on the register or by using the "map-pr [ilolb]" where "i" is inputs only, "o" is outputs only and "b" is both inputs and outputs.

To improve design coding times VHDL and Verilog synthesis macro libraries have been developed to explicitly create these structures. The output library macros are listed in Table 43. The O and OB inputs to the macros are the external net connections.

Table 43: Output Library Macros

| Name             | Inputs        | Outputs |

|------------------|---------------|---------|

| OBUFDS_FD_LVDS   | D, C          | O, OB   |

| OBUFDS_FDE_LVDS  | DD, CE, C     | O, OB   |

| OBUFDS_FDC_LVDS  | D, C, CLR     | O, OB   |

| OBUFDS_FDCE_LVDS | D, CE, C, CLR | O, OB   |

| OBUFDS_FDP_LVDS  | D, C, PRE     | O, OB   |

| OBUFDS_FDPE_LVDS | D, CE, C, PRE | O, OB   |

| OBUFDS_FDR_LVDS  | D, C, R       | O, OB   |

| OBUFDS_FDRE_LVDS | D, CE, C, R   | O, OB   |

| OBUFDS_FDS_LVDS  | D, C, S       | O, OB   |

| OBUFDS_FDSE_LVDS | D, CE, C, S   | O, OB   |

| OBUFDS_LD_LVDS   | D, G          | O, OB   |

| OBUFDS_LDE_LVDS  | D, GE, G      | O, OB   |

| OBUFDS_LDC_LVDS  | D, G, CLR     | O, OB   |

| OBUFDS_LDCE_LVDS | D, GE, G, CLR | O, OB   |

| OBUFDS_LDP_LVDS  | D, G, PRE     | O, OB   |

| OBUFDS_LDPE_LVDS | D, GE, G, PRE | O, OB   |

# **IOB Input Switching Characteristics Standard Adjustments**

|                                    |                        |                    |       | Speed | Grade <sup>(1)</sup> |       |       |

|------------------------------------|------------------------|--------------------|-------|-------|----------------------|-------|-------|

| Description                        | Symbol                 | Standard           | Min   | -8    | -7                   | -6    | Units |

| Data Input Delay Adjustments       |                        |                    |       |       |                      |       |       |

| Standard-specific data input delay | T <sub>ILVTTL</sub>    | LVTTL              | 0.0   | 0.0   | 0.0                  | 0.0   | ns    |

| adjustments                        | T <sub>ILVCMOS2</sub>  | LVCMOS2            | -0.02 | 0.0   | 0.0                  | 0.0   | ns    |

|                                    | T <sub>ILVCMOS18</sub> | LVCMOS18           | -0.02 | +0.20 | +0.20                | +0.20 | ns    |

|                                    | T <sub>ILVDS</sub>     | LVDS               | 0.00  | +0.15 | +0.15                | +0.15 | ns    |

|                                    | T <sub>ILVPECL</sub>   | LVPECL             | 0.00  | +0.15 | +0.15                | +0.15 | ns    |

|                                    | T <sub>IPCl33_3</sub>  | PCI, 33 MHz, 3.3 V | -0.05 | +0.08 | +0.08                | +0.08 | ns    |

|                                    | T <sub>IPCI66_3</sub>  | PCI, 66 MHz, 3.3 V | -0.05 | -0.11 | -0.11                | -0.11 | ns    |

|                                    | T <sub>IGTL</sub>      | GTL                | +0.10 | +0.14 | +0.14                | +0.14 | ns    |

|                                    | T <sub>IGTLPLUS</sub>  | GTL+               | +0.06 | +0.14 | +0.14                | +0.14 | ns    |

|                                    | T <sub>IHSTL</sub>     | HSTL               | +0.02 | +0.04 | +0.04                | +0.04 | ns    |

|                                    | T <sub>ISSTL2</sub>    | SSTL2              | -0.04 | +0.04 | +0.04                | +0.04 | ns    |

|                                    | T <sub>ISSTL3</sub>    | SSTL3              | -0.02 | +0.04 | +0.04                | +0.04 | ns    |

|                                    | T <sub>ICTT</sub>      | CTT                | +0.01 | +0.10 | +0.10                | +0.10 | ns    |

|                                    | T <sub>IAGP</sub>      | AGP                | -0.03 | +0.04 | +0.04                | +0.04 | ns    |

#### Notes:

1

<sup>1.</sup> Input timing i for LVTTL is measured at 1.4 V. For other I/O standards, see Table 3.

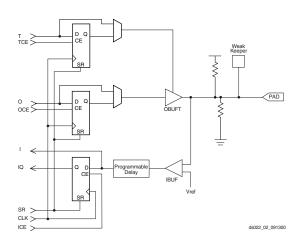

Figure 1: Virtex-E Input/Output Block (IOB)

# **IOB Output Switching Characteristics Standard Adjustments**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown.

|                                                                       |                         |                    |       | Speed | Grade    |          |       |

|-----------------------------------------------------------------------|-------------------------|--------------------|-------|-------|----------|----------|-------|

| Description                                                           | Symbol                  | Standard           | Min   | -8    | -7       | -6       | Units |

| Output Delay Adjustments                                              |                         |                    |       |       | <u>'</u> | <u> </u> |       |

| Standard-specific adjustments for                                     | T <sub>OLVTTL_S2</sub>  | LVTTL, Slow, 2 mA  | 4.2   | +14.7 | +14.7    | +14.7    | ns    |

| output delays terminating at pads (based on standard capacitive load, | T <sub>OLVTTL_S4</sub>  | 4 mA               | 2.5   | +7.5  | +7.5     | +7.5     | ns    |

| Csl)                                                                  | T <sub>OLVTTL_S6</sub>  | 6 mA               | 1.8   | +4.8  | +4.8     | +4.8     | ns    |

|                                                                       | T <sub>OLVTTL_S8</sub>  | 8 mA               | 1.2   | +3.0  | +3.0     | +3.0     | ns    |

|                                                                       | T <sub>OLVTTL_S12</sub> | 12 mA              | 1.0   | +1.9  | +1.9     | +1.9     | ns    |

|                                                                       | T <sub>OLVTTL_S16</sub> | 16 mA              | 0.9   | +1.7  | +1.7     | +1.7     | ns    |

|                                                                       | T <sub>OLVTTL_S24</sub> | 24 mA              | 0.8   | +1.3  | +1.3     | +1.3     | ns    |

|                                                                       | T <sub>OLVTTL_F2</sub>  | LVTTL, Fast, 2 mA  | 1.9   | +13.1 | +13.1    | +13.1    | ns    |

|                                                                       | T <sub>OLVTTL_F4</sub>  | 4 mA               | 0.7   | +5.3  | +5.3     | +5.3     | ns    |

|                                                                       | T <sub>OLVTTL_F6</sub>  | 6 mA               | 0.20  | +3.1  | +3.1     | +3.1     | ns    |

|                                                                       | T <sub>OLVTTL_F8</sub>  | 8 mA               | 0.10  | +1.0  | +1.0     | +1.0     | ns    |

|                                                                       | T <sub>OLVTTL_F12</sub> | 12 mA              | 0.0   | 0.0   | 0.0      | 0.0      | ns    |

|                                                                       | T <sub>OLVTTL_F16</sub> | 16 mA              | -0.10 | -0.05 | -0.05    | -0.05    | ns    |

|                                                                       | T <sub>OLVTTL_F24</sub> | 24 mA              | -0.10 | -0.20 | -0.20    | -0.20    | ns    |

|                                                                       | T <sub>OLVCMOS_2</sub>  | LVCMOS2            | 0.10  | +0.09 | +0.09    | +0.09    | ns    |

|                                                                       | T <sub>OLVCMOS_18</sub> | LVCMOS18           | 0.10  | +0.7  | +0.7     | +0.7     | ns    |

|                                                                       | T <sub>OLVDS</sub>      | LVDS               | -0.39 | -1.2  | -1.2     | -1.2     | ns    |

|                                                                       | T <sub>OLVPECL</sub>    | LVPECL             | -0.20 | -0.41 | -0.41    | -0.41    | ns    |

|                                                                       | T <sub>OPCI33_3</sub>   | PCI, 33 MHz, 3.3 V | 0.50  | +2.3  | +2.3     | +2.3     | ns    |

|                                                                       | T <sub>OPCI66_3</sub>   | PCI, 66 MHz, 3.3 V | 0.10  | -0.41 | -0.41    | -0.41    | ns    |

|                                                                       | T <sub>OGTL</sub>       | GTL                | 0.6   | +0.49 | +0.49    | +0.49    | ns    |

|                                                                       | T <sub>OGTLP</sub>      | GTL+               | 0.7   | +0.8  | +0.8     | +0.8     | ns    |

|                                                                       | T <sub>OHSTL_I</sub>    | HSTL I             | 0.10  | -0.51 | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OHSTL_IIII</sub> | HSTL III           | -0.10 | -0.91 | -0.91    | -0.91    | ns    |

|                                                                       | T <sub>OHSTL_IV</sub>   | HSTL IV            | -0.20 | -1.01 | -1.01    | -1.01    | ns    |

|                                                                       | T <sub>OSSTL2_I</sub>   | SSTL2 I            | -0.10 | -0.51 | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OSSTL2_II</sub>  | SSTL2 II           | -0.20 | -0.91 | -0.91    | -0.91    | ns    |

|                                                                       | T <sub>OSSTL3_I</sub>   | SSTL3 I            | -0.20 | -0.51 | -0.51    | -0.51    | ns    |

|                                                                       | T <sub>OSSTL3_II</sub>  | SSTL3 II           | -0.30 | -1.01 | -1.01    | -1.01    | ns    |

|                                                                       | T <sub>OCTT</sub>       | CTT                | 0.0   | -0.61 | -0.61    | -0.61    | ns    |

|                                                                       | T <sub>OAGP</sub>       | AGP                | -0.1  | -0.91 | -0.91    | -0.91    | ns    |

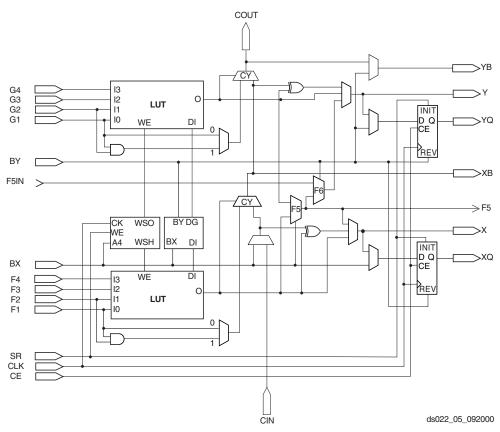

Figure 2: Detailed View of Virtex-E Slice

# **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                             |                                      |          | Speed    | Grade   |         |         |

|---------------------------------------------|--------------------------------------|----------|----------|---------|---------|---------|

| Description <sup>(1)</sup>                  | Symbol                               | Min      | -8       | -7      | -6      | Units   |

| Combinatorial Delays                        |                                      |          |          |         |         |         |

| F operand inputs to X via XOR               | T <sub>OPX</sub>                     | 0.32     | 0.68     | 0.8     | 0.8     | ns, max |

| F operand input to XB output                | T <sub>OPXB</sub>                    | 0.35     | 0.65     | 0.8     | 0.9     | ns, max |

| F operand input to Y via XOR                | T <sub>OPY</sub>                     | 0.59     | 1.07     | 1.4     | 1.5     | ns, max |

| F operand input to YB output                | T <sub>OPYB</sub>                    | 0.48     | 0.89     | 1.1     | 1.3     | ns, max |

| F operand input to COUT output              | T <sub>OPCYF</sub>                   | 0.37     | 0.71     | 0.9     | 1.0     | ns, max |

| G operand inputs to Y via XOR               | T <sub>OPGY</sub>                    | 0.34     | 0.72     | 0.8     | 0.9     | ns, max |

| G operand input to YB output                | T <sub>OPGYB</sub>                   | 0.47     | 0.78     | 1.2     | 1.3     | ns, max |

| G operand input to COUT output              | T <sub>OPCYG</sub>                   | 0.36     | 0.60     | 0.9     | 1.0     | ns, max |

| BX initialization input to COUT             | T <sub>BXCY</sub>                    | 0.19     | 0.36     | 0.51    | 0.57    | ns, max |

| CIN input to X output via XOR               | T <sub>CINX</sub>                    | 0.27     | 0.50     | 0.6     | 0.7     | ns, max |

| CIN input to XB                             | T <sub>CINXB</sub>                   | 0.02     | 0.04     | 0.07    | 0.08    | ns, max |

| CIN input to Y via XOR                      | T <sub>CINY</sub>                    | 0.26     | 0.45     | 0.7     | 0.7     | ns, max |

| CIN input to YB                             | T <sub>CINYB</sub>                   | 0.16     | 0.28     | 0.38    | 0.43    | ns, max |

| CIN input to COUT output                    | T <sub>BYP</sub>                     | 0.05     | 0.10     | 0.14    | 0.15    | ns, max |

| Multiplier Operation                        |                                      |          |          |         |         |         |

| F1/2 operand inputs to XB output via AND    | T <sub>FANDXB</sub>                  | 0.10     | 0.30     | 0.35    | 0.39    | ns, max |

| F1/2 operand inputs to YB output via AND    | T <sub>FANDYB</sub>                  | 0.28     | 0.56     | 0.7     | 0.8     | ns, max |

| F1/2 operand inputs to COUT output via AND  | T <sub>FANDCY</sub>                  | 0.17     | 0.38     | 0.46    | 0.51    | ns, max |

| G1/2 operand inputs to YB output via AND    | T <sub>GANDYB</sub>                  | 0.20     | 0.46     | 0.55    | 0.7     | ns, max |

| G1/2 operand inputs to COUT output via AND  | T <sub>GANDCY</sub>                  | 0.09     | 0.28     | 0.30    | 0.34    | ns, max |

| Setup and Hold Times before/after Clock CLK |                                      | _        |          |         | •       |         |

| CIN input to FFX                            | T <sub>CCKX</sub> /T <sub>CKCX</sub> | 0.47 / 0 | 1.0 / 0  | 1.2 / 0 | 1.3 / 0 | ns, min |

| CIN input to FFY                            | T <sub>CCKY</sub> /T <sub>CKCY</sub> | 0.49 / 0 | 0.92 / 0 | 1.2 / 0 | 1.3 / 0 | ns, min |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

# **Virtex-E Pin-to-Pin Input Parameter Guidelines**

All devices are 100% functionally tested. Listed below are representative values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted.

# Global Clock Set-Up and Hold for LVTTL Standard, with DLL

| Description <sup>(1)</sup>                                                                                                                                        | Symbol                                 | Device <sup>(3)</sup> | Min        | -8         | -7         | -6         | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------|------------|------------|------------|------------|-------|

| Input Setup and Hold Time Rela for LVTTL Standard.                                                                                                                |                                        |                       |            |            |            |            |       |

| For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Switching Characteristics Standard Adjustments" on page 6. |                                        |                       |            |            |            |            |       |

| No Delay                                                                                                                                                          | T <sub>PSDLL</sub> /T <sub>PHDLL</sub> | XCV405E               | 1.5 / -0.4 | 1.5 / -0.4 | 1.6 / -0.4 | 1.7 / -0.4 | ns    |

| Global Clock and IFF, with DLL                                                                                                                                    |                                        | XCV812E               | 1.5 / -0.4 | 1.5 / -0.4 | 1.6 / -0.4 | 1.7 / -0.4 | ns    |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. DLL output jitter is already included in the timing calculation.

# Global Clock Set-Up and Hold for LVTTL Standard, without DLL

|                                                                                                                                                                   |                                      |                       |         | Speed Grade <sup>(2)</sup> |         |         |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|---------|----------------------------|---------|---------|-------|--|--|

| Description <sup>(1)</sup>                                                                                                                                        | Symbol                               | Device <sup>(3)</sup> | Min     | -8                         | -7      | -6      | Units |  |  |

| Input Setup and Hold Time Relative for LVTTL Standard.                                                                                                            |                                      |                       |         |                            |         |         |       |  |  |

| For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Switching Characteristics Standard Adjustments" on page 6. |                                      |                       |         |                            |         |         |       |  |  |

| Full Delay                                                                                                                                                        | T <sub>PSFD</sub> /T <sub>PHFD</sub> | XCV405E               | 2.3 / 0 | 2.3 / 0                    | 2.3 / 0 | 2.3 / 0 | ns    |  |  |

| Global Clock and IFF, without DLL                                                                                                                                 |                                      | XCV812E               | 2.5 / 0 | 2.5 / 0                    | 2.5 / 0 | 2.5 / 0 | ns    |  |  |

#### Notes:

- IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

### **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                                  |                    |                    |     |     | Speed | Grade |     |     |       |

|----------------------------------|--------------------|--------------------|-----|-----|-------|-------|-----|-----|-------|

|                                  |                    |                    | -   | -8  | -     | ·7    | -   | 6   |       |

| Description                      | Symbol             | F <sub>CLKIN</sub> | Min | Max | Min   | Max   | Min | Max | Units |

| Input Clock Frequency (CLKDLLHF) | FCLKINHF           |                    | 60  | 320 | 60    | 320   | 60  | 260 | MHz   |

| Input Clock Frequency (CLKDLL)   | FCLKINLF           |                    | 25  | 160 | 25    | 160   | 25  | 135 | MHz   |

| Input Clock Low/High Pulse Width | T <sub>DLLPW</sub> | ≥25 MHz            | 5.0 |     | 5.0   |       | 5.0 |     | ns    |

|                                  |                    | ≥50 MHz            | 3.0 |     | 3.0   |       | 3.0 |     | ns    |

|                                  |                    | ≥100 MHz           | 2.4 |     | 2.4   |       | 2.4 |     | ns    |

|                                  |                    | ≥150 MHz           | 2.0 |     | 2.0   |       | 2.0 |     | ns    |

|                                  |                    | ≥200 MHz           | 1.8 |     | 1.8   |       | 1.8 |     | ns    |

|                                  |                    | ≥250 MHz           | 1.5 |     | 1.5   |       | 1.5 |     | ns    |

|                                  |                    | ≥300 MHz           | 1.3 |     | 1.3   |       | NA  |     | ns    |

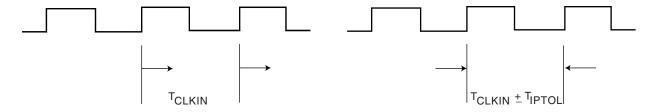

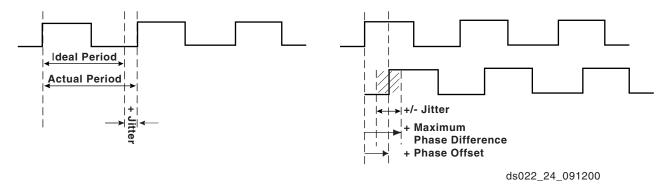

Period Tolerance: the allowed input clock period change in nanoseconds.

**Output Jitter:** the difference between an ideal reference clock edge and the actual design.

Phase Offset and Maximum Phase Difference

Figure 4: DLL Timing Waveforms

| Date     | Version | Revision                                                                                                                                                              |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/20/00 | 1.3     | <ul> <li>Updated speed grade -8 numbers in Virtex-E Electrical Characteristics tables<br/>(Module 3).</li> </ul>                                                      |

|          |         | <ul> <li>Updated minimums in Table 11 (Module 2), and added notes to Table 12 (Module 2).</li> </ul>                                                                  |

|          |         | <ul> <li>Added to note 2 of Absolute Maximum Ratings (Module 3).</li> </ul>                                                                                           |

|          |         | • Changed all minimum hold times to -0.4 for Global Clock Set-Up and Hold for LVTTL Standard, with DLL (Module 3).                                                    |

|          |         | <ul> <li>Revised maximum T<sub>DLLPW</sub> in -6 speed grade for <b>DLL Timing Parameters</b> (Module 3).</li> </ul>                                                  |

| 04/02/01 | 1.4     | <ul> <li>In Table 4, FG676 Fine-Pitch BGA — XCV405E, pin B19 is no longer labeled as VREF,<br/>and pin G16 is now labeled as VREF.</li> </ul>                         |

|          |         | <ul> <li>Updated values in Virtex-E Switching Characteristics tables.</li> </ul>                                                                                      |

|          |         | <ul> <li>Converted data sheet to modularized format. See the Virtex-E Extended Memory Data<br/>Sheet section.</li> </ul>                                              |

| 04/19/01 | 1.5     | Updated values in Virtex-E Switching Characteristics tables.                                                                                                          |

| 07/23/01 | 1.6     | <ul> <li>Under Absolute Maximum Ratings, changed (T<sub>SOL</sub>) to 220 °C.</li> </ul>                                                                              |

|          |         | <ul> <li>Changes made to SSTL symbol names in IOB Input Switching Characteristics Standard<br/>Adjustments table.</li> </ul>                                          |

| 07/26/01 | 1.7     | <ul> <li>Removed T<sub>SOL</sub> parameter and added footnote to Absolute Maximum Ratings table.</li> </ul>                                                           |

| 09/18/01 | 1.8     | Reworded power supplies footnote to Absolute Maximum Ratings table.                                                                                                   |

| 10/25/01 | 1.9     | <ul> <li>Updated the speed grade designations used in data sheets, and added Table 1, which<br/>shows the current speed grade designation for each device.</li> </ul> |

|          |         | Updated Power-On Power Supply Requirements table.                                                                                                                     |

| 11/09/01 | 2.0     | <ul> <li>Updated the XCV405E device speed grade designation to Preliminary in Table 1.</li> </ul>                                                                     |

|          |         | <ul> <li>Updated Power-On Power Supply Requirements table.</li> </ul>                                                                                                 |

| 02/01/02 | 2.1     | <ul> <li>Updated footnotes to the DC Input and Output Levels and DLL Clock Tolerance, Jitter,<br/>and Phase Information tables.</li> </ul>                            |

| 07/17/02 | 2.2     | <ul> <li>Data sheet designation upgraded from Preliminary to Production.</li> </ul>                                                                                   |

|          |         | <ul> <li>Removed mention of MIL-M-38510/605 specification.</li> </ul>                                                                                                 |

|          |         | <ul> <li>Added link to XAPP158 from the Power-On Power Supply Requirements section.</li> </ul>                                                                        |

| 09/10/02 | 2.3     | <ul> <li>Revised V<sub>IN</sub> in Absolute Maximum Ratings Table. Added Clock CLK switching</li> </ul>                                                               |

|          |         | characteristics to "IOB Input Switching Characteristics" on page 5 and "IOB Output                                                                                    |

| 10/00/20 | 0.0.4   | Switching Characteristics, Figure 1" on page 7.  Added footnote regarding V <sub>IN</sub> PCI compliance to Absolute Maximum Batings table.                           |

| 12/22/02 | 2.3.1   | , lades leed legal along V <sub>III</sub> 1 e. demphalies to Absolute Marine I talings table.                                                                         |

| 03/14/03 | 2.3.2   | <ul> <li>Under Power-On Power Supply Requirements, the fastest ramp rate is no longer a<br/>"suggested" rate.</li> </ul>                                              |

# **Virtex-E Extended Memory Data Sheet**

The Virtex-E Extended Memory Data Sheet contains the following modules:

- DS025-1, Virtex-E 1.8V Extended Memory FPGAs: Introduction and Ordering Information (Module 1)

- DS025-2, Virtex-E 1.8V Extended Memory FPGAs: <u>Functional Description (Module 2)</u>

- DS025-3, Virtex-E 1.8V Extended Memory FPGAs:

DC and Switching Characteristics (Module 3)

- DS025-4, Virtex-E 1.8V Extended Memory FPGAs: <u>Pinout Tables (Module 4)</u>

#### **BG560 Package Differential Pin Pair Summary** Table 2: XCV405E and XCV812E

| 50 | 2 | H5  | E2  | NA | -      |

|----|---|-----|-----|----|--------|

| 51 | 2 | H4  | G3  | √  | VREF_2 |

| 52 | 2 | J5  | F1  | NA | -      |

| 53 | 2 | J4  | НЗ  | 2  | -      |

| 54 | 2 | K5  | H2  | NA | VREF_2 |

| 55 | 2 | J3  | K4  | NA | -      |

| 56 | 2 | L5  | КЗ  | √  | D1     |

| 57 | 2 | L4  | K2  | √  | D2     |

| 58 | 2 | M5  | L3  | 2  | -      |

| 59 | 2 | L1  | M4  | NA | -      |

| 60 | 2 | N5  | M2  | 1  | VREF_2 |

| 61 | 2 | N4  | N3  | 1  | -      |

| 62 | 2 | N2  | P5  | NA | -      |

| 63 | 2 | P4  | P3  | √  | D3     |

| 64 | 2 | P2  | R5  | 2  | -      |

| 65 | 2 | R4  | R3  | NA | -      |

| 66 | 2 | R1  | T4  | NA | VREF_2 |

| 67 | 2 | T5  | ТЗ  | NA | -      |

| 68 | 2 | T2  | U3  | √  | IRDY   |

| 69 | 3 | U1  | U2  | NA | -      |

| 70 | 3 | V2  | V4  | NA | VREF_3 |

| 71 | 3 | V5  | V3  | NA | -      |

| 72 | 3 | W1  | W3  | 2  | -      |

| 73 | 3 | W4  | W5  | √  | VREF_3 |

| 74 | 3 | Y3  | Y4  | NA | -      |

| 75 | 3 | AA1 | Y5  | 1  | -      |

| 76 | 3 | AA3 | AA4 | 1  | VREF_3 |

| 77 | 3 | AB3 | AA5 | NA | -      |

| 78 | 3 | AC1 | AB4 | 2  | -      |

| 79 | 3 | AC3 | AB5 | √  | D5     |

| 80 | 3 | AC4 | AD3 | √  | VREF_3 |

| 81 | 3 | AE1 | AC5 | 1  | -      |

| 82 | 3 | AD4 | AF1 | NA | VREF_3 |

| 83 | 3 | AF2 | AD5 | NA | -      |

**BG560 Package Differential Pin Pair Summary** Table 2: XCV405E and XCV812E

| 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   |      |      |    |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|------|------|----|---------------|

| 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84  | 3 | AG2  | AE4  | NA | -             |

| 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85  | 3 | AH1  | AE5  | √  | VREF_3        |

| 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86  | 3 | AF4  | AJ1  | NA | -             |

| 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87  | 3 | AJ2  | AF5  | 2  | -             |

| 90 3 AL1 AH4 NA - 91 3 AJ4 AH5 √ INIT 92 4 AL4 AJ6 √ - 93 4 AK5 AN3 NA - 94 4 AL5 AJ7 √ - 95 4 AM4 AM5 √ VREF_4 96 4 AK7 AL6 1 - 97 4 AM6 AN6 √ - 98 4 AL7 AJ9 √ VREF_4 99 4 AN7 AL8 NA - 100 4 AM8 AJ10 1 - 101 4 AL9 AM9 1 VREF_4 102 4 AK10 AN9 1 - 103 4 AL11 AJ12 √ - 105 4 AN11 AK12 NA - 106 4 AL12 AM12 √ - 107 4 AK13 AL13 √ VREF_4 108 4 AM13 AN13 1 - 109 4 AJ14 AK14 √ - 110 4 AM14 AN15 √ VREF_4 111 4 AJ15 AK15 NA - 112 4 AL16 AJ16 1 VREF_4 113 4 AL16 AJ16 1 VREF_4 114 4 AK16 AN17 1 - 115 5 AM17 AM18 NA GCLK LVDS 1/0 116 5 AK18 AJ18 1 VREF_5                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 88  | 3 | AG4  | AK2  | 1  | VREF_3        |

| 91 3 AJ4 AH5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89  | 3 | AJ3  | AG5  | NA | -             |

| 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90  | 3 | AL1  | AH4  | NA | -             |

| 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91  | 3 | AJ4  | AH5  | √  | INIT          |

| 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92  | 4 | AL4  | AJ6  | √  | -             |

| 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93  | 4 | AK5  | AN3  | NA | -             |

| 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94  | 4 | AL5  | AJ7  | √  | -             |

| 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95  | 4 | AM4  | AM5  | √  | VREF_4        |

| 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96  | 4 | AK7  | AL6  | 1  | -             |

| 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97  | 4 | AM6  | AN6  | √  | -             |