# E·XFL

#### NXP USA Inc. - MKM34Z256VLL7R Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 75MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | DMA, LCD, WDT                                                          |

| Number of I/O              | 72                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 12x16b, 4x24b                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkm34z256vll7r |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Timers

- Quad Timer (QTMR)

- Periodic Interrupt Timer (PIT)

- Low Power Timer (LPTMR)

- Programmable Delay Block (PDB)

- Independent Real Time Clock (iRTC)

#### Human-machine interface

- Up to 4×60 (8×56, 6×58) segment LCD controller operating in all low-power modes

- General purpose input/output (GPIO)

#### Security and integrity modules

- Memory Mapped Cryptographic Acceleration Unit (MMCAU) for AES encryption

- Random Number Generator (RNGA), complying with NIST: SP800-90

- Programmable Cyclic Redundancy Check (PCRC)

- 80-bit unique identification number per chip

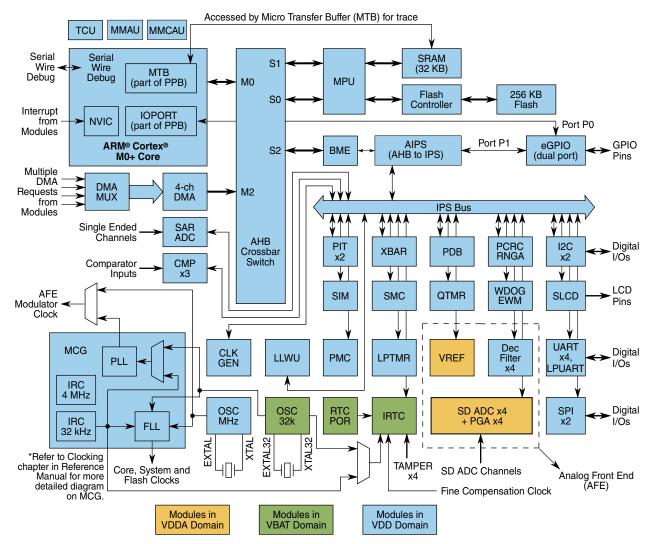

The following figure shows the functional modules in the chip.

## **1.4 Voltage and current operating ratings**

| Symbol               | Description                                                               | Min.                  | Max.                   | Unit |

|----------------------|---------------------------------------------------------------------------|-----------------------|------------------------|------|

| V <sub>DD</sub>      | Digital supply voltage                                                    | -0.3                  | 3.6                    | V    |

| V <sub>DIO</sub>     | Digital input voltage (except RESET, EXTAL, and XTAL)                     | -0.3                  | V <sub>DD</sub> + 0.3  | V    |

| V <sub>DTamper</sub> | Tamper input voltage                                                      | -0.3                  | V <sub>BAT</sub> + 0.3 | V    |

| V <sub>AIO</sub>     | Analog <sup>1</sup> , RESET, EXTAL, and XTAL input voltage                | -0.3                  | V <sub>DD</sub> + 0.3  | V    |

| I <sub>D</sub>       | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                     | mA   |

| V <sub>DDA</sub>     | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3  | V    |

| V <sub>BAT</sub>     | RTC battery supply voltage                                                | -0.3                  | 3.6                    | V    |

1. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

## 2 General

## 2.1 AC electrical characteristics

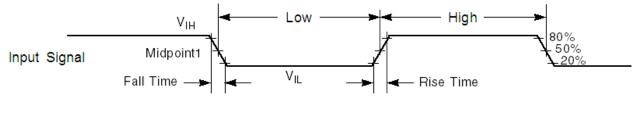

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH}-V_{IL})/2.$

Figure 2. Input signal measurement reference

## 2.2 Nonswitching electrical specifications

| Symbol             | Description                                                  | Min. | Тур. | Max. | Unit | Notes |

|--------------------|--------------------------------------------------------------|------|------|------|------|-------|

| V <sub>LVDH</sub>  | Falling low-voltage detect threshold — high range (LVDV=01)  | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                  |      |      |      |      | 1     |

| $V_{LVW1H}$        | Level 1 falling (LVWV=00)                                    | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | Level 2 falling (LVWV=01)                                    | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | Level 3 falling (LVWV=10)                                    | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{\rm LVW4H}$    | Level 4 falling (LVWV=11)                                    | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | SH Low-voltage inhibit reset/recover hysteresis — high range |      | 80   | -    | mV   |       |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00)   | 1.54 | 1.60 | 1.66 | V    |       |

|                    | Low-voltage warning thresholds — low range                   |      |      |      |      | 1     |

| $V_{LVW1L}$        | Level 1 falling (LVWV=00)                                    | 1.74 | 1.80 | 1.86 | V    |       |

| $V_{LVW2L}$        | Level 2 falling (LVWV=01)                                    | 1.84 | 1.90 | 1.96 | V    |       |

| V <sub>LVW3L</sub> | Level 3 falling (LVWV=10)                                    | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$        | Level 4 falling (LVWV=11)                                    | 2.04 | 2.10 | 2.16 | V    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range     | —    | 60   | -    | mV   |       |

| $V_{BG}$           | Bandgap voltage reference                                    | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed       | 900  | 1000 | 1100 | μs   |       |

### Table 2. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising threshold is the sum of falling threshold and hysteresis voltage

#### Table 3. VBAT power operating requirements

| Symbol                | Description                            | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------|------|------|------|------|-------|

| V <sub>POR_VBAT</sub> | Falling VBAT supply POR detect voltage | 0.8  | 1.1  | 1.5  | V    |       |

## 2.2.3 Voltage and current operating behaviors

| Table 4. | Voltage and current operating behaviors |  |

|----------|-----------------------------------------|--|

|----------|-----------------------------------------|--|

| Symbol           | Description                                                                                           | Min.                  | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------------|------|------|-------|

| V <sub>OH</sub>  | Output high voltage — low-drive strength                                                              |                       |      |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = 5 mA                                   | $V_{DD} - 0.5$        | —    | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = 2.5 \text{ mA}$ | V <sub>DD</sub> – 0.5 | _    | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                                               | —                     | 100  | mA   |       |

| Symbol               | Description                                                             | Min. | Тур. | Max. | Unit | Notes |

|----------------------|-------------------------------------------------------------------------|------|------|------|------|-------|

|                      | • −40 °C<br>• 105 °C                                                    | _    | 6.05 | 15   | μA   |       |

| I <sub>DD_VBAT</sub> | Average current when VDD is OFF and LFSR and Tamper clocks set to 2 Hz. |      |      |      |      | 7, 8  |

|                      | • @ 3.0 V<br>• 25 °C                                                    | _    | 1.42 | 3    | μA   |       |

|                      | • -40 °C                                                                |      | 1.24 | 2.5  | μA   |       |

|                      | • 105 °C                                                                |      | 8.04 | 16   | μA   |       |

Table 6. Power consumption operating behaviors (continued)

- 1. See AFE specification for  $I_{DDA}$ .

- 75 MHz core and system clock, 25 MHz bus clock, and 25 MHz flash clock. MCG configured for FBE mode. All peripheral clocks disabled.

- 3. Should be reduced by 500  $\mu A.$

- 4. 2 MHz core/system clock, and 1 MHz bus/flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing while (1) loop from flash.

- 5. 2 MHz core/system clock, and 1 MHz bus/flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing while (1) loop from flash.

- 6. 2 MHz core/system clock, and 1 MHz bus/flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. No flash accesses; some activity on DMA & RAM assumed.

- 7. Includes 32 kHz oscillator current and RTC operation.

- 8. An external power switch for VBAT should be present on board to have better battery life and keep VBAT pin powered in all conditions. There is no internal power switch in RTC.

### 2.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors

| Symbol           | Description                        | Frequency<br>band<br>(MHz) | Тур. | Unit | Notes |

|------------------|------------------------------------|----------------------------|------|------|-------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                    | 14   | dBµV |       |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                     | 16   | dBµV |       |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                    | 12   | dBµV |       |

| $V_{RE4}$        | Radiated emissions voltage, band 4 | 500–1000                   | 5    | dBµV |       |

| $V_{RE\_IEC}$    | IEC level                          | 0.15–1000                  | М    | _    | 1     |

1.  $V_{DD}$  = 3.3 V,  $T_A$  = 25 °C,  $f_{OSC}$  = 10 MHz (crystal),  $f_{SYS}$  = 75 MHz,  $f_{BUS}$  = 25 MHz

### 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

12

| Symbol | Description                                                                         | Min. | Max. | Unit                | Notes |

|--------|-------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path  |      | _    | Bus clock<br>cycles | 1     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Asynchronous path | 16   | -    | ns                  |       |

|        | External reset pulse width (digital glitch filter disabled)                         | 100  | _    | ns                  | 2     |

|        | Port rise and fall time                                                             |      |      |                     |       |

|        | Slew disabled                                                                       |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7 V                                                    | _    | 8    | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6 V$                                                        | _    | 5    | ns                  |       |

|        | Slew enabled                                                                        |      |      |                     |       |

|        | • $1.71 \le V_{DD} \le 2.7 \text{ V}$                                               | _    | 27   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6 \text{ V}$                                                | _    | 16   | ns                  |       |

| Table 10. | General | switching | specifications |

|-----------|---------|-----------|----------------|

|-----------|---------|-----------|----------------|

1. The greater synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

## 2.4 Thermal specifications

### 2.4.1 Thermal operating requirements

#### Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. <sup>1</sup> | Unit |

|----------------|--------------------------|------|-------------------|------|

| TJ             | Die junction temperature | -40  | 125               | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105               | °C   |

1. Maximum  $T_A$  can be exceeded **only if** the user ensures that  $T_J$  does **not** exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:

$T_J = T_A + R_{\theta JA} \times chip \text{ power dissipation.}$

### 2.4.2 Thermal attributes

| Board type           | Symbol           | Description                                      | 100 LQFP | 144 LQFP | Unit | Notes |

|----------------------|------------------|--------------------------------------------------|----------|----------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub> | Thermal<br>resistance,<br>junction to<br>ambient | 62       | 55       | °C/W | 1     |

## 3.1 Core modules

### 3.1.1 Single Wire Debug (SWD)

### Table 12. SWD switching characteristics at 2.7 V (2.7-3.6 V)

| Symbol                             | Description                | Value | Unit | Notes |

|------------------------------------|----------------------------|-------|------|-------|

| SWD CLK                            | Frequency of SWD operation | 20    | MHz  |       |

| Inputs, t <sub>SUI</sub>           | Data setup time            | 5     | ns   | 1     |

| inputs, t <sub>HI</sub>            | Data hold time             | 0     | ns   | 1     |

| after clock edge, t <sub>DVO</sub> | Data valid Time            | 32    | ns   | 1     |

| t <sub>HO</sub>                    | Data Valid Hold            | 0     | ns   | 1     |

1. Input transition assumed = 1 ns. Output transition assumed = 50 pF.

#### Table 13. Switching characteristics at 1.7 V (1.7-3.6 V)

| Symbol                             | Description                | Value | Unit | Notes |

|------------------------------------|----------------------------|-------|------|-------|

| SWD CLK                            | Frequency of SWD operation | 18    | MHz  |       |

| Inputs, t <sub>SUI</sub>           | Data setup time            | 4.7   | ns   | 1     |

| inputs, t <sub>HI</sub>            | Data hold time             | 0     | ns   | 1     |

| after clock edge, t <sub>DVO</sub> | Data valid Time            | 49.4  | ns   | 2     |

| t <sub>HO</sub>                    | Data Valid Hold            | 0     | ns   | 1     |

1. Input transition assumed = 1 ns. Output transition assumed = 50 pF.

2. Frequency of SWD clock (18 MHz) is applicable only in case the input setup time of the device outside is not more than 6.15 ns, else the frequency of SWD clock would need to be lowered.

### 3.1.2 Analog Front End (AFE)

#### AFE switching characteristics at (2.7 V-3.6 V)

**Case 1:** Clock is coming In and Data is also coming In (XBAR ports timed with respect to AFE clock defined at pad PTB7, PTE3, and PTK4).

Table 14. AFE switching characteristics (2.7 V-3.6 V)

| Symbol                   | Description            | Value | Unit | Notes |

|--------------------------|------------------------|-------|------|-------|

| AFE CLK                  | Frequency of operation | 10    | MHz  |       |

| Inputs, t <sub>SUI</sub> | Data setup time        | 5     | ns   | 1     |

| inputs, t <sub>HI</sub>  | Data hold time         | 0     | ns   | 1     |

1. Input Transition: 1 ns. Output Load: 50 pF.

16

Peripheral operating requirements and behaviors

| Symbol         | Description                                                             | Min.  | Тур. | Max. | Unit | Notes |

|----------------|-------------------------------------------------------------------------|-------|------|------|------|-------|

| $V_{DD}$       | Supply voltage                                                          | 1.71  | _    | 3.6  | V    |       |

| IDDOSC         | Supply current — low-power mode (HGO=0)                                 |       |      |      |      | 1     |

|                | • 32 kHz                                                                |       | 500  |      | nA   |       |

|                | • 1 MHz                                                                 | _     | 200  | —    | μA   |       |

|                | • 4 MHz                                                                 |       | 200  | —    | μA   |       |

|                | • 8 MHz (RANGE=01)                                                      |       | 300  | —    | μA   |       |

|                | • 16 MHz                                                                |       | 950  | —    | μA   |       |

|                | • 24 MHz                                                                |       | 1.2  | —    | mA   |       |

|                | • 32 MHz                                                                | _     | 1.5  | _    | mA   |       |

| IDDOSC         | Supply current — high-gain mode (HGO=1)                                 |       |      |      |      | 1     |

|                | • 32 kHz                                                                |       | 25   |      | μA   |       |

|                | • 1 MHz                                                                 | _     | 300  |      | μA   |       |

|                | • 4 MHz                                                                 |       | 400  | _    | μA   |       |

|                | • 8 MHz (RANGE=01)                                                      |       | 500  | _    | μA   |       |

|                | • 16 MHz                                                                |       | 2.5  | _    | mA   |       |

|                | • 24 MHz                                                                |       | 3    | _    | mA   |       |

|                | • 32 MHz                                                                | _     | 4    | _    | mA   |       |

| C <sub>x</sub> | EXTAL load capacitance                                                  | _     |      |      |      | 2, 3  |

| Cy             | XTAL load capacitance                                                   | _     |      | _    |      | 2, 3  |

|                | Capacitance of EXTAL                                                    | 247   | _    | _    | ff   |       |

|                | <ul><li>Die level (100 LQFP)</li><li>Package level (100 LQFP)</li></ul> | 0.495 |      |      | pF   |       |

|                | Capacitance of XTAL                                                     | 265   | _    | —    | ff   |       |

|                | <ul><li>Die level (100 LQFP)</li><li>Package level (100 LQFP)</li></ul> | 0.495 |      |      | pF   |       |

| R <sub>F</sub> | Feedback resistor — low-frequency, low-power mode (HGO=0)               | —     |      | —    | MΩ   | 2, 4  |

|                | Feedback resistor — low-frequency, high-gain mode (HGO=1)               | —     | 10   | —    | MΩ   |       |

|                | Feedback resistor — high-frequency, low-power mode (HGO=0)              | —     |      | —    | MΩ   |       |

|                | Feedback resistor — high-frequency, high-gain mode (HGO=1)              | _     | 1    | —    | MΩ   |       |

| R <sub>S</sub> | Series resistor — low-frequency, low-power<br>mode (HGO=0)              | _     | _    | —    | kΩ   |       |

|                | Series resistor — low-frequency, high-gain mode (HGO=1)                 | _     | 200  | _    | kΩ   |       |

### 3.2.2.1 Oscillator DC electrical specifications Table 19. Oscillator DC electrical specifications

| Num | Symbol            | Description                                  | Min. | Max. | Unit |

|-----|-------------------|----------------------------------------------|------|------|------|

| 3   | V <sub>XTAL</sub> | XTAL Input<br>Voltage                        | -0.3 | 3.6  | V    |

| 4   | T <sub>A</sub>    | Operating<br>Temperature<br>Range (Packaged) | -40  | 135  | °C   |

| 5   | TJ                | Operating<br>Temperature<br>Range (Junction) | -40  | 135  | °C   |

| 6   | T <sub>stg</sub>  | Storage<br>Temperature<br>Range              | -65  | 150  | °C   |

| Table 21. | 32kHz oscillator absolute maximum rating | S | (continued) | ļ |

|-----------|------------------------------------------|---|-------------|---|

|-----------|------------------------------------------|---|-------------|---|

#### 3.2.3.2 32 kHz oscillator DC electrical specifications Table 22. 32kHz oscillator DC electrical specifications

| Symbol                       | Description                                   | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>BAT</sub>             | Supply voltage                                | 1.71 | —    | 3.6  | V    |

| R <sub>F</sub>               | Internal feedback resistor                    | _    | 100  | —    | MΩ   |

| C <sub>para</sub>            | Parasitical capacitance of EXTAL32 and XTAL32 | -    | 5    | 7    | pF   |

| V <sub>pp</sub> <sup>1</sup> | Peak-to-peak amplitude of oscillation         | —    | 0.6  |      | V    |

1. When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to required oscillator components and must not be connected to any other devices.

#### 3.2.3.3 32 kHz oscillator frequency specifications Table 23. 32 kHz oscillator frequency specifications

| Symbol                  | Description                               | Min. | Тур.   | Max.             | Unit | Notes |

|-------------------------|-------------------------------------------|------|--------|------------------|------|-------|

| f <sub>osc_lo</sub>     | Oscillator crystal                        | —    | 32.768 | _                | kHz  |       |

| t <sub>start</sub>      | Crystal start-up time                     | —    | 1000   | _                | ms   | 1     |

| f <sub>ec_extal32</sub> | Externally provided input clock frequency | _    | 32.768 | _                | kHz  | 2     |

| V <sub>ec_extal32</sub> | Externally provided input clock amplitude | 700  | _      | V <sub>BAT</sub> | mV   | 2, 3  |

1. Proper PC board layout procedures must be followed to achieve specifications.

- 2. This specification is for an externally supplied clock driven to EXTAL32 and does not apply to any other clock input. The oscillator remains enabled and XTAL32 must be left unconnected.

- 3. The parameter specified is a peak-to-peak value and  $V_{IH}$  and  $V_{IL}$  specifications do not apply. The voltage of the applied clock must be within the range of  $V_{SS}$  to  $V_{BAT}$ .

### NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

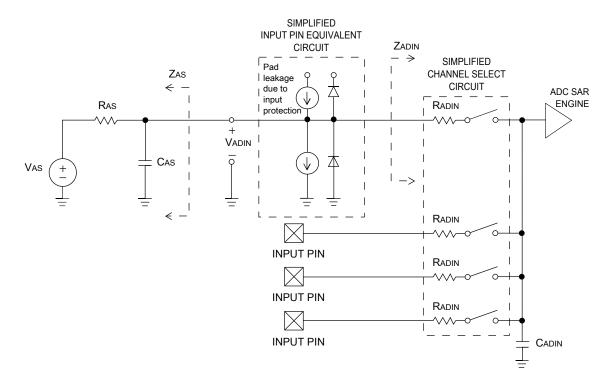

Figure 3. ADC input impedance equivalency diagram

### 3.4.1.2 16-bit ADC electrical characteristics

|                      |                              |                                          | · · · · · · · · · · · · · · · · · · · |                   |                 |                  |                      |

|----------------------|------------------------------|------------------------------------------|---------------------------------------|-------------------|-----------------|------------------|----------------------|

| Symbol               | Description                  | Conditions <sup>1</sup>                  | Min.                                  | Typ. <sup>2</sup> | Max.            | Unit             | Notes                |

| I <sub>DDA_ADC</sub> | Supply current               |                                          | 0.215                                 | —                 | 1.7             | mA               | 3                    |

|                      | ADC                          | • ADLPC = 1, ADHSC = 0                   | 1.2                                   | 2.4               | 3.9             | MHz              | t <sub>ADACK</sub> = |

|                      | asynchronous<br>clock source | <ul> <li>ADLPC = 1, ADHSC = 1</li> </ul> | 2.4                                   | 4.0               | 6.1             | MHz              | 1/f <sub>ADACK</sub> |

| f <sub>ADACK</sub>   |                              | • ADLPC = 0, ADHSC = 0                   | 3.0                                   | 5.2               | 7.3             | MHz              |                      |

|                      |                              | • ADLPC = 0, ADHSC = 1                   | 4.4                                   | 6.2               | 9.5             | MHz              |                      |

|                      | Sample Time                  | See Reference Manual chapter for         | r sample tim                          | ies               |                 |                  |                      |

| TUE                  | Total                        | 12-bit modes                             | _                                     | ±4                | ±6.8            | LSB <sup>4</sup> | 5                    |

|                      | unadjusted<br>error          | <li>&lt;12-bit modes</li>                | —                                     | ±1.4              | ±2.1            |                  |                      |

| DNL                  | Differential non-            | 12-bit modes                             | _                                     | ±0.7              | -1.1 to         | LSB <sup>4</sup> | 5                    |

|                      | linearity                    | <ul> <li>&lt;12-bit modes</li> </ul>     | —                                     | ±0.2              | +1.9            |                  |                      |

|                      |                              |                                          |                                       |                   | –0.3 to<br>+0.5 |                  |                      |

| INL                  | Integral non-                | 12-bit modes                             | _                                     | ±1.0              | -2.7 to         | LSB <sup>4</sup> | 5                    |

|                      | linearity                    |                                          | _                                     | ±0.5              | +1.9            |                  |                      |

Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ )

| Symbol              | Description                                                                 | Min.   | Тур. | Max.   | Unit   | Notes |

|---------------------|-----------------------------------------------------------------------------|--------|------|--------|--------|-------|

| VREFH               | Voltage reference output with — factory trim                                | 1.1584 |      | 1.2376 | V      |       |

| VREFH               | Voltage reference output — user trim                                        | 1.178  | _    | 1.202  | V      |       |

| VREFL               | Voltage reference output                                                    | 0.38   | 0.4  | 0.42   | V      |       |

| V <sub>step</sub>   | Voltage reference trim step                                                 | —      | 0.5  | —      | mV     |       |

| V <sub>tdrift</sub> | Temperature drift when ICOMP = 0<br>across full temperature range           | _      | 18   |        | ppm/ºC |       |

|                     | Temperature drift when ICOMP = 1<br>across full temperature range           | _      | 6    | _      | ppm/°C | 1     |

|                     | Temperature drift when ICOMP = 1 across -40 $^{\circ}$ C to 70 $^{\circ}$ C | —      | 5    |        | ppm/°C | 1, 2  |

|                     | Temperature drift when ICOMP = 1 across 0 $^{\circ}$ C to 50 $^{\circ}$ C   | _      | 3    |        | ppm/°C | 1, 2  |

| Ac                  | Aging coefficient                                                           | —      | —    | 400    | uV/yr  |       |

| l <sub>bg</sub>     | Bandgap only current                                                        | —      | _    | 80     | μA     | 2     |

| I <sub>Ip</sub>     | Low-power buffer current                                                    | —      | _    | 0.19   | mA     | 2     |

| I <sub>hp</sub>     | High-power buffer current                                                   | —      | _    | 0.5    | mA     | 2     |

| I <sub>LOAD</sub>   | VREF buffer current                                                         | -2     | _    | 2      | mA     | 3, 4  |

| $\Delta V_{LOAD}$   | Load regulation                                                             |        |      |        | μV     | 2, 5  |

|                     | • current = ± 1.0 mA                                                        | -      | 200  | _      |        |       |

| T <sub>stup</sub>   | Buffer startup time                                                         | —      |      | 20     | ms     |       |

| V <sub>vdrift</sub> | Voltage drift (VREFHmax -VREFHmin across the full voltage range)            | —      | 0.5  | _      | mV     | 2     |

#### Table 32. VREF full-range operating behaviors (continued)

1. ICOMP=1 is recommended to get best temperature drift. CHOPEN bit = 1 is also recommended.

2. See the chip's Reference Manual for the appropriate settings of VREF Status and Control register.

3. 2 mA  $I_{\text{LOAD}}$  is only achievable for above 2.7 V  $V_{\text{DDA}}$  condition.

4. See the chip's Reference Manual for the appropriate settings of SIM Miscellaneous Control Register.

5. Load regulation voltage is the difference between VREFH voltage with no load vs. voltage with defined load.

#### NOTE

Temperature drift per degree is ( (VREFHmax-VREFHmin)/ (temperature range)/VREFHmin ) in ppm/°C

### 3.4.4 AFE electrical specifications

| Symbo<br>I          | Description                    | Conditions                                                                                                             | Min | Typ <sup>1</sup> | Мах | Unit | Notes |

|---------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|------|-------|

| f <sub>Nyq</sub>    | Input bandwidth                | Normal Mode                                                                                                            | 1.5 | 1.5              | 1.5 | kHz  |       |

|                     |                                | Low-Power Mode                                                                                                         | 1.5 | 1.5              | 1.5 |      |       |

| V <sub>CM</sub>     | Input Common Mode<br>Reference |                                                                                                                        | 0   |                  | 0.8 | V    |       |

| VIN <sub>diff</sub> | Differential input range       | Gain = 1 (PGA ON/OFF) <sup>2</sup>                                                                                     |     | ± 500            |     | mV   |       |

|                     |                                | Gain = 2                                                                                                               |     | ± 250            |     | mV   |       |

|                     |                                | Gain = 4                                                                                                               |     | ± 125            |     | mV   |       |

|                     |                                | Gain = 8                                                                                                               |     | ± 62             |     | mV   |       |

|                     |                                | Gain = 16                                                                                                              |     | ± 31             |     | mV   |       |

|                     |                                | Gain = 32                                                                                                              |     | ± 15             |     | mV   |       |

| SNR                 | Signal to Noise Ratio          | Normal Mode<br>• f <sub>IN</sub> =50 Hz; gain=01, common<br>mode=0V, V <sub>pp</sub> =1000mV (full                     | 90  | 92               |     | dB   |       |

|                     |                                | range diff.)<br>• f <sub>IN</sub> =50 Hz; gain=02, common<br>mode=0V, V <sub>pp</sub> = 500mV<br>(differential ended)  | 88  | 90               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=04, common<br/>mode=0V, V<sub>pp</sub>= 250mV<br/>(differential ended)</li> </ul>  | 82  | 86               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=08, common<br/>mode=0V, V<sub>pp</sub>= 125mV<br/>(differential ended)</li> </ul>  | 76  | 82               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=16, common<br/>mode=0V, V<sub>pp</sub>= 62mV<br/>(differential ended)</li> </ul>   | 70  | 78               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=32, common<br/>mode=0V, V<sub>pp</sub>= 31mV<br/>(differential ended)</li> </ul>   | 64  | 74               |     |      |       |

|                     |                                | Low-Power Mode<br>• f <sub>IN</sub> =50 Hz; gain=01, common<br>mode=0V, V <sub>pp</sub> =1000mV (full<br>range diff.)  | 82  | 82               |     | dB   |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=02, common<br/>mode=0V, V<sub>pp</sub>= 500mV<br/>(differential ended)</li> </ul>  | 76  | 78               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=04, common<br/>mode=0V, V<sub>pp</sub>= 250mV<br/>(differential ended )</li> </ul> | 70  | 74               |     |      |       |

|                     |                                | <ul> <li>f<sub>IN</sub>=50 Hz; gain=08, common<br/>mode=0V, V<sub>pp</sub>= 125mV<br/>(differential ended )</li> </ul> | 64  | 70               |     |      |       |

|                     |                                |                                                                                                                        | 58  | 66               |     |      |       |

### 3.4.4.1 ΣΔ ADC + PGA specifications Table 33. ΣΔ ADC + PGA specifications

| Symbo<br>I                               | Description                                                                         | Conditions                                                                                                                                                                                                                     | Min  | Typ <sup>1</sup> | Max  | Unit   | Notes |

|------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|------|--------|-------|

|                                          |                                                                                     | <ul> <li>f<sub>IN</sub>=50 Hz; gain=16, common<br/>mode=0V, V<sub>pp</sub>= 62mV<br/>(differential ended)</li> <li>f<sub>IN</sub>=50 Hz; gain=32, common<br/>mode=0V, V<sub>pp</sub>= 31mV<br/>(differential ended)</li> </ul> | 52   | 62               |      |        |       |

| SINAD                                    | Signal-to-Noise +<br>Distortion Ratio                                               | Normal Mode<br>• f <sub>IN</sub> =50 Hz; gain=01, common<br>mode=0V, V <sub>pp</sub> =500mV<br>(differential ended )                                                                                                           |      | 78               |      | dB     |       |

|                                          |                                                                                     | Low-Power Mode<br>• f <sub>IN</sub> =50 Hz; gain=01, common<br>mode=0V, V <sub>pp</sub> =500mV<br>(differential ended )                                                                                                        |      | 74               |      | dB     |       |

| CMMR                                     | Common Mode Rejection<br>Ratio                                                      | <ul> <li>f<sub>IN</sub>=50 Hz; gain=01, common<br/>mode=0V, Vid=100 mV</li> <li>f<sub>IN</sub>=50 Hz; gain=32, common<br/>mode=0V, V<sub>id</sub>=100 mV</li> </ul>                                                            |      | 70<br>70         |      | dB     |       |

| E <sub>offset</sub>                      | Offset Error                                                                        | Gain=01, V <sub>pp</sub> =1000 mV (full range diff.)                                                                                                                                                                           |      |                  | ± 5  | mV     |       |

| ∆<br>Offset <sub>Te</sub><br>mp          | Offset Temperature Drift <sup>3</sup>                                               | Gain=01, V <sub>pp</sub> =1000 mV (full range<br>diff.)                                                                                                                                                                        |      |                  | ± 25 | ppm/°C |       |

| Δ<br>Gain <sub>Tem</sub><br><sub>p</sub> | Gain Temperature Drift -<br>Gain error caused by<br>temperature drifts <sup>4</sup> | <ul> <li>Gain=01, V<sub>pp</sub>=500 mV<br/>(differential ended)</li> <li>Gain=32, V<sub>pp</sub>=15 mV<br/>(differential ended)</li> </ul>                                                                                    |      |                  | ± 75 | ppm/°C |       |

| PSRR <sub>A</sub><br>c                   | AC Power Supply<br>Rejection Ratio                                                  | Gain=01, VCC = 3 V ± 100 mV, f <sub>IN</sub><br>= 50 Hz                                                                                                                                                                        |      | 60               |      | dB     |       |

| XT                                       | Crosstalk (with the input of<br>the affected channel<br>grounded)                   | Gain=01, V <sub>id</sub> = 500 mV, f <sub>IN</sub> = 50 Hz                                                                                                                                                                     |      |                  | -100 | dB     |       |

| f <sub>MCLK</sub>                        | Modulator Clock<br>Frequency Range                                                  | Normal Mode                                                                                                                                                                                                                    | 0.03 |                  | 6.5  | MHz    |       |

|                                          |                                                                                     | Low-Power Mode                                                                                                                                                                                                                 | 0.03 |                  | 1.6  |        |       |

| I <sub>DDA_PG</sub><br>A                 | Current consumption by PGA (each channel)                                           | Normal Mode (f <sub>MCLK</sub> = 6.144 MHz,<br>OSR= 2048)                                                                                                                                                                      |      |                  | 2.6  | mA     | 5     |

|                                          |                                                                                     | Low-Power Mode (f <sub>MCLK</sub> = 0.768<br>MHz, OSR= 256)                                                                                                                                                                    |      |                  | 0    |        |       |

| I <sub>DDA_AD</sub><br>C                 | Current Consumption by ADC (each channel)                                           | Normal Mode (f <sub>MCLK</sub> = 6.144 MHz,<br>OSR= 2048)                                                                                                                                                                      |      |                  | 1.4  | mA     |       |

|                                          |                                                                                     | Low-Power Mode (f <sub>MCLK</sub> = 0.768<br>MHz, OSR= 256)                                                                                                                                                                    |      |                  | 0.5  |        |       |

#### Table 33. $\Sigma \triangle$ ADC + PGA specifications (continued)

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>MCLK</sub> = 6.144 MHz, OSR = 2048 for Normal mode and f<sub>MCLK</sub> = 768 kHz, OSR = 256 for Low-Power Mode unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. The full-scale input range in single-ended mode is  $0.5V_{pp}$ .

34

#### Peripheral operating requirements and behaviors

| Symbo<br>I               | Description                               | Conditions                                                                                                   | Min          | Typ <sup>1</sup> | Мах        | Unit | Notes |

|--------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------|------------------|------------|------|-------|

| PSRR <sub>A</sub><br>c   | AC Power Supply<br>Rejection Ratio        | Gain=01, VCC = 3 V ± 100 mV, f <sub>IN</sub><br>= 50 Hz                                                      |              | 60               |            | dB   |       |

| ХТ                       | Crosstalk                                 | Gain=01, $V_{id}$ = 500 mV, $f_{IN}$ = 50 Hz                                                                 |              |                  | -100       | dB   |       |

| f <sub>MCLK</sub>        | Modulator Clock<br>Frequency Range        | Normal Mode<br>Low-Power Mode                                                                                | 0.03<br>0.03 |                  | 6.5<br>1.6 | MHz  |       |

| I <sub>DDA_AD</sub><br>C | Current Consumption by ADC (each channel) | Normal Mode ( $f_{MCLK}$ = 6.144 MHz,<br>OSR= 2048)<br>Low-Power Mode ( $f_{MCLK}$ = 0.768<br>MHz, OSR= 256) |              |                  | 1.4<br>0.5 | mA   |       |

| Table 34. | ΣΔ ADC standalone s | pecifications | (continued) |

|-----------|---------------------|---------------|-------------|

|-----------|---------------------|---------------|-------------|

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>MCLK</sub> = 6.144 MHz, OSR = 2048 for Normal mode and f<sub>MCLK</sub> = 768 kHz, OSR = 256 for Low-Power Mode unless otherwise stated. Typical values are for reference only and are not tested in production.

2. Represent combined gain temperature drift of the SD ADC, and Internal 1.2 VREF blocks.

3. Represent combined offset temperature drift of the SD ADC, and Internal 1.2 VREF blocks; Defined by shorting both differential inputs to ground.

### 3.4.4.3 External modulator interface

The external modulator interface on this device comprises of a Clock signal and 1-bit data signal. Depending on the modulator device being used the interface works as follows:

- Clock supplied to external modulator which drives data on rising edge and the KM device captures it on falling edge or next rising edge.

- Clock and data are supplied by external modulator and KM device can sample it on falling edge or next rising edge.

Depending on control bit in AFE, the sampling edge is changed.

### 3.5 Timers

See General switching specifications.

### 3.6 Communication interfaces

### 3.6.1 I2C switching specifications

See General switching specifications.

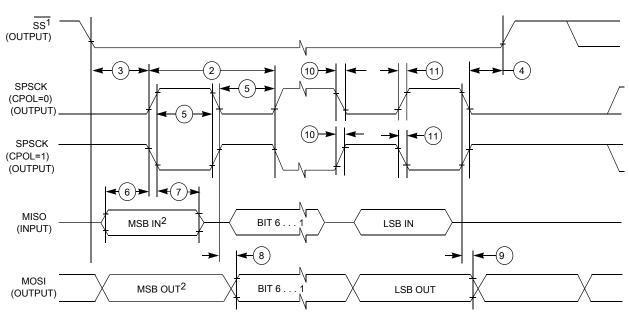

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit               | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|--------------------|------|

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>  | 2048 x                   | ns                 | 2    |

|      |                     |                                |                          | t <sub>periph</sub>      |                    |      |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                      | —                        | t <sub>SPSCK</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                      | —                        | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | 1024 x                   | ns                 | —    |

|      |                     |                                |                          | t <sub>periph</sub>      |                    |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 96                       | —                        | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                        | —                        | ns                 | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 52                       | ns                 | —    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                 | —    |

| 10   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                 | —    |

|      | t <sub>FI</sub>     | Fall time input                | 1                        |                          |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | -                        | 36                       | ns                 | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                    |      |

Table 36. SPI master mode timing on slew rate enabled pads (continued)

- 1. For both SPI0 and SPI1,  $f_{\text{periph}}$  is the system clock (f\_{\text{SYS}}).

- 2.  $t_{periph} = 1/f_{periph}$

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 7. SPI master mode timing (CPHA = 0)

| Symbol             | Description                                                                           | Min. | Тур. | Max.                   | Unit                | Notes |

|--------------------|---------------------------------------------------------------------------------------|------|------|------------------------|---------------------|-------|

|                    | • RVTRIM=1110                                                                         | _    | 0.99 | —                      |                     |       |

|                    | • RVTRIM=0001                                                                         | —    | 1.01 | —                      |                     |       |

|                    | • RVTRIM=1001                                                                         | —    | 1.02 | _                      |                     |       |

|                    | • RVTRIM=0101                                                                         | —    | 1.03 | _                      |                     |       |

|                    | • RVTRIM=1101                                                                         | —    | 1.05 | _                      |                     |       |

|                    | • RVTRIM=0011                                                                         | —    | 1.06 | _                      |                     |       |

|                    | • RVTRIM=1011                                                                         | —    | 1.07 | _                      |                     |       |

|                    | • RVTRIM=0111                                                                         | —    | 1.08 | _                      |                     |       |

|                    | • RVTRIM=1111                                                                         | _    | 1.09 | _                      |                     |       |

| Δ <sub>RTRIM</sub> | V <sub>IREG</sub> TRIM resolution                                                     |      |      | 3.0                    | % V <sub>IREG</sub> |       |

| I <sub>VIREG</sub> | V <sub>IREG</sub> current adder — RVEN = 1                                            | _    | 1    | —                      | μA                  |       |

| I <sub>RBIAS</sub> | RBIAS current adder                                                                   |      |      |                        |                     |       |

|                    | <ul> <li>LADJ = 10 or 11 — High load (LCD glass<br/>capacitance ≤ 8000 pF)</li> </ul> | —    | 10   | _                      | μA                  |       |

|                    | <ul> <li>LADJ = 00 or 01 — Low load (LCD glass<br/>capacitance ≤ 2000 pF)</li> </ul>  | —    | 1    | _                      | μA                  |       |

| R <sub>RBIAS</sub> | RBIAS resistor values                                                                 |      |      |                        |                     |       |

|                    | <ul> <li>LADJ = 10 or 11 — High load (LCD glass<br/>capacitance ≤ 8000 pF)</li> </ul> | —    | 0.28 | _                      | MΩ                  |       |

|                    | <ul> <li>LADJ = 00 or 01 — Low load (LCD glass<br/>capacitance ≤ 2000 pF)</li> </ul>  | —    | 2.98 | _                      | ΜΩ                  |       |

| VLL1               | VLL1 voltage                                                                          | —    | —    | V <sub>IREG</sub>      | V                   | 4     |

| VLL2               | VLL2 voltage                                                                          | _    | —    | 2 x V <sub>IREG</sub>  | V                   | 4     |

| VLL3               | VLL3 voltage                                                                          |      | —    | 3 x V <sub>IREG</sub>  | V                   | 4     |

| VLL1               | VLL1 voltage                                                                          |      |      | V <sub>DDA</sub> / 3   | V                   | 5     |

| VLL2               | VLL2 voltage                                                                          |      |      | V <sub>DDA</sub> / 1.5 | V                   | 5     |

| VLL3               | VLL3 voltage                                                                          | —    |      | V <sub>DDA</sub>       | V                   | 5     |

#### Table 39. LCD electricals (continued)

1. The actual value used could vary with tolerance.

- 2. For highest glass capacitance values, LCD\_GCR[LADJ] should be configured as specified in the LCD Controller chapter within the device's reference manual.

- 3.  $V_{\rm IREG}$  maximum should never be externally driven to any level other than  $V_{DD}$  0.15 V

- VLL1, VLL2 and VLL3 are a function of V<sub>IREG</sub> only when the regulator is enabled (GCR[RVEN]=1) and the charge pump is enabled (GCR[CPSEL]=1).

- 5. VLL1, VLL2 and VLL3 are a function of  $V_{DDA}$  only under either of the following conditions:

- The charge pump is enabled (GCR[CPSEL]=1), the regulator is disabled (GCR[RVEN]=0), and VLL3 = V<sub>DDA</sub> through the internal power switch (GCR[VSUPPLY]=0).

- The resistor bias string is enabled (GCR[CPSEL]=0), the regulator is disabled (GCR[RVEN]=0), and VLL3 is connected to V<sub>DDA</sub> externally (GCR[VSUPPLY]=1).

#### Pinout

| 144<br>QFP | 100<br>QFP | Pin Name          | DEFAULT  | ALT0                             | ALT1              | ALT2            | ALT3            | ALT4            | ALT5     | ALT6 | ALT7    |

|------------|------------|-------------------|----------|----------------------------------|-------------------|-----------------|-----------------|-----------------|----------|------|---------|

| 77         | 52         | PTD5              | Disabled | ADC0_SE4a                        | PTD5              | LPTMR0_<br>ALT3 | QTMR0_<br>TMR0  | UART3_CTS_<br>b |          |      |         |

| 78         | 53         | PTD6/<br>LLWU_P8  | Disabled | ADC0_SE5a                        | PTD6/<br>LLWU_P8  | LPTMR0_<br>ALT2 | CMP1_OUT        | UART3_RTS_<br>b |          |      |         |

| 79         | 54         | PTD7/<br>LLWU_P7  | Disabled | CMP0_IN4                         | PTD7/<br>LLWU_P7  | I2C0_SCL        | XBAR_IN4        | UART3_RX        |          |      |         |

| 80         | 55         | PTE0              | Disabled |                                  | PTE0              | I2C0_SDA        | XBAR_OUT4       | UART3_TX        | CLKOUT   |      |         |

| 81         | —          | PTK2              | Disabled | ADC0_SE14                        | PTK2              | UART0_TX        |                 |                 |          |      |         |

| 82         | _          | PTK3/<br>LLWU_P19 | Disabled | ADC0_SE15                        | PTK3/<br>LLWU_P19 | UART0_RX        |                 |                 |          |      |         |

| 83         | 56         | PTE1              | RESET_b  |                                  | PTE1              |                 |                 |                 |          |      | RESET_b |

| 84         | 57         | PTE2              | EXTAL0   | EXTAL0                           | PTE2              | EWM_IN          | XBAR_IN6        | I2C1_SDA        |          |      |         |

| 85         | 58         | PTE3              | XTAL0    | XTAL0                            | PTE3              | EWM_OUT_b       | AFE_CLK         | I2C1_SCL        |          |      |         |

| 86         | 59         | VSS               | VSS      | VSS                              |                   |                 |                 |                 |          |      |         |

| 87         | 60         | VSSA              | VSSA     | VSSA                             |                   |                 |                 |                 |          |      |         |

| 88         | 61         | VDDA              | VDDA     | VDDA                             |                   |                 |                 |                 |          |      |         |

| 89         | 62         | VDD               | VDD      | VDD                              |                   |                 |                 |                 |          |      |         |

| 90         | 63         | PTE4              | Disabled |                                  | PTE4              | LPTMR0_<br>ALT1 | UART2_CTS_<br>b | EWM_IN          |          |      |         |

| 91         | 64         | PTE5/<br>LLWU_P6  | Disabled |                                  | PTE5/<br>LLWU_P6  | QTMR0_<br>TMR3  | UART2_RTS_<br>b | EWM_OUT_b       |          |      |         |

| 92         | 65         | PTE6/<br>LLWU_P5  | SWD_DIO  | CMP0_IN2                         | PTE6/<br>LLWU_P5  | XBAR_IN5        | UART2_RX        |                 | I2C0_SCL |      | SWD_DIO |

| 93         | 66         | PTE7              | SWD_CLK  | ADC0_SE6a                        | PTE7              | XBAR_OUT5       | UART2_TX        |                 | I2C0_SDA |      | SWD_CLK |

| 94         | 67         | PTF0/<br>LLWU_P4  | Disabled | ADC0_SE7a/<br>CMP2_IN3           | PTF0/<br>LLWU_P4  | RTC_CLKOUT      | QTMR0_<br>TMR2  | CMP0_OUT        |          |      |         |

| 95         | 68         | PTF1              | Disabled | LCD_P0/<br>ADC0_SE8/<br>CMP2_IN4 | PTF1              | QTMR0_<br>TMR0  | XBAR_OUT6       |                 |          |      | LCD_P0  |

| 96         | 69         | PTF2              | Disabled | LCD_P1/<br>ADC0_SE9/<br>CMP2_IN5 | PTF2              | CMP1_OUT        | RTC_CLKOUT      |                 |          |      | LCD_P1  |

| 97         | _          | PTK4              | Disabled | LCD_P51                          | PTK4              | XBAR_IN9        | AFE_CLK         |                 |          |      | LCD_P51 |

| 98         | -          | PTK5              | Disabled |                                  | PTK5              | UART1_RX        |                 |                 |          |      |         |

| 99         | _          | PTK6              | Disabled |                                  | PTK6              | UART1_TX        |                 |                 |          |      |         |

| 100        | 70         | PTF3/<br>LLWU_P20 | Disabled | LCD_P2                           | PTF3/<br>LLWU_P20 | SPI1_PCS0       | LPTMR0_<br>ALT2 | UART0_RX        |          |      | LCD_P2  |

| 101        | 71         | PTF4              | Disabled | LCD_P3                           | PTF4              | SPI1_SCK        | LPTMR0_<br>ALT1 | UART0_TX        |          |      | LCD_P3  |

| 102        | 72         | PTF5              | Disabled | LCD_P4                           | PTF5              | SPI1_MISO       | I2C1_SCL        |                 |          |      | LCD_P4  |

| 103        | 73         | PTF6/<br>LLWU_P3  | Disabled | LCD_P5                           | PTF6/<br>LLWU_P3  | SPI1_MOSI       | I2C1_SDA        |                 |          |      | LCD_P5  |

| 104        | 74         | PTF7              | Disabled | LCD_P6                           | PTF7              | QTMR0_<br>TMR2  | CLKOUT          | CMP2_OUT        |          |      | LCD_P6  |

| 144<br>QFP | 100<br>QFP | Pin Name                                                                                              | DEFAULT  | ALTO                 | ALT1              | ALT2              | ALT3            | ALT4      | ALT5      | ALT6 | ALT7    |

|------------|------------|-------------------------------------------------------------------------------------------------------|----------|----------------------|-------------------|-------------------|-----------------|-----------|-----------|------|---------|

| 105        | -          | PTK7                                                                                                  | Disabled | LCD_P52              | PTK7              | I2C0_SCL          | XBAR_OUT9       |           |           |      | LCD_P52 |

| 106        | _          | PTL0                                                                                                  | Disabled | LCD_P53              | PTL0              | I2C0_SDA          |                 |           |           |      | LCD_P53 |

| 107        | _          | NC                                                                                                    | NC       |                      |                   |                   |                 |           |           |      |         |

| 108        | _          | NC                                                                                                    | NC       |                      |                   |                   |                 |           |           |      |         |

| 109        | —          | NC                                                                                                    | NC       |                      |                   |                   |                 |           |           |      |         |

| 110        | 75         | PTG0                                                                                                  | Disabled | LCD_P7               | PTG0              | QTMR0_<br>TMR1    | LPTMR0_<br>ALT3 |           |           |      | LCD_P7  |

| 111        | 76         | PTG1/<br>LLWU_P2                                                                                      | Disabled | LCD_P8/<br>ADC0_SE10 | PTG1/<br>LLWU_P2  |                   | LPTMR0_<br>ALT1 |           |           |      | LCD_P8  |

| 112        | 77         | PTG2/<br>LLWU_P1                                                                                      | Disabled | LCD_P9/<br>ADC0_SE11 | PTG2/<br>LLWU_P1  | SPI0_PCS0         |                 |           |           |      | LCD_P9  |

| 113        | 78         | PTG3                                                                                                  | Disabled | LCD_P10              | PTG3              | SPI0_SCK          | I2C0_SCL        |           |           |      | LCD_P10 |

| 114        | 79         | PTG4                                                                                                  | Disabled | LCD_P11              | PTG4              | SPI0_MOSI         | I2C0_SDA        |           |           |      | LCD_P11 |

| 115        | 80         | PTG5                                                                                                  | Disabled | LCD_P12              | PTG5              | SPI0_MISO         | LPTMR0_<br>ALT2 |           |           |      | LCD_P12 |

| 116        | 81         | PTG6/<br>LLWU_P0                                                                                      | Disabled | LCD_P13              | PTG6/<br>LLWU_P0  |                   | LPTMR0_<br>ALT3 |           |           |      | LCD_P13 |

| 117        | 82         | PTG7                                                                                                  | Disabled | LCD_P14              | PTG7              |                   |                 |           |           |      | LCD_P14 |

| 118        | 83         | PTH0                                                                                                  | Disabled | LCD_P15              | PTH0              | LPUARTO_<br>CTS_b |                 |           |           |      | LCD_P15 |

| 119        | 84         | PTH1                                                                                                  | Disabled | LCD_P16              | PTH1              | LPUART0_<br>RTS_b |                 |           |           |      | LCD_P16 |

| 120        | 85         | PTH2                                                                                                  | Disabled | LCD_P17              | PTH2              | LPUART0_RX        |                 |           |           |      | LCD_P17 |

| 121        | 86         | PTH3                                                                                                  | Disabled | LCD_P18              | PTH3              | LPUART0_TX        |                 |           |           |      | LCD_P18 |

| 122        | 87         | PTH4                                                                                                  | Disabled | LCD_P19              | PTH4              |                   |                 |           |           |      | LCD_P19 |

| 123        | 88         | PTH5                                                                                                  | Disabled | LCD_P20              | PTH5              |                   |                 |           |           |      | LCD_P20 |

| 124        | 89         | PTH6                                                                                                  | Disabled |                      | PTH6              | UART1_CTS_<br>b   | SPI1_PCS0       | XBAR_IN7  |           |      |         |

| 125        | 90         | PTH7                                                                                                  | Disabled |                      | PTH7              | UART1_RTS_<br>b   | SPI1_SCK        | XBAR_OUT7 |           |      |         |

| 126        | 91         | PTIO/<br>LLWU_P21                                                                                     | Disabled | CMP0_IN5             | PTIO/<br>LLWU_P21 | UART1_RX          | XBAR_IN8        | SPI1_MISO | SPI1_MOSI |      |         |

| 127        | 92         | PTI1 (This pin<br>is true open<br>drain pad.<br>External pull-<br>up resistor<br>should be<br>added.) | Disabled |                      | PTI1              | UART1_TX          | XBAR_OUT8       | SPI1_MOSI | SPI1_MISO |      |         |

| 128        | -          | PTL1                                                                                                  | Disabled | LCD_P54              | PTL1              | XBAR_IN10         |                 |           |           |      | LCD_P54 |

| 129        | _          | PTL2                                                                                                  | Disabled | LCD_P55              | PTL2              | XBAR_OUT10        |                 |           |           |      | LCD_P55 |

| 130        | 93         | PTI2/<br>LLWU_P22                                                                                     | Disabled | LCD_P21              | PTI2/<br>LLWU_P22 | LPUART0_RX        |                 |           |           |      | LCD_P21 |

| 131        | 94         | PTI3                                                                                                  | Disabled | LCD_P22              | PTI3              | LPUART0_TX        | CMP2_OUT        |           |           |      | LCD_P22 |

| 132        | 95         | VSS                                                                                                   | VSS      | VSS                  |                   |                   |                 |           |           |      |         |

Kinetis KM34 Sub-Family Data Sheet, Rev. 2, May 2015

47

### 8.2.1 Example

This is an example of an operating behavior:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μA   |

## 8.3 **Definition: Attribute**

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

### 8.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | _    | 7    | pF   |

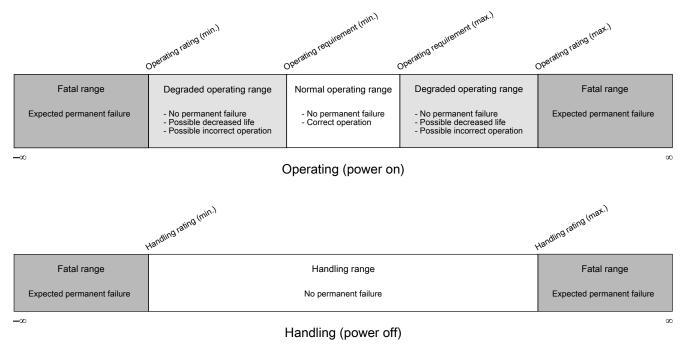

### 8.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- Handling ratings apply when the chip is not powered.

### 8.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

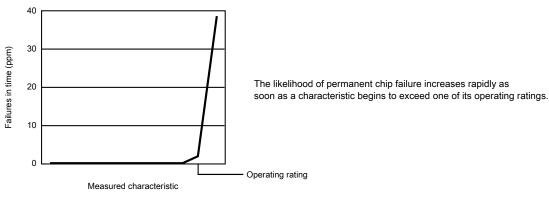

## 8.5 Result of exceeding a rating

## 8.6 Relationship between ratings and operating requirements

## 8.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

• Never exceed any of the chip's ratings.

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: www.freescale.com/salestermsandconditions.

Freescale, the Freescale logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2014-2015 Freescale Semiconductor, Inc.

Document Number KM34P144M75SF0 Revision 2, May 2015