#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 49                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p54l3beabr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                             | Table 2. SPC56xP54                  | 4x/SPC56xP60x                                        | device compar      | ison (continued        | )         |  |  |

|-----------------------------|-------------------------------------|------------------------------------------------------|--------------------|------------------------|-----------|--|--|

|                             | Feature                             | SPC560P54                                            | SPC560P60          | SPC56AP54              | SPC56AP60 |  |  |

| Enhanced D<br>access) cha   | MA (direct memory nnels             | 16                                                   |                    |                        |           |  |  |

| FlexRay                     |                                     | Yes (64 message buffer)                              |                    |                        |           |  |  |

| FlexCAN (co                 | ontroller area network)             |                                                      | 3(1)               | ),(2)                  |           |  |  |

| Safety port                 |                                     |                                                      | Yes (via third Fl  | exCAN module)          |           |  |  |

| FCCU (fault                 | collection and control unit)        |                                                      | Ye                 | s <sup>(3)</sup>       |           |  |  |

| CTU (cross                  | triggering unit)                    |                                                      | Ye                 | es                     |           |  |  |

| eTimer char                 | inels                               |                                                      | 2 :                | × 6                    |           |  |  |

| FlexPWM (p<br>channels      | oulse-width modulation)             |                                                      | Ν                  | lo                     |           |  |  |

| Analog-to-di                | gital converters (ADC)              | One (10-bit, 27-channel) <sup>(4)</sup>              |                    |                        |           |  |  |

| LINFlex mod                 | dules                               | 2 (1 × Master/Slave, 1 × Master only) <sup>(5)</sup> |                    |                        |           |  |  |

| DSPI (deser<br>interface) m | ial serial peripheral<br>odules     | 5 <sup>(6)</sup>                                     |                    |                        |           |  |  |

| CRC (cyclic                 | redundancy check) units             | 2 <sup>(7)</sup>                                     |                    |                        |           |  |  |

| JTAG interfa                | ace                                 | Yes                                                  |                    |                        |           |  |  |

| Nexus port of               | controller (NPC)                    |                                                      | Yes (Lev           | /el 2+) <sup>(8)</sup> |           |  |  |

|                             | Digital power supply <sup>(9)</sup> | 3.3 V                                                | or 5 V single supp | ly with external trar  | nsistor   |  |  |

| Cummba                      | Analog power supply                 |                                                      | 3.3 V              | or 5 V                 |           |  |  |

| Supply                      | Internal RC oscillator              |                                                      | 16                 | MHz                    |           |  |  |

|                             | External crystal oscillator         |                                                      | 4–40               | MHz                    |           |  |  |

| Packages                    |                                     | LQFP100 LQFP104<br>LQFP144 LQFP176 <sup>(</sup>      |                    |                        |           |  |  |

| Temperature                 | Standard ambient temperature        |                                                      | -40 to             | 125 °C                 |           |  |  |

Table 2. SPC56xP54x/SPC56xP60x device comparison (continued)

1. Each FlexCAN module has 32 message buffers.

2. One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

3. Enhanced FCCU version.

4. Same amount of ADC channels as on SPC560P44/50 not considering the internally connected ones. 26 channels on LQFP144 and 16 channels on LQFP100.

- 5. LinFlex\_1 is Master Only.

- 6. Increased number of CS for DSPI\_1.

- 7. Upgraded specification with addition of 8-bits polynomial (CRC-8 VDA CAN) support and 3rd context.

- 8. Improved debugging capability with data trace capability and increased Nexus throughput available on emulation package.

- 9. 3.3 V range and 5 V range correspond to different orderable parts.

- 10. Software development package only. Not available for production.

- Watchpoint triggering, watchpoint triggers program tracing

- DDR

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin<sup>(a)</sup>

## 1.5.28 IEEE 1149.1 (JTAG) controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with four pins (TDI, TMS, TCK, TDO)

- Selectable modes of operation include JTAGC/debug or normal system operation.

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC, ACCESS\_AUX\_TAP\_CORE0, ACCESS\_AUX\_TAP\_CORE1, ACCESS\_AUX\_TAP\_NASPS\_0, ACCESS\_AUX\_TAP\_NASPS\_1

- Three test data registers: a bypass register, a boundary scan register, and a device identification register.

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry.

## 1.5.29 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN transistor

- Regulates external 3.3 V to 5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

a. At least one TCK clock is necessary for the EVTI signal to be recognized by the MCU.

|                         | lable 6. System pi                                                                                                                                                                   |                   | ,      |                     |             |                                                                             |                            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|---------------------|-------------|-----------------------------------------------------------------------------|----------------------------|

|                         |                                                                                                                                                                                      |                   | Pad Sp | beed <sup>(1)</sup> |             | Pin                                                                         |                            |

| Symbol                  | Description                                                                                                                                                                          | Direction         | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144<br><br><br><br><br>1<br>29<br>30<br>87<br>88<br>89<br>31<br>107 | LQFP<br>176 <sup>(2)</sup> |

| MDO5                    | Nexus Message Data Output—line 5                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 8                          |

| MDO6                    | Nexus Message Data Output—line 6                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 9                          |

| MDO7                    | Nexus Message Data Output—line 7                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 110                        |

| MDO8                    | Nexus Message Data Output—line 8                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 111                        |

| MDO9                    | Nexus Message Data Output—line 9                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 112                        |

| MDO10                   | Nexus Message Data Output—line 10                                                                                                                                                    | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 166                        |

| MDO11                   | Nexus Message Data Output—line 11                                                                                                                                                    | Output<br>Only    | Fa     | ist                 | _           | _                                                                           | 171                        |

| RDY                     | Nexus ready output                                                                                                                                                                   | Output<br>Only    | _      | _                   | _           | _                                                                           | 172                        |

| NMI                     | Non-Maskable Interrupt                                                                                                                                                               | Input Only        | _      | _                   | 1           | 1                                                                           | 1                          |

| XTAL                    | Analog output of the oscillator amplifier<br>circuit. Needs to be grounded if oscillator is<br>used in bypass mode.                                                                  | _                 | _      | _                   | 18          | 29                                                                          | 37                         |

| EXTAL                   | Analog input of the oscillator amplifier<br>circuit, when the oscillator is not in bypass<br>mode.<br>Analog input for the clock generator when<br>the oscillator is in bypass mode. | _                 | _      |                     | 19          | 30                                                                          | 38                         |

| TMS <sup>(3)</sup>      | JTAG state machine control                                                                                                                                                           | Input Only        |        | _                   | 59          | 87                                                                          | 105                        |

| TCK <sup>(3)</sup>      | JTAG clock                                                                                                                                                                           | Input Only        | —      | _                   | 60          | 88                                                                          | 106                        |

| TDI <sup>(3)</sup>      | JTAG data input                                                                                                                                                                      | Input Only        | —      | —                   | 58          | 86                                                                          | 104                        |

| TDO <sup>(3)</sup>      | JTAG data output                                                                                                                                                                     | Output<br>Only    | _      | _                   | 61          | 89                                                                          | 107                        |

|                         | Reset                                                                                                                                                                                | pin               |        |                     |             |                                                                             |                            |

| RESET <sup>(4)</sup>    | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                                            | Bidirection<br>al | Medium | _                   | 20          | 31                                                                          | 39                         |

|                         | Test p                                                                                                                                                                               | in                |        |                     |             |                                                                             |                            |

| V <sub>PP TEST</sub>    | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | —                 | _      | _                   | 74          | 107                                                                         | 131                        |

| V <sub>REG_BYPASS</sub> | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | _                 | _      |                     | 34          | 51                                                                          | 59                         |

|                         |                                                                                                                                                                                      |                   |        |                     |             |                                                                             |                            |

## Table 6. System pins (continued)

1. SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

|       | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                   |                                          |                                         |                         |         |                      |             |        |                            |  |  |

|-------|------------------------------------------------|-----------------------------------|------------------------------------------|-----------------------------------------|-------------------------|---------|----------------------|-------------|--------|----------------------------|--|--|

| Port  | PCR                                            | Alternate                         |                                          | Peripheral                              | I/O                     | Pad s   | speed <sup>(6)</sup> |             | Pin    |                            |  |  |

| pin   | No.                                            | function <sup>(2),</sup><br>(3)   | Functions                                | (4)                                     | direction<br>(5)        | SRC = 0 | SRC = 1              | LQFP<br>100 | P LQFP | LQFP<br>176 <sup>(7)</sup> |  |  |

| D[7]  | PCR[55]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[55]<br>CS3_1<br>—<br>CS4_0<br>SIN_3 | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>—<br>O<br>I | Slow    | Medium               | 26          | 37     | 45                         |  |  |

| D[8]  | PCR[56]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[56]<br>CS2_1<br>RDY<br>CS5_0        | SIUL<br>DSPI_1<br>nexus_0<br>DSPI_0     | I/O<br>O<br>O           | Slow    | Medium               | 21          | 32     | 40                         |  |  |

| D[9]  | PCR[57]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>—<br>TXD<br>CS6_1            | SIUL<br>—<br>LINFlex_1<br>DSPI_1        | I/O<br>  0<br>0         | Slow    | Medium               | 15          | 26     | 34                         |  |  |

| D[10] | PCR[58]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>—<br>CS0_3<br>—              | SIUL<br>—<br>DSPI_3<br>—                | I/O<br>—<br>I/O<br>—    | Slow    | Medium               | 53          | 76     | 92                         |  |  |

| D[11] | PCR[59]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>—<br>CS1_3<br>SCK_3          | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>0<br>I/O    | Slow    | Medium               | 54          | 78     | 94                         |  |  |

| D[12] | PCR[60]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>—<br>CS7_1<br>RXD            | SIUL<br>—<br>—<br>DSPI_1<br>LINFlex_1   | I/O<br>—<br>—<br>0<br>I | Slow    | Medium               | 70          | 99     | 123                        |  |  |

| D[13] | PCR[61]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>—<br>CS2_3<br>SOUT_3         | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>O<br>O      | Slow    | Medium               | 67          | 95     | 119                        |  |  |

| D[14] | PCR[62]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[62]<br>—<br>CS3_3<br>—<br>SIN_3     | SIUL<br>—<br>DSPI_3<br>—<br>DSPI_3      | I/O<br>—<br>—<br>—<br>— | Slow    | Medium               | 73          | 105    | 129                        |  |  |

| D[15] | PCR[63]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[63]<br>—<br>—<br>—<br>AN[20]        | SIUL<br>—<br>—<br>—<br>ADC_0            | Input Only              | _       | _                    | 41          | 58     | 66                         |  |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                 |                    |                   |                  |         |                     |             |             |                            |  |  |

|-------------|------------------------------------------------|---------------------------------|--------------------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|--|--|

|             |                                                | Alternate                       |                    |                   | I/O              | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |  |  |

| Port<br>pin | PCR<br>No.                                     | function <sup>(2),</sup><br>(3) | Functions          | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |  |

|             |                                                | ALT0                            | GPIO[71]           | SIUL              |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT1                            |                    | —                 |                  |         |                     |             |             |                            |  |  |

| E[7]        | PCR[71]                                        | ALT2<br>ALT3                    |                    | —                 | Input Only       | —       | _                   |             | 48          | 56                         |  |  |

|             |                                                | ALI 3                           | <br>AN[10]         | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0                            | GPIO[72]           | SIUL              |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT1                            |                    |                   |                  |         |                     |             |             |                            |  |  |

| E[8]        | PCR[72]                                        | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 59          | 67                         |  |  |

|             |                                                | ALT3                            | _                  | _                 |                  |         |                     |             |             |                            |  |  |

|             |                                                | —                               | AN[22]             | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0                            | GPIO[73]           | SIUL              |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT1                            | —                  | —                 |                  |         |                     |             |             |                            |  |  |

| E[9]        | PCR[73]                                        | ALT2                            | —                  | —                 | Input Only       | —       | —                   |             | 61          | 69                         |  |  |

|             |                                                | ALT3                            | —<br>AN[23]        | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                |                                 |                    |                   |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0<br>ALT1                    | GPIO[74]           | SIUL              |                  |         |                     |             |             |                            |  |  |

| E[10]       | PCR[74]                                        | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 63          | 75                         |  |  |

|             |                                                | ALT3                            | _                  | _                 | r · · · J        |         |                     |             |             | _                          |  |  |

|             |                                                | —                               | AN[24]             | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0                            | GPIO[75]           | SIUL              |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT1                            | —                  | —                 |                  |         |                     |             |             |                            |  |  |

| E[11]       | PCR[75]                                        | ALT2                            | —                  | —                 | Input Only       | —       | —                   |             | 65          | 77                         |  |  |

|             |                                                | ALT3                            | —<br>AN[25]        | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0                            |                    | SIUL              |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALTU<br>ALT1                    | GPIO[76]           | 510L              |                  |         |                     |             |             |                            |  |  |

| E[12]       | PCR[76]                                        | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 67          | 79                         |  |  |

|             |                                                | ALT3                            | —                  | —                 | . ,              |         |                     |             |             |                            |  |  |

|             |                                                | —                               | AN[26]             | ADC_0             |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0                            | GPIO[77]           | SIUL              | I/O              |         |                     |             |             |                            |  |  |

|             |                                                | ALT1                            | SCK_3              | DSPI_3            | I/O              |         |                     |             |             |                            |  |  |

| E[13]       | PCR[77]                                        | ALT2                            | —                  | -                 | —                | Slow    | Medium              | —           | 117         | 141                        |  |  |

|             |                                                | ALT3                            |                    | <br>SIUL          | —<br>I           |         |                     |             |             |                            |  |  |

|             |                                                | -                               | EIRQ[25]           |                   |                  |         |                     |             |             |                            |  |  |

|             |                                                | ALT0<br>ALT1                    | GPIO[78]<br>SOUT_3 | SIUL<br>DSPI_3    | I/O<br>O         |         |                     |             |             |                            |  |  |

| E[14]       | PCR[78]                                        | ALT1<br>ALT2                    |                    |                   | _                | Slow    | Medium              | _           | 119         | 143                        |  |  |

| ]           |                                                | ALT3                            | _                  | _                 | _                | 0.011   |                     |             |             |                            |  |  |

|             |                                                | _                               | EIRQ[26]           | SIUL              | I                |         |                     |             |             |                            |  |  |

Table 7 Bin muxing<sup>(1)</sup> (continued)

|             | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                   |                                |                             |                    |         |                     |             |     |                            |  |  |

|-------------|------------------------------------------------|-----------------------------------|--------------------------------|-----------------------------|--------------------|---------|---------------------|-------------|-----|----------------------------|--|--|

| Port        | DCD                                            | Alternate                         |                                | Borinhoral                  | I/O                | Pad s   | peed <sup>(6)</sup> |             | Pin |                            |  |  |

| Port<br>pin | PCR<br>No.                                     | function <sup>(2),</sup><br>(3)   | Functions                      | Peripheral<br>(4)           | direction<br>(5)   | SRC = 0 | SRC = 1             | LQFP<br>100 |     | LQFP<br>176 <sup>(7)</sup> |  |  |

| F[7]        | PCR[87]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[87]<br>—<br>MCKO<br>—     | SIUL<br>—<br>nexus_0<br>—   | I/O<br>  O         | Slow    | Fast                | _           | 19  | 27                         |  |  |

| F[8]        | PCR[88]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[88]<br><br>MSEO1<br>      | SIUL<br>—<br>nexus_0<br>—   | I/O<br>—<br>—<br>— | Slow    | Fast                | _           | 20  | 28                         |  |  |

| F[9]        | PCR[89]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[89]<br>—<br>MSEO0<br>—    | SIUL<br>—<br>nexus_0<br>—   | /O<br>  O<br>      | Slow    | Fast                | _           | 23  | 31                         |  |  |

| F[10]       | PCR[90]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[90]<br><br>EVTO<br>       | SIUL<br>—<br>nexus_0<br>—   | I/O<br>  0<br> -   | Slow    | Fast                | _           | 24  | 32                         |  |  |

| F[11]       | PCR[91]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[91]<br>EVTI<br>—          | SIUL<br>nexus_0<br>—        | I/O<br>I<br>—      | Slow    | Medium              | _           | 25  | 33                         |  |  |

| F[12]       | PCR[92]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[92]<br>ETC[3]<br>—        | SIUL<br>eTimer_1<br>—       | I/O<br>I/O<br>—    | Slow    | Medium              | _           | 106 | 130                        |  |  |

| F[13]       | PCR[93]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[93]<br>ETC[4]<br>—        | SIUL<br>eTimer_1<br>—       | I/O<br>I/O<br>—    | Slow    | Medium              | _           | 112 | 136                        |  |  |

| F[14]       | PCR[94]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[94]<br>TXD<br>—           | SIUL<br>LINFlex_1<br>       | I/O<br>O           | Slow    | Medium              | _           | 115 | 139                        |  |  |

| F[15]       | PCR[95]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[95]<br>—<br>—<br>—<br>RXD | SIUL<br>—<br>—<br>LINFlex_1 | VO<br>   <br>      | Slow    | Medium              | _           | 113 | 137                        |  |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Port  | PCR      | Alternate                         |                                 | Peripheral                  | I/O                     | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |  |

|-------|----------|-----------------------------------|---------------------------------|-----------------------------|-------------------------|---------|---------------------|-------------|-------------|----------------------------|--|

| pin   | No.      | function <sup>(2),</sup><br>(3)   | Functions                       | (4)                         | direction<br>(5)        | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |

| G[8]  | PCR[104] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[104]<br><br>CS3_4<br>      | SIUL<br>—<br>DSPI_4<br>—    | I/O<br>—<br>0<br>—      | Slow    | Medium              | _           | 81          | 97                         |  |

| G[9]  | PCR[105] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[105]<br>—<br>—<br>—<br>RXD | SIUL<br>—<br>—<br>FlexCAN_1 | I/O<br>—<br>—<br>—<br>— | Slow    | Medium              | _           | 79          | 95                         |  |

| G[10] | PCR[106] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[106]<br>—<br>TXD<br>—      | SIUL<br>—<br>FlexCAN_1<br>— | V<br>0                  | Slow    | Medium              | _           | 77          | 93                         |  |

| G[11] | PCR[107] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[107]<br>—<br>—<br>—        | SIUL<br>—<br>—<br>—         | I/O<br>—<br>—           | Slow    | Medium              | _           | 75          | 91                         |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

1. This table concerns Enhanced Full-featured version. Please refer to "SPC56xP54x/SPC56xP60x device configuration difference" table for difference between Enhanced Full-featured, Full-featured, and Airbag configuration.

2. ALT0 is the primary (default) function for each port after reset.

3. Alternate functions are chosen by setting the values of the PCR[PA] bitfields inside the SIU module. PCR[PA] = 00 → ALT0; PCR[PA] = 01 → ALT1; PCR[PA] = 10 → ALT2; PCR[PA] = 11 → ALT3. This is intended to select the output functions; to use one of the input-only functions, the PCR[IBE] bit must be written to '1', regardless of the values selected in the PCR[PA] bitfields. For this reason, the value corresponding to an input only function is reported as "—".

4. Module included on the MCU.

5. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMI[PADSELx] bitfields inside the SIUL module.

6. Programmable via the SRC (Slew Rate Control) bits in the respective Pad Configuration Register.

7. LQFP176 available only as development package.

8. Weak pull down during reset.

| Symbol                                       |    | Parameter                              | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |

|----------------------------------------------|----|----------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

|                                              |    | 2 2 V voltago regulator                | —                                     | 3.0                          | 3.6                          |      |

| $V_{DD_HV_REG}$                              | SR | 3.3 V voltage regulator supply voltage | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

|                                              |    | 3.3 V ADC supply and high              | —                                     | 3.0                          | 5.5                          |      |

| V <sub>DD_HV_AD</sub>                        | SR | reference voltage                      | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | 5.5                          | V    |

| V <sub>SS_HV_AD</sub>                        | SR | ADC ground and low reference voltage   | _                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR | Internal supply voltage                | —                                     | —                            | —                            | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>(3)</sup>     | SR | Internal reference voltage             | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR | Internal supply voltage                | —                                     | —                            | —                            | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR | Internal reference voltage             | —                                     | 0                            | 0                            | V    |

| T <sub>A</sub>                               | SR | Ambient temperature under bias         | _                                     | -40                          | 125                          | °C   |

Table 11. Recommended operating conditions (3.3 V) (continued)

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

Figure 7 shows the constraints of the different power supplies.

# 3.11 DC electrical characteristics

## 3.11.1 DC electrical characteristics (5 V)

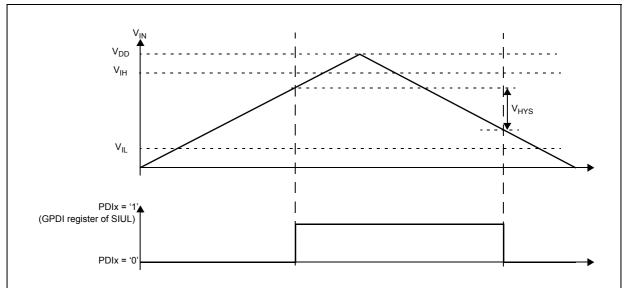

*Table 20* gives the DC electrical characteristics at 5 V ( $4.5 \text{ V} < \text{V}_{\text{DD}_{\text{HV}_{\text{IOX}}}} < 5.5 \text{ V}$ , NVUSRO[PAD3V5V]=0) as described in *Figure 13*.

## Figure 13. I/O input DC electrical characteristics definition

| Table 20. DC electrical chara | acteristics (5.0 V, | NVUSRO[PAD3 | V5V]=0) |

|-------------------------------|---------------------|-------------|---------|

|                               |                     |             |         |

| Symbol              | I | Parameter                            | Conditions              | Min                         | Мах                         | Unit |

|---------------------|---|--------------------------------------|-------------------------|-----------------------------|-----------------------------|------|

| V <sub>IL</sub>     | D | Minimum low level input voltage      | —                       | -0.1 <sup>(1)</sup>         | —                           | V    |

| V <sub>IL</sub>     | Ρ | Maximum level input voltage          | —                       | —                           | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>     | Ρ | Minimum high level input voltage     | —                       | 0.65 V <sub>DD_HV_IOx</sub> | —                           | V    |

| V <sub>IH</sub>     | D | Maximum high level input voltage     | —                       | _                           | $V_{DD_HV_IOx} + 0.1^{(1)}$ | V    |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis           | —                       | 0.1 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_S</sub>   | Ρ | Slow, low level output voltage       | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8V <sub>DD_HV_IOx</sub>   | —                           | V    |

| V <sub>OL_M</sub>   | Ρ | Medium, low level output voltage     | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_M</sub>   | Ρ | Medium, high level output voltage    | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_F</sub>   | Ρ | Fast, low level output voltage       | I <sub>OL</sub> = 3 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_F</sub>   | Ρ | Fast, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |

| V <sub>OL_SYM</sub> | Ρ | Symmetric, low level output voltage  | I <sub>OL</sub> = 3 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |

| Symbo           | I | Parameter                                           | Conditions                        | Min  | Мах | Unit |

|-----------------|---|-----------------------------------------------------|-----------------------------------|------|-----|------|

|                 | Р | Equivalent pull-down current                        | V <sub>IN</sub> = V <sub>IL</sub> | 10   | —   |      |

| I <sub>PD</sub> | F |                                                     | $V_{IN} = V_{IH}$                 | —    | 130 | μA   |

| I <sub>IL</sub> | Р | Input leakage current<br>(all bidirectional ports)  | $T_A = -40$ to 125 °C             | _    | 1   | μA   |

| I <sub>IL</sub> | Ρ | Input leakage current<br>(all ADC input-only ports) | $T_A = -40$ to 125 °C             | _    | 0.5 | μA   |

| C <sub>IN</sub> | D | Input capacitance                                   | —                                 | _    | 10  | pF   |

| 1               | D | RESET, equivalent pull-up current                   | $V_{IN} = V_{IL}$                 | –130 | —   | μA   |

| I <sub>PU</sub> |   |                                                     | $V_{IN} = V_{IH}$                 | _    | -10 | μΛ   |

| 1               | D | RESET, equivalent pull-down                         | $V_{IN} = V_{IL}$                 | 10   | _   | μA   |

| IPD             |   | current                                             | V <sub>IN</sub> = V <sub>IH</sub> |      | 130 | μΑ   |

# Table 22. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V]=1)<sup>(1)</sup> (continued)

1. These specifications are design targets and subject to change per device characterization.

2. "SR" parameter values must not exceed the absolute maximum ratings shown in Table 9.

| Gumbal                  |   |        | Davamatar                                                                         | Canditiana                                                                                         |                          | Va                                                       | lue | Unit |    |  |

|-------------------------|---|--------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------|-----|------|----|--|

| Symbol                  |   |        | Parameter                                                                         | Conditions                                                                                         |                          | Тур                                                      | Мах | Unit |    |  |

|                         |   |        | RUN — Maximum Mode <sup>(1)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V<br>ADC Freq = 32 MHz<br>PLL Freq = 64 MHz | 64 MHz                   | 90                                                       | 120 |      |    |  |

|                         | т |        |                                                                                   |                                                                                                    | 16 MHz                   | 21                                                       | 37  |      |    |  |

|                         | 1 |        | single core <sup>(2)</sup> VDD_LV_CORE       externally forced to 1.3V            |                                                                                                    | 40 MHz                   | 35                                                       | 55  |      |    |  |

|                         |   |        |                                                                                   |                                                                                                    | 64 MHz                   | 48                                                       | 72  |      |    |  |

|                         |   |        |                                                                                   | 16 MHz                                                                                             | 24                       | 41                                                       |     |      |    |  |

| I <sub>DD_LV_CORE</sub> |   |        |                                                                                   |                                                                                                    | 40 MHz                   | 42                                                       | 64  |      |    |  |

|                         |   |        |                                                                                   |                                                                                                    | 64 MHz                   | 58                                                       | 85  |      |    |  |

|                         |   | Supply | RUN — Maximum Mode <sup>(4)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V                                           | 64 MHz                   | 85                                                       | 113 | mA   |    |  |

|                         | Ρ | Р      | current                                                                           | current                                                                                            | HALT Mode <sup>(5)</sup> | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V | _   | 5.5  | 15 |  |

|                         |   |        | STOP Mode <sup>(6)</sup>                                                          | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V                                           | _                        | 4.5                                                      | 13  |      |    |  |

|                         | D |        | Flash memory supply current during read                                           | V <sub>DD_HV_FL</sub> at 3.3 V                                                                     | _                        | _                                                        | 14  |      |    |  |

| I <sub>DD_FLASH</sub>   |   |        | Flash memory supply current<br>during erase operation on 1<br>flash memory module | V <sub>DD_HV_FL</sub> at 3.3 V                                                                     | _                        | _                                                        | 42  |      |    |  |

| I <sub>DD_ADC</sub>     | Т |        | ADC supply current —<br>Maximum Mode                                              | V <sub>DD_HV_AD</sub> at 3.3 V<br>ADC Freq = 16 MHz                                                | _                        | 3                                                        | 4   |      |    |  |

| I <sub>DD_OSC</sub>     | Т |        | OSC supply current                                                                | V <sub>DD_OSC</sub> at 3.3 V                                                                       | 8 MHz                    | 2.4                                                      | 3   |      |    |  |

Maximum mode configuration: Code fetched from Flash executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- RAM, Code and Data Flash powered, code fetched from Flash executed by single core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- RAM, Code and Data Flash powered, code fetched from Flash executed by dual core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- Maximum mode configuration: Code fetched from RAM executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- 5. HALT mode configuration, only for the "P" classification: Code Flash memory in low power mode, data Flash memory in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

- STOP mode configuration, only for the "P" classification: Code and data Flash memories in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

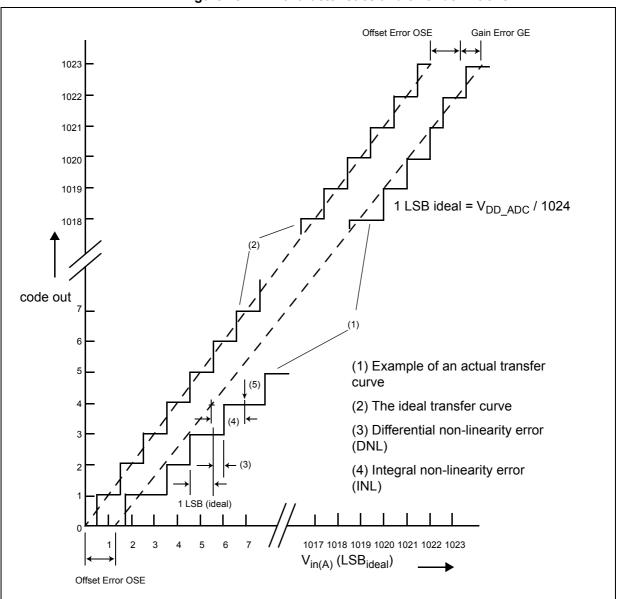

Figure 15. ADC characteristics and error definitions

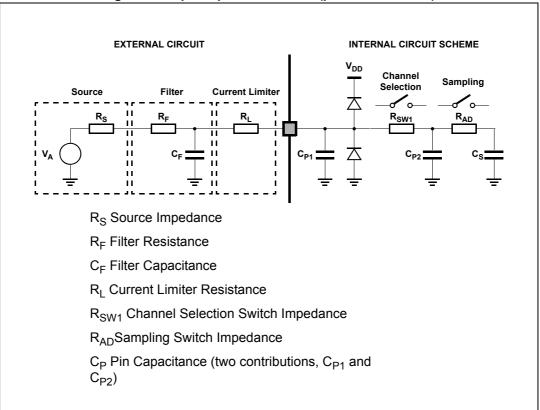

## 3.15.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high-frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuate the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

DocID18340 Rev 6

The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance: being  $C_S$  and  $C_{P2}$  substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S + C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc \times (C_S + C_{P2}))$ ), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S + C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the *Equation 4*:

### **Equation 4**

$$V_A \times \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

*Equation 4* generates a constraint for external network design, in particular on resistive path. Internal switch resistances ( $R_{SW}$  and  $R_{AD}$ ) can be neglected with respect to external resistances.

Figure 16. Input equivalent circuit (precise channels)

# 3.15.2 ADC conversion characteristics

| Symbol                          |    | Doromotor                                                                                                                  | Conditions <sup>(1)</sup>                                                                               |                        | Unit |                                |      |

|---------------------------------|----|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------|------|--------------------------------|------|

|                                 |    | Parameter                                                                                                                  | Conditions                                                                                              | Min                    | Тур  | Мах                            | Unit |

| V <sub>INAN</sub>               | SR | Analog input voltage <sup>(2)</sup>                                                                                        | _                                                                                                       | $V_{SS\_HV\_AD} - 0.3$ | _    | V <sub>SS_HV_AD</sub><br>+ 0.3 | V    |

| f <sub>CK</sub>                 | SR | ADC Clock frequency<br>(depends on ADC<br>configuration)<br>(The duty cycle depends on<br>AD_clk <sup>(3)</sup> frequency) | _                                                                                                       | 3 <sup>(4)</sup>       | _    | 60                             | MHz  |

| f <sub>s</sub>                  | SR | Sampling frequency                                                                                                         | _                                                                                                       | _                      | _    | 1.53                           | MHz  |

| +                               | D  | Sample time <sup>(5)</sup>                                                                                                 | f <sub>ADC</sub> = 20 MHz,<br>INPSAMP = 3                                                               | 125                    | _    | _                              | ns   |

| t <sub>ADC_S</sub>              |    |                                                                                                                            | f <sub>ADC</sub> = 9 MHz,<br>INPSAMP = 255                                                              | —                      | _    | 28.2                           | μs   |

| t <sub>ADC_C</sub>              | Ρ  | Conversion time <sup>(6)</sup>                                                                                             | $f_{ADC} = 20 \text{ MHz}^{(7)},$<br>INPCMP = 1                                                         | 0.650                  | _    | _                              | μs   |

| C <sub>S</sub> <sup>(8)</sup>   | D  | ADC input sampling capacitance                                                                                             | _                                                                                                       | —                      | _    | 2.5                            | pF   |

| C <sub>P1</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 1                                                                                                | _                                                                                                       | —                      | _    | 3                              | pF   |

| C <sub>P2</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 2                                                                                                | _                                                                                                       | —                      | _    | 1                              | pF   |

| C <sub>P3</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 3                                                                                                | _                                                                                                       | —                      | _    | 1                              | pF   |

| R <sub>SW1</sub> <sup>(8)</sup> | D  | Internal resistance of analog source                                                                                       | $V_{DD_HV_AD} = 5 V \pm 10\%$                                                                           | —                      | _    | 0.6                            | kΩ   |

| INSW1                           | D  |                                                                                                                            | V <sub>DD_HV_AD</sub> = 3.3 V ±10%                                                                      |                        | _    | 3                              | kΩ   |

| R <sub>SW2</sub> <sup>(8)</sup> | D  | Internal resistance of analog source                                                                                       | $V_{DD_HV_AD}$ = 5 V ±10%                                                                               |                        | _    | 2.15                           | kΩ   |

| TSW2                            | D  |                                                                                                                            | V <sub>DD_HV_AD</sub> = 3.3 V ±10%                                                                      |                        | _    | 3.6                            | kΩ   |

| R <sub>AD</sub> <sup>(8)</sup>  | D  | Internal resistance of analog source                                                                                       | _                                                                                                       | _                      | _    | 2                              | kΩ   |

| I <sub>INJ</sub>                | т  | Input current injection                                                                                                    | Current injection on one ADC<br>input, different from the<br>converted one. Remains<br>within TUE spec. | -5                     | _    | 5                              | mA   |

| INL                             | Ρ  | Integral Non Linearity No overload                                                                                         |                                                                                                         | —                      | ±1.5 | -                              | LSB  |

| DNL                             | Ρ  | Differential Non Linearity                                                                                                 | No overload                                                                                             | -1.0                   | _    | 1.0                            | LSB  |

| OFS                             | Т  | Offset error — —                                                                                                           |                                                                                                         | ±1                     | _    | LSB                            |      |

| GNE                             | Т  | Gain error         —         ±1         –                                                                                  |                                                                                                         |                        | LSB  |                                |      |

| TUE                             | Ρ  | Total unadjusted error<br>without current injection                                                                        | 16 precision channels                                                                                   | -2.5                   |      | 2.5                            | LSB  |

g. The output drive provided is open drain and hence must be terminated by an external resistor of value 1 k $\Omega$ .

| Course to a l      |          | с  | Demonstra                                                                                      | •                                                                                         |                     |     |                      |      |  |

|--------------------|----------|----|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|-----|----------------------|------|--|

| Symbo              | Symbol ( |    | Parameter                                                                                      | Conditions <sup>(1)</sup>                                                                 | Min                 | Тур | Max                  | Unit |  |

| V <sub>IH</sub>    | SR       | Ρ  | Input High Level CMOS<br>(Schmitt Trigger)                                                     | —                                                                                         | 0.65V <sub>DD</sub> | —   | V <sub>DD</sub> +0.4 | V    |  |

| V <sub>IL</sub>    | SR       | Ρ  | Input low Level CMOS<br>(Schmitt Trigger)                                                      | —                                                                                         | -0.4                | _   | 0.35V <sub>DD</sub>  | V    |  |

| V <sub>HYS</sub>   | сс       | С  | Input hysteresis CMOS<br>(Schmitt Trigger)                                                     | —                                                                                         | 0.1V <sub>DD</sub>  | _   | _                    | V    |  |

|                    |          |    |                                                                                                | Push Pull, $I_{OL}$ = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | _                   |     | 0.1V <sub>DD</sub>   | V    |  |

| V <sub>OL</sub> CO | сс       | Ρ  | Output low level                                                                               | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>   | —                   | _   | 0.1V <sub>DD</sub>   |      |  |

|                    |          |    |                                                                                                | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | _                   | _   | 0.5                  |      |  |

| T <sub>tr</sub> CC |          |    | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                        |                                                                                           | _                   | _   | 10                   |      |  |

|                    |          | DO |                                                                                                |                                                                                           |                     | 20  |                      |      |  |

|                    | <u> </u> |    |                                                                                                |                                                                                           | —                   | _   | 40                   | - ns |  |

|                    |          |    |                                                                                                |                                                                                           | —                   | _   | 12                   |      |  |

|                    |          |    |                                                                                                |                                                                                           | _                   | _   | 25                   |      |  |

|                    |          |    |                                                                                                | _                                                                                         |                     | 40  |                      |      |  |

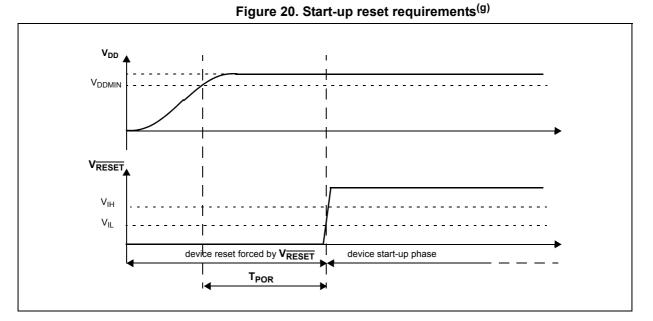

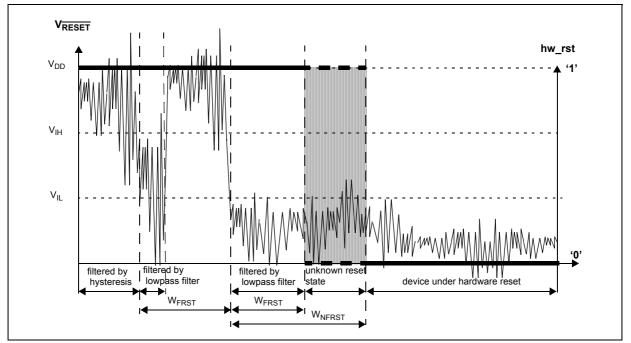

| W <sub>FRST</sub>  | SR       | Ρ  | RESET input filtered pulse                                                                     |                                                                                           | —                   |     | 40                   | ns   |  |

| W <sub>NFRST</sub> | SR       | Ρ  | RESET input not filtered pulse                                                                 | _                                                                                         | 500                 | _   | _                    | ns   |  |

| T <sub>POR</sub>   | сс       | D  | maximum delay before<br>internal reset is released<br>after all VDD_HV reach<br>nominal supply |                                                                                           |                     | _   | 1                    | ms   |  |

|                    |          | Ρ  | P Weak pull-up current absolute value                                                          | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                                | 10                  | —   | 150                  | μA   |  |

| I <sub>WPU</sub>   | СС       |    |                                                                                                | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                                                | 10                  | _   | 150                  |      |  |

|                    |          |    |                                                                                                | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(4)</sup>                                 | 10                  | —   | 250                  |      |  |

## Table 37. RESET electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40  $^{\circ}C$  to  $T_{A\mbox{ MAX}},$  unless otherwise specified.

2. This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of device reference manual).

3. C<sub>L</sub> includes device and package capacitance (C<sub>PKG</sub> < 5 pF).

The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

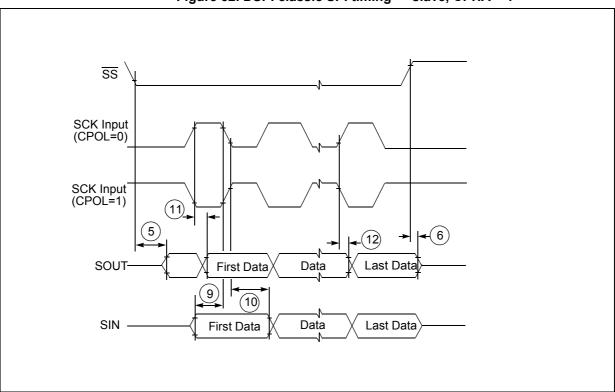

Figure 32. DSPI classic SPI timing — slave, CPHA = 1

DocID18340 Rev 6

# 5 Ordering information

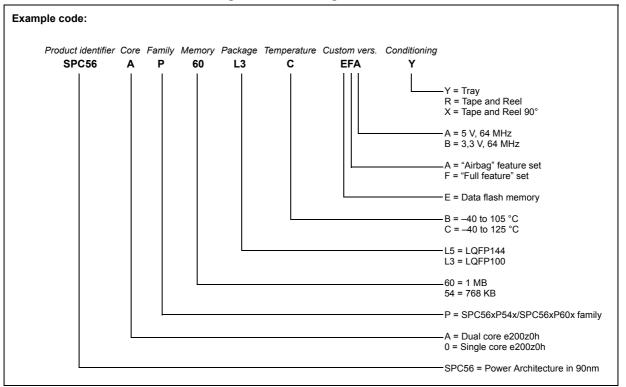

# Figure 40. Ordering information scheme<sup>(h)</sup>

h. Not all configurations are available on the market. Please contact your ST sales representative to get the list of orderable commercial part number.

# 6 Revision history

Table 44 summarizes revisions to this document.

| Date        | Revision | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|