#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p54l5beaay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

## 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the SPC56xP54x/SPC56xP60x series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications specifically the airbag application.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 1.3 Device comparison

*Table 2* provides a summary of different members of the SPC56xP54x/SPC56xP60x family and their features—relative to Full-featured version—to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                                   | SPC560P54 | SPC560P60       | SPC56AP54        | SPC56AP60 |

|-----------------------------------------------------------|-----------|-----------------|------------------|-----------|

| Code Flash memory (with ECC)                              | 768 KB    | 1 MB            | 768 KB           | 1 MB      |

| Data Flash / EE (with ECC)                                |           | 64              | KB               |           |

| SRAM (with ECC)                                           | 64 KB     | 80 KB           | 64 KB            | 80 KB     |

| Processor core                                            | 32-bit e  | 200z0h          | 32-bit Dua       | l e200z0h |

| Instruction set                                           |           | VI              | Ē                |           |

| CPU performance                                           |           | 0-64            | MHz              |           |

| FMPLL (frequency-modulated phase-<br>locked loop) modules |           |                 | 1                |           |

| INTC (interrupt controller) channels                      |           | 14              | 48               |           |

| PIT (periodic interrupt timer)                            |           | 1 (includes fou | r 32-bit timers) |           |

Table 2. SPC56xP54x/SPC56xP60x device comparison

SPC56xP54x/SPC56xP60x is present on the market in two different options enabling different features: Full-featured, and Airbag configuration. *Table 3* shows the main differences between the two versions.

## Table 3. SPC56xP54x/SPC56xP60x device configuration difference

| Feature                                             | Enhanced<br>Full-featured | Full-featured | Airbag |

|-----------------------------------------------------|---------------------------|---------------|--------|

| FlexCAN (controller area network)                   | 3                         | 2             | 2      |

| CTU (cross triggering unit)                         | Ye                        | es            | No     |

| FlexRay                                             | Yes (64 mes               | sage buffer)  | No     |

| DSPI (deserial serial peripheral interface) modules | Į                         | 5             | 4      |

| CRC (cyclic redundancy check) unit                  | 2                         | 2             | 1      |

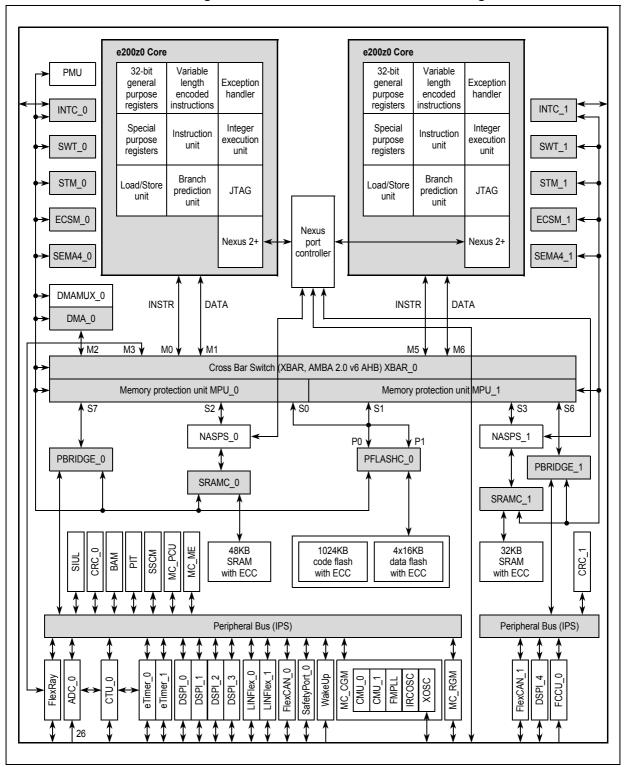

# 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC56xP54x/SPC56xP60x MCU. *Table 4* summarizes the functions of the blocks.

Figure 1. SPC56xP54x/SPC56xP60x block diagram

DocID18340 Rev 6

# 2 Package pinouts and signal descriptions

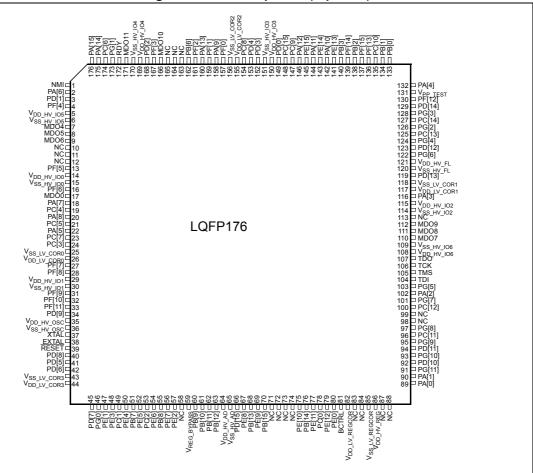

# 2.1 Package pinouts

The LQFP pinouts are shown in the following figures.

b. Software development package only. Not available for production.

|             |            | Alternate                              |                                                                | e 7. Pin mux                                            | I/O                       | ,       | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|----------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3)        | Functions                                                      | Peripheral<br>(4)                                       | direction<br>(5)          | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             | •          | •                                      |                                                                | Po                                                      | ort B                     |         |                     |             |             |                            |

| B[0]        | PCR[16]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[16]<br>TXD<br>ETC[2]<br>DEBUG[0]<br>EIRQ[15]              | SIUL<br>FlexCAN_0<br>eTimer_1<br>SSCM<br>SIUL           | I/O<br>O<br>I/O<br>I      | Slow    | Medium              | 76          | 109         | 133                        |

| B[1]        | PCR[17]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[17]<br>CS7_1<br>ETC[3]<br>DEBUG[1]<br>RXD<br>EIRQ[16]     | SIUL<br>DSPI_1<br>eTimer_1<br>SSCM<br>FlexCAN_0<br>SIUL | I/O<br>O<br>I/O<br>I<br>I | Slow    | Medium              | 77          | 110         | 134                        |

| B[2]        | PCR[18]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[18]<br>TXD<br>SOUT_4<br>DEBUG[2]<br>EIRQ[17]              | SIUL<br>LINFlex_0<br>DSPI_4<br>SSCM<br>SIUL             | 1/0<br>0<br>1/0<br>-      | Slow    | Medium              | 79          | 114         | 138                        |

| B[3]        | PCR[19]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[19]<br>—<br>SCK_4<br>DEBUG[3]<br>RXD                      | SIUL<br>—<br>DSPI_4<br>SSCM<br>LINFlex_0                | ₩<br>₩<br>₩<br>₩<br>₩     | Slow    | Medium              | 80          | 116         | 140                        |

| B[6]        | PCR[22]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[22]<br>clk_out<br>CS2_2<br>clk_out_div2<br>56<br>EIRQ[18] | SIUL<br>MC_CGL<br>DSPI_2<br>MC_CGL<br>SIUL              | ₩<br>0<br>0<br>1          | Slow    | Medium              | 96          | 138         | 162                        |

| B[7]        | PCR[23]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[23]<br>—<br>—<br>AN[0]<br>RXD                             | SIUL<br>—<br>—<br>ADC_0<br>LINFlex_0                    | Input Only                | —       | _                   | 29          | 43          | 51                         |

| B[8]        | PCR[24]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[24]<br>—<br>—<br>—<br>AN[1]<br>ETC[5]                     | SIUL<br>—<br>—<br>ADC_0<br>eTimer_0                     | Input Only                | _       | _                   | 31          | 47          | 55                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Dent        | DOD        | Alternate                       |           |                   | I/O              | -       | peed <sup>(6)</sup> |        | Pin         |                            |    |

|-------------|------------|---------------------------------|-----------|-------------------|------------------|---------|---------------------|--------|-------------|----------------------------|----|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 0 SRC = 1     |        | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |    |

|             | <u>.</u>   |                                 |           | Po                | ort C            |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[32]  | SIUL              |                  |         |                     |        |             |                            |    |

|             |            | ALT1                            | —         | —                 |                  |         |                     |        |             |                            |    |

| C[0]        | PCR[32]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 45     | 66          | 78                         |    |

|             |            | ALT3                            | —         | —                 |                  |         |                     |        |             |                            |    |

|             |            |                                 | AN[19]    | ADC_0             |                  |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[33]  | SIUL              |                  |         |                     |        |             |                            |    |

|             |            | ALT1                            | —         | —                 |                  |         |                     |        |             |                            |    |

| C[1]        | PCR[33]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 28     | 41          | 49                         |    |

|             |            | ALT3                            | —         | —                 |                  |         |                     |        |             |                            |    |

|             |            | —                               | AN[2]     | ADC_0             |                  |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[34]  | SIUL              |                  |         |                     |        |             |                            |    |

|             |            | ALT1                            | —         | —                 |                  |         |                     |        |             |                            |    |

| C[2]        | PCR[34]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 30     | 45          | 53                         |    |

|             |            | ALT3                            | —         | —                 |                  |         |                     |        |             |                            |    |

|             |            |                                 | AN[3]     | ADC_0             |                  |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[35]  | SIUL              | I/O              |         |                     |        |             |                            |    |

|             |            | ALT1                            | CS1_0     | DSPI_0            | 0                |         |                     |        |             |                            |    |

| C[3]        | PCR[35]    | PCR[35]                         | ALT2      | ETC[4]            | eTimer_1         | I/O     | Slow                | Medium | 10          | 16                         | 24 |

|             |            | ALT3                            | TXD       | LINFlex_1         | 0                |         |                     |        |             |                            |    |

|             |            | —                               | EIRQ[21]  | SIUL              | I                |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[36]  | SIUL              | I/O              |         |                     |        |             |                            |    |

|             |            | ALT1                            | CS0_0     | DSPI_0            | I/O              |         |                     |        |             |                            |    |

| C[4]        | PCR[36]    | ALT2                            | —         | —                 | —                | Slow    | Medium              | 5      | 11          | 19                         |    |

|             |            | ALT3                            | DEBUG[4]  | SSCM              |                  |         |                     |        |             |                            |    |

|             |            |                                 | EIRQ[22]  | SIUL              | I                |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[37]  | SIUL              | I/O              |         |                     |        |             |                            |    |

|             |            | ALT1                            | SCK_0     | DSPI_0            | I/O              |         |                     |        |             |                            |    |

| C[5]        | PCR[37]    | ALT2                            | SCK_4     | DSPI_4            | I/O              | Slow    | Medium              | 7      | 13          | 21                         |    |

|             |            | ALT3                            | DEBUG[5]  | SSCM              | _                |         |                     |        |             |                            |    |

|             |            |                                 | EIRQ[23]  | SIUL              | I                |         |                     |        |             |                            |    |

|             |            | ALT0                            | GPIO[38]  | SIUL              | I/O              |         |                     |        |             |                            |    |

|             |            | ALT1                            | SOUT_0    | DSPI_0            | 0                |         |                     | • -    |             |                            |    |

| C[6]        | PCR[38]    | ALT2                            | —         | —                 | —                | Slow    | Medium              | 98     | 142         | 174                        |    |

|             |            | ALT3                            | DEBUG[6]  | SSCM              |                  |         |                     |        |             |                            |    |

|             |            | —                               | EIRQ[24]  | SIUL              | I                |         |                     |        |             |                            |    |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |            | Alternate                       |           |                   | J/O              | -       | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|---------------------------------|-----------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |            | •                               |           | Po                | ort G            |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[96]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | F[0]      | FCCU              | 0                |         |                     |             |             |                            |

| G[0]        | PCR[96]    | ALT2                            | —         | —                 | —                | Slow    | Medium              | —           | 38          | 46                         |

|             |            | ALT3                            | —         | —                 | —                |         |                     |             |             |                            |

|             |            | —                               | EIRQ[30]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[97]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | F[1]      | FCCU              | 0                |         |                     |             |             |                            |

| G[1]        | PCR[97]    | ALT2                            | —         | —                 | —                | Slow    | Medium              |             | 141         | 173                        |

|             |            | ALT3                            |           | _                 | _                |         |                     |             |             |                            |

|             |            |                                 | EIRQ[31]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[98]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | —         | —                 | —                |         |                     | _           | 102         |                            |

| G[2]        | PCR[98]    | ALT2                            | —         | —                 | —                | Slow    | Medium              |             |             | 126                        |

|             |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|             |            | —                               | SIN_4     | DSPI_4            | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[99]  | SIUL              | I/O              |         |                     |             |             |                            |

| G[3]        | PCR[99]    | ALT1                            |           | —                 | _                | Slow    | Medium              | Medium —    | 104         | 128                        |

|             |            | ALT2                            | SOUT_4    | DSPI_4            | 0                |         |                     |             |             |                            |

|             |            | ALT3                            |           | —                 | —                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[100] | SIUL              | I/O              |         |                     |             |             |                            |

| G[4]        | PCR[100]   | ALT1                            | —         | —                 | —                | Slow    | Medium              |             | 100         | 124                        |

|             |            | ALI2                            | SCK_4     | DSPI_4            | I/O              |         |                     |             |             |                            |

|             |            | ALT3                            |           | —                 |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[101] | SIUL              | I/O              |         |                     |             |             |                            |

| G[5]        | PCR[101]   | ALT1                            | _         |                   | —                | Slow    | Medium              | _           | 85          | 103                        |

|             |            | ALIZ                            | CS0_4     | DSPI_4            | I/O              |         |                     |             |             |                            |

|             |            | ALT3                            |           |                   |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[102] | SIUL              | I/O              |         |                     |             |             |                            |

| G[6]        | PCR[102]   | ALT1                            |           |                   | _                | Slow    | Medium              |             | 98          | 122                        |

|             |            | ALT2                            | CS1_4     | DSPI_4            | 0                |         |                     |             |             |                            |

|             |            | ALT3                            | _         |                   |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[103] | SIUL              | I/O              |         |                     |             |             | 101                        |

| G[7]        | PCR[103]   | ALT1                            |           |                   |                  | Slow    | Medium              |             | 83          |                            |

|             |            | ALT2<br>ALT3                    | CS2_4     | DSPI_4            | 0                |         |                     |             |             |                            |

|             |            | ALIS                            | _         | _                 | _                |         |                     |             |             |                            |

# Table 7. Pin muxing<sup>(1)</sup> (continued)

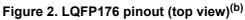

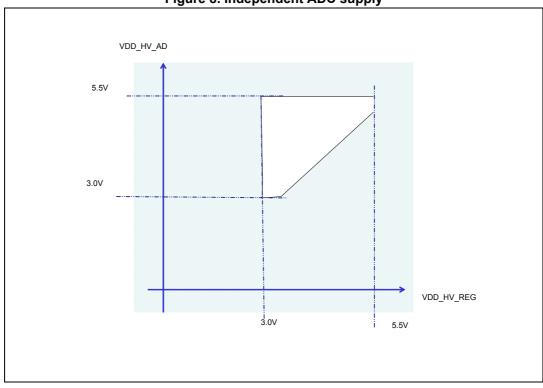

# Figure 6. Independent ADC supply<sup>(e)</sup>

#### **Recommended operating conditions** 3.4

| Table 10. Recommended | operating co | nditions (5.0 | V) |

|-----------------------|--------------|---------------|----|

|                       |              |               |    |

| Symbol                                |                                     | Parameter                                               | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |

|---------------------------------------|-------------------------------------|---------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| V <sub>SS_HV</sub>                    | SR                                  | Digital ground                                          | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR                                  | 5.0 V input/output supply voltage                       | _                                     | 4.5                          | 5.5                          | V    |

| V <sub>SS_HV_IOx</sub>                | SR                                  | Input/output ground voltage                             | —                                     | 0                            | 0                            | V    |

|                                       |                                     | 5.0 V code and data flash                               | —                                     | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_FL</sub>                 | L SR memory supply voltage Relative | Relative to<br>V <sub>DD_HV_IOx</sub>                   | V <sub>DD_HV_IOx</sub> -0.1           | V <sub>DD_HV_IOx</sub> + 0.1 | V                            |      |

| V <sub>SS_HV_FL</sub>                 | SR                                  | Code and data flash<br>memory ground                    | _                                     | 0                            | 0                            | V    |

|                                       |                                     | 5.0.V. crystal oscillator                               | —                                     | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_OSC</sub>                | SR                                  | 5.0 V crystal oscillator<br>amplifier supply voltage    | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1  | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_OSC</sub>                | SR                                  | 5.0 V crystal oscillator<br>amplifier reference voltage |                                       | 0                            | 0                            | V    |

e. Device design targets the removal of this conditions. To be confirmed by design during device validation.

| Symbol                                       |                                           | Parameter                            | Conditions Min                        |                              | Max <sup>(1)</sup>           | Unit |  |

|----------------------------------------------|-------------------------------------------|--------------------------------------|---------------------------------------|------------------------------|------------------------------|------|--|

|                                              |                                           | 2 2 V voltago regulator              | —                                     | 3.0                          | 3.6                          |      |  |

| $V_{DD_HV_REG}$                              | SR 3.3 V voltage regulator supply voltage |                                      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |  |

|                                              |                                           | 3.3 V ADC supply and high            | —                                     | 3.0                          | 5.5                          |      |  |

| V <sub>DD_HV_AD</sub>                        | SR                                        | reference voltage                    | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | 5.5                          | V    |  |

| V <sub>SS_HV_AD</sub>                        | SR                                        | ADC ground and low reference voltage | _                                     | 0                            | 0                            | V    |  |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR                                        | Internal supply voltage              | —                                     | —                            | —                            | V    |  |

| V <sub>SS_LV_REGCOR</sub> <sup>(3)</sup>     | SR                                        | Internal reference voltage           | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR                                        | Internal supply voltage              | —                                     | —                            | —                            | V    |  |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR                                        | Internal reference voltage           | —                                     | 0                            | 0                            | V    |  |

| T <sub>A</sub>                               | SR                                        | Ambient temperature under bias       | _                                     | -40                          | 125                          | °C   |  |

Table 11. Recommended operating conditions (3.3 V) (continued)

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

Figure 7 shows the constraints of the different power supplies.

## Figure 8. Independent ADC supply

# 3.5 Thermal characteristics

#### Table 12. Thermal characteristics for 144-pin LQFP

| Symbol             |   | Parameter                                                                 | Conditions            | Typical value | Unit |

|--------------------|---|---------------------------------------------------------------------------|-----------------------|---------------|------|

| Р                  | D | Thermal resistance junction-to-ambient, natural convection <sup>(1)</sup> | Single layer board—1s | 53.4          | °C/W |

| $R_{	heta JA}$     | D | natural convection <sup>(1)</sup>                                         | Four layer board—2s2p | 43.9          | °C/W |

| $R_{\theta JB}$    | D | Thermal resistance junction-to-board <sup>(2)</sup>                       | Four layer board—2s2p | 29.6          | °C/W |

| $R_{\theta JCtop}$ | D | Thermal resistance junction-to-case $(top)^{(3)}$                         | Single layer board—1s | 9.3           | °C/W |

| $\Psi_{JB}$        | D | Junction-to-board, natural convection <sup>(4)</sup>                      | Operating conditions  | 29.8          | °C/W |

| $\Psi_{JC}$        | D | Junction-to-case, natural convection <sup>(5)</sup>                       | Operating conditions  | 1.3           | °C/W |

1. Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

2. Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

4. Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

5. Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

| Symbol              |                                                     | Parameter                                                                 | Conditions            | Typical value | Unit |  |  |

|---------------------|-----------------------------------------------------|---------------------------------------------------------------------------|-----------------------|---------------|------|--|--|

| P                   | D                                                   | Thermal resistance junction-to-ambient, natural convection <sup>(1)</sup> | Single layer board—1s | 47.3          | °C/W |  |  |

| IN⊕JA               | $R_{\theta JA}$ D natural convection <sup>(1)</sup> |                                                                           | Four layer board—2s2p | 35.6          | °C/W |  |  |

| $R_{	hetaJB}$       | D                                                   | Thermal resistance junction-to-board <sup>(2)</sup>                       | Four layer board—2s2p | 19.1          | °C/W |  |  |

| R <sub>0JCtop</sub> | D                                                   | Thermal resistance junction-to-case (top) <sup>(3)</sup>                  | Single layer board—1s | 9.1           | °C/W |  |  |

| $\Psi_{JB}$         | D                                                   | Junction-to-board, natural convection <sup>(4)</sup>                      | Operating conditions  | 19.1          | °C/W |  |  |

| $\Psi_{JC}$         | D                                                   | Junction-to-case, natural convection <sup>(5)</sup>                       | Operating conditions  | 1.1           | °C/W |  |  |

Table 13. Thermal characteristics for 100-pin LQFP

1. Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

2. Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

4. Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

5. Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

## 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

Equation 1  $T_J = T_A + (R_{\theta JA} \times P_D)$

where:

$T_A$  = ambient temperature for the package (<sup>o</sup>C)

$R_{\theta JA}$ = junction to ambient thermal resistance (<sup>o</sup>C/W)

$P_D$ = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

## Equation 2 $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta,JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta,IC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

# 3.11 DC electrical characteristics

## 3.11.1 DC electrical characteristics (5 V)

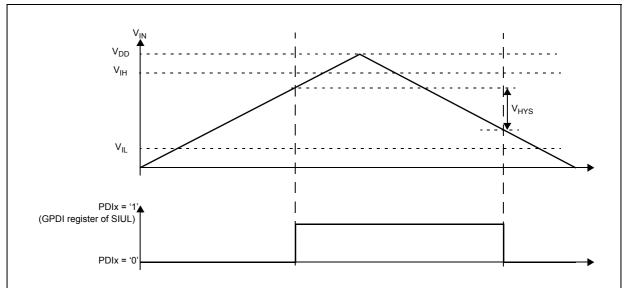

*Table 20* gives the DC electrical characteristics at 5 V ( $4.5 \text{ V} < \text{V}_{\text{DD}_{\text{HV}_{\text{IOX}}}} < 5.5 \text{ V}$ , NVUSRO[PAD3V5V]=0) as described in *Figure 13*.

## Figure 13. I/O input DC electrical characteristics definition

| Table 20. DC electrical chara | acteristics (5.0 V, | NVUSRO[PAD3 | V5V]=0) |

|-------------------------------|---------------------|-------------|---------|

|                               |                     |             |         |

| Symbol              |   | Parameter                            | Conditions              | Min                         | Мах                                                | Unit |

|---------------------|---|--------------------------------------|-------------------------|-----------------------------|----------------------------------------------------|------|

| V <sub>IL</sub>     | D | Minimum low level input voltage      | —                       | -0.1 <sup>(1)</sup>         | —                                                  | V    |

| V <sub>IL</sub>     | Ρ | Maximum level input voltage          | —                       | —                           | 0.35 V <sub>DD_HV_IOx</sub>                        | V    |

| V <sub>IH</sub>     | Ρ | Minimum high level input voltage     | —                       | 0.65 V <sub>DD_HV_IOx</sub> | —                                                  | V    |

| V <sub>IH</sub>     | D | Maximum high level input voltage     | _                       | —                           | $V_{\text{DD}\_\text{HV}\_\text{IOx}} + 0.1^{(1)}$ | V    |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis           | —                       | 0.1 V <sub>DD_HV_IOx</sub>  | —                                                  | V    |

| V <sub>OL_S</sub>   | Ρ | Slow, low level output voltage       | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>                         | V    |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8V <sub>DD_HV_IOx</sub>   | —                                                  | V    |

| V <sub>OL_M</sub>   | Ρ | Medium, low level output voltage     | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>                         | V    |

| V <sub>OH_M</sub>   | Ρ | Medium, high level output voltage    | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | —                                                  | V    |

| V <sub>OL_F</sub>   | Ρ | Fast, low level output voltage       | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>                         | V    |

| V <sub>OH_F</sub>   | Ρ | Fast, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | —                                                  | V    |

| V <sub>OL_SYM</sub> | Ρ | Symmetric, low level output voltage  | I <sub>OL</sub> = 3 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>                         | V    |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | _                                                  | V    |

| Symbo             | I  | Parameter                                           | Conditions                        | Min  | Мах | Unit |

|-------------------|----|-----------------------------------------------------|-----------------------------------|------|-----|------|

| 1                 | Р  | Equivalent pull-up current                          | $V_{IN} = V_{IL}$                 | -130 | _   |      |

| I <sub>PU</sub>   | 1  | Equivalent puil-up current                          | $V_{IN} = V_{IH}$                 | _    | -10 | μA   |

|                   | Р  | Equivalent pull-down current                        | $V_{IN} = V_{IL}$                 | 10   | —   |      |

| I <sub>PD</sub>   | Г  | Equivalent puil-down current                        | $V_{IN} = V_{IH}$                 |      | 130 | μA   |

| Ι <sub>ΙL</sub>   | Ρ  | Input leakage current<br>(all bidirectional ports)  | T <sub>A</sub> =40 to 125 °C      | -1   | 1   | μA   |

| IIL               | Ρ  | Input leakage current<br>(all ADC input-only ports) | T <sub>A</sub> = -40 to 125 °C    | -0.5 | 0.5 | μA   |

| C <sub>IN</sub>   | D  | Input capacitance                                   | —                                 | _    | 10  | pF   |

| 1                 | D  | RESET, equivalent pull-up current                   | V <sub>IN</sub> = V <sub>IL</sub> | -130 | _   |      |

| I <sub>PU</sub>   |    |                                                     | $V_{IN} = V_{IH}$                 | —    | -10 | μA   |

| 1                 |    |                                                     | V <sub>IN</sub> = V <sub>IL</sub> | 10   |     |      |

| I <sub>PD</sub> D | 1) |                                                     | V <sub>IN</sub> = V <sub>IH</sub> | _    | 130 | μA   |

## Table 20. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V]=0) (continued)

1. "SR" parameter values must not exceed the absolute maximum ratings shown in *Table 9*.

| Symbol                |   | Parameter |                                                        | Conditions                                                                                      |                                | Value                                                 |                                | Unit |    |    |  |

|-----------------------|---|-----------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------|--------------------------------|------|----|----|--|

|                       |   |           | Parameter                                              | Conditions                                                                                      |                                | Тур                                                   | Мах                            | Unit |    |    |  |

|                       |   |           | RUN — Maximum Mode <sup>(1)</sup>                      | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V<br>ADC Freq = 32 MHz<br>PLL Freq = 64 MHz | 64 MHz                         | 90                                                    | 120                            |      |    |    |  |

|                       |   |           |                                                        |                                                                                                 | 16 MHz                         | 21                                                    | 37                             |      |    |    |  |

|                       | Т |           | RUN - Platform consumption, single core <sup>(2)</sup> |                                                                                                 | 40 MHz                         | 35                                                    | 55                             |      |    |    |  |

|                       |   |           | 5                                                      | VDD_LV_CORE                                                                                     | 64 MHz                         | 48                                                    | 72                             |      |    |    |  |

|                       |   |           | externally forced to 1.3V                              | 16 MHz                                                                                          | 24                             | 41                                                    |                                |      |    |    |  |

| IDD_LV_CORE           |   |           | RUN - Platform consumption, dual core <sup>(3)</sup>   |                                                                                                 | 40 MHz                         | 42                                                    | 64                             |      |    |    |  |

|                       |   |           |                                                        | 64 MHz                                                                                          | 58                             | 85                                                    |                                |      |    |    |  |

|                       | Ρ | Supply    | RUN — Maximum Mode <sup>(4)</sup>                      | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V                                           | 64 MHz                         | 85                                                    | 113                            | mA   |    |    |  |

|                       |   | current   | HALT Mode <sup>(5)</sup>                               | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V                                           | _                              | 5.5                                                   | 15                             |      |    |    |  |

|                       |   |           |                                                        |                                                                                                 | STOP Mode <sup>(6)</sup>       | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V | _                              | 4.5  | 13 |    |  |

|                       | т | т         |                                                        |                                                                                                 |                                | Flash memory supply current during read               | V <sub>DD_HV_FL</sub> at 5.0 V | _    |    | 14 |  |

| I <sub>DD_FLASH</sub> |   |           | Flash memory supply current                            |                                                                                                 | V <sub>DD_HV_FL</sub> at 5.0 V | _                                                     | _                              | 42   |    |    |  |

| I <sub>DD_ADC</sub>   | т |           | ADC supply current —<br>Maximum Mode                   | V <sub>DD_HV_AD</sub> at 5.0 V<br>ADC Freq = 16 MHz                                             | _                              | 3                                                     | 4                              |      |    |    |  |

| I <sub>DD_OSC</sub>   | Т |           | OSC supply current                                     | V <sub>DD_OSC</sub> at 5.0 V                                                                    | 8 MHz                          | 2.6                                                   | 3.2                            |      |    |    |  |

Maximum mode configuration: Code fetched from Flash executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

RAM, Code and Data Flash powered, code fetched from Flash executed by single core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- RAM, Code and Data Flash powered, code fetched from Flash executed by dual core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- Maximum mode configuration: Code fetched from RAM executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

5. HALT mode configuration, only for the "P" classification: Code Flash memory in low power mode, data Flash memory in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

STOP mode configuration, only for the "P" classification: Code and data Flash memories in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

| Symbo           | I | Parameter                                           | Conditions                        | Min  | Мах | Unit |

|-----------------|---|-----------------------------------------------------|-----------------------------------|------|-----|------|

|                 | Р | Equivalent pull-down current                        | V <sub>IN</sub> = V <sub>IL</sub> | 10   | —   |      |

| I <sub>PD</sub> | F |                                                     | $V_{IN} = V_{IH}$                 | —    | 130 | μA   |

| I <sub>IL</sub> | Р | Input leakage current<br>(all bidirectional ports)  | $T_A = -40$ to 125 °C             | _    | 1   | μA   |

| I <sub>IL</sub> | Р | Input leakage current<br>(all ADC input-only ports) | $T_A = -40$ to 125 °C             | _    | 0.5 | μA   |

| C <sub>IN</sub> | D | Input capacitance                                   | —                                 | _    | 10  | pF   |

| 1               | D | RESET, equivalent pull-up current                   | $V_{IN} = V_{IL}$                 | –130 | —   | μA   |

| I <sub>PU</sub> |   |                                                     | $V_{IN} = V_{IH}$                 | _    | -10 | μΛ   |

| 1               | D | RESET, equivalent pull-down current                 | $V_{IN} = V_{IL}$                 | 10   | _   | μA   |

| IPD             |   |                                                     | V <sub>IN</sub> = V <sub>IH</sub> |      | 130 | μΑ   |

## Table 22. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V]=1)<sup>(1)</sup> (continued)

1. These specifications are design targets and subject to change per device characterization.

2. "SR" parameter values must not exceed the absolute maximum ratings shown in Table 9.

| Symbol  |     | C Parameter                              |                                            | Conditions <sup>(1)</sup>         |                                               |                                 | Unit                           |     |     |    |    |

|---------|-----|------------------------------------------|--------------------------------------------|-----------------------------------|-----------------------------------------------|---------------------------------|--------------------------------|-----|-----|----|----|

|         |     | C                                        | Farameter                                  | Conditions                        |                                               |                                 | Тур                            | Мах | onn |    |    |

|         |     |                                          |                                            | C <sub>L</sub> = 25 pF, 40 MHz    |                                               | _                               | _                              | 22  |     |    |    |

|         |     |                                          |                                            | C <sub>L</sub> = 25 pF, 64 MHz    | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |                                 |                                | 33  |     |    |    |

| 1       | сс  | D                                        |                                            | Root medium square                | C <sub>L</sub> = 100 pF, 40 MHz               |                                 |                                |     | 56  | mA |    |

| IRMSFST | 00  |                                          |                                            |                                   | -                                             |                                 | C <sub>L</sub> = 25 pF, 40 MHz |     | _   | _  | 14 |

|         |     |                                          |                                            | C <sub>L</sub> = 25 pF, 64 MHz    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                               | _                              | 20  |     |    |    |

|         |     |                                          |                                            |                                   |                                               | C <sub>L</sub> = 100 pF, 40 MHz |                                | _   | _   | 35 |    |

| 1       | ~ - |                                          | Sum of all the static                      | V <sub>DD</sub> = 5.0 V ± 10%, P/ | AD3V5V = 0                                    | _                               | _                              | 70  |     |    |    |

| AVGSEG  | SR  | D I/O current within a<br>supply segment | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |                                   | _                                             | _                               | 65                             | mA  |     |    |    |

## Table 26. I/O consumption (continued)

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

2. Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

# 3.12 Main oscillator electrical characteristics

The SPC56xP54x/SPC56xP60x provides an oscillator/resonator driver.

| Symbol           |    | Parameter                          | Min | Max | Unit |

|------------------|----|------------------------------------|-----|-----|------|

| Cynhod           |    |                                    |     | тал | onit |

| f <sub>OSC</sub> | SR | Oscillator frequency               | 4   | 40  | MHz  |

| 9 <sub>m</sub>   | Ρ  | Transconductance                   | 6.5 | 25  | mA/V |

| V <sub>OSC</sub> | Т  | Oscillation amplitude on EXTAL pin | 1   | _   | V    |

| toscsu           | Т  | Start-up time <sup>(1),(2)</sup>   | 8   | _   | ms   |

## Table 27. Main oscillator electrical characteristics (5.0 V, NVUSRO[PAD3V5V]=0)

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of EXTAL.

| Symbol             |    | Parameter                          | Min | Мах | Unit |

|--------------------|----|------------------------------------|-----|-----|------|

| f <sub>OSC</sub>   | SR | Oscillator frequency               | 4   | 40  | MHz  |

| 9 <sub>m</sub>     | Ρ  | Transconductance                   | 4   | 20  | mA/V |

| V <sub>OSC</sub>   | Т  | Oscillation amplitude on EXTAL pin | 1   | _   | V    |

| t <sub>oscsu</sub> | Т  | Start-up time <sup>(1),(2)</sup>   | 8   |     | ms   |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of EXTAL.

In particular two different transient periods can be distinguished:

• A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

#### **Equation 5**

$$\tau_{1} = (R_{SW} + R_{AD}) \times \frac{C_{P} \times C_{S}}{C_{P} + C_{S}}$$

*Equation 5* can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \times C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation* 7:

### **Equation 7**

$$V_{A1} \times (C_S + C_{P1} + C_{P2}) = V_A \times (C_{P1} + C_{P2})$$

• A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance  $R_L$ : again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2 \! < \! R_L \! \times (C_S \! + C_{P1} \! + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraint on  $R_L$  sizing is obtained:

#### Equation 9

$$8.5 \times \tau_2 = 8.5 \times R_L \times (C_S + C_{P1} + C_{P2}) < T_S$$

Of course, R<sub>L</sub> shall be sized also according to the current limitation constraints, in combination with R<sub>S</sub> (source impedance) and R<sub>F</sub> (filter resistance). Being C<sub>F</sub> definitively bigger than C<sub>P1</sub>, C<sub>P2</sub> and C<sub>S</sub>, then the final voltage V<sub>A2</sub> (at the end of the charge transfer transient) will be much higher than V<sub>A1</sub>. *Equation 10* must be respected (charge balance assuming now C<sub>S</sub> already charged at V<sub>A1</sub>):

## **Equation 10**

$$V_{A2} \times (C_S + C_{P1} + C_{P2} + C_F) = V_A \times C_F + V_{A1} \times (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on

DocID18340 Rev 6

# 3.15.2 ADC conversion characteristics

| Symbol                          |    | Devemeter                                                                                                                  | Conditions <sup>(1)</sup>                                                                               |                                                       | Unit |                                |      |

|---------------------------------|----|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|--------------------------------|------|

| Symbo                           | וכ | Parameter                                                                                                                  | Conditions                                                                                              | Min                                                   | Тур  | Мах                            | Unit |

| V <sub>INAN</sub>               | SR | Analog input voltage <sup>(2)</sup>                                                                                        | _                                                                                                       | $\begin{array}{c} V_{SS\_HV\_AD} \\ -0.3 \end{array}$ | _    | V <sub>SS_HV_AD</sub><br>+ 0.3 | V    |

| f <sub>CK</sub>                 | SR | ADC Clock frequency<br>(depends on ADC<br>configuration)<br>(The duty cycle depends on<br>AD_clk <sup>(3)</sup> frequency) | _                                                                                                       | 3 <sup>(4)</sup>                                      | _    | 60                             | MHz  |

| f <sub>s</sub>                  | SR | Sampling frequency                                                                                                         | _                                                                                                       | _                                                     | _    | 1.53                           | MHz  |

| +                               | D  | Sample time <sup>(5)</sup>                                                                                                 | f <sub>ADC</sub> = 20 MHz,<br>INPSAMP = 3                                                               | 125                                                   | _    | _                              | ns   |

| t <sub>ADC_S</sub>              |    |                                                                                                                            | f <sub>ADC</sub> = 9 MHz,<br>INPSAMP = 255                                                              | —                                                     | _    | 28.2                           | μs   |

| t <sub>ADC_C</sub>              | Ρ  | Conversion time <sup>(6)</sup>                                                                                             | $f_{ADC} = 20 \text{ MHz}^{(7)},$<br>INPCMP = 1                                                         | 0.650                                                 | _    |                                | μs   |

| C <sub>S</sub> <sup>(8)</sup>   | D  | ADC input sampling capacitance                                                                                             | _                                                                                                       | —                                                     | _    | 2.5                            | pF   |

| C <sub>P1</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 1                                                                                                | _                                                                                                       | —                                                     | _    | 3                              | pF   |

| C <sub>P2</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 2                                                                                                | _                                                                                                       | —                                                     | _    | 1                              | pF   |

| C <sub>P3</sub> <sup>(8)</sup>  | D  | ADC input pin capacitance 3                                                                                                | _                                                                                                       | —                                                     | —    | 1                              | pF   |

| R <sub>SW1</sub> <sup>(8)</sup> | D  | Internal resistance of analog                                                                                              | $V_{DD_HV_AD} = 5 V \pm 10\%$                                                                           | —                                                     | _    | 0.6                            | kΩ   |

| INSW1                           | D  | source                                                                                                                     | V <sub>DD_HV_AD</sub> = 3.3 V ±10%                                                                      |                                                       | _    | 3                              | kΩ   |

| R <sub>SW2</sub> <sup>(8)</sup> | D  | Internal resistance of analog                                                                                              | $V_{DD_HV_AD}$ = 5 V ±10%                                                                               |                                                       | _    | 2.15                           | kΩ   |

| TSW2                            | D  | source                                                                                                                     | V <sub>DD_HV_AD</sub> = 3.3 V ±10%                                                                      |                                                       | _    | 3.6                            | kΩ   |

| R <sub>AD</sub> <sup>(8)</sup>  | D  | Internal resistance of analog source                                                                                       | _                                                                                                       | _                                                     | _    | 2                              | kΩ   |

| I <sub>INJ</sub>                | т  | Input current injection                                                                                                    | Current injection on one ADC<br>input, different from the<br>converted one. Remains<br>within TUE spec. | -5                                                    | _    | 5                              | mA   |

| INL                             | Ρ  | Integral Non Linearity                                                                                                     | No overload                                                                                             | —                                                     | ±1.5 | -                              | LSB  |

| DNL                             | Ρ  | Differential Non Linearity                                                                                                 | No overload                                                                                             | -1.0                                                  | _    | 1.0                            | LSB  |

| OFS                             | Т  | Offset error                                                                                                               | —                                                                                                       |                                                       | ±1   | _                              | LSB  |

| GNE                             | Т  | Gain error                                                                                                                 | —                                                                                                       | _                                                     | ±1   |                                | LSB  |

| TUE                             | Ρ  | Total unadjusted error<br>without current injection                                                                        | 16 precision channels                                                                                   | -2.5                                                  |      | 2.5                            | LSB  |

| Symbol             |    | ~  | Deveneter                                                                                      | Conditions <sup>(1)</sup>                                                                 |                                                                                           | Value                                                                 | )                    | 11   |    |  |

|--------------------|----|----|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|------|----|--|

| Symbo              | DI | С  | Parameter                                                                                      | Conditions                                                                                | Min                                                                                       | Тур                                                                   | Max                  | Unit |    |  |

| V <sub>IH</sub>    | SR | Ρ  | Input High Level CMOS<br>(Schmitt Trigger)                                                     | —                                                                                         | 0.65V <sub>DD</sub>                                                                       | —                                                                     | V <sub>DD</sub> +0.4 | V    |    |  |

| V <sub>IL</sub>    | SR | Ρ  | Input low Level CMOS<br>(Schmitt Trigger)                                                      | —                                                                                         | -0.4                                                                                      | _                                                                     | 0.35V <sub>DD</sub>  | V    |    |  |

| V <sub>HYS</sub>   | сс | С  | Input hysteresis CMOS<br>(Schmitt Trigger)                                                     | —                                                                                         | 0.1V <sub>DD</sub>                                                                        | _                                                                     | _                    | V    |    |  |

|                    |    |    |                                                                                                | Push Pull, $I_{OL}$ = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | _                                                                                         |                                                                       | 0.1V <sub>DD</sub>   |      |    |  |

| V <sub>OL</sub>    | сс | СР | P Output low level                                                                             | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>(2)</sup>   | —                                                                                         | _                                                                     | 0.1V <sub>DD</sub>   | V    |    |  |

|                    |    |    |                                                                                                |                                                                                           | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | _                                                                     | _                    | 0.5  |    |  |

|                    |    |    |                                                                                                | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                      | _                                                                                         | _                                                                     | 10                   |      |    |  |

|                    |    |    |                                                                                                | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                      | _                                                                                         | _                                                                     | 20                   |      |    |  |

| т                  | сс | D  | D                                                                                              | Output transition time                                                                    |                                                                                           | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _                    | _    | 40 |  |

| T <sub>tr</sub>    |    |    |                                                                                                |                                                                                           | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                      | —                                                                     | _                    | 12   | ns |  |