#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K × 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p54l5beabr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

## 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the SPC56xP54x/SPC56xP60x series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications specifically the airbag application.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

## 1.3 Device comparison

*Table 2* provides a summary of different members of the SPC56xP54x/SPC56xP60x family and their features—relative to Full-featured version—to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                                   | SPC560P54                       | SPC560P60       | SPC56AP54        | SPC56AP60 |  |  |

|-----------------------------------------------------------|---------------------------------|-----------------|------------------|-----------|--|--|

| Code Flash memory (with ECC)                              | 768 KB                          | 1 MB            | 768 KB           | 1 MB      |  |  |

| Data Flash / EE (with ECC)                                |                                 | 64              | KB               |           |  |  |

| SRAM (with ECC)                                           | 64 KB                           | 80 KB           | 64 KB            | 80 KB     |  |  |

| Processor core                                            | 32-bit e200z0h 32-bit Dual e200 |                 |                  | l e200z0h |  |  |

| Instruction set                                           | VLE                             |                 |                  |           |  |  |

| CPU performance                                           |                                 | 0-64            | MHz              |           |  |  |

| FMPLL (frequency-modulated phase-<br>locked loop) modules | 1                               |                 |                  |           |  |  |

| INTC (interrupt controller) channels                      | 148                             |                 |                  |           |  |  |

| PIT (periodic interrupt timer)                            |                                 | 1 (includes fou | r 32-bit timers) |           |  |  |

Table 2. SPC56xP54x/SPC56xP60x device comparison

| Table 2. SPC56xP54x/SPC56xP60x device comparison (continued) |                                     |                                                      |                    |                       |           |  |  |  |  |

|--------------------------------------------------------------|-------------------------------------|------------------------------------------------------|--------------------|-----------------------|-----------|--|--|--|--|

|                                                              | Feature                             | SPC560P54                                            | SPC560P60          | SPC56AP54             | SPC56AP60 |  |  |  |  |

| Enhanced D<br>access) cha                                    | MA (direct memory nnels             |                                                      | 1                  | 6                     |           |  |  |  |  |

| FlexRay                                                      |                                     |                                                      | Yes (64 mes        | sage buffer)          |           |  |  |  |  |

| FlexCAN (co                                                  | ontroller area network)             |                                                      | 3(1)               | ),(2)                 |           |  |  |  |  |

| Safety port                                                  |                                     |                                                      | Yes (via third Fl  | exCAN module)         |           |  |  |  |  |

| FCCU (fault                                                  | collection and control unit)        |                                                      | Ye                 | s <sup>(3)</sup>      |           |  |  |  |  |

| CTU (cross                                                   | triggering unit)                    |                                                      | Ye                 | es                    |           |  |  |  |  |

| eTimer char                                                  | inels                               |                                                      | 2 :                | × 6                   |           |  |  |  |  |

| FlexPWM (p<br>channels                                       | oulse-width modulation)             |                                                      | Ν                  | lo                    |           |  |  |  |  |

| Analog-to-di                                                 | gital converters (ADC)              | One (10-bit, 27-channel) <sup>(4)</sup>              |                    |                       |           |  |  |  |  |

| LINFlex mod                                                  | dules                               | 2 (1 × Master/Slave, 1 × Master only) <sup>(5)</sup> |                    |                       |           |  |  |  |  |

| DSPI (deser<br>interface) m                                  | ial serial peripheral<br>odules     | 5 <sup>(6)</sup>                                     |                    |                       |           |  |  |  |  |

| CRC (cyclic                                                  | redundancy check) units             | 2 <sup>(7)</sup>                                     |                    |                       |           |  |  |  |  |

| JTAG interfa                                                 | ace                                 | Yes                                                  |                    |                       |           |  |  |  |  |

| Nexus port of                                                | controller (NPC)                    | Yes (Level 2+) <sup>(8)</sup>                        |                    |                       |           |  |  |  |  |

|                                                              | Digital power supply <sup>(9)</sup> | 3.3 V                                                | or 5 V single supp | ly with external trar | nsistor   |  |  |  |  |

| Cummba                                                       | Analog power supply                 |                                                      | 3.3 V              | or 5 V                |           |  |  |  |  |

| Supply                                                       | Internal RC oscillator              |                                                      | 16                 | MHz                   |           |  |  |  |  |

|                                                              | External crystal oscillator         |                                                      | 4–40               | MHz                   |           |  |  |  |  |

| Packages                                                     |                                     | LQFP100 LQFF<br>LQFP144 LQFP                         |                    |                       |           |  |  |  |  |

| Temperature                                                  | Standard ambient temperature        |                                                      | -40 to             | 125 °C                |           |  |  |  |  |

Table 2. SPC56xP54x/SPC56xP60x device comparison (continued)

1. Each FlexCAN module has 32 message buffers.

2. One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

3. Enhanced FCCU version.

4. Same amount of ADC channels as on SPC560P44/50 not considering the internally connected ones. 26 channels on LQFP144 and 16 channels on LQFP100.

- 5. LinFlex\_1 is Master Only.

- 6. Increased number of CS for DSPI\_1.

- 7. Upgraded specification with addition of 8-bits polynomial (CRC-8 VDA CAN) support and 3rd context.

- 8. Improved debugging capability with data trace capability and increased Nexus throughput available on emulation package.

- 9. 3.3 V range and 5 V range correspond to different orderable parts.

- 10. Software development package only. Not available for production.

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency)

Programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

### 1.5.9 Main oscillator

The main oscillator provides these features:

- Input frequency range 4 MHz to 40 MHz

- Crystal input mode or Oscillator input mode

- PLL reference

#### 1.5.10 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC Oscillator provides these features:

- Nominal frequency 16 MHz

- ±6% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

### **1.5.11 Periodic interrupt timer (PIT)**

The PIT module implements these features:

- Up to four general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

### 1.5.12 System timer module (STM)

The STM module implements these features:

- 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

The STM module is replicated for each processor.

## **1.5.21** Serial communication interface module (LINFlex)

The LINFlex on the SPC56xP54x/SPC56xP60x features the following:

- Supports LIN Master mode (on both modules), LIN Slave mode (on one module) and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 Specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and up to 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors: Sync field; Delimiter; ID parity; Bit; Framing; Checksum and Time-out errors

- Classic or extended checksum calculation

- Configurable Break duration as long as 36-bit times

- Programmable Baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit or 9-bit words)

- Error detection and flagging

- Parity, Noise and Framing errors

- Interrupt-driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

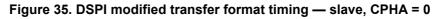

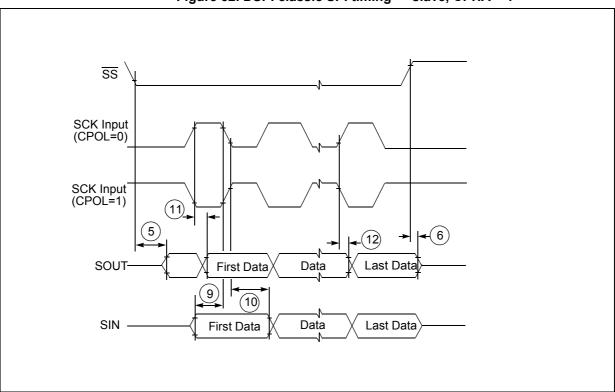

## 1.5.22 Deserial serial peripheral interface (DSPI)

The deserial serial peripheral interface (DSPI) module provides a synchronous serial interface for communication between the SPC56xP54x/SPC56xP60x MCU and external devices.

- Watchpoint triggering, watchpoint triggers program tracing

- DDR

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin<sup>(a)</sup>

## 1.5.28 IEEE 1149.1 (JTAG) controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with four pins (TDI, TMS, TCK, TDO)

- Selectable modes of operation include JTAGC/debug or normal system operation.

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC, ACCESS\_AUX\_TAP\_CORE0, ACCESS\_AUX\_TAP\_CORE1, ACCESS\_AUX\_TAP\_NASPS\_0, ACCESS\_AUX\_TAP\_NASPS\_1

- Three test data registers: a bypass register, a boundary scan register, and a device identification register.

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry.

### 1.5.29 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN transistor

- Regulates external 3.3 V to 5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

a. At least one TCK clock is necessary for the EVTI signal to be recognized by the MCU.

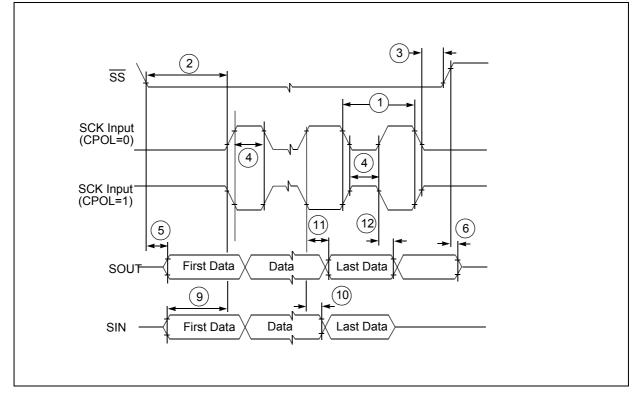

#### Figure 4. LQFP100 pinout (top view)<sup>(d)</sup>

#### 2.2 **Pin descriptions**

The following sections provide signal descriptions and related information about the functionality and configuration of the SPC56xP54x/SPC56xP60x devices.

#### 2.2.1 Power supply and reference voltage pins

Table 5 lists the power supply and reference voltage for the SPC56xP54x/SPC56xP60x devices.

|        |                                                         | Pin         |                            |    |

|--------|---------------------------------------------------------|-------------|----------------------------|----|

| Symbol | LQFP<br>100                                             | LQFP<br>144 | LQFP<br>176 <sup>(1)</sup> |    |

|        |                                                         |             |                            |    |

| BCTRL  | Voltage regulator external NPN Ballast base control pin | 47          | 69                         | 81 |

| Table 5. | Supply | pins |

|----------|--------|------|

|----------|--------|------|

d. Availability of port pin alternate functions depends on product selection.

|                                   | Supply                                                                                                                                                                        |             | Pin         |                            |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------|--|

| Symbol                            | Description                                                                                                                                                                   | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(1)</sup> |  |

| $V_{DD\_HV\_REG}(3.3$ V or 5.0 V) | Voltage regulator supply voltage                                                                                                                                              | 50          | 72          | 86                         |  |

| V <sub>DD_LV_REGCOR</sub>         | 1.2 V decoupling <sup>(2)</sup> pins for core logic supply and voltage regulator feedback. Decoupling capacitor must be connected between this pins and $V_{SS_LV\_REGCOR}$ . | 48          | 70          | 82                         |  |

| V <sub>SS_LV_REGCOR</sub>         | 1.2 V decoupling <sup>(2)</sup> pins for core logic GND and voltage regulator                                                                                                 |             |             |                            |  |

|                                   | ADC0 reference and supply voltage                                                                                                                                             |             |             |                            |  |

| V <sub>DD_HV_AD</sub>             | ADC supply and high reference voltage                                                                                                                                         | 39          | 56          | 64                         |  |

| V <sub>SS_HV_AD</sub>             | ADC ground and low reference voltage                                                                                                                                          | 40          | 57          | 65                         |  |

|                                   | Power supply pins (3.3 V or 5.0 V)                                                                                                                                            |             |             |                            |  |

| V <sub>DD_HV_IO0</sub>            | Input/Output supply voltage                                                                                                                                                   |             | 6           | 14                         |  |

| V <sub>SS_HV_IO0</sub>            | Input/Output ground                                                                                                                                                           |             | 7           | 15                         |  |

| V <sub>DD_HV_IO1</sub>            | Input/Output supply voltage                                                                                                                                                   | 13          | 21          | 29                         |  |

| V <sub>SS_HV_IO1</sub>            | Input/Output ground                                                                                                                                                           | 14          | 22          | 30                         |  |

| V <sub>DD_HV_IO2</sub>            | Input/Output supply voltage                                                                                                                                                   | 63          | 91          | 115                        |  |

| V <sub>SS_HV_IO2</sub>            | Input/Output ground                                                                                                                                                           | 62          | 90          | 114                        |  |

| V <sub>DD_HV_IO3</sub>            | Input/Output supply voltage                                                                                                                                                   | 87          | 126         | 150                        |  |

| V <sub>SS_HV_IO3</sub>            | Input/Output ground                                                                                                                                                           | 88          | 127         | 151                        |  |

| V <sub>DD_HV_IO4</sub>            | Input/Output supply voltage                                                                                                                                                   | _           | _           | 169                        |  |

| V <sub>SS_HV_IO4</sub>            | Input/Output ground                                                                                                                                                           | _           | _           | 170                        |  |

| V <sub>DD_HV_IO5</sub>            | Input/Output supply voltage                                                                                                                                                   | _           | —           | 5                          |  |

| V <sub>SS_HV_IO5</sub>            | Input/Output ground                                                                                                                                                           | _           | _           | 6                          |  |

| V <sub>DD_HV_IO6</sub>            | Input/Output supply voltage                                                                                                                                                   | _           | _           | 108                        |  |

| V <sub>SS_HV_IO6</sub>            | Input/Output ground                                                                                                                                                           | _           | —           | 109                        |  |

| V <sub>DD_HV_FL</sub>             | Code and data flash supply voltage                                                                                                                                            | 69          | 97          | 121                        |  |

| V <sub>SS_HV_FL</sub>             | Code and data flash supply ground                                                                                                                                             | 68          | 96          | 120                        |  |

| V <sub>DD_HV_OSC</sub>            | Crystal oscillator amplifier supply voltage                                                                                                                                   | 16          | 27          | 35                         |  |

| V <sub>SS_HV_OSC</sub>            | Crystal oscillator amplifier ground                                                                                                                                           | 17          | 28          | 36                         |  |

|                                   | Power supply pins (1.2 V)                                                                                                                                                     |             |             |                            |  |

| V <sub>DD_LV_COR0</sub>           | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR0}$ pin.                                | 12          | 18          | 26                         |  |

| Table 5. Supply pins (continued) | Table | 5. S | supply | pins | (continued) |

|----------------------------------|-------|------|--------|------|-------------|

|----------------------------------|-------|------|--------|------|-------------|

|                         | Supply                                                                                                                                             |    |     |     |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|--|--|

| Symbol                  | Symbol Description                                                                                                                                 |    |     |     |  |  |

| V <sub>SS_LV_COR0</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR0}$ pin.         | 11 | 17  | 25  |  |  |

| V <sub>DD_LV_COR1</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{\rm SS\_LV\_COR1}$ pin. | 65 | 93  | 117 |  |  |

| V <sub>SS_LV_COR1</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR1}$ pin.         | 66 | 94  | 118 |  |  |

| V <sub>DD_LV_COR2</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR2}$ pin.     | 92 | 131 | 155 |  |  |

| V <sub>SS_LV_COR2</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR\ 2}$ pin.       | 93 | 132 | 156 |  |  |

| V <sub>DD_LV_COR3</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR3}$ pin.     | 25 | 36  | 44  |  |  |

| V <sub>SS_LV_COR3</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR~3}$ pin.        | 24 | 35  | 43  |  |  |

| Table | 5  | Supply | v nins  | (continued) |

|-------|----|--------|---------|-------------|

| Table | υ. | Suppi  | y pilis | (continueu) |

1. LQFP176 available only as development package.

2. See datasheet Voltage Regulator Electrical Characteristics section for more details.

## 2.2.2 System pins

*Table 6* and *Table 7* contain information on pin functions for the SPC56xP54x/SPC56xP60x devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective Pad Configuration Register (PCR) values.

|        |                                  |                | Pad Sp | beed <sup>(1)</sup> | Pin         |             |                            |  |  |  |  |  |

|--------|----------------------------------|----------------|--------|---------------------|-------------|-------------|----------------------------|--|--|--|--|--|

| Symbol | Description                      | Direction      | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |  |  |  |  |  |

|        | Dedicated pins                   |                |        |                     |             |             |                            |  |  |  |  |  |

| MDO0   | Nexus Message Data Output—line 0 | Output<br>Only | Fast   |                     | _           | 9           | 17                         |  |  |  |  |  |

| MDO4   | Nexus Message Data Output—line 4 | Output<br>Only | Fast   |                     | _           | _           | 7                          |  |  |  |  |  |

#### Table 6. System pins

|             |            | Alternate                              |                                                        | • 7. Pin mux                                             | <i>I/O</i>                     | ,       | peed <sup>(6)</sup> | Pin         |             |                            |     |

|-------------|------------|----------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--------------------------------|---------|---------------------|-------------|-------------|----------------------------|-----|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3)        | Functions                                              | Peripheral<br>(4)                                        | direction<br>(5)               | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |     |

| A[2]        | DODINI     | ALT0<br>ALT1<br>ALT2                   | GPIO[2]<br>ETC[2]<br>CS3_4                             | SIUL<br>eTimer_0<br>DSPI_4                               | I/O<br>I/O<br>O                | Slow    |                     | Madium      | 57          | 0.4                        | 100 |

| (8)         | PCR[2]     | ALT3<br>—<br>—<br>—                    | <br>SIN_2<br>ABS[0]<br>EIRQ[2]                         | <br>DSPI_2<br>MC_RGM<br>SIUL                             |                                | Slow    | Medium              | 57          | 84          | 102                        |     |

| A[3]<br>(8) | PCR[3]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[3]<br>ETC[3]<br>CS0_2<br>—<br>ABS[1]<br>EIRQ[3]   | SIUL<br>eTimer_0<br>DSPI_2<br>—<br>MC_RGM<br>SIUL        | I/O<br>I/O<br>I/O<br>I<br>I    | Slow    | Medium              | 64          | 92          | 116                        |     |

| A[4]<br>(8) | PCR[4]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[4]<br>ETC[0]<br>CS1_2<br>ETC[4]<br>FAB<br>EIRQ[4] | SIUL<br>eTimer_1<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL | I/O<br>I/O<br>I/O<br>I<br>I    | Slow    | Medium              | 75          | 108         | 132                        |     |

| A[5]        | PCR[5]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[5]<br>CS0_1<br>ETC[5]<br>CS7_0<br>EIRQ[5]         | SIUL<br>DSPI_1<br>eTimer_1<br>DSPI_0<br>SIUL             | I/O<br>I/O<br>I/O<br>I         | Slow    | Medium              | 8           | 14          | 22                         |     |

| A[6]        | PCR[6]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[6]<br>SCK_1<br>CS2_4<br><br>EIRQ[6]               | SIUL<br>DSPI_1<br>DSPI_4<br><br>SIUL                     | I/O<br>I/O<br>I/O<br>I         | Slow    | Medium              | 2           | 2           | 2                          |     |

| A[7]        | PCR[7]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[7]<br>SOUT_1<br>CS1_4<br>—<br>EIRQ[7]             | SIUL<br>DSPI_1<br>DSPI_4<br>—<br>SIUL                    | I/O<br>O<br>I/O<br>I           | Slow    | Medium              | 4           | 10          | 18                         |     |

| A[8]        | PCR[8]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[8]<br>—<br>CS0_4<br>—<br>SIN_1<br>EIRQ[8]         | SIUL<br>—<br>DSPI_4<br>—<br>DSPI_1<br>SIUL               | I/O<br>—<br>I/O<br>—<br>I<br>I | Slow    | Medium              | 6           | 12          | 20                         |     |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |            | Alternate                              |                                                                | e 7. Pin mux                                            | I/O                       | ,       | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|----------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3)        | Functions                                                      | Peripheral<br>(4)                                       | direction<br>(5)          | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             | Port B     |                                        |                                                                |                                                         |                           |         |                     |             |             |                            |

| B[0]        | PCR[16]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[16]<br>TXD<br>ETC[2]<br>DEBUG[0]<br>EIRQ[15]              | SIUL<br>FlexCAN_0<br>eTimer_1<br>SSCM<br>SIUL           | I/O<br>O<br>I/O<br>I      | Slow    | Medium              | 76          | 109         | 133                        |

| B[1]        | PCR[17]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[17]<br>CS7_1<br>ETC[3]<br>DEBUG[1]<br>RXD<br>EIRQ[16]     | SIUL<br>DSPI_1<br>eTimer_1<br>SSCM<br>FlexCAN_0<br>SIUL | I/O<br>O<br>I/O<br>I<br>I | Slow    | Medium              | 77          | 110         | 134                        |

| B[2]        | PCR[18]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[18]<br>TXD<br>SOUT_4<br>DEBUG[2]<br>EIRQ[17]              | SIUL<br>LINFlex_0<br>DSPI_4<br>SSCM<br>SIUL             | 1/0<br>0<br>1/0<br>-      | Slow    | Medium              | 79          | 114         | 138                        |

| B[3]        | PCR[19]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[19]<br>—<br>SCK_4<br>DEBUG[3]<br>RXD                      | SIUL<br>—<br>DSPI_4<br>SSCM<br>LINFlex_0                | ₩<br>₩<br>₩<br>₩<br>₩     | Slow    | Medium              | 80          | 116         | 140                        |

| B[6]        | PCR[22]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[22]<br>clk_out<br>CS2_2<br>clk_out_div2<br>56<br>EIRQ[18] | SIUL<br>MC_CGL<br>DSPI_2<br>MC_CGL<br>SIUL              | ₩<br>0<br>0<br>1          | Slow    | Medium              | 96          | 138         | 162                        |

| B[7]        | PCR[23]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[23]<br>—<br>—<br>AN[0]<br>RXD                             | SIUL<br>—<br>—<br>ADC_0<br>LINFlex_0                    | Input Only                | —       | _                   | 29          | 43          | 51                         |

| B[8]        | PCR[24]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[24]<br>—<br>—<br>—<br>AN[1]<br>ETC[5]                     | SIUL<br>—<br>—<br>ADC_0<br>eTimer_0                     | Input Only                | _       | _                   | 31          | 47          | 55                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Table 7. Pin muxing <sup>(1)</sup> (continued) |            |                                              |                                          |                                         |                         |                          |             |             |                            |     |

|------------------------------------------------|------------|----------------------------------------------|------------------------------------------|-----------------------------------------|-------------------------|--------------------------|-------------|-------------|----------------------------|-----|

| Port                                           | PCR<br>No. | Alternate<br>function <sup>(2),</sup><br>(3) | Functions (4)                            | Dorinhorol                              | I/O                     | Pad speed <sup>(6)</sup> |             | Pin         |                            |     |

| pin                                            |            |                                              |                                          | direction<br>(5)                        | SRC = 0                 | SRC = 1                  | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |     |

| D[7]                                           | PCR[55]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—            | GPIO[55]<br>CS3_1<br>—<br>CS4_0<br>SIN_3 | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>—<br>O<br>I | Slow                     | Medium      | 26          | 37                         | 45  |

| D[8]                                           | PCR[56]    | ALT0<br>ALT1<br>ALT2<br>ALT3                 | GPIO[56]<br>CS2_1<br>RDY<br>CS5_0        | SIUL<br>DSPI_1<br>nexus_0<br>DSPI_0     | I/O<br>O<br>O           | Slow                     | Medium      | 21          | 32                         | 40  |

| D[9]                                           | PCR[57]    | ALT0<br>ALT1<br>ALT2<br>ALT3                 | GPIO[57]<br>—<br>TXD<br>CS6_1            | SIUL<br>—<br>LINFlex_1<br>DSPI_1        | I/O<br>  0<br>0         | Slow                     | Medium      | 15          | 26                         | 34  |

| D[10]                                          | PCR[58]    | ALT0<br>ALT1<br>ALT2<br>ALT3                 | GPIO[58]<br>—<br>CS0_3<br>—              | SIUL<br>—<br>DSPI_3<br>—                | I/O<br>—<br>I/O<br>—    | Slow                     | Medium      | 53          | 76                         | 92  |

| D[11]                                          | PCR[59]    | ALT0<br>ALT1<br>ALT2<br>ALT3                 | GPIO[59]<br>—<br>CS1_3<br>SCK_3          | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>0<br>I/O    | Slow                     | Medium      | 54          | 78                         | 94  |

| D[12]                                          | PCR[60]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—            | GPIO[60]<br>—<br>CS7_1<br>RXD            | SIUL<br>—<br>—<br>DSPI_1<br>LINFlex_1   | I/O<br>—<br>—<br>0<br>I | Slow                     | Medium      | 70          | 99                         | 123 |

| D[13]                                          | PCR[61]    | ALT0<br>ALT1<br>ALT2<br>ALT3                 | GPIO[61]<br>—<br>CS2_3<br>SOUT_3         | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>O<br>O      | Slow                     | Medium      | 67          | 95                         | 119 |

| D[14]                                          | PCR[62]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—            | GPIO[62]<br>—<br>CS3_3<br>—<br>SIN_3     | SIUL<br>—<br>DSPI_3<br>—<br>DSPI_3      | I/O<br>—<br>—<br>—<br>— | Slow                     | Medium      | 73          | 105                        | 129 |

| D[15]                                          | PCR[63]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—            | GPIO[63]<br>—<br>—<br>—<br>AN[20]        | SIUL<br>—<br>—<br>—<br>ADC_0            | Input Only              | _                        | _           | 41          | 58                         | 66  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Dent        |            | Alternate                       |           |                   | ral I/O<br>direction<br>(5) | Pad speed <sup>(6)</sup> |         | Pin         |             |                            |

|-------------|------------|---------------------------------|-----------|-------------------|-----------------------------|--------------------------|---------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) |                             | SRC = 0                  | SRC = 1 | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             | Pr         |                                 |           |                   |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[64]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT1                            | —         | —                 |                             |                          |         |             |             |                            |

| E[0]        | PCR[64]    | ALT2                            | —         | —                 | Input Only                  | —                        | —       | 46          | 68          | 80                         |

|             |            | ALT3                            | —         | —                 |                             |                          |         |             |             |                            |

|             |            | —                               | AN[21]    | ADC_0             |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[65]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT1                            | —         | —                 |                             |                          |         |             |             |                            |

| E[1]        | PCR[65]    | ALT2                            | —         | —                 | Input Only                  | —                        | _       | 27          | 39          | 47                         |

|             |            | ALT3                            |           | —                 |                             |                          |         |             |             |                            |

|             |            | —                               | AN[4]     | ADC_0             |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[66]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT1                            | —         | —                 |                             |                          |         |             | 10          |                            |

| E[2]        | PCR[66]    | ALT2                            | —         | —                 | Input Only                  | —                        | —       | 32          | 49          | 57                         |

|             |            | ALT3                            |           | ADC_0             |                             |                          |         |             |             |                            |

|             |            | —                               | AN[5]     |                   |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[67]  | SIUL              |                             |                          |         |             |             |                            |

| E131        | PCR[67]    | ALT1<br>ALT2                    | —         | —                 | Input Only                  |                          |         |             | 40          | 48                         |

| E[3]        | FCR[07]    | ALT2<br>ALT3                    |           | _                 | Input Only                  | _                        | _       |             | 40          | 40                         |

|             |            |                                 | AN[6]     | ADC_0             |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[68]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT0<br>ALT1                    |           | 510L              |                             |                          |         |             |             |                            |

| E[4]        | PCR[68]    | ALT2                            | _         | _                 | Input Only                  | _                        | _       |             | 42          | 50                         |

|             | []         | ALT3                            | _         | _                 |                             |                          |         |             | .=          |                            |

|             |            | —                               | AN[7]     | ADC_0             |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[69]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT1                            |           | _                 |                             |                          |         |             |             |                            |

| E[5]        | PCR[69]    | ALT2                            | —         | —                 | Input Only                  | —                        | _       |             | 44          | 52                         |

|             |            | ALT3                            | —         | —                 |                             |                          |         |             |             |                            |

|             |            | —                               | AN[8]     | ADC_0             |                             |                          |         |             |             |                            |

|             |            | ALT0                            | GPIO[70]  | SIUL              |                             |                          |         |             |             |                            |

|             |            | ALT1                            | —         | _                 |                             |                          |         |             |             |                            |

| E[6]        | PCR[70]    | ALT2                            | —         | _                 | Input Only                  | —                        | _       | —           | 46          | 54                         |

|             |            | ALT3                            | —         | -                 |                             |                          |         |             |             |                            |

|             |            |                                 | AN[9]     | ADC_0             |                             |                          |         |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

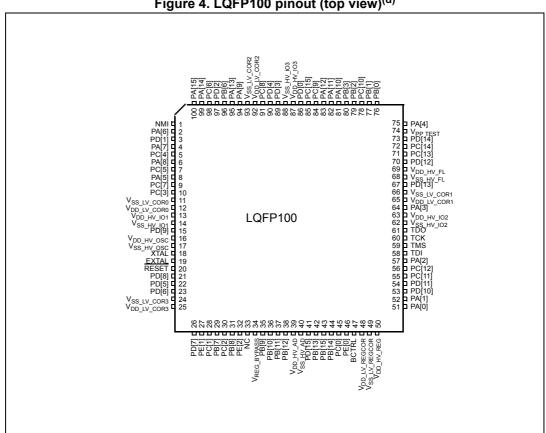

## Figure 6. Independent ADC supply<sup>(e)</sup>

#### **Recommended operating conditions** 3.4

| Table 10. Recommended | operating co | nditions (5.0 | V) |

|-----------------------|--------------|---------------|----|

|                       |              |               |    |

| Symbol                                |    | Parameter                                               | Conditions                            | Min                         | Max <sup>(1)</sup>           | Unit |  |

|---------------------------------------|----|---------------------------------------------------------|---------------------------------------|-----------------------------|------------------------------|------|--|

| V <sub>SS_HV</sub>                    | SR | Digital ground                                          | —                                     | 0                           | 0                            | V    |  |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 5.0 V input/output supply voltage                       | _                                     | 4.5                         | 5.5                          | V    |  |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                             | —                                     | 0                           | 0                            | V    |  |

|                                       |    | 5.0 V code and data flash memory supply voltage         | —                                     | 4.5                         | 5.5                          | V    |  |

| V <sub>DD_HV_FL</sub>                 | SR |                                                         | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 |      |  |

| V <sub>SS_HV_FL</sub>                 | SR | Code and data flash<br>memory ground                    | _                                     | 0                           | 0                            | V    |  |

|                                       |    | 5.0.V. crystal oscillator                               | —                                     | 4.5                         | 5.5                          |      |  |

| V <sub>DD_HV_OSC</sub>                | SR | 5.0 V crystal oscillator<br>amplifier supply voltage    | Relative to $V_{DD_HV_IOx} = 0.7$     |                             | V <sub>DD_HV_IOx</sub> + 0.1 | V    |  |

| V <sub>SS_HV_OSC</sub>                | SR | 5.0 V crystal oscillator<br>amplifier reference voltage |                                       | 0                           | 0                            | V    |  |

e. Device design targets the removal of this conditions. To be confirmed by design during device validation.

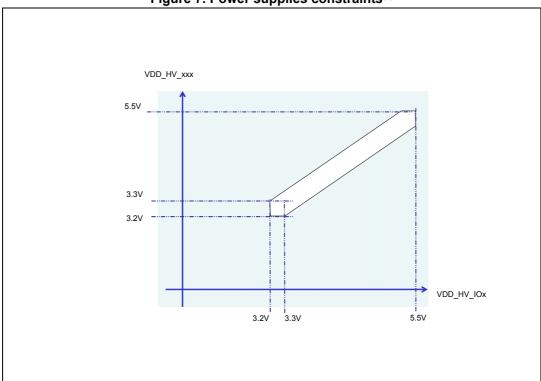

Figure 7. Power supplies constraints<sup>(f)</sup>

The SPC56xP54x/SPC56xP60x supply architecture provides an ADC supply that is managed independently of standard  $V_{DD_HV}$  supply. *Figure 8* shows the constraints of the ADC power supply.

f. IO AC and DC characteristics are guaranteed only in the range 3.0 V–3.6 V when PAD3V5V is low, and in the range 4.5 V–5.5 V when PAD3V5V is high.

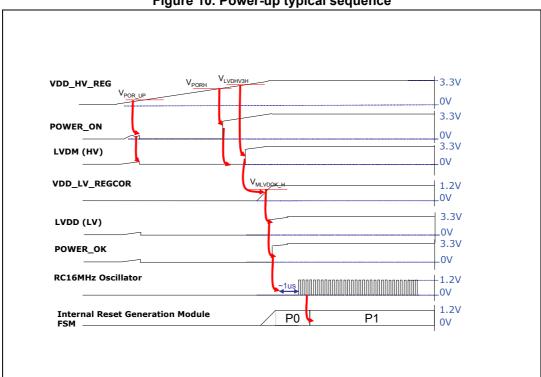

Figure 10. Power-up typical sequence

DocID18340 Rev 6

#### **Electrical characteristics**

- 2. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

- Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- 4. f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- 5. This value is determined by the crystal manufacturer and board design.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

- 7. Proper PC board layout procedures must be followed to achieve specifications.

- 8. Values are obtained with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of  $C_{\text{JITTER}}$  and either  $f_{\text{CS}}$  or  $f_{\text{DS}}$  (depending on whether center spread or down spread modulation is enabled).

- 9. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

- 10. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 11. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 12. This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

- 13. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

# 3.14 **16 MHz RC oscillator electrical characteristics**

| Symbol                      |   | Parameter                                                                                                                                         | Conditions             | Min | Тур | Max | Unit |

|-----------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| f <sub>RC</sub>             | Ρ | RC oscillator frequency                                                                                                                           | T <sub>A</sub> = 25 °C | —   | 16  |     | MHz  |

| $\Delta_{RCMVAR}$           | Ρ | Fast internal RC oscillator variation<br>over temperature and<br>supply with respect to $f_{RC}$ at TA = 25 °C<br>in high-frequency configuration | —                      | -6  | _   | 6   | %    |

| $\Delta_{\mathrm{RCMTRIM}}$ | Т | Post Trim Accuracy: The variation of the PTF <sup>(1)</sup> from the 16 MHz                                                                       | T <sub>A</sub> = 25 °C | -1  | _   | 1   | %    |

| $\Delta_{RCMSTEP}$          | Т | Fast internal RC oscillator trimming step                                                                                                         | T <sub>A</sub> = 25 °C | _   | 1.6 | _   | %    |

Table 31. 16 MHz RC oscillator electrical characteristics

1. PTF = Post Trimming Frequency: The frequency of the output clock after trimming at typical supply voltage and temperature

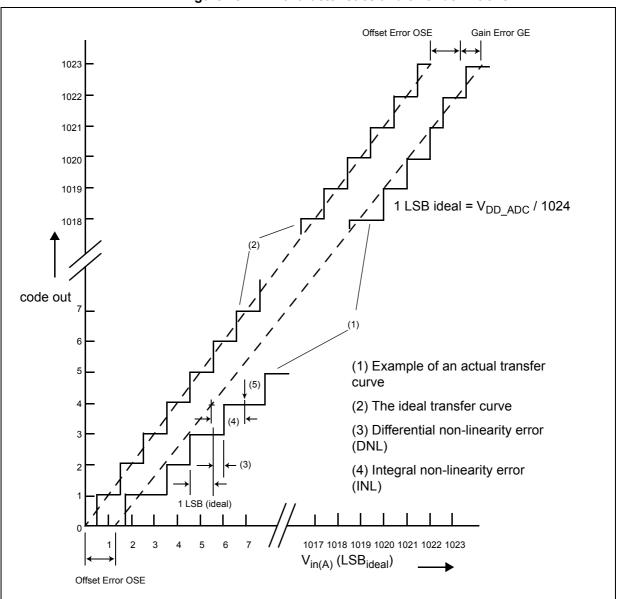

# 3.15 Analog-to-Digital converter (ADC) electrical characteristics

The device provides a 10-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Figure 15. ADC characteristics and error definitions

### 3.15.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high-frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuate the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

DocID18340 Rev 6

g. The output drive provided is open drain and hence must be terminated by an external resistor of value 1 k $\Omega$ .

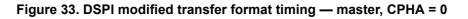

Figure 32. DSPI classic SPI timing — slave, CPHA = 1

DocID18340 Rev 6

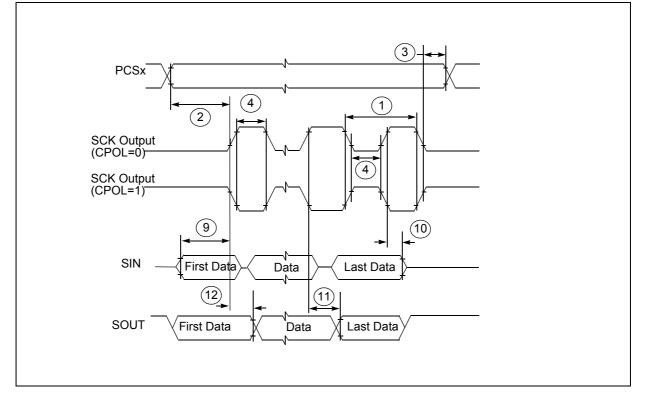

Figure 34. DSPI modified transfer format timing — master, CPHA = 1