Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p54l5beaby |

Table 2. SPC56xP54x/SPC56xP60x device comparison (continued)

|                              | Feature                             | SPC560P54                                            | SPC560P60           | SPC56AP54              | SPC56AP60                                     |  |  |

|------------------------------|-------------------------------------|------------------------------------------------------|---------------------|------------------------|-----------------------------------------------|--|--|

| Enhanced D                   | MA (direct memory nnels             | 16                                                   |                     |                        |                                               |  |  |

| FlexRay                      |                                     |                                                      | Yes (64 mes         | sage buffer)           |                                               |  |  |

| FlexCAN (co                  | ontroller area network)             |                                                      | 3 <sup>(1)</sup>    | ),(2)                  |                                               |  |  |

| Safety port                  |                                     |                                                      | Yes (via third FI   | exCAN module)          |                                               |  |  |

| FCCU (fault                  | collection and control unit)        |                                                      | Yes                 | s <sup>(3)</sup>       |                                               |  |  |

| CTU (cross                   | triggering unit)                    |                                                      | Ye                  | es                     |                                               |  |  |

| eTimer chan                  | inels                               |                                                      | 2 >                 | <b>&lt;</b> 6          |                                               |  |  |

| FlexPWM (p channels          | ulse-width modulation)              |                                                      | N                   | lo                     |                                               |  |  |

| Analog-to-di                 | gital converters (ADC)              | One (10-bit, 27-channel) <sup>(4)</sup>              |                     |                        |                                               |  |  |

| LINFlex mod                  | dules                               | 2 (1 × Master/Slave, 1 × Master only) <sup>(5)</sup> |                     |                        |                                               |  |  |

| DSPI (deser<br>interface) me | ial serial peripheral<br>odules     | 5 <sup>(6)</sup>                                     |                     |                        |                                               |  |  |

| CRC (cyclic                  | redundancy check) units             |                                                      | 2                   | (7)                    |                                               |  |  |

| JTAG interfa                 | ice                                 |                                                      | Ye                  | es                     |                                               |  |  |

| Nexus port of                | controller (NPC)                    |                                                      | Yes (Lev            | /el 2+) <sup>(8)</sup> |                                               |  |  |

|                              | Digital power supply <sup>(9)</sup> | 3.3 V                                                | or 5 V single suppl | y with external trai   | nsistor                                       |  |  |

| Cupply                       | Analog power supply                 |                                                      | 3.3 V               | or 5 V                 |                                               |  |  |

| Supply                       | Internal RC oscillator              |                                                      | 16 1                | MHz                    |                                               |  |  |

|                              | External crystal oscillator         |                                                      | 4–40                | MHz                    |                                               |  |  |

| Packages                     |                                     |                                                      | LQFP100<br>LQFP144  |                        | LQFP100<br>LQFP144<br>LQFP176 <sup>(10)</sup> |  |  |

| Temperature                  | Standard ambient temperature        |                                                      | –40 to              | 125 °C                 |                                               |  |  |

- 1. Each FlexCAN module has 32 message buffers.

- 2. One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

- 3. Enhanced FCCU version.

- Same amount of ADC channels as on SPC560P44/50 not considering the internally connected ones. 26 channels on LQFP144 and 16 channels on LQFP100.

- 5. LinFlex\_1 is Master Only.

- 6. Increased number of CS for DSPI\_1.

- 7. Upgraded specification with addition of 8-bits polynomial (CRC-8 VDA CAN) support and 3rd context.

- 8. Improved debugging capability with data trace capability and increased Nexus throughput available on emulation package.

- 9. 3.3 V range and 5 V range correspond to different orderable parts.

- 10. Software development package only. Not available for production.

SPC56xP54x/SPC56xP60x is present on the market in two different options enabling different features: Full-featured, and Airbag configuration. *Table 3* shows the main differences between the two versions.

Table 3. SPC56xP54x/SPC56xP60x device configuration difference

| Feature                                             | Enhanced<br>Full-featured | Full-featured | Airbag |

|-----------------------------------------------------|---------------------------|---------------|--------|

| FlexCAN (controller area network)                   | 3                         | 2             | 2      |

| CTU (cross triggering unit)                         | Ye                        | es            | No     |

| FlexRay                                             | Yes (64 mes               | sage buffer)  | No     |

| DSPI (deserial serial peripheral interface) modules | ţ                         | 5             | 4      |

| CRC (cyclic redundancy check) unit                  | 2                         | 2             | 1      |

### 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC56xP54x/SPC56xP60x MCU. *Table 4* summarizes the functions of the blocks.

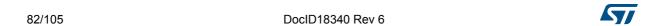

The DSPI modules provide these features:

- Full duplex, synchronous transfers

- Master or slave operation

- Programmable master bit rates

- Programmable clock polarity and phase

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- Up to 28 chip select lines available

- 8 each on DSPI 0 and DSPI 1

- 4 each on DSPI 2, DSPI 3, and DSPI 4

- 8 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering up to 5 transfers on the transmit and receive side

- Queueing operation possible through use of the eDMA

- General purpose I/O functionality on pins when not used for SPI

#### 1.5.23 eTimer

Two eTimer modules are provided, each with six 16-bit general purpose up/down timer/counter per module. The following features are implemented:

- Individual channel capability

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0 % to 100% pulse measurement

- Rotation direction flag (Quad decoder mode)

- Maximum count rate

- Equals peripheral clock/2 for external event counting

- Equals peripheral clock for internal clock counting

- Cascadeable counters

- Programmable count modulo

- Quadrature decode capabilities

- Counters can share available input pins

- Count once or repeatedly

- Preloadable counters

- Pins available as GPIO when timer functionality not in use

# 2 Package pinouts and signal descriptions

### 2.1 Package pinouts

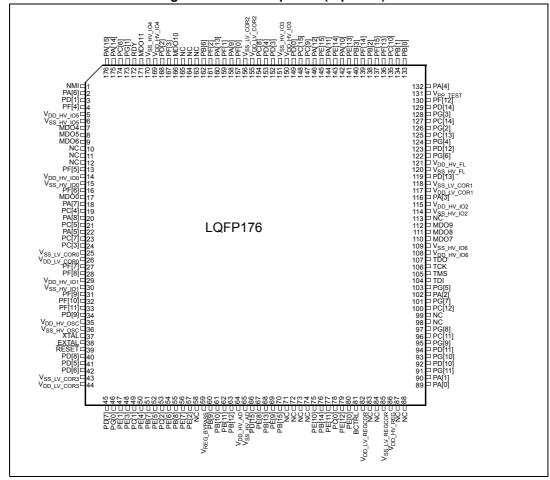

The LQFP pinouts are shown in the following figures.

Figure 2. LQFP176 pinout (top view)<sup>(b)</sup>

b. Software development package only. Not available for production.

DocID18340 Rev 6 27/105

Table 5. Supply pins (continued)

|                                         | Supply                                                                                                                                                                              |             | Pin         |                            |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------|

| Symbol                                  | Description                                                                                                                                                                         | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(1)</sup> |

| V <sub>DD_HV_REG</sub> (3.3 V or 5.0 V) | Voltage regulator supply voltage                                                                                                                                                    | 50          | 72          | 86                         |

| V <sub>DD_LV_REGCOR</sub>               | 1.2 V decoupling <sup>(2)</sup> pins for core logic supply and voltage regulator feedback. Decoupling capacitor must be connected between this pins and V <sub>SS_LV_REGCOR</sub> . | 48          | 70          | 82                         |

| V <sub>SS_LV_REGCOR</sub>               | 1.2 V decoupling <sup>(2)</sup> pins for core logic GND and voltage regulator feedback. Decoupling capacitor must be connected between this pins and V <sub>DD_LV_REGCOR</sub> .    | 49          | 71          | 85                         |

|                                         | ADC0 reference and supply voltage                                                                                                                                                   |             |             |                            |

| V <sub>DD_HV_AD</sub>                   | ADC supply and high reference voltage                                                                                                                                               | 39          | 56          | 64                         |

| V <sub>SS_HV_AD</sub>                   | ADC ground and low reference voltage                                                                                                                                                | 40          | 57          | 65                         |

|                                         | Power supply pins (3.3 V or 5.0 V)                                                                                                                                                  | I.          | I.          | I.                         |

| V <sub>DD_HV_IO0</sub>                  | Input/Output supply voltage                                                                                                                                                         | _           | 6           | 14                         |

| V <sub>SS_HV_IO0</sub>                  | Input/Output ground                                                                                                                                                                 | _           | 7           | 15                         |

| V <sub>DD_HV_IO1</sub>                  | Input/Output supply voltage                                                                                                                                                         | 13          | 21          | 29                         |

| V <sub>SS_HV_IO1</sub>                  | Input/Output ground                                                                                                                                                                 | 14          | 22          | 30                         |

| V <sub>DD_HV_IO2</sub>                  | Input/Output supply voltage                                                                                                                                                         | 63          | 91          | 115                        |

| V <sub>SS_HV_IO2</sub>                  | Input/Output ground                                                                                                                                                                 | 62          | 90          | 114                        |

| V <sub>DD_HV_IO3</sub>                  | Input/Output supply voltage                                                                                                                                                         | 87          | 126         | 150                        |

| V <sub>SS_HV_IO3</sub>                  | Input/Output ground                                                                                                                                                                 | 88          | 127         | 151                        |

| V <sub>DD_HV_IO4</sub>                  | Input/Output supply voltage                                                                                                                                                         | _           | _           | 169                        |

| V <sub>SS_HV_IO4</sub>                  | Input/Output ground                                                                                                                                                                 | _           | _           | 170                        |

| V <sub>DD_HV_IO5</sub>                  | Input/Output supply voltage                                                                                                                                                         | _           | _           | 5                          |

| V <sub>SS_HV_IO5</sub>                  | Input/Output ground                                                                                                                                                                 | _           | _           | 6                          |

| V <sub>DD_HV_IO6</sub>                  | Input/Output supply voltage                                                                                                                                                         | _           | _           | 108                        |

| V <sub>SS_HV_IO6</sub>                  | Input/Output ground                                                                                                                                                                 | _           | _           | 109                        |

| V <sub>DD_HV_FL</sub>                   | Code and data flash supply voltage                                                                                                                                                  | 69          | 97          | 121                        |

| V <sub>SS_HV_FL</sub>                   | Code and data flash supply ground                                                                                                                                                   | 68          | 96          | 120                        |

| V <sub>DD_HV_OSC</sub>                  | Crystal oscillator amplifier supply voltage                                                                                                                                         | 16          | 27          | 35                         |

| V <sub>SS_HV_OSC</sub>                  | Crystal oscillator amplifier ground                                                                                                                                                 | 17          | 28          | 36                         |

|                                         | Power supply pins (1.2 V)                                                                                                                                                           |             |             |                            |

| V <sub>DD_LV_COR0</sub>                 | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR0}$ pin.                                      | 12          | 18          | 26                         |

30/105 DocID18340 Rev 6

Pin Supply **LQFP LQFP LQFP Symbol** Description 176<sup>(1)</sup> 100 144 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest 17 25 11 V<sub>SS LV COR0</sub> V<sub>DD LV COR0</sub> pin 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest 65 93 117 V<sub>DD LV COR1</sub> V<sub>SS\_LV\_COR1</sub> pin. 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest 118 66 94 V<sub>SS LV COR1</sub> V<sub>DD\_LV</sub> COR1 pin. 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest 92 131 155 V<sub>DD LV COR2</sub> V<sub>SS LV COR2</sub> pin. 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest 93 132 156 V<sub>SS\_LV\_COR2</sub> V<sub>DD\_LV\_COR 2</sub> pin. 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest 25 V<sub>DD LV COR3</sub> 36 44 V<sub>SS LV COR3</sub> pin. 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest 35 24 43 V<sub>SS\_LV\_COR3</sub> V<sub>DD\_LV\_COR 3</sub> pin.

Table 5. Supply pins (continued)

#### 2.2.2 System pins

*Table 6* and *Table 7* contain information on pin functions for the SPC56xP54x/SPC56xP60x devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective Pad Configuration Register (PCR) values.

Table 6. System pins

| Symbol | Description                      |                | Pad Speed <sup>(1)</sup> |       | Pin         |             |                            |

|--------|----------------------------------|----------------|--------------------------|-------|-------------|-------------|----------------------------|

|        |                                  | Direction      | SRC=0                    | SRC=1 | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |

|        | Dedicated                        | d pins         |                          |       |             |             |                            |

| MDO0   | Nexus Message Data Output—line 0 | Output<br>Only | Fa                       | ıst   | _           | 9           | 17                         |

| MDO4   | Nexus Message Data Output—line 4 | Output<br>Only | Fast                     |       | _           | _           | 7                          |

<sup>1.</sup> LQFP176 available only as development package.

<sup>2.</sup> See datasheet Voltage Regulator Electrical Characteristics section for more details.

Table 6. System pins (continued)

|                         | Table 6. System pi                                                                                                                                                        |                | Pad Sp | peed <sup>(1)</sup> | Pin         |             |                            |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|---------------------|-------------|-------------|----------------------------|

| Symbol                  | Description                                                                                                                                                               | Direction      | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |

| MDO5                    | Nexus Message Data Output—line 5                                                                                                                                          | Output<br>Only | Fa     | st                  | _           | _           | 8                          |

| MDO6                    | Nexus Message Data Output—line 6                                                                                                                                          | Output<br>Only | Fa     | st                  | _           | _           | 9                          |

| MDO7                    | Nexus Message Data Output—line 7                                                                                                                                          | Output<br>Only | Fa     | st                  | _           | _           | 110                        |

| MDO8                    | Nexus Message Data Output—line 8                                                                                                                                          | Output<br>Only | Fa     | st                  | _           | _           | 111                        |

| MDO9                    | Nexus Message Data Output—line 9                                                                                                                                          | Output<br>Only | Fa     | st                  | _           | _           | 112                        |

| MDO10                   | Nexus Message Data Output—line 10                                                                                                                                         | Output<br>Only | Fa     | st                  | _           | _           | 166                        |

| MDO11                   | Nexus Message Data Output—line 11                                                                                                                                         | Output<br>Only | Fa     | st                  | _           | _           | 171                        |

| RDY                     | Nexus ready output                                                                                                                                                        | Output<br>Only | _      | _                   | _           | _           | 172                        |

| NMI                     | Non-Maskable Interrupt                                                                                                                                                    | Input Only     | _      | _                   | 1           | 1           | 1                          |

| XTAL                    | Analog output of the oscillator amplifier circuit. Needs to be grounded if oscillator is used in bypass mode.                                                             | _              | _      | _                   | 18          | 29          | 37                         |

| EXTAL                   | Analog input of the oscillator amplifier circuit, when the oscillator is not in bypass mode.  Analog input for the clock generator when the oscillator is in bypass mode. | _              | _      | _                   | 19          | 30          | 38                         |

| TMS <sup>(3)</sup>      | JTAG state machine control                                                                                                                                                | Input Only     | _      | _                   | 59          | 87          | 105                        |

| TCK <sup>(3)</sup>      | JTAG clock                                                                                                                                                                | Input Only     | _      | 1                   | 60          | 88          | 106                        |

| TDI <sup>(3)</sup>      | JTAG data input                                                                                                                                                           | Input Only     | _      | 1                   | 58          | 86          | 104                        |

| TDO <sup>(3)</sup>      | JTAG data output                                                                                                                                                          | Output<br>Only | _      | -                   | 61          | 89          | 107                        |

|                         | Reset                                                                                                                                                                     | pin            |        |                     |             |             |                            |

| RESET <sup>(4)</sup>    | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                                 | Bidirection al | Medium | _                   | 20          | 31          | 39                         |

|                         | Test p                                                                                                                                                                    | in             |        |                     |             |             |                            |

| V <sub>PP TEST</sub>    | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                              | _              | _      | _                   | 74          | 107         | 131                        |

| V <sub>REG_BYPASS</sub> | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                              | _              | _      |                     | 34          | 51          | 59                         |

<sup>1.</sup> SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

32/105 DocID18340 Rev 6

# 3.3 Absolute maximum ratings

Table 9. Absolute maximum ratings<sup>(1)</sup>

| Symbol                     |     | Parameter                                                                                                                | Conditions                         | Min Max <sup>(2)</sup>      |                                       | Unit |

|----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|---------------------------------------|------|

| V <sub>SS_HV</sub>         | SR  | Digital ground                                                                                                           | _                                  | 0                           | 0                                     | V    |

| V <sub>DD_HV_IOx</sub> (3) | SR  | 3.3 V / 5.0 V input/output supply voltage with respect to ground (V <sub>SS_HV</sub> )                                   | _                                  | -0.3                        | 6.0                                   | V    |

| V <sub>SS_HV_IOx</sub>     | SR  | Input/output ground voltage with respect to ground (V <sub>SS_HV</sub> )                                                 | _                                  | -0.1                        | 0.1                                   | ٧    |

|                            |     | 3.3 V / 5.0 V code and data flash                                                                                        | _                                  | -0.3                        | 6.0                                   |      |

| V <sub>DD_HV_FL</sub>      | SR  | memory supply voltage with respect to ground (V <sub>SS_HV</sub> )                                                       | Relative to V <sub>DD_HV_IOx</sub> | -0.3                        | V <sub>DD_HV_IOx</sub> + 0.3          | V    |

| V <sub>SS_HV_FL</sub>      | SR  | Code and data flash memory ground with respect to ground (V <sub>SS_HV</sub> )                                           | _                                  | -0.1                        | 0.1                                   | V    |

|                            |     | 3.3 V / 5.0 V crystal oscillator                                                                                         | _                                  | -0.3                        | 6.0                                   |      |

| V <sub>DD_HV_OSC</sub>     | SR  | amplifier supply voltage with respect to ground (V <sub>SS_HV</sub> )                                                    | Relative to V <sub>DD_HV_IOx</sub> | -0.3                        | V <sub>DD_HV_IOx</sub> + 0.3          | V    |

| V <sub>SS_HV_OSC</sub>     | SR  | 3.3 V / 5.0 V crystal oscillator amplifier reference voltage with respect to ground (V <sub>SS_HV</sub> )                | _                                  | -0.1                        | 0.1                                   | ٧    |

|                            |     | 3.3 V / 5.0 V voltage regulator supply                                                                                   | _                                  | - 0.3                       | 6.0                                   |      |

| $V_{DD\_HV\_REG}$          | SR  | voltage with respect to ground (V <sub>SS_HV</sub> )                                                                     | Relative to V <sub>DD_HV_IOx</sub> | - 0.3                       | V <sub>DD_HV_IOx</sub> + 0.3          | V    |

| V                          | SR  | 3.3 V / 5.0 V ADC supply and high reference voltage with respect to                                                      | V <sub>DD_HV_REG</sub><br>< 2.7 V  | - 0.3                       | V <sub>DD_HV_REG</sub><br>+ 0.3       | V    |

| V <sub>DD_HV_AD</sub>      | Six | ground (V <sub>SS_HV</sub> )                                                                                             | V <sub>DD_HV_REG</sub> > 2.7 V     | - 0.3                       | 6.0                                   | V    |

| V <sub>SS_HV_AD</sub>      | SR  | ADC ground and low reference voltage with respect to ground (V <sub>SS_HV</sub> )                                        | _                                  | -0.1                        | 0.1                                   | V    |

| TV <sub>DD</sub>           | SR  | Slope characteristics on all V <sub>DD</sub> during power up <sup>(4)</sup> with respect to ground (V <sub>SS_HV</sub> ) | _                                  | 3.0 <sup>(5)</sup>          | 500 x 10 <sup>3</sup><br>(0.5 [V/µs]) | V/s  |

|                            |     | Voltage on any pin with respect to                                                                                       | _                                  | -0.3                        | 6.0                                   |      |

| V <sub>IN</sub>            | SR  | ground (V <sub>SS_HV_IOx</sub> ) with respect to ground (V <sub>SS_HV</sub> )                                            | Relative to V <sub>DD_HV_IOx</sub> | -0.3                        | V <sub>DD_HV_IOx</sub> + 0.3          | V    |

| V                          | SR  | Analog input voltage                                                                                                     | V <sub>DD_HV_REG</sub><br>< 2.7 V  | V <sub>SS_HV_AD</sub> - 0.3 | V <sub>DD_HV_AD</sub> + 0.3           | V    |

| V <sub>INAN</sub>          | JIX | Analog input voltage                                                                                                     | V <sub>DD_HV_REG</sub> > 2.7 V     | V <sub>SS_HV_AD</sub>       | V <sub>DD_HV_AD</sub>                 | V    |

| I <sub>INJPAD</sub>        | SR  | Injected input current on any pin during overload condition                                                              | _                                  | -10                         | 10                                    | mA   |

Max<sup>(1)</sup> **Conditions Symbol Parameter** Min Unit 3.0 3.6 3.3 V voltage regulator SR ٧  $V_{DD\_HV\_REG}$ Relative to supply voltage  $V_{DD\_HV\_IOx} + 0.1$  $V_{DD\_HV\_IOx} - 0.1$  $V_{DD\_HV\_IOx}$ 3.0 5.5 3.3 V ADC supply and high SR ٧ V<sub>DD HV AD</sub> Relative to reference voltage 5.5 V<sub>DD\_HV\_REG</sub> – 0.1  $V_{DD\_HV\_REG}$ ADC ground and low  $V_{SS\_HV\ AD}$ SR 0 0 reference voltage  $V_{DD\_LV\_REGCOR}^{(3),(4)}$ SR ٧ Internal supply voltage V<sub>SS LV REGCOR</sub>(3) SR Internal reference voltage 0 0 ٧  $V_{DD\_LV\_CORx}^{-}$ SR Internal supply voltage V V<sub>SS\_LV\_CORx</sub><sup>(3)</sup> ٧ 0 0 SR Internal reference voltage Ambient temperature under °C  $T_A$ SR <del>-4</del>0 125 bias

Table 11. Recommended operating conditions (3.3 V) (continued)

Figure 7 shows the constraints of the different power supplies.

Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2.</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD\_HV\_IOy} - V_{DD\_HV\_IOx}| < 100$  mV.

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an

on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to

high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast

emitter.

<sup>4.</sup> The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

SR

SR

SR

$C_{DEC2}$

C<sub>DEC3</sub>

L<sub>Req</sub>

Value С **Conditions Symbol Parameter** Unit Min Max Тур Output voltage under ٧ V<sub>DD LV\_REGCOR</sub> CC Ρ maximum load run supply Post-trimming 1.15 1.32 current configuration BJT from Table 16. 3 capacitances (i.e. X7R or 19.5 30 μF X8R capacitors) with nominal External decoupling/stability  $C_{\text{DEC1}}$ SR value of 10 µF ceramic capacitor BJT BC817, one capacitance 14.3 22 μF of 22 µF BJT from Table 16. 3x10 µF. Resulting ESR of all three Absolute maximum value 50  $\text{m}\Omega$ capacitors of CDEC1 between 100 kHz and 10 MHz SR **RREG** BJT BC817, 1x 22 µF. Resulting ESR of the unique Absolute maximum value 10 40  $\mathsf{m}\Omega$ capacitor C<sub>DEC1</sub> between 100 kHz and 10 MHz 4 capacitances (i.e. X7R or

Table 17. Voltage regulator electrical characteristics

#### 3.8.2 Voltage monitor electrical characteristics

External decoupling/stability

External decoupling/stability

Resulting ESL of  $V_{DD\ HV\ REG}$

BCTRL and V<sub>DD LV CORx</sub> pins

ceramic capacitor

ceramic capacitor on

V<sub>DD HV REG</sub>

The device implements a Power On Reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the V<sub>DD</sub> and the V<sub>DD LV</sub> voltage while device is supplied:

C<sub>DEC1</sub>

X8R capacitors) with nominal

3 capacitances (i.e. X7R or X8R capacitors) with nominal

value of 10  $\mu$ F;  $C_{DEC3}$  has to

be equal or greater than

value of 440 nF

1200

19.5

1760

30

nF

μF

nΗ

15

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0V  $\pm$  10% range

- LVDLVCOR monitors low voltage digital power domain

DocID18340 Rev 6 60/105

#### 3.11.2 DC electrical characteristics (3.3 V)

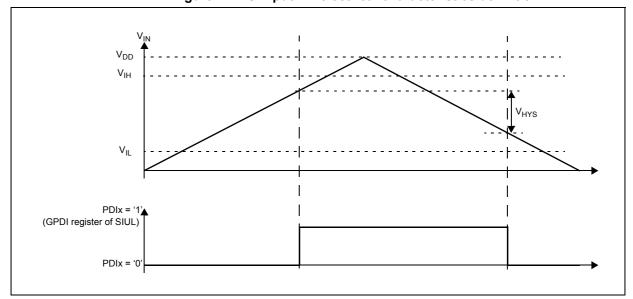

*Table 22* gives the DC electrical characteristics at 3.3 V (3.0 V <  $V_{DD\_HV\_IOX}$  < 3.6 V, NVUSRO[PAD3V5V]=1) as described in *Figure 14*.

Figure 14. I/O input DC electrical characteristics definition

Table 22. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V]=1)<sup>(1)</sup>

| Symbo               | I | Parameter                            | Conditions                 | Min                          | Max                           | Unit |

|---------------------|---|--------------------------------------|----------------------------|------------------------------|-------------------------------|------|

| V <sub>IL</sub>     | D | Minimum low level input voltage      | _                          | -0.1 <sup>(2)</sup>          | _                             | V    |

| V <sub>IL</sub>     | Р | Maximum low level input voltage      | _                          | _                            | 0.35 V <sub>DD_HV_IOx</sub>   | V    |

| V <sub>IH</sub>     | Р | Minimum high level input voltage     | _                          | 0.65 V <sub>DD_HV_IOx</sub>  | _                             | V    |

| V <sub>IH</sub>     | D | Maximum high level input voltage     | _                          | _                            | $V_{DD\_HV\_IOx} + 0.1^{(2)}$ | V    |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis           | _                          | 0.1 V <sub>DD_HV_IOx</sub>   | _                             | V    |

| V <sub>OL_S</sub>   | Р | Slow, low level output voltage       | I <sub>OL</sub> = 1.5 mA   | _                            | 0.5                           | V    |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage      | $I_{OH} = -1.5 \text{ mA}$ | $V_{DD\_HV\_IOx} - 0.8$      |                               | V    |

| V <sub>OL_M</sub>   | Р | Medium, low level output voltage     | I <sub>OL</sub> = 2 mA     | _                            | 0.5                           | ٧    |

| V <sub>OH_M</sub>   | Р | Medium, high level output voltage    | I <sub>OH</sub> = -2 mA    | $V_{DD\_HV\_IOx} - 0.8$      | _                             | V    |

| V <sub>OL_F</sub>   | Р | Fast, high level output voltage      | I <sub>OL</sub> = 11 mA    | _                            | 0.5                           | V    |

| V <sub>OH_F</sub>   | Р | Fast, high level output voltage      | I <sub>OH</sub> = -11 mA   | $V_{DD\_HV\_IOx} - 0.8$      | _                             | V    |

| V <sub>OL_SYM</sub> | Р | Symmetric, high level output voltage | I <sub>OL</sub> = 1.5 mA   | _                            | 0.5                           | ٧    |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OH</sub> = -1.5 mA  | V <sub>DD_HV_IOx</sub> – 0.8 | 1                             | ٧    |

| la                  | Р | Equivalent pull-up current           | $V_{IN} = V_{IL}$          | -130                         |                               | μA   |

| I <sub>PU</sub>     | • | Legarvaioni paii-ap canent           | $V_{IN} = V_{IH}$          | _                            | -10                           | μΛ   |

INTERNAL CIRCUIT SCHEME **EXTERNAL CIRCUIT** Channel Extended Sampling Selection Switch Source Filter **Current Limiter**  $\triangle$ R<sub>S</sub>: Source impedance R<sub>F</sub>: Filter resistance C<sub>F</sub>: Filter capacitance R<sub>L</sub>: Current limiter resistance  $R_{SW1}$ : Channel selection switch impedance (two contributions,  $R_{SW1}$  and  $R_{SW2}$ ) R<sub>AD</sub>: Sampling switch impedance  $C_{P}\!\!:$  Pin capacitance (two contributions,  $C_{P1},\,C_{P2}$  and  $C_{P3})$ C<sub>S</sub>: Sampling capacitance

Figure 17. Input equivalent circuit (extended channels)

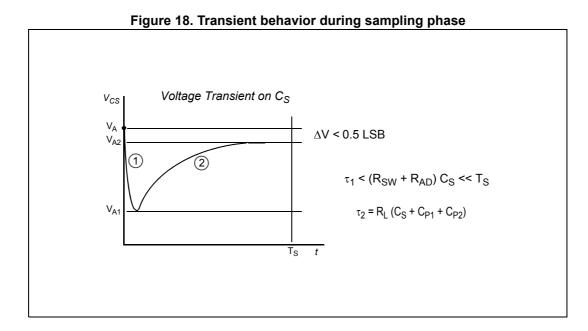

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 16*): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

5

| Symbo | Symbol Parameter Conditions <sup>(1)</sup> Min |                                               | Conditions(1)         |     | Value |   | Unit |

|-------|------------------------------------------------|-----------------------------------------------|-----------------------|-----|-------|---|------|

| Symbo |                                                |                                               | Тур                   | Max | Oilit |   |      |

| TUE   | Т                                              | Total unadjusted error with current injection | 16 precision channels | -3  | _     | 3 | LSB  |

| TUE   | Т                                              | Total unadjusted error with current injection | 10 standard channels  | -4  | _     | 4 | LSB  |

Table 32. ADC conversion characteristics (continued)

- V<sub>DD</sub> = 3.3 V to 3.6 V / 4.5 V to 5.5 V, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified and analog input voltage from V<sub>SS\_HV\_AD</sub> to V<sub>DD\_HV\_AD</sub>.

- V<sub>INAN</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

- 3. AD\_clk clock is always half of the ADC module input clock defined via the auxiliary clock divider for the ADC.

- 4. When configured to allow 60 MHz ADC, the minimum ADC clock speed is 9 MHz, below which precision is lost.

- 5. During the sample time the input capacitance CS can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>ADC\_S</sub>. After the end of the sample time t<sub>ADC\_S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>ADC\_S</sub> depend on programming.

- 6. This parameter includes the sample time  $t_{ADC\ S}$ .

- 7. 20 MHz ADC clock. Specific prescaler is programmed on MC PLL CLK to provide 20 MHz clock to the ADC.

- 8. See Figure 16.

### 3.16 Flash memory electrical characteristics

Table 33. Program and erase specifications

|                          |   |                                                   |            | Value |                    |                               |                    |      |

|--------------------------|---|---------------------------------------------------|------------|-------|--------------------|-------------------------------|--------------------|------|

| Symbol                   |   | Parameter Conditions                              |            | Min   | Typ <sup>(1)</sup> | Initial<br>max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |

| T <sub>wprogram</sub>    | Р | Word Program (32 bits) Time <sup>(4)</sup>        | Data Flash | _     | 30                 | 70                            | 500                | μs   |

| T <sub>dwprogram</sub>   | Р | Double Word (64 bits) Program Time <sup>(4)</sup> | Code Flash | _     | 18                 | 50                            | 500                | μs   |

| Tayana                   | Р | Bank Program (64 KB) <sup>(4), (5)</sup>          | Data Flash | _     | 0.49               | 1.2                           | 4.1                | s    |

| T <sub>BKPRG</sub>       | Р | Bank Program (1056 KB) <sup>(4), (5)</sup>        | Code Flash | _     | 2.6                | 6.6                           | 66                 | s    |

| T <sub>MDPRG</sub>       | Р | Module Program (512 KB) <sup>(4)</sup>            | Code Flash | _     | 1.3                | 1.65                          | 33                 | S    |

| T                        | Р | 16 KB Block Pre-program and Erase Time            | Code Flash |       | 200                | 500                           | 5000               | ms   |

| T <sub>16kpperase</sub>  | ' | To No block Tre-program and Erase Time            | Data Flash |       | 700                | 800                           | 3000               | 1113 |

| T <sub>32kpperase</sub>  | Р | 32 KB Block Pre-program and Erase Time            | Code Flash | _     | 300                | 600                           | 5000               | ms   |

| T <sub>64kpperase</sub>  | Р | 64 KB Block Pre-program and Erase Time            | Code Flash | _     | 400                | 900                           | 5000               | ms   |

| T <sub>128kpperase</sub> | Р | 128 KB Block Pre-program and Erase Time           | Code Flash | _     | 600                | 1300                          | 5000               | ms   |

| t                        | Р | P Erase Suspend Request Rate <sup>(6)</sup>       | Code Flash | 20    |                    |                               |                    | ms   |

| t <sub>ESRT</sub>        | Р |                                                   | Data Flash | 10    |                    | _                             |                    | 1113 |

Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

<sup>2.</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

- The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

- 4. Actual hardware programming times. This does not include software overhead.

- Typical bank programming time assumes that all cells are programmed in a single pulse. In reality some cells will require more than one pulse, adding a small overhead to total bank programming time (see Initial Max column).

- 6. Time between erase suspend resume and next erase suspend.

Table 34. Flash memory module life

| Cumbo     |   | Parameter                                                                                                         | Conditions                         | Val    | ue     | Unit   |

|-----------|---|-------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|--------|--------|

| Symbo     | ı | Parameter                                                                                                         | Conditions                         | Min    | Тур    | Unit   |

| P/E       | С | Number of program/erase cycles per block for 16 KB blocks over the operating temperature range (T <sub>J</sub> )  | _                                  | 100000 | 100000 | cycles |

| P/E       | O | Number of program/erase cycles per block for 32 KB blocks over the operating temperature range (T <sub>J</sub> )  | _                                  | 10000  | 100000 | cycles |

| P/E       | O | Number of program/erase cycles per block for 64 KB blocks over the operating temperature range (T <sub>J</sub> )  | _                                  | 10000  | 100000 | cycles |

| P/E       | С | Number of program/erase cycles per block for 128 KB blocks over the operating temperature range (T <sub>J</sub> ) | _                                  | 1000   | 100000 | cycles |

|           |   |                                                                                                                   | Blocks with 0 – 1000<br>P/E cycles | 20     | _      | years  |

| Retention | С | Minimum data retention at 85 °C average ambient temperature <sup>(1)</sup>                                        | Blocks with 10000 P/E cycles       | 10     | _      | years  |

|           |   |                                                                                                                   | Blocks with 100000 P/E cycles      | 5      | _      | years  |

Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

Table 35. Flash read access timing

| Symbol | С | Parameter Conditions <sup>(1)</sup>                                                |               | Max | Unit    |

|--------|---|------------------------------------------------------------------------------------|---------------|-----|---------|

| Fmax   | С | Maximum working frequency for Code Flash                                           | 2 wait states | 66  | MHz     |

| Tillax |   | at given number of WS in worst conditions                                          | 0 wait states | 22  | 1011 12 |

| Fmax   | С | Maximum working frequency for Data Flash at given number of WS in worst conditions | 8 wait states | 66  | MHz     |

<sup>1.</sup> VDD =  $3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ , TA =  $-40 \text{ to } 125 \,^{\circ}\text{C}$ , unless otherwise specified.

### 3.17 AC specifications

#### 3.17.1 Pad AC specifications

Table 36. Output pin transition times

| Symbol               |    | С   | Parameter                                                           | Conditions <sup>(1)</sup>  |                                                               |                    | Value |     |      |

|----------------------|----|-----|---------------------------------------------------------------------|----------------------------|---------------------------------------------------------------|--------------------|-------|-----|------|

|                      |    | J   | raiametei                                                           | Conditions                 |                                                               | Min                | Тур   | Max | Unit |

| T <sub>tr</sub>      | СС | D   | Output transition time output pin <sup>(2)</sup> SLOW configuration | C <sub>L</sub> = 25 pF     | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0                 | _                  | _     | 50  |      |

|                      |    | Т   |                                                                     | C <sub>L</sub> = 50 pF     |                                                               | _                  | _     | 100 |      |

|                      |    | D   |                                                                     | C <sub>L</sub> = 100 pF    |                                                               | _                  | _     | 125 | ns   |

|                      |    | D   |                                                                     | C <sub>L</sub> = 25 pF     |                                                               |                    | _     | 40  |      |

|                      |    | Т   |                                                                     | C <sub>L</sub> = 50 pF     | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                 | _                  | _     | 50  |      |

|                      |    | D   |                                                                     | C <sub>L</sub> = 100 pF    |                                                               |                    | _     | 75  |      |

|                      |    | D   | Output transition time output pin <sup>(2)</sup>                    | C <sub>L</sub> = 25 pF     | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                 | _                  | _     | 10  | - ns |

| T <sub>tr</sub> (    | СС | Т   |                                                                     | C <sub>L</sub> = 50 pF     |                                                               | _                  | _     | 20  |      |

|                      |    | C D |                                                                     | C <sub>L</sub> = 100 pF    |                                                               | _                  | _     | 40  |      |

|                      |    |     | MEDIUM configuration                                                | C <sub>L</sub> = 25 pF     |                                                               | _                  | _     | 12  |      |

|                      |    | Т   |                                                                     | C <sub>L</sub> = 50 pF     |                                                               | _                  | _     | 25  |      |

|                      |    | D   |                                                                     | C <sub>L</sub> = 100 pF    |                                                               | _                  | _     | 40  |      |

| T <sub>tr</sub>      | CC | C D | Output transition time output pin <sup>(2)</sup> FAST configuration | C <sub>L</sub> = 25 pF     | SIUL.PCRx.SRC = 1  V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _                  | _     | 4   |      |

|                      |    |     |                                                                     | C <sub>L</sub> = 50 pF     |                                                               | _                  | _     | 6   |      |

|                      |    |     |                                                                     | C <sub>L</sub> = 100 pF    |                                                               | _                  | _     | 12  | ne   |

|                      |    |     |                                                                     | C <sub>L</sub> = 25 pF     |                                                               | _                  | _     | 4   | ns   |

|                      |    |     |                                                                     | C <sub>L</sub> = 50 pF     |                                                               | _                  | 7     |     |      |

|                      |    |     |                                                                     | C <sub>L</sub> = 100 pF    | SIUL.PCRx.SRC = 1                                             | _                  | _     | 12  | ]    |

| T <sub>sim</sub> (3) | CC | Т   | Symmetric, same drive strength                                      | V <sub>DD</sub> = 5.0 V    | ± 10%, PAD3V5V = 0                                            | _                  | _     | 4   | ns   |

| 'sim` '              |    |     | between N and P trai                                                | between N and P transistor | $V_{DD} = 3.3 \text{ V}$                                      | ± 10%, PAD3V5V = 1 | _     | _   | 5    |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 °C to  $T_{A\ MAX}$ , unless otherwise specified.

### 3.18 AC timing characteristics

### 3.18.1 RESET pin characteristics

The SPC56xP54x/SPC56xP60x implements a dedicated bidirectional RESET pin.

<sup>2.</sup>  $C_L$  includes device and package capacitances ( $C_{PKG}$  < 5 pF).

<sup>3.</sup> Transition timing of both positive and negative slopes will differ maximum 50 %.

Figure 23. JTAG test access port timing

Table 41. DSPI timing<sup>(1)</sup> (continued)

| No. | Syml | bol C        |      | Parameter                   | Conditions                  | Min | Max | Unit |  |

|-----|------|--------------|------|-----------------------------|-----------------------------|-----|-----|------|--|

|     |      |              | CC D | Data hold time for outputs  | Master (MTFE = 0)           | -2  | _   |      |  |

| 12  |      | dO CC D Data |      |                             | Slave                       | 6   | _   | 200  |  |

| 12  | ίнο  |              |      | Data fiold time for outputs | Master (MTFE = 1, CPHA = 0) | 6   | _   | ns   |  |

|     |      |              |      |                             | Master (MTFE = 1, CPHA = 1) | -2  | _   |      |  |

<sup>1.</sup> All timing are provided with 50pF capacitance on output, 1ns transition time on input signal

Figure 29. DSPI classic SPI timing — master, CPHA = 0

92/105 DocID18340 Rev 6

Table 42. LQFP144 mechanical data

| Symphol            |        | mm     |        | inches <sup>(1)</sup> |        |        |  |

|--------------------|--------|--------|--------|-----------------------|--------|--------|--|

| Symbol             | Min    | Тур    | Max    | Min                   | Тур    | Max    |  |

| А                  | _      | _      | 1.600  | _                     | _      | 0.0630 |  |

| A1                 | 0.050  | _      | 0.150  | 0.0020                | _      | 0.0059 |  |

| A2                 | 1.350  | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b                  | 0.170  | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С                  | 0.090  | _      | 0.200  | 0.0035                | _      | 0.0079 |  |

| D                  | 21.800 | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| D1                 | 19.800 | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| D3                 | _      | 17.500 | _      | _                     | 0.6890 | _      |  |

| E                  | 21.800 | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| E1                 | 19.800 | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| E3                 | _      | 17.500 | _      | _                     | 0.6890 | _      |  |

| е                  | _      | 0.500  | _      | _                     | 0.0197 | _      |  |

| L                  | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1                 | _      | 1.000  | _      | _                     | 0.0394 | _      |  |

| k                  | 0.0 °  | 3.5 °  | 7.0°   | 3.5 °                 | 0.0 °  | 7.0 °  |  |

| ccc <sup>(2)</sup> | 0.080  |        |        | 0.0031                |        |        |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

<sup>2.</sup> Tolerance.

# 5 Ordering information

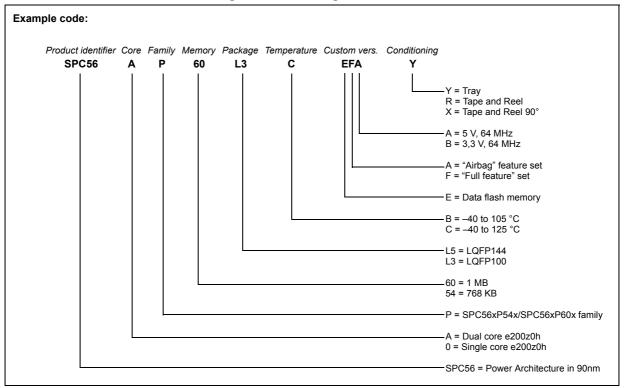

Figure 40. Ordering information scheme<sup>(h)</sup>

577

h. Not all configurations are available on the market. Please contact your ST sales representative to get the list of orderable commercial part number.

# 6 Revision history

*Table 44* summarizes revisions to this document.

Table 44. Document revision history

| Date        | Revision | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Dec-2010 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18-Oct-2011 | 2        | In the Feature list: Revised the first bullet. Changed "Up to 82 GPIO" to "Up to 80 GPIO" Changed "FlexRay module" to "1 FlexRay™ module". Added Section 1.5: Feature details Table 4: SPC56xP54x/SPC56xP60x series block summary, added FlexRay entry. In the "LQFP176 pinout (top view)" figure:  − Pin 104 now is TDI, was PB[5]  − Pin 107 now is TDO, was PB[4]  − Pin 71 now is NC, was OKOUT  − Pin 72 now is NC, was OKOUT  − Pin 88 now is NC, was OKOUT  − Pin 88 now is NC, was IPP_LIVI_B_VDDIO Table 7: Pin muxing:  PB[6] was clk_out_div5, is now clk_out_div256 Removed PB[4] and PB[5] rows In the A[3] row, changed ABS[2] to ABS[1] Section 3.11: DC electrical characteristics, added "Peripherals supply current (5 V and 3.3 V)" table Table 14: EMI testing specifications, removed all references to SAE Replaced both Table 12: Thermal characteristics for 144-pin LQFP and Table 30: PLLMRFM electrical specifications (V <sub>DDPLL</sub> = 1.08 V to 1.32 V, V <sub>SS</sub> = V <sub>SSPLL</sub> = 0 V, TA = TL to TH), changed the max value of f <sub>SYS</sub> from 120 to 64 Table 33: Program and erase specifications: Removed all TBC changed the initial max value of T <sub>BKPRG</sub> (Code Flash) from 3.3 to 6.6 s changed the max value of T <sub>BKPRG</sub> (Data Flash) from 3.0 to 500 μs Added t <sub>ESRT</sub> row Table 17: Voltage regulator electrical characteristics, updated V <sub>DD_L</sub> v <sub>REGCOR</sub> values Updated Table 18: Low voltage monitor electrical characteristics Updated Table 18: Low voltage monitor electrical characteristics Updated Table 21: Supply current (5.0 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.3 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.4 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.5 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.6 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.8 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.8 V, NVUSRO[PAD3V5V]=0) and Table 23: Supply current (3.8 V, NVUSRO[PAD3V5V]=0) |