Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p54l5cefay |

allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority.

- Modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and IOP critical interrupt mechanism

The INTC module is replicated for each processor.

# 1.5.7 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC56xP54x/SPC56xP60x:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- Programmable output clock divider (÷1, ÷2, ÷3 to ÷256)

- eTimer module running at the same frequency as the e200z0h core

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode

- Supports frequency trimming by user application

### 1.5.8 Frequency modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4 MHz to 40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The FMPLL multiplication factor, output clock divider ratio are all software configurable.

The FMPLL has the following major features:

- Input clock frequency from 4 MHz to 40 MHz

- Voltage controlled oscillator (VCO) range from 256 MHz to 512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the PLL to relock

- Modulation enabled/disabled through software

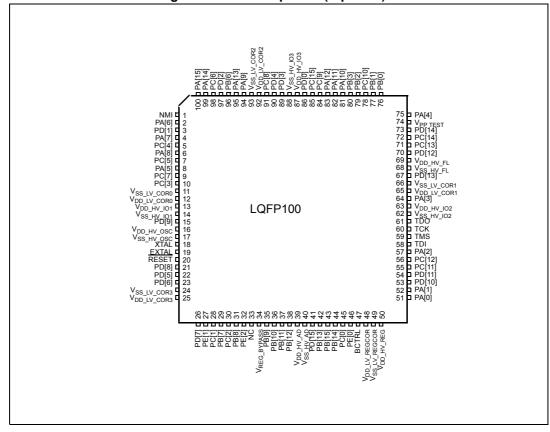

Figure 4. LQFP100 pinout (top view)(d)

# 2.2 Pin descriptions

The following sections provide signal descriptions and related information about the functionality and configuration of the SPC56xP54x/SPC56xP60x devices.

# 2.2.1 Power supply and reference voltage pins

*Table 5* lists the power supply and reference voltage for the SPC56xP54x/SPC56xP60x devices.

Supply

Pin

Symbol

Description

LQFP 100

LQFP 144

LQFP 176<sup>(1)</sup>

VREG control and power supply pins

BCTRL

Voltage regulator external NPN Ballast base control pin

47

69

81

Table 5. Supply pins

d. Availability of port pin alternate functions depends on product selection.

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Dorest      | DOD        | Alternate                         |                                        | Davish sand                  | 1/0              |         | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|-----------------------------------|----------------------------------------|------------------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup> (3)      | Functions                              | Peripheral<br>(4)            | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

| B[9]        | PCR[25]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[25]<br>—<br>—<br>—<br>—<br>AN[11] | SIUL<br>—<br>—<br>—<br>ADC_0 | Input Only       |         |                     | 35          | 52          | 60                         |

| B[10]       | PCR[26]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[26]<br>—<br>—<br>—<br>—<br>AN[12] | SIUL<br><br><br><br>ADC_0    | Input Only       | _       | _                   | 36          | 53          | 61                         |

| B[11]       | PCR[27]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[27]<br>—<br>—<br>—<br>—<br>AN[13] | SIUL  ADC_0                  | Input Only       | _       | _                   | 37          | 54          | 62                         |

| B[12]       | PCR[28]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[28]<br>—<br>—<br>—<br>—<br>AN[14] | SIUL  ADC_0                  | Input Only       | _       | _                   | 38          | 55          | 63                         |

| B[13]       | PCR[29]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[29]  AN[16] RXD                   | SIUL  —  —  ADC_0  LINFlex_1 | Input Only       | _       | _                   | 42          | 60          | 68                         |

| B[14]       | PCR[30]    | ALT0 ALT1 ALT2 ALT3               | GPIO[30]  AN[17] ETC[4] EIRQ[19]       | SIUL  ADC_0 eTimer_0 SIUL    | Input Only       | _       | _                   | 44          | 64          | 76                         |

| B[15]       | PCR[31]    | ALT0 ALT1 ALT2 ALT3 —             | GPIO[31]  AN[18] EIRQ[20]              | SIUL  ADC_0 SIUL             | Input Only       | _       | _                   | 43          | 62          | 70                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|      | Table 7. Pin muxing(1) (continued) |                                   |                                                    |                                          |                             |         |                     |             |             |                            |  |  |

|------|------------------------------------|-----------------------------------|----------------------------------------------------|------------------------------------------|-----------------------------|---------|---------------------|-------------|-------------|----------------------------|--|--|

| Port | PCR                                | Alternate                         |                                                    | Peripheral                               | I/O                         | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |  |  |

| pin  | No.                                | function <sup>(2),</sup> (3)      | Functions                                          | (4)                                      | direction<br>(5)            | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |  |

|      |                                    |                                   |                                                    | Po                                       | ort C                       |         |                     |             |             |                            |  |  |

| C[0] | PCR[32]                            | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[32]<br>—<br>—<br>—<br>—                       | SIUL<br>—<br>—<br>—                      | Input Only                  | _       | _                   | 45          | 66          | 78                         |  |  |

| C[1] | PCR[33]                            | ALT0 ALT1 ALT2 ALT3 —             | AN[19]  GPIO[33]  —  —  AN[2]                      | ADC_0 SIUL ADC_0                         | Input Only                  | _       | _                   | 28          | 41          | 49                         |  |  |

| C[2] | PCR[34]                            | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[34]<br>—<br>—<br>—<br>—<br>AN[3]              | SIUL  ADC_0                              | Input Only                  |         |                     | 30          | 45          | 53                         |  |  |

| C[3] | PCR[35]                            | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[35]<br>CS1_0<br>ETC[4]<br>TXD<br>EIRQ[21]     | SIUL DSPI_0 eTimer_1 LINFlex_1 SIUL      | I/O<br>O<br>I/O<br>O<br>I   | Slow    | Medium              | 10          | 16          | 24                         |  |  |

| C[4] | PCR[36]                            | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[36]<br>CS0_0<br>—<br>DEBUG[4]<br>EIRQ[22]     | SIUL<br>DSPI_0<br>—<br>SSCM<br>SIUL      | I/O<br>I/O<br>—<br>—<br>I   | Slow    | Medium              | 5           | 11          | 19                         |  |  |

| C[5] | PCR[37]                            | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[37]<br>SCK_0<br>SCK_4<br>DEBUG[5]<br>EIRQ[23] | SIUL<br>DSPI_0<br>DSPI_4<br>SSCM<br>SIUL | 1/O<br>1/O<br>1/O<br>—<br>I | Slow    | Medium              | 7           | 13          | 21                         |  |  |

| C[6] | PCR[38]                            | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[38] SOUT_0 — DEBUG[6] EIRQ[24]                | SIUL<br>DSPI_0<br>—<br>SSCM<br>SIUL      | I/O<br>O<br>—<br>—<br>I     | Slow    | Medium              | 98          | 142         | 174                        |  |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |                        | Alternate                    |           | . 7. Pin mux      | I/O              |         | speed <sup>(6)</sup> |             | Pin             |                            |  |  |      |  |   |  |  |  |  |  |  |

|-------------|------------------------|------------------------------|-----------|-------------------|------------------|---------|----------------------|-------------|-----------------|----------------------------|--|--|------|--|---|--|--|--|--|--|--|

| Port<br>pin | PCR<br>No.             | function <sup>(2),</sup> (3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1              | LQFP<br>100 | LQFP<br>144     | LQFP<br>176 <sup>(7)</sup> |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[47]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT1                         | CA_TR_EN  | FlexRay_0         | 0                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| C[15]       | PCR[47]                | ALT2                         | ETC[0]    | eTimer_1          | I/O              | Slow    | Symmetric            | 85          | 124             | 148                        |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         |           |                   | _                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | _                            | EXT_IN    | CTU_0             | I                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        |                              |           |                   |                  |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[48]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[0]        | PCR[48]                | ALT1                         | CA_TX     | FlexRay_0         | 0                | Slow    | Symmetric            | 86          | 125             | 149                        |  |  |      |  |   |  |  |  |  |  |  |

| امام        | i Cit[ <del>1</del> 0] | ALT2                         | ETC[1]    | eTimer_1          | I/O              | Siow    | Symmetric            | 00          | 123             | 143                        |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         | _         | 1                 | -                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[49]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT1                         | CS4_1     | DSPI_1            | 0                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[1]        | PCR[49]                | ALT2                         | ETC[2]    | eTimer_1          | I/O              | Slow    | Medium               | 3           | 3               | 3                          |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         | EXT_TRG   | CTU_0             | 0                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | _                            | CA_RX     | FlexRay_0         | 1                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[50]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT1                         | CS5_1     | DSPI_1            | 0                | Slow    |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[2]        | PCR[50]                | ALT2                         | ETC[3]    | eTimer_1          | I/O              |         | Medium               | 97          | 140             | 168                        |  |  |      |  |   |  |  |  |  |  |  |

|             |                        |                              |           |                   |                  |         |                      |             |                 |                            |  |  | ALT3 |  | _ |  |  |  |  |  |  |

|             |                        | _                            | CB_RX     | FlexRay_0         | I                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[51]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[3]        | PCR[51]                | ALT1                         | CB_TX     | FlexRay_0         | 0                | Slow    | Symmetric            | 89          | 128             | 152                        |  |  |      |  |   |  |  |  |  |  |  |

| D[O]        | rorqon                 | ALT2                         | ETC[4]    | eTimer_1          | I/O              | Ciow    | Cymmetric            | 00          | 120             | 102                        |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         | _         | _                 | _                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[52]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[4]        | PCR[52]                | ALT1                         | CB_TR_EN  | FlexRay_0         | 0                | Slow    | Symmetric            | 90          | 129             | 153                        |  |  |      |  |   |  |  |  |  |  |  |

| -[.]        | . 0[0_]                | ALT2                         | ETC[5]    | eTimer_1          | I/O              | 0.011   | 9,,,,,,              |             | 0               |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         |           | _                 | _                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[53]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[5]        | PCR[53]                | ALT1                         | CS3_0     | DSPI_0            | 0                | Slow    | Medium               | 22          | 33              | 41                         |  |  |      |  |   |  |  |  |  |  |  |

| D[O]        | i Ort[00]              | ALT2                         | _         | _                 | _                | Ciow    | Wicalam              |             | 00              | 71                         |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         | SOUT_3    | DSPI_3            | 0                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT0                         | GPIO[54]  | SIUL              | I/O              |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

| D[6]        | PCR[54]                | ALT1                         | CS2_0     | DSPI_0            | 0                | Slow    | w Medium             | 23          | 34              | 42                         |  |  |      |  |   |  |  |  |  |  |  |

| اداما       | 1 OI ([J+]             | ALT2                         | SCK_3     | DSPI_3            | I/O              | Slow    |                      | 20          | J- <del>1</del> | 74                         |  |  |      |  |   |  |  |  |  |  |  |

|             |                        | ALT3                         | SOUT_4    | DSPI_4            | 0                |         |                      |             |                 |                            |  |  |      |  |   |  |  |  |  |  |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Dorest      | DOD        | Alternate                       |             | Daniah anal       | 1/0              | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|---------------------------------|-------------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions   | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |            | ALT0                            | GPIO[55]    | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | CS3_1       | DSPI_1            | 0                |         |                     |             |             |                            |

| D[7]        | PCR[55]    | ALT2                            | _           | _                 | _                | Slow    | Medium              | 26          | 37          | 45                         |

|             |            | ALT3                            | CS4_0       | DSPI_0            | 0                |         |                     |             |             |                            |

|             |            | _                               | SIN_3       | DSPI_3            | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[56]    | SIUL              | I/O              |         |                     |             |             |                            |

| D[8]        | PCR[56]    | ALT1                            | CS2_1       | DSPI_1            | 0                | Slow    | Medium              | 21          | 32          | 40                         |

|             |            | ALT2                            | RDY         | nexus_0           | 0                |         |                     |             |             |                            |

|             |            | ALT3                            | CS5_0       | DSPI_0            | 0                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[57]    | SIUL              | I/O              |         |                     |             |             |                            |

| D[9]        | PCR[57]    | ALT1                            |             |                   | _                | Slow    | Medium              | 15          | 26          | 34                         |

|             |            | ALT2                            | TXD         | LINFlex_1         | 0                |         |                     |             |             |                            |

|             |            | ALT3                            | CS6_1       | DSPI_1            | 0                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[58]    | SIUL              | I/O              |         |                     |             |             |                            |

| D[10]       | PCR[58]    | ALT1                            |             | _                 | _                | Slow    | Medium              | 53          | 76          | 92                         |

| _[]         |            | ALT2                            | CS0_3       | DSPI_3            | I/O              |         |                     |             |             |                            |

|             |            | ALT3                            |             | _                 | _                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[59]    | SIUL              | I/O              |         |                     |             |             |                            |

| D[11]       | PCR[59]    | ALT1                            | _           | _                 | _                | Slow    | Medium              | 54          | 78          | 94                         |

|             |            | ALT2                            | CS1_3       | DSPI_3            | 0                | 0.0     |                     |             |             |                            |

|             |            | ALT3                            | SCK_3       | DSPI_3            | I/O              |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[60]    | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | _           | _                 | _                |         |                     |             |             |                            |

| D[12]       | PCR[60]    | ALT2                            |             |                   | _                | Slow    | Medium              | Medium 70   | 99          | 123                        |

|             |            | ALT3                            | CS7_1       | DSPI_1            | 0                |         |                     |             |             |                            |

|             |            | _                               | RXD         | LINFlex_1         | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[61]    | SIUL              | I/O              |         |                     |             |             |                            |

| D[13]       | PCR[61]    | ALT1                            | _           | _                 | _                | Slow    | Medium              | 67          | 95          | 119                        |

| ' '         |            | ALT2                            | CS2_3       | DSPI_3            | 0                |         |                     |             |             |                            |

|             |            | ALT3                            | SOUT_3      | DSPI_3            | 0                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[62]    | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | _           | _                 | _                |         |                     |             |             |                            |

| D[14]       | PCR[62]    | ALT2                            | CS3_3       | DSPI_3            | 0                | Slow    | Medium              | 73          | 105         | 129                        |

|             |            | ALT3                            | CIN 2       |                   |                  |         |                     |             |             |                            |

|             |            |                                 | SIN_3       | DSPI_3            | 1                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[63]    | SIUL              |                  |         |                     |             |             |                            |

| D:4 = 7     | DODIO:     | ALT1                            | _           | _                 | Immi + O -1      |         |                     | 4.4         |             | 00                         |

| D[15]       | PCR[63]    | ALT2                            | _           | _                 | Input Only       | _       | <b>—</b> 41         | 58          | 66          |                            |

|             |            | ALT3                            | —<br>AN[20] | ADC_0             |                  |         |                     |             |             |                            |

|             |            | _                               | ۸۱۷[ZU]     | YPC_0             |                  |         |                     |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |            | Alternate                         |                                        | 7. Pin mux                   | I/O              |             | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|-----------------------------------|----------------------------------------|------------------------------|------------------|-------------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup> (3)      | Functions                              | Peripheral<br>(4)            | direction<br>(5) | SRC = 0     | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |            |                                   |                                        | Po                           | ort E            |             |                     |             |             |                            |

| E[0]        | PCR[64]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[64]<br>—<br>—<br>—<br>—<br>AN[21] | SIUL<br>—<br>—<br>—<br>ADC_0 | Input Only       | _           | _                   | 46          | 68          | 80                         |

| E[1]        | PCR[65]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[65]  — — — AN[4]                  | SIUL  ADC_0                  | Input Only       | _           | _                   | 27          | 39          | 47                         |

| E[2]        | PCR[66]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[66]<br>—<br>—<br>—<br>—<br>AN[5]  | SIUL ADC_0                   | Input Only       | nput Only — |                     | 32          | 49          | 57                         |

| E[3]        | PCR[67]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[67]<br>—<br>—<br>—<br>—<br>AN[6]  | SIUL  ADC_0                  | Input Only       | _           | _                   | _           | 40          | 48                         |

| E[4]        | PCR[68]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[68]<br>—<br>—<br>—<br>—<br>AN[7]  | SIUL  ADC_0                  | Input Only       | _           | _                   | _           | 42          | 50                         |

| E[5]        | PCR[69]    | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[69]<br>—<br>—<br>—<br>—<br>AN[8]  | SIUL  ADC_0                  | Input Only       | _           | _                   | _           | 44          | 52                         |

| E[6]        | PCR[70]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[70]<br>—<br>—<br>—<br>—<br>AN[9]  | SIUL  ADC_0                  | Input Only       | _           | _                   | _           | 46          | 54                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |            | Alternate                    |             |                   | I/O              | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|------------------------------|-------------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup> (3) | Functions   | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |            | ALT0                         | GPIO[71]    | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                         | _           | _                 |                  |         |                     |             |             |                            |

| E[7]        | PCR[71]    | ALT2                         | _           | _                 | Input Only       | _       | _                   | _           | 48          | 56                         |

|             |            | ALT3                         | —<br>AN[10] | ADC_0             |                  |         |                     |             |             |                            |

|             |            |                              |             |                   |                  |         |                     |             |             |                            |

|             |            | ALT0<br>ALT1                 | GPIO[72]    | SIUL              |                  |         |                     |             |             |                            |

| E[8]        | PCR[72]    | ALT1                         | _           | _                 | Input Only       |         |                     |             | 59          | 67                         |

|             | FCR[12]    | ALT2                         |             |                   | Input Only       | _       | _                   | _           | 39          | 07                         |

|             |            | — AL13                       | AN[22]      | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[73]    | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                         | —           | _                 |                  |         |                     |             |             |                            |

| E[9]        | PCR[73]    | ALT2                         | _           | _                 | Input Only       | _       | _                   | _           | 61          | 69                         |

|             |            | ALT3                         | _           | _                 |                  |         |                     |             |             |                            |

|             |            | _                            | AN[23]      | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[74]    | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                         | _           | _                 |                  |         |                     |             |             |                            |

| E[10]       | PCR[74]    | ALT2                         | _           | _                 | Input Only       | _       | _                   | _           | 63          | 75                         |

|             |            | ALT3                         | _           | _                 |                  |         |                     |             |             |                            |

|             |            | _                            | AN[24]      | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[75]    | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                         | _           | _                 |                  |         |                     |             |             |                            |

| E[11]       | PCR[75]    | ALT2                         | _           | _                 | Input Only       | _       | _                   | _           | 65          | 77                         |

|             |            | ALT3                         | —<br>AN[25] | ADC_0             |                  |         |                     |             |             |                            |

|             |            |                              |             |                   |                  |         |                     |             |             |                            |

|             |            | ALT0<br>ALT1                 | GPIO[76]    | SIUL              |                  |         |                     |             |             |                            |

| F[12]       | PCR[76]    | ALT1                         |             |                   | Input Only       | _       | _                   |             | 67          | 79                         |

| _[]         | 1 011[70]  | ALT3                         | _           | _                 | input Only       |         |                     |             | 01          | 70                         |

|             |            | _                            | AN[26]      | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[77]    | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                         | SCK_3       | DSPI_3            | I/O              |         |                     |             |             |                            |

| E[13]       | PCR[77]    | ALT2                         | _           | _                 | _                | Slow    | Medium              |             | 117         | 141                        |

|             |            | ALT3                         | _           | _                 | _                |         |                     |             |             |                            |

|             |            | _                            | EIRQ[25]    | SIUL              | 1                |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[78]    | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                         | SOUT_3      | DSPI_3            | 0                | Slow    |                     |             |             |                            |

| E[14]       | PCR[78]    | ALT2                         | _           | _                 | _                |         | Slow Medium         | _           | 119         | 143                        |

|             |            | ALT3                         |             | _                 |                  |         |                     |             |             |                            |

|             |            | _                            | EIRQ[26]    | SIUL              | I                |         |                     |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |            | Alternate                    |           |                   | 1/0              |         | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|------------------------------|-----------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup> (3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |            | ALT0<br>ALT1                 | GPIO[79]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                         |           |                   | _                |         |                     |             |             |                            |

| E[15]       | PCR[79]    | ALT3                         | _         | _                 | _                | Slow    | Medium              | Medium —    | 121         | 145                        |

|             |            | _                            | SIN_3     | DSPI_3            | I                |         |                     |             |             |                            |

|             |            | — EIRQ[27] SIUL I            |           |                   |                  |         |                     |             |             |                            |

|             |            |                              |           | Po                | ort F            |         |                     | •           |             |                            |

|             |            | ALT0                         | GPIO[80]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                         | DBG_0     | FlexRay_0         | 0                |         |                     |             |             |                            |

| F[0]        | PCR[80]    | ALT2                         | CS3_3     | DSPI_3            | 0                | Slow    | Medium              |             | 133         | 157                        |

|             |            | ALT3                         | _         | _                 | _                |         |                     |             |             |                            |

|             |            | _                            | EIRQ[28]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[81]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                         | DBG_1     | FlexRay_0         | 0                |         |                     |             |             |                            |

| F[1]        | PCR[81]    | ALT2                         | CS2_3     | DSPI_3            | 0                | Slow    | Medium              | _           | 135         | 159                        |

|             |            | ALT3                         | _         | _                 | _                |         |                     |             |             |                            |

|             |            | _                            | EIRQ[29]  | SIUL              | Į                |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[82]  | SIUL              | I/O              |         |                     |             |             |                            |

| F[2]        | PCR[82]    | ALT1                         | DBG_2     | FlexRay_0         | 0                | Slow    | Medium              |             | 137         | 161                        |

| 1 [2]       | 1 (11(02)  | ALT2                         | CS1_3     | DSPI_3            | 0                | Slow    | iviedium            |             | 137         | 101                        |

|             |            | ALT3                         | _         | _                 | _                |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[83]  | SIUL              | I/O              |         |                     |             |             |                            |

| F[3]        | PCR[83]    | ALT1                         | DBG_3     | FlexRay_0         | 0                | Slow    | Medium              |             | 139         | 167                        |

| ا [ت]       | i Cit[00]  | ALT2                         | CS0_3     | DSPI_3            | I/O              | Siow    | Mcdiairi            |             | 133         | 107                        |

|             |            | ALT3                         | _         | _                 | _                |         |                     |             |             |                            |

|             |            | ALT0                         | _         | _                 | _                |         |                     |             |             |                            |

| F[4]        | PCR[84]    | ALT1                         | _         | _                 | _                | Slow    | Fast                |             | 4           | 4                          |

| נידן י      | 1 OIN[O+]  | ALT2                         | MDO[3]    | nexus_0           | 0                | CIOW    | 1 431               |             | 7           | 7                          |

|             |            | ALT3                         | _         | _                 |                  |         |                     |             |             |                            |

|             |            | ALT0                         | _         | _                 | _                |         |                     |             |             |                            |

| F[5]        | PCR[85]    | ALT1                         | _         | _                 | _                | Slow    | Fast                |             | 5           | 13                         |

| ا اِی       | i Cit[00]  | ALT2                         | MDO[2]    | nexus_0           | 0                | CIOW    | 1 431               |             |             | 10                         |

|             |            | ALT3                         |           | _                 | _                |         |                     |             |             |                            |

|             |            | ALT0                         | GPIO[86]  | SIUL              | I/O              |         |                     |             |             |                            |

| F[6]        | PCR1861    | ALT1                         | _         | _                 | _                | Slow    | Slow Fast           | _           | 8           | 16                         |

| , [O]       | PCR[86]    | ALT2                         | MDO[1]    | nexus_0           | 0                | CIOW    |                     |             |             |                            |

|             |            | ALT3                         | _         | _                 | -                |         |                     |             |             |                            |

# 3 Electrical characteristics

### 3.1 Introduction

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

Caution:

All of the following parameter values can vary depending on the application and must be confirmed during silicon validation, silicon characterization or silicon reliability trial.

#### 3.2 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

Classification tag

Tag description

P

Those parameters are guaranteed during production testing on each individual device.

C

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.

T

Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category.

D

Those parameters are derived mainly from simulations.

Table 8. Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

577

| Symbol             |   | Parameter                                                                 | Conditions            | Typical value | Unit |

|--------------------|---|---------------------------------------------------------------------------|-----------------------|---------------|------|

| D                  | D | Thermal resistance junction-to-ambient, natural convection <sup>(1)</sup> | Single layer board—1s | 47.3          | °C/W |

| $R_{	hetaJA}$      | D | natural convection <sup>(1)</sup>                                         | Four layer board—2s2p | 35.6          | °C/W |

| $R_{	heta JB}$     | D | Thermal resistance junction-to-board <sup>(2)</sup>                       | Four layer board—2s2p | 19.1          | °C/W |

| $R_{\theta JCtop}$ | D | Thermal resistance junction-to-case (top) <sup>(3)</sup>                  | Single layer board—1s | 9.1           | °C/W |

| $\Psi_{JB}$        | D | Junction-to-board, natural convection <sup>(4)</sup>                      | Operating conditions  | 19.1          | °C/W |

| $\Psi_{\sf JC}$    | D | Junction-to-case, natural convection <sup>(5)</sup>                       | Operating conditions  | 1.1           | °C/W |

Table 13. Thermal characteristics for 100-pin LQFP

- Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

- Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

- Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

## 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

Equation 1

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_A$ = ambient temperature for the package ( ${}^{\circ}$ C)

$R_{\theta,JA}$ = junction to ambient thermal resistance ( ${}^{\circ}C/W$ )

P<sub>D</sub>= power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

Equation 2

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

56/105

R<sub>θ,JA</sub> = junction to ambient thermal resistance (°C/W)

R<sub>0.IC</sub>= junction to case thermal resistance (°C/W)

R<sub>θCA</sub>= case to ambient thermal resistance (°C/W)

DocID18340 Rev 6

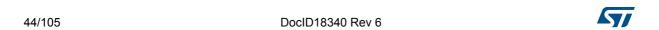

Figure 12. Brown-out typical sequence

# 3.10 NVUSRO register

Portions of the device configuration, such as high voltage supply, and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options register (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

# 3.10.1 NVUSRO[PAD3V5V] field description

Table 19 shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 19. PAD3V5V field description<sup>(1)</sup>

| Value <sup>(2)</sup> | Description                  |

|----------------------|------------------------------|

| 0                    | High voltage supply is 5.0 V |

| 1                    | High voltage supply is 3.3 V |

- 1. See the device reference manual for more information on the NVUSRO register.

- 2. '1' is delivery value. It is part of shadow Flash, thus programmable by customer.

The DC electrical characteristics are dependent on the PAD3V5V bit value.

Table 21. Supply current (5.0 V, NVUSRO[PAD3V5V]=0)

| Oh al                   |                                                                                    |         | Damana atau                                                                 | O a maliki a ma                                                                        |         | Va      | lue     | 11!4    |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|-------------------------|------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|-----------|--|--|---------|--|---|---------|--------------------------|----------------------------------------------------|---|-----|----|--|

| Symbol                  |                                                                                    |         | Parameter                                                                   | Conditions                                                                             |         | Тур     | Max     | Unit    |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         | RUN — Maximum Mode <sup>(1)</sup>                                           | V <sub>DD_LV_CORE</sub> externally forced at 1.3 V ADC Freq = 32 MHz PLL Freq = 64 MHz | 64 MHz  | 90      | 120     |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

| I <sub>DD_LV_CORE</sub> |                                                                                    |         | DUN DIVIS                                                                   |                                                                                        | 16 MHz  | 21      | 37      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         | Т                                                                                  |         | RUN - Platform consumption, single core <sup>(2)</sup>                      |                                                                                        | 40 MHz  | 35      | 55      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         | 3                                                                           | VDD_LV_CORE                                                                            | 64 MHz  | 48      | 72      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         | RUN - Platform consumption, dual core <sup>(3)</sup>                        | externally forced to 1.3V                                                              | 16 MHz  | 24      | 41      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         |                                                                             |                                                                                        | 40 MHz  | 42      | 64      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         |                                                                             |                                                                                        | 64 MHz  | 58      | 85      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    | Supply  | RUN — Maximum Mode <sup>(4)</sup>                                           | V <sub>DD_LV_CORE</sub> externally forced at 1.3 V                                     | 64 MHz  | 85      | 113     | mA      |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         | Р                                                                                  | current | current                                                                     | current                                                                                | current | current | current | current | current | current | current | current | current | current | ourrent | current | current - |  |  | current |  | - | current | HALT Mode <sup>(5)</sup> | V <sub>DD_LV_CORE</sub> externally forced at 1.3 V | _ | 5.5 | 15 |  |

|                         |                                                                                    |         | STOP Mode <sup>(6)</sup>                                                    | V <sub>DD_LV_CORE</sub> externally forced at 1.3 V                                     | _       | 4.5     | 13      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

|                         |                                                                                    |         | Flash memory supply current during read                                     | V <sub>DD_HV_FL</sub> at 5.0 V                                                         | _       | l       | 14      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

| I <sub>DD_FLASH</sub>   | Т                                                                                  |         | Flash memory supply current during erase operation on 1 flash memory module | V <sub>DD_HV_FL</sub> at 5.0 V                                                         | _       | _       | 42      |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

| I <sub>DD_ADC</sub>     | ADC supply current — V <sub>DD_HV_AD</sub> at 5.0 V Maximum Mode ADC Freq = 16 MHz |         | _                                                                           | 3                                                                                      | 4       |         |         |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

| I <sub>DD_OSC</sub>     | Т                                                                                  |         | OSC supply current                                                          | V <sub>DD_OSC</sub> at 5.0 V                                                           | 8 MHz   | 2.6     | 3.2     |         |         |         |         |         |         |         |         |         |           |  |  |         |  |   |         |                          |                                                    |   |     |    |  |

- Maximum mode configuration: Code fetched from Flash executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- RAM, Code and Data Flash powered, code fetched from Flash executed by single core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz).

Code is performing continuous data transfer from Flash to RAM.

- RAM, Code and Data Flash powered, code fetched from Flash executed by dual core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz).

Code is performing continuous data transfer from Flash to RAM.

- Maximum mode configuration: Code fetched from RAM executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- 5. HALT mode configuration, only for the "P" classification: Code Flash memory in low power mode, data Flash memory in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

- 6. STOP mode configuration, only for the "P" classification: Code and data Flash memories in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

In particular two different transient periods can be distinguished:

A first and quick charge transfer from the internal capacitance C<sub>P1</sub> and C<sub>P2</sub> to the sampling capacitance C<sub>S</sub> occurs (C<sub>S</sub> is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which C<sub>P2</sub> is reported in parallel to C<sub>P1</sub> (call C<sub>P</sub> = C<sub>P1</sub> + C<sub>P2</sub>), the two capacitances C<sub>P</sub> and C<sub>S</sub> are in series, and the time constant is

#### **Equation 5**

$$\tau_1 = (R_{SW} + R_{AD}) \times \frac{C_P \times C_S}{C_P + C_S}$$

Equation 5 can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

## **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \times C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

#### **Equation 7**

$$V_{A1} \times (C_S + C_{P1} + C_{P2}) = V_A \times (C_{P1} + C_{P2})$$

A second charge transfer involves also C<sub>F</sub> (that is typically bigger than the on-chip capacitance) through the resistance R<sub>L</sub>: again considering the worst case in which C<sub>P2</sub> and C<sub>S</sub> were in parallel to C<sub>P1</sub> (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2\!<\!R_L\!\times\!(C_S\!+\!C_{P1}\!+\!C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraint on  $R_L$  sizing is obtained:

#### **Equation 9**

$$8.5 \times \tau_2 = 8.5 \times R_L \times (C_S + C_{P1} + C_{P2}) < \ T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

#### **Equation 10**

$$V_{A2} \times (C_S + C_{P1} + C_{P2} + C_F) = V_A \times C_F + V_{A1} \times (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the R<sub>F</sub>C<sub>F</sub> filter, is not able to provide the extra charge to compensate the voltage drop on

# 3.18.2 IEEE 1149.1 interface timing

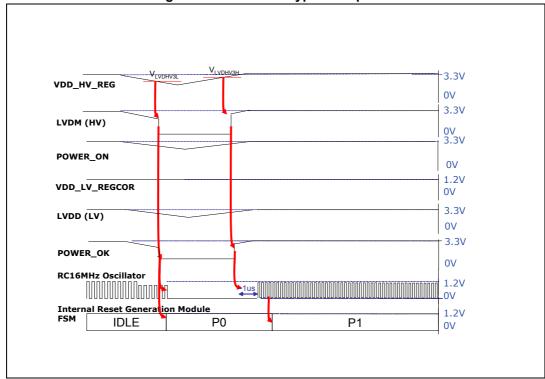

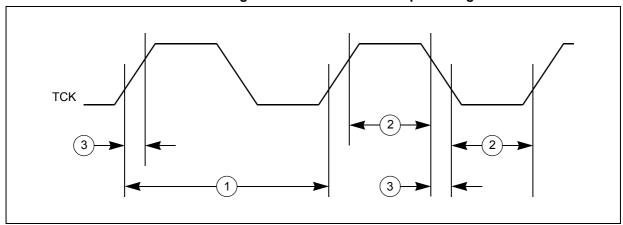

Table 38. JTAG pin AC electrical characteristics

| No. | Symbol                |    | С | Parameter                                                     | Conditions | Min | Max | Unit |

|-----|-----------------------|----|---|---------------------------------------------------------------|------------|-----|-----|------|

| 1   | t <sub>JCYC</sub>     | CC | D | TCK cycle time                                                | _          | 100 | _   | ns   |

| 2   | t <sub>JDC</sub>      | CC | D | TCK clock pulse width (measured at V <sub>DD_HV_IOx</sub> /2) | _          | 40  | 60  | ns   |

| 3   | t <sub>TCKRISE</sub>  | CC | D | TCK rise and fall times (40% – 70%)                           | _          | _   | 3   | ns   |

| 4   | $t_{TMSS}, t_{TDIS}$  | СС | D | TMS, TDI data setup time                                      | _          | 5   | _   | ns   |

| 5   | $t_{TMSH,} t_{TDIH}$  | CC | D | TMS, TDI data hold time                                       | _          | 25  | _   | ns   |

| 6   | t <sub>TDOV</sub>     | CC | D | TCK low to TDO data valid                                     | _          | _   | 40  | ns   |

| 7   | t <sub>TDOI</sub>     | СС | D | TCK low to TDO data invalid                                   | _          | 0   | _   | ns   |

| 8   | t <sub>TDOHZ</sub>    | СС | D | TCK low to TDO high impedance                                 | _          | 40  | _   | ns   |

| 9   | t <sub>BSDV</sub>     | СС | D | TCK falling edge to output valid                              | _          | _   | 50  | ns   |

| 10  | t <sub>BSDVZ</sub>    | СС | D | TCK falling edge to output valid out of high impedance        | _          | _   | 50  | ns   |

| 11  | t <sub>BSDHZ</sub>    | СС | D | TCK falling edge to output high impedance                     | _          | _   | 50  | ns   |

| 12  | t <sub>BSDST</sub>    | СС | D | Boundary scan input valid to TCK rising edge                  | _          | 50  | _   | ns   |

| 13  | t <sub>BSDHT</sub> CC |    | D | TCK rising edge to boundary scan input invalid                | _          | 50  |     | ns   |

Figure 22. JTAG test clock input timing

Figure 24. JTAG boundary scan timing

# 3.18.3 Nexus timing

Table 39. Nexus debug port timing<sup>(1)</sup>

| Table 33. Nexus debug port tilling |                    |    |   |                              |                              |     |                          |      |  |  |  |

|------------------------------------|--------------------|----|---|------------------------------|------------------------------|-----|--------------------------|------|--|--|--|

| No.                                | Symbol             |    | C | Parameter                    | Value                        |     |                          | Unit |  |  |  |

|                                    |                    |    |   |                              | Min                          | Тур | Max                      | Unit |  |  |  |

| 1                                  | t <sub>MCYC</sub>  | CC | D | MCKO cycle time              | 32                           | _   | _                        | ns   |  |  |  |

| 2                                  | t <sub>MDOV</sub>  | СС | D | MCKO edge to MDO data valid  | -<br>0.1 × t <sub>MCYC</sub> | _   | 0.25 × t <sub>MCYC</sub> | ns   |  |  |  |

| 3                                  | t <sub>MSEOV</sub> | СС | D | MCKO edge to MSEO data valid | -<br>0.1 × t <sub>MCYC</sub> | _   | 0.25 × t <sub>MCYC</sub> | ns   |  |  |  |

| 4                                  | t <sub>EVTOV</sub> | СС | D | MCKO edge to EVTO data valid | -<br>0.1 × t <sub>MCYC</sub> | _   | 0.25 × t <sub>MCYC</sub> | ns   |  |  |  |

| 5                                  | t <sub>TCYC</sub>  | СС | D | TCK cycle time               | 64 <sup>(2)</sup>            | _   | _                        | ns   |  |  |  |

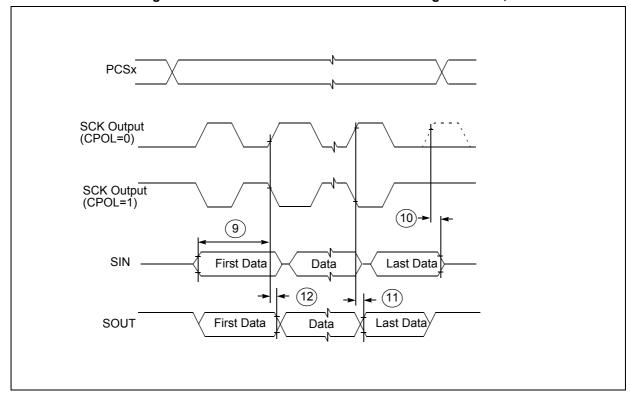

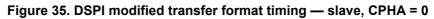

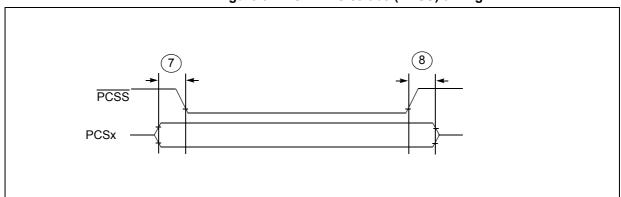

Figure 34. DSPI modified transfer format timing — master, CPHA = 1

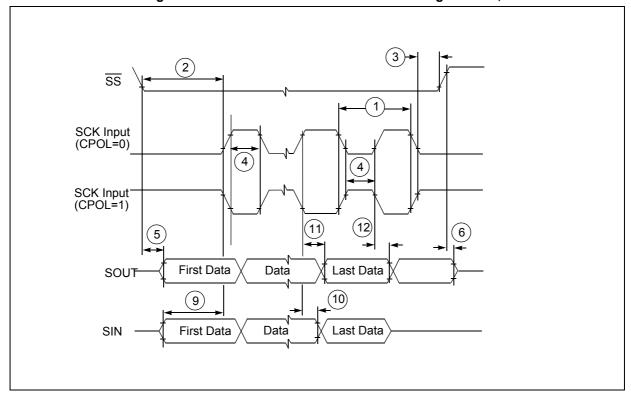

Figure 36. DSPI modified transfer format timing — slave, CPHA = 1

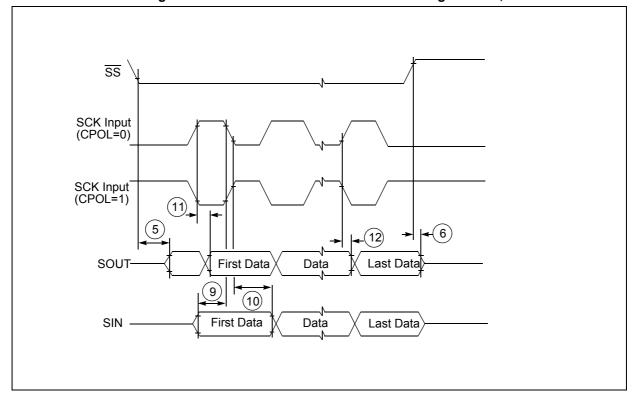

Figure 37. DSPI PCS strobe (PCSS) timing

# 4.2.2 LQFP100 mechanical outline drawing

0.25 mm 0.10 inch GAGE PLANE L1 E3 E1 Pin 1 С identification SEATING PLANE С 1L\_ME

Figure 39. LQFP100 package mechanical drawing

Table 43. LQFP100 mechanical data

| Symbol |       | mm    |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min   | Тур   | Max   | Min                   | Тур    | Max    |  |

| Α      | _     | _     | 1.600 | _                     | _      | 0.0630 |  |

| A1     | 0.050 | _     | 0.150 | 0.0020                | _      | 0.0059 |  |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved