#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 80K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p60l5ceaar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Package | Part number                |                            |  |  |  |  |  |

|---------|----------------------------|----------------------------|--|--|--|--|--|

|         | 768 KB Flash               | 1 MB Flash                 |  |  |  |  |  |

| LQFP144 | SPC560P54L5<br>SPC56AP54L5 | SPC560P60L5<br>SPC56AP60L5 |  |  |  |  |  |

| LQFP100 | SPC560P54L3<br>SPC56AP54L3 | SPC560P60L3<br>SPC56AP60L3 |  |  |  |  |  |

### Table 1. Device summary

SPC56xP54x/SPC56xP60x is present on the market in two different options enabling different features: Full-featured, and Airbag configuration. *Table 3* shows the main differences between the two versions.

### Table 3. SPC56xP54x/SPC56xP60x device configuration difference

| Feature                                             | Enhanced<br>Full-featured | Full-featured           | Airbag |

|-----------------------------------------------------|---------------------------|-------------------------|--------|

| FlexCAN (controller area network)                   | 3                         | 2                       | 2      |

| CTU (cross triggering unit)                         | Ye                        | Yes                     |        |

| FlexRay                                             | Yes (64 mes               | Yes (64 message buffer) |        |

| DSPI (deserial serial peripheral interface) modules | 5                         |                         | 4      |

| CRC (cyclic redundancy check) unit                  | 2                         |                         | 1      |

## 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC56xP54x/SPC56xP60x MCU. *Table 4* summarizes the functions of the blocks.

The flash memory module provides the following features:

- Up to 1024 KB flash memory

- 14 blocks (2×16 KB + 2×32 KB + 2×16 KB + 2×64 KB + 6×128 KB) code flash

- 4 blocks (16 KB + 16 KB + 16 KB + 16 KB) data flash

- Full Read While Write (RWW) capability between code and data flash

- Four 128-bit wide prefetch buffers to provide single cycle in-line accesses (prefetch buffers can be configured to prefetch code or data or both)

- Typical flash memory access time: 0 wait states for buffer hits, 2 wait states for page buffer miss at 64 MHz

- Hardware managed flash memory writes handled by 32-bit RISC Krypton engine

- Hardware and software configurable read and write access protections on a per-master basis.

- Configurable access timing allowing use in a wide range of system frequencies.

- Multiple-mapping support and mapping-based block access timing (0–31 additional cycles) allowing use for emulation of other memory types.

- Software programmable block program/erase restriction control.

- Erase of selected block(s)

- Read page size of 128 bits (4 words)

- 64-bit ECC with single-bit correction, double-bit detection for data integrity

- Embedded hardware program and erase algorithm

- Erase suspend, program suspend and erase-suspended program

- Censorship protection scheme to prevent flash memory content visibility

- Hardware support for EEPROM emulation

### 1.5.5 On-chip SRAM with ECC

The SPC56xP54x/SPC56xP60x SRAM module provides a general-purpose memory of up to 80 KB.

The SRAM module provides the following features:

- Supports read/write accesses mapped to the SRAM memory from any master

- Up to 80 KB general purpose RAM

- 2 blocks (48 KB + 32 KB)

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

- Typical SRAM access time: 0 wait state for reads and 32-bit writes; 1 wait state for 8and 16-bit writes if back to back with a read to same memory block

### 1.5.6 Interrupt controller (INTC)

The INTC (interrupt controller) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency)

Programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

### 1.5.9 Main oscillator

The main oscillator provides these features:

- Input frequency range 4 MHz to 40 MHz

- Crystal input mode or Oscillator input mode

- PLL reference

### 1.5.10 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC Oscillator provides these features:

- Nominal frequency 16 MHz

- ±6% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

### **1.5.11 Periodic interrupt timer (PIT)**

The PIT module implements these features:

- Up to four general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

### 1.5.12 System timer module (STM)

The STM module implements these features:

- 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

The STM module is replicated for each processor.

The default booting scheme is the one which uses the internal flash memory (an internal pull-down is used to select this mode). The alternate option allows the user to boot via FlexCAN or LINFlex (using the boot assist module software).

A censorship scheme is provided to protect the contents of the flash memory and offer increased security for the entire device.

A password mechanism is designed to grant the legitimate user access to the non-volatile memory.

#### 1.5.16.1 Boot assist module (BAM)

The BAM is a block of read-only one-time programmed memory and is identical for all SPC56xP54x/SPC56xP60x devices that are based on the e200z0h core. The BAM program is executed every time the device is powered on if the alternate boot mode has been selected by the user.

The BAM provides the following features:

- Serial bootloading via FlexCAN or LINFlex.

- BAM can accept a password via the used serial communication channel to grant the legitimate user access to the non-volatile memory.

### 1.5.17 Error correction status module (ECSM)

The ECSM on this device features the following:

- Platform configuration and revision

- ECC error reporting for flash memory and SRAM

- ECC error injection for SRAM

The ECSM module is replicated for each processor.

### 1.5.18 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. FlexCAN module contains 32 message buffers.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, Version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1 Mbit/s

- 32 message buffers of 0 to 8 bytes data length

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

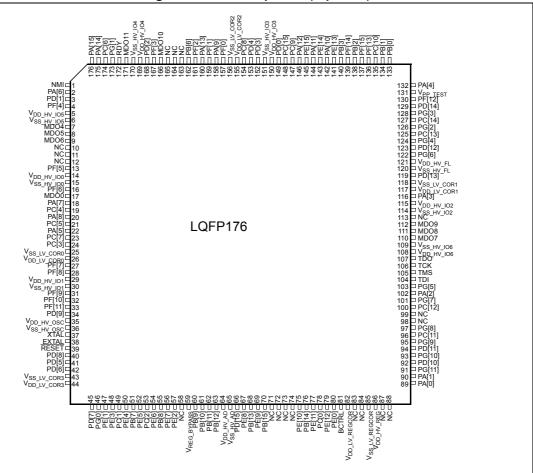

# 2 Package pinouts and signal descriptions

## 2.1 Package pinouts

The LQFP pinouts are shown in the following figures.

b. Software development package only. Not available for production.

|             |            | Alternate                              |                                                        | • 7. Pin mux                                             | 1/0                            | ,       | peed <sup>(6)</sup> |             |             |                            |

|-------------|------------|----------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--------------------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3)        | Functions                                              | Peripheral<br>(4)                                        | direction<br>(5)               | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

| A[2]        | DODINI     | ALT0<br>ALT1<br>ALT2                   | GPIO[2]<br>ETC[2]<br>CS3_4                             | SIUL<br>eTimer_0<br>DSPI_4                               | I/O<br>I/O<br>O                |         |                     | 57          | 0.4         | 100                        |

| (8)         | PCR[2]     | ALT3<br>—<br>—<br>—                    | <br>SIN_2<br>ABS[0]<br>EIRQ[2]                         | <br>DSPI_2<br>MC_RGM<br>SIUL                             |                                | Slow    | Medium              | 57          | 84          | 102                        |

| A[3]<br>(8) | PCR[3]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[3]<br>ETC[3]<br>CS0_2<br>—<br>ABS[1]<br>EIRQ[3]   | SIUL<br>eTimer_0<br>DSPI_2<br>—<br>MC_RGM<br>SIUL        | I/O<br>I/O<br>I/O<br>I<br>I    | Slow    | Medium              | 64          | 92          | 116                        |

| A[4]<br>(8) | PCR[4]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[4]<br>ETC[0]<br>CS1_2<br>ETC[4]<br>FAB<br>EIRQ[4] | SIUL<br>eTimer_1<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL | I/O<br>I/O<br>I/O<br>I<br>I    | Slow    | Medium              | 75          | 108         | 132                        |

| A[5]        | PCR[5]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[5]<br>CS0_1<br>ETC[5]<br>CS7_0<br>EIRQ[5]         | SIUL<br>DSPI_1<br>eTimer_1<br>DSPI_0<br>SIUL             | I/O<br>I/O<br>I/O<br>I         | Slow    | Medium              | 8           | 14          | 22                         |

| A[6]        | PCR[6]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[6]<br>SCK_1<br>CS2_4<br><br>EIRQ[6]               | SIUL<br>DSPI_1<br>DSPI_4<br><br>SIUL                     | I/O<br>I/O<br>I/O<br>I         | Slow    | Medium              | 2           | 2           | 2                          |

| A[7]        | PCR[7]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[7]<br>SOUT_1<br>CS1_4<br>—<br>EIRQ[7]             | SIUL<br>DSPI_1<br>DSPI_4<br>—<br>SIUL                    | I/O<br>O<br>I/O<br>I           | Slow    | Medium              | 4           | 10          | 18                         |

| A[8]        | PCR[8]     | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[8]<br>—<br>CS0_4<br>—<br>SIN_1<br>EIRQ[8]         | SIUL<br>—<br>DSPI_4<br>—<br>DSPI_1<br>SIUL               | I/O<br>—<br>I/O<br>—<br>I<br>I | Slow    | Medium              | 6           | 12          | 20                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Port  | PCR      | Alternate                         |                                 | Peripheral                  | I/O                     | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |

|-------|----------|-----------------------------------|---------------------------------|-----------------------------|-------------------------|---------|---------------------|-------------|-------------|----------------------------|

| pin   |          | function <sup>(2),</sup><br>(3)   | Functions                       | (4)                         | direction<br>(5)        | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

| G[8]  | PCR[104] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[104]<br><br>CS3_4<br>      | SIUL<br>—<br>DSPI_4<br>—    | I/O<br>—<br>0<br>—      | Slow    | Medium              | _           | 81          | 97                         |

| G[9]  | PCR[105] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[105]<br>—<br>—<br>—<br>RXD | SIUL<br>—<br>—<br>FlexCAN_1 | I/O<br>—<br>—<br>—<br>— | Slow    | Medium              | _           | 79          | 95                         |

| G[10] | PCR[106] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[106]<br>—<br>TXD<br>—      | SIUL<br>—<br>FlexCAN_1<br>— | V<br>0                  | Slow    | Medium              | _           | 77          | 93                         |

| G[11] | PCR[107] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[107]<br>—<br>—<br>—        | SIUL<br>—<br>—<br>—         | I/O<br>—<br>—           | Slow    | Medium              | _           | 75          | 91                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

1. This table concerns Enhanced Full-featured version. Please refer to "SPC56xP54x/SPC56xP60x device configuration difference" table for difference between Enhanced Full-featured, Full-featured, and Airbag configuration.

2. ALT0 is the primary (default) function for each port after reset.

3. Alternate functions are chosen by setting the values of the PCR[PA] bitfields inside the SIU module. PCR[PA] = 00 → ALT0; PCR[PA] = 01 → ALT1; PCR[PA] = 10 → ALT2; PCR[PA] = 11 → ALT3. This is intended to select the output functions; to use one of the input-only functions, the PCR[IBE] bit must be written to '1', regardless of the values selected in the PCR[PA] bitfields. For this reason, the value corresponding to an input only function is reported as "—".

4. Module included on the MCU.

5. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMI[PADSELx] bitfields inside the SIUL module.

6. Programmable via the SRC (Slew Rate Control) bits in the respective Pad Configuration Register.

7. LQFP176 available only as development package.

8. Weak pull down during reset.

## 3 Electrical characteristics

### 3.1 Introduction

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

**Caution:** All of the following parameter values can vary depending on the application and must be confirmed during silicon validation, silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

| Table 8. | Parameter | classifications |

|----------|-----------|-----------------|

|----------|-----------|-----------------|

*Note:* The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.3 Absolute maximum ratings

| Table 9. Absolute maximum ratings <sup>(1)</sup> |     |                                                                                                                 |                                       |                                |                                       |      |  |  |  |

|--------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------|---------------------------------------|------|--|--|--|

| Symbol                                           |     | Parameter                                                                                                       | Conditions                            | Min                            | Max <sup>(2)</sup>                    | Unit |  |  |  |

| V <sub>SS_HV</sub>                               | SR  | Digital ground                                                                                                  | —                                     | 0                              | 0                                     | V    |  |  |  |

| V <sub>DD_HV_IOx</sub> <sup>(3)</sup>            | SR  | 3.3 V / 5.0 V input/output supply voltage with respect to ground (V <sub>SS_HV</sub> )                          | _                                     | -0.3                           | 6.0                                   | V    |  |  |  |

| $V_{SS_HV_IOx}$                                  | SR  | Input/output ground voltage with respect to ground (V <sub>SS_HV</sub> )                                        | _                                     | -0.1                           | 0.1                                   | V    |  |  |  |

|                                                  |     | 3.3 V / 5.0 V code and data flash                                                                               | —                                     | -0.3                           | 6.0                                   |      |  |  |  |

| V <sub>DD_HV_FL</sub>                            | SR  | memory supply voltage with respect to ground ( $V_{SS_HV}$ )                                                    | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3                           | V <sub>DD_HV_IOx</sub> +<br>0.3       | V    |  |  |  |

| V <sub>SS_HV_FL</sub>                            | SR  | Code and data flash memory ground with respect to ground $(V_{\mbox{SS}_{\mbox{HV}}})$                          | _                                     | -0.1                           | 0.1                                   | V    |  |  |  |

|                                                  |     | 3.3 V / 5.0 V crystal oscillator                                                                                | —                                     | -0.3                           | 6.0                                   |      |  |  |  |

| V <sub>DD_HV_OSC</sub>                           | SR  | amplifier supply voltage with respect to ground ( $V_{SS_HV}$ )                                                 | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3                           | V <sub>DD_HV_IOx</sub> +<br>0.3       | V    |  |  |  |

| V <sub>SS_HV_OSC</sub>                           | SR  | 3.3 V / 5.0 V crystal oscillator<br>amplifier reference voltage with<br>respect to ground (V <sub>SS_HV</sub> ) | _                                     | -0.1                           | 0.1                                   | V    |  |  |  |

|                                                  |     | 3.3 V / 5.0 V voltage regulator supply                                                                          | —                                     | - 0.3                          | 6.0                                   |      |  |  |  |

| V <sub>DD_HV_REG</sub>                           | SR  | voltage with respect to ground $(V_{SS_HV})$                                                                    | Relative to<br>V <sub>DD_HV_IOx</sub> | - 0.3                          | V <sub>DD_HV_IOx</sub> +<br>0.3       | V    |  |  |  |

|                                                  | SR  | 3.3 V / 5.0 V ADC supply and high reference voltage with respect to                                             | V <sub>DD_HV_REG</sub><br>< 2.7 V     | - 0.3                          | V <sub>DD_HV_REG</sub><br>+ 0.3       | v    |  |  |  |

| V <sub>DD_HV_AD</sub>                            | SIX | ground (V <sub>SS_HV</sub> )                                                                                    | V <sub>DD_HV_REG</sub><br>> 2.7 V     | - 0.3                          | 6.0                                   | v    |  |  |  |

| V <sub>SS_HV_AD</sub>                            | SR  | ADC ground and low reference voltage with respect to ground (V <sub>SS_HV</sub> )                               | _                                     | -0.1                           | 0.1                                   | V    |  |  |  |

| TV <sub>DD</sub>                                 | SR  | Slope characteristics on all $V_{DD}$ during power up <sup>(4)</sup> with respect to ground ( $V_{SS_HV}$ )     | _                                     | 3.0 <sup>(5)</sup>             | 500 x 10 <sup>3</sup><br>(0.5 [V/µs]) | V/s  |  |  |  |

|                                                  |     | Voltage on any pin with respect to                                                                              | —                                     | -0.3                           | 6.0                                   |      |  |  |  |

| V <sub>IN</sub>                                  | SR  | ground (V_{SS_HV_IOx}) with respect to ground (V_{SS_HV})                                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3                           | V <sub>DD_HV_IOx</sub> +<br>0.3       | V    |  |  |  |

| V                                                | SR  | Analog input voltage                                                                                            | V <sub>DD_HV_REG</sub><br>< 2.7 V     | V <sub>SS_HV_AD</sub> -<br>0.3 | V <sub>DD_HV_AD</sub> + 0.3           | V    |  |  |  |

| V <sub>INAN</sub>                                |     |                                                                                                                 | V <sub>DD_HV_REG</sub><br>> 2.7 V     | V <sub>SS_HV_AD</sub>          | V <sub>DD_HV_AD</sub>                 | V    |  |  |  |

| I <sub>INJPAD</sub>                              | SR  | Injected input current on any pin during overload condition                                                     | _                                     | -10                            | 10                                    | mA   |  |  |  |

### Table 9. Absolute maximum ratings<sup>(1)</sup>

| Symbol                                       |    | Parameter Conditions                           |                                       | Min                          | Max <sup>(1)</sup>           | Unit |  |

|----------------------------------------------|----|------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|--|

|                                              |    |                                                | —                                     | 4.5                          | 5.5                          |      |  |

| $V_{DD_HV_REG}$                              | SR | 5.0 V voltage regulator<br>supply voltage      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |  |

|                                              |    |                                                | —                                     | 4.5                          | 5.5                          |      |  |

| $V_{DD_HV_AD}$                               | SR | 5.0 V ADC supply and high<br>reference voltage | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> -0.1  | _                            | V    |  |

| V <sub>SS_HV_AD</sub>                        | SR | ADC ground and low reference voltage           | _                                     | 0                            | 0                            | V    |  |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR | Internal supply voltage                        | —                                     | _                            | —                            | V    |  |

| $V_{SS_{LV}_{REGCOR}}^{(3)}$                 | SR | Internal reference voltage                     | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR | Internal supply voltage                        | —                                     | —                            | —                            | V    |  |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR | Internal reference voltage                     | —                                     | 0                            | 0                            | V    |  |

| T <sub>A</sub>                               | SR | Ambient temperature under bias                 | _                                     | -40                          | 125                          | °C   |  |

| Table 10. Recommended | operating conditions | (5.0 V) | (continued) |

|-----------------------|----------------------|---------|-------------|

|                       | operating container  | (0.0.0) | (001101000) |

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

| Symbol                                |    | Parameter                                               | Conditions                            | Min                         | Max <sup>(1)</sup>           | Unit |

|---------------------------------------|----|---------------------------------------------------------|---------------------------------------|-----------------------------|------------------------------|------|

| V <sub>SS_HV</sub>                    | SR | Digital ground                                          | —                                     | 0                           | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 3.3 V input/output supply voltage                       | _                                     | 3.0                         | 3.6                          | V    |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                             | —                                     | 0                           | 0                            | V    |

|                                       |    | 2.2.V code and date flach                               | —                                     | 3.0                         | 3.6                          |      |

| V <sub>DD_HV_FL</sub>                 |    | 3.3 V code and data flash<br>memory supply voltage      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_FL</sub>                 | SR | Code and data flash<br>memory ground                    | _                                     | 0                           | 0                            | V    |

|                                       |    | 2.2.V. crustal oscillator                               | —                                     | 3.0                         | 3.6                          |      |

| V <sub>DD_HV_OSC</sub>                | SR | 3.3 V crystal oscillator<br>amplifier supply voltage    | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_OSC</sub>                | SR | 3.3 V crystal oscillator<br>amplifier reference voltage | _                                     | 0                           | 0                            | V    |

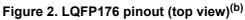

### Table 11. Recommended operating conditions (3.3 V)

Figure 7. Power supplies constraints<sup>(f)</sup>

The SPC56xP54x/SPC56xP60x supply architecture provides an ADC supply that is managed independently of standard  $V_{DD_HV}$  supply. *Figure 8* shows the constraints of the ADC power supply.

f. IO AC and DC characteristics are guaranteed only in the range 3.0 V–3.6 V when PAD3V5V is low, and in the range 4.5 V–5.5 V when PAD3V5V is high.

| Table 13. Mermai characteristics for Too-pin Eq. F |   |                                                                           |                       |               |      |  |  |  |

|----------------------------------------------------|---|---------------------------------------------------------------------------|-----------------------|---------------|------|--|--|--|

| Symbol                                             |   | Parameter                                                                 | Conditions            | Typical value | Unit |  |  |  |

| P                                                  | D | Thermal resistance junction-to-ambient, natural convection <sup>(1)</sup> | Single layer board—1s | 47.3          | °C/W |  |  |  |

| $R_{	heta JA}$ -                                   | D | natural convection <sup>(1)</sup>                                         | Four layer board—2s2p | 35.6          | °C/W |  |  |  |

| $R_{	hetaJB}$                                      | D | Thermal resistance junction-to-board <sup>(2)</sup>                       | Four layer board—2s2p | 19.1          | °C/W |  |  |  |

| R <sub>0JCtop</sub>                                | D | Thermal resistance junction-to-case (top) <sup>(3)</sup>                  | Single layer board—1s | 9.1           | °C/W |  |  |  |

| $\Psi_{JB}$                                        | D | Junction-to-board, natural convection <sup>(4)</sup>                      | Operating conditions  | 19.1          | °C/W |  |  |  |

| $\Psi_{JC}$                                        | D | Junction-to-case, natural convection <sup>(5)</sup>                       | Operating conditions  | 1.1           | °C/W |  |  |  |

Table 13. Thermal characteristics for 100-pin LQFP

1. Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

2. Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

4. Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

5. Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

### 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

Equation 1  $T_J = T_A + (R_{\theta JA} \times P_D)$

where:

$T_A$  = ambient temperature for the package (<sup>o</sup>C)

$R_{\theta JA}$ = junction to ambient thermal resistance (<sup>o</sup>C/W)

$P_D$ = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

### Equation 2 $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta,IC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

| Symbol                  |   |         | Davamatar                                                                         | Conditions                                                                                         |          | Value |     | Unit |

|-------------------------|---|---------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------|-------|-----|------|

| Бутроі                  |   |         | Parameter                                                                         | Conditions                                                                                         |          | Тур   | Мах | Unit |

|                         |   |         | RUN — Maximum Mode <sup>(1)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V<br>ADC Freq = 32 MHz<br>PLL Freq = 64 MHz | 64 MHz   | 90    | 120 |      |

|                         | т |         |                                                                                   |                                                                                                    | 16 MHz   | 21    | 37  |      |

|                         | 1 |         | RUN - Platform consumption, single core <sup>(2)</sup>                            |                                                                                                    | 40 MHz   | 35    | 55  |      |

|                         |   |         | 5                                                                                 | VDD_LV_CORE                                                                                        | 64 MHz   | 48    | 72  | -    |

|                         |   |         | RUN - Platform consumption, dual core <sup>(3)</sup>                              | externally forced to 1.3V                                                                          | 16 MHz   | 24    | 41  |      |

| I <sub>DD_LV_CORE</sub> |   |         |                                                                                   |                                                                                                    | 40 MHz   | 42    | 64  |      |

|                         |   |         |                                                                                   |                                                                                                    | 64 MHz 5 | 58    | 85  |      |

|                         | Ρ | Supply  | RUN — Maximum Mode <sup>(4)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V                                           | 64 MHz   | 85    | 113 | mA   |

|                         |   | current | HALT Mode <sup>(5)</sup>                                                          | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V                                           | _        | 5.5   | 15  |      |

|                         |   |         | STOP Mode <sup>(6)</sup>                                                          | V <sub>DD_LV_CORE</sub><br>externally forced at<br>1.3 V                                           | _        | 4.5   | 13  |      |

|                         |   |         | Flash memory supply current during read                                           | V <sub>DD_HV_FL</sub> at 3.3 V                                                                     | _        | _     | 14  |      |

| I <sub>DD_FLASH</sub>   | D |         | Flash memory supply current<br>during erase operation on 1<br>flash memory module | $V_{DD_{HV_{FL}}}$ at 3.3 V                                                                        | _        | _     | 42  |      |

| I <sub>DD_ADC</sub>     | Т |         | ADC supply current —<br>Maximum Mode                                              | V <sub>DD_HV_AD</sub> at 3.3 V<br>ADC Freq = 16 MHz                                                | _        | 3     | 4   |      |

| I <sub>DD_OSC</sub>     | Т |         | OSC supply current                                                                | V <sub>DD_OSC</sub> at 3.3 V                                                                       | 8 MHz    | 2.4   | 3   |      |

Maximum mode configuration: Code fetched from Flash executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- RAM, Code and Data Flash powered, code fetched from Flash executed by single core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- RAM, Code and Data Flash powered, code fetched from Flash executed by dual core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- Maximum mode configuration: Code fetched from RAM executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

- 5. HALT mode configuration, only for the "P" classification: Code Flash memory in low power mode, data Flash memory in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

- STOP mode configuration, only for the "P" classification: Code and data Flash memories in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

| Ш        |

|----------|

| ē        |

| <u>₽</u> |

| <u>-</u> |

| <u>હ</u> |

| ົ        |

| ž        |

| ar       |

| ခ        |

| Ť        |

| ž.       |

| ş        |

| ត        |

| "        |

DocID18340 Rev 6

70/105

| O maked                     |                         | Demonstern                                       |                                                                                                                        |                                                                                                                                                                      | Value                             |                                   |        |

|-----------------------------|-------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--------|

| Symbol                      |                         | Parameter                                        |                                                                                                                        | Conditions                                                                                                                                                           | Тур                               | Max                               | - Unit |

| I <sub>DD_HV</sub> (CAN)    | т                       | CAN (FlexCAN)<br>supply current on<br>VDD_HV_REG | 500 Kbyte/s                                                                                                            | Total (static + dynamic)<br>consumption:<br>– FlexCAN in loop-back mode<br>– XTAL@ 8 MHz used as CAN<br>engine clock source<br>– Message sending period is 580<br>μs | 21.6 * f <sub>periph</sub>        | 28.1* f <sub>periph</sub>         |        |

| I <sub>DD_HV</sub> (SCI)    | т                       | SCI (LINFlex) supply<br>current on<br>VDD_HV_REG | Total (static + dynamic) consumption:<br>– LIN mode<br>– Baudrate: 115.2 Kbyte/s                                       |                                                                                                                                                                      | 10.8 * f <sub>periph</sub>        | 14.1 * f <sub>periph</sub>        | μA     |

| I <sub>DD_HV(SPI)</sub>     | т                       | SPI (DSPI) supply<br>current on<br>VDD_HV_REG    | Ballast dynamic consumptio<br>communication):<br>– Baudrate: 2 Mbit/s<br>– Transmission every 8 µs<br>– Frame: 16 bits | on (continuous                                                                                                                                                       | 4.8 * f <sub>periph</sub>         | 6.3 * f <sub>periph</sub>         |        |

| I <sub>DD_HV(ADC)</sub>     | т                       | ADC supply current<br>on VDD_HV_REG              | VDD = 5.5 V                                                                                                            | Ballast dynamic consumption (continuous conversion)                                                                                                                  | 120 * f <sub>periph</sub>         | 156 * f <sub>periph</sub>         |        |

| DD_HV_ADC(ADC)              | т                       | ADC supply current<br>on VDD_HV_ADC              | VDD = 5.5 V                                                                                                            | Analog dynamic consumption (continuous conversion)                                                                                                                   | 0.005 * f <sub>periph</sub> + 2.8 | 0.007 * f <sub>periph</sub> + 3.4 | mA     |

| I <sub>DD_HV</sub> (eTimer) | т                       | eTimer supply current<br>on VDD_HV_REG           | PWM signals generation<br>on all 1 channel @10kHz                                                                      | Dynamic consumption does not change varying the frequency                                                                                                            | 1.8                               | 2.4                               | mA     |

| I <sub>DD_HV(FlexRay)</sub> | T Current on VDD_HV_REG |                                                  | Static consumption                                                                                                     |                                                                                                                                                                      | 4.2 * f <sub>periph</sub>         | 5.5 * f <sub>periph</sub>         | μA     |

1. Operating conditions:  $f_{periph} = 8 \text{ MHz}$  to 64 MHz

### **Electrical characteristics**

- 2. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

- Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- 4. f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- 5. This value is determined by the crystal manufacturer and board design.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

- 7. Proper PC board layout procedures must be followed to achieve specifications.

- 8. Values are obtained with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of  $C_{\text{JITTER}}$  and either  $f_{\text{CS}}$  or  $f_{\text{DS}}$  (depending on whether center spread or down spread modulation is enabled).

- 9. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

- 10. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 11. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 12. This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

- 13. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

## 3.14 **16 MHz RC oscillator electrical characteristics**

| Symbol                      |   | Parameter                                                                                                                                         | Conditions             | Min | Тур | Max | Unit |

|-----------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| f <sub>RC</sub>             | Ρ | RC oscillator frequency                                                                                                                           | T <sub>A</sub> = 25 °C | —   | 16  |     | MHz  |

| $\Delta_{RCMVAR}$           | Ρ | Fast internal RC oscillator variation<br>over temperature and<br>supply with respect to $f_{RC}$ at TA = 25 °C<br>in high-frequency configuration | —                      | -6  | _   | 6   | %    |

| $\Delta_{\mathrm{RCMTRIM}}$ | Т | Post Trim Accuracy: The variation of the PTF <sup>(1)</sup> from the 16 MHz                                                                       | T <sub>A</sub> = 25 °C | -1  | _   | 1   | %    |

| $\Delta_{RCMSTEP}$          | Т | Fast internal RC oscillator trimming step                                                                                                         | T <sub>A</sub> = 25 °C | _   | 1.6 | _   | %    |

Table 31. 16 MHz RC oscillator electrical characteristics

1. PTF = Post Trimming Frequency: The frequency of the output clock after trimming at typical supply voltage and temperature

## 3.15 Analog-to-Digital converter (ADC) electrical characteristics

The device provides a 10-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

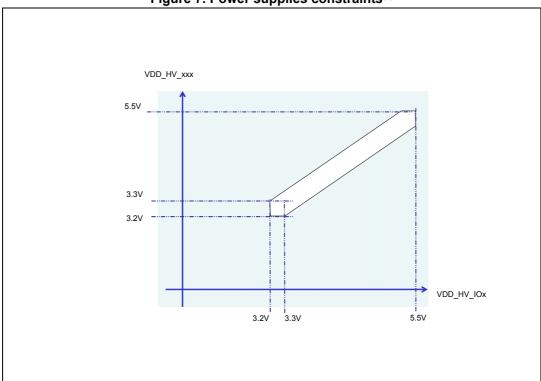

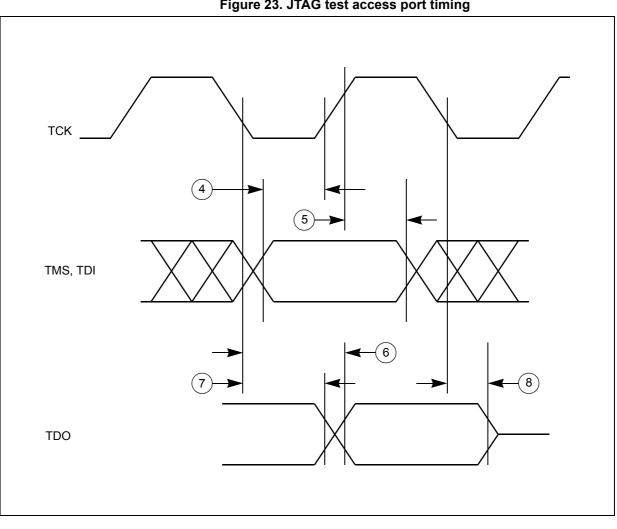

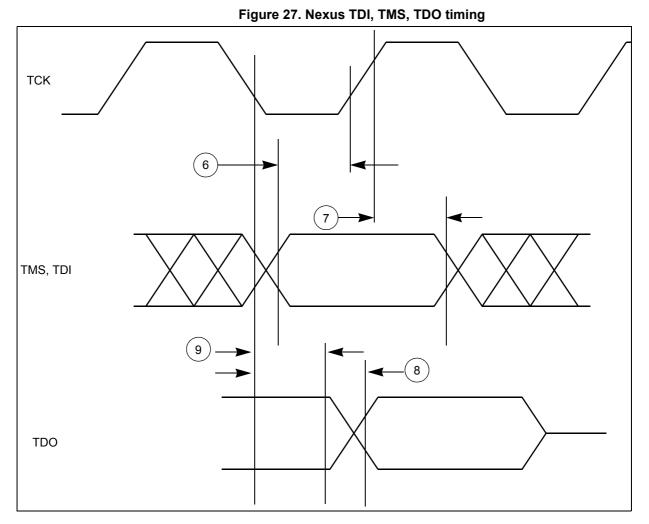

## 3.18.2 IEEE 1149.1 interface timing

|     | Table 50. JTAG pill AC electrical citatacteristics |    |   |                                                        |            |     |     |      |

|-----|----------------------------------------------------|----|---|--------------------------------------------------------|------------|-----|-----|------|

| No. | o. Symbol                                          |    | С | Parameter                                              | Conditions | Min | Мах | Unit |

| 1   | t <sub>JCYC</sub>                                  | CC | D | TCK cycle time                                         | —          | 100 | —   | ns   |

| 2   | t <sub>JDC</sub>                                   | СС | D | TCK clock pulse width (measured at $V_{DD_HV_IOx}/2$ ) | —          | 40  | 60  | ns   |

| 3   | t <sub>TCKRISE</sub>                               | СС | D | TCK rise and fall times (40% – 70%)                    | —          | —   | 3   | ns   |

| 4   | t <sub>TMSS,</sub> t <sub>TDIS</sub>               | СС | D | TMS, TDI data setup time                               | —          | 5   | _   | ns   |

| 5   | t <sub>TMSH,</sub> t <sub>TDIH</sub>               | СС | D | TMS, TDI data hold time                                | —          | 25  | _   | ns   |

| 6   | t <sub>TDOV</sub>                                  | СС | D | TCK low to TDO data valid                              | —          | —   | 40  | ns   |

| 7   | t <sub>TDOI</sub>                                  | СС | D | TCK low to TDO data invalid                            | —          | 0   | _   | ns   |

| 8   | t <sub>TDOHZ</sub>                                 | СС | D | TCK low to TDO high impedance                          | —          | 40  | _   | ns   |

| 9   | t <sub>BSDV</sub>                                  | СС | D | TCK falling edge to output valid                       | —          | —   | 50  | ns   |

| 10  | t <sub>BSDVZ</sub>                                 | СС | D | TCK falling edge to output valid out of high impedance | —          | —   | 50  | ns   |

| 11  | t <sub>BSDHZ</sub>                                 | СС | D | TCK falling edge to output high impedance              | —          |     | 50  | ns   |

| 12  | t <sub>BSDST</sub>                                 | СС | D | Boundary scan input valid to TCK rising edge           | —          | 50  | _   | ns   |

| 13  | t <sub>BSDHT</sub>                                 | CC | D | TCK rising edge to boundary scan input invalid         | —          | 50  | _   | ns   |

Table 38. JTAG pin AC electrical characteristics

### Figure 22. JTAG test clock input timing

Figure 23. JTAG test access port timing

## 3.18.4 External interrupt timing (IRQ pin)

| Table 40. External interrupt timing <sup>(1)</sup> | Table 40. Externa | al interrupt timing <sup>(1)</sup> |

|----------------------------------------------------|-------------------|------------------------------------|

|----------------------------------------------------|-------------------|------------------------------------|

| No. | Symb              | ool | С | Parameter                            | Conditions | Min                  | Max | Unit             |

|-----|-------------------|-----|---|--------------------------------------|------------|----------------------|-----|------------------|

| 1   | t <sub>IPWL</sub> | СС  | D | IRQ pulse width low                  | —          | 4                    | —   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | СС  | D | IRQ pulse width high                 | _          | 4                    | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | СС  | D | IRQ edge to edge time <sup>(2)</sup> | _          | 4 + N <sup>(3)</sup> | _   | t <sub>CYC</sub> |

1. IRQ timing specified at  $f_{SYS}$  = 64 MHz and  $V_{DD_HV_IOx}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$ , and CL = 200pF with SRC = 0b00.

2. Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

3. N= ISR time to clear the flag.

# 6 Revision history

Table 44 summarizes revisions to this document.

| Date        | Revision | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Dec-2010 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18-Oct-2011 | 2        | In the Feature list:<br>Revised the first bullet.<br>Changed "Up to 82 GPIO" to "Up to 80 GPIO"<br>Changed "and 82 GPIO" to "and 49 GPIO"<br>Changed "FlexRay module" to "1 FlexRay™ module".<br>Added Section 1.5: Feature details<br>Table 4: SPC56xP54x/SPC56xP60x series block summary, added<br>FlexRay entry.<br>In the "LQFP176 pinout (top view)" figure:<br>– Pin 104 now is TDI, was PB[5]<br>– Pin 107 now is TDO, was PB[4]<br>– Pin 71 now is NC, was OKOUT<br>– Pin 72 now is NC, was OKOUT B<br>– Pin 87 now is NC, was OKOUT B<br>– Pin 87 now is NC, was OKOUT B<br>– Pin 87 now is NC, was IPP_LIVI_B_VDDIO<br>Table 7: Pin muxing:<br>PB[6] was clk_out_div5, is now clk_out_div256<br>Removed PB[4] and PB[5] rows<br>In the A[3] row, changed ABS[2] to ABS[1]<br>Section 3.11: DC electrical characteristics, added "Peripherals supply<br>current (5 V and 3.3 V)" table<br>Table 13: Thermal characteristics for 144-pin LQFP and<br>Table 13: Thermal characteristics for 144-pin LQFP and<br>Table 30: PLLMRFM electrical specifications (V <sub>DDPLL</sub> = 1.08 V to<br>1.32 V, V <sub>SS</sub> = V <sub>SSPLL</sub> = 0 V, TA = TL to TH), changed the max value<br>of f <sub>SVS</sub> from 120 to 64<br>Table 33: Program and erase specifications:<br>Removed all TBC<br>changed the max value of T <sub>BKPRG</sub> (Data Flash) from 3.0 to 500 µs<br>Added t <sub>ESRT</sub> row<br>Table 17: Voltage regulator electrical characteristics, updated<br>V <sub>DD_LV</sub> REGCOR values<br>Updated Table 18: Low voltage monitor electrical characteristics<br>Updated Table 21: Supply current (5.0 V, NVUSRO[PAD3V5V]=0) and<br>Table 23: Supply current (3.3 V, NVUSRO[PAD3V5V]=1)<br>Removed orderable parts tables. |