#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K × 8                                                                  |

| RAM Size                   | 80K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p60l5ceaay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency)

Programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

## 1.5.9 Main oscillator

The main oscillator provides these features:

- Input frequency range 4 MHz to 40 MHz

- Crystal input mode or Oscillator input mode

- PLL reference

### 1.5.10 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC Oscillator provides these features:

- Nominal frequency 16 MHz

- ±6% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

## **1.5.11 Periodic interrupt timer (PIT)**

The PIT module implements these features:

- Up to four general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

## 1.5.12 System timer module (STM)

The STM module implements these features:

- 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

The STM module is replicated for each processor.

### 1.5.13 Software watchdog timer (SWT)

The SWT has the following features:

- Fault tolerant output

- Safe internal RC oscillator as reference clock

- Windowed watchdog

- Program flow control monitor with 16-bit pseudorandom key generation

The SWT module is replicated for each processor.

## 1.5.14 Fault collection and control unit (FCCU)

The FCCU provides an independent fault reporting mechanism even if the CPU is exhibiting unstable behaviors. The FCCU module has the following features:

- Redundant collection of hardware checker results

- Redundant collection of error information and latch of faults from critical modules on the device

- Collection of self-test results

- Configurable and graded fault control

- Internal reactions (no internal reaction, IRQ)

- External reaction (failure is reported to the external/surrounding system via configurable output pins)

## 1.5.15 System integration unit (SIUL)

The SPC56xP54x/SPC56xP60x SIUL controls MCU pad configuration, external interrupts, general purpose I/O (GPIO) pin configuration, and internal peripheral multiplexing.

The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

The SIUL provides the following features:

- Centralized general purpose input output (GPIO) control of input/output pins and analog input-only pads (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins (except ADC channels) can be alternatively configured as both general purpose input or output pins

- ADC channels support alternative configuration as general purpose inputs

- Direct readback of the pin value is supported on all pins through the SIU

- Configurable digital input filter that can be applied to some general purpose input pins for noise elimination

- Up to 4 internal functions can be multiplexed onto one pin

### 1.5.16 Boot and censorship

Different booting modes are available in the SPC56xP54x/SPC56xP60x:

- From internal flash memory

- Via a serial link

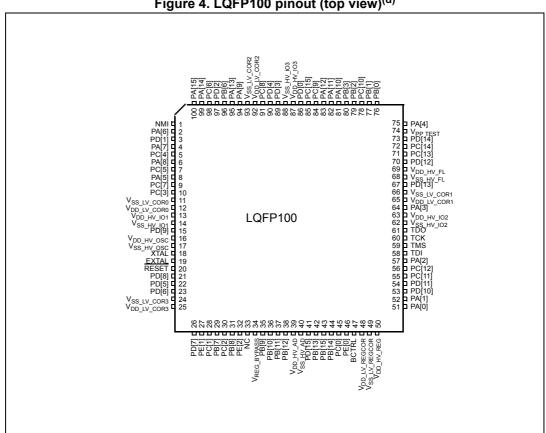

### Figure 4. LQFP100 pinout (top view)<sup>(d)</sup>

#### 2.2 **Pin descriptions**

The following sections provide signal descriptions and related information about the functionality and configuration of the SPC56xP54x/SPC56xP60x devices.

#### 2.2.1 Power supply and reference voltage pins

Table 5 lists the power supply and reference voltage for the SPC56xP54x/SPC56xP60x devices.

| Supply |                                                         |    | Pin |                            |

|--------|---------------------------------------------------------|----|-----|----------------------------|

| Symbol | Description                                             |    |     | LQFP<br>176 <sup>(1)</sup> |

|        | VREG control and power supply pins                      |    |     |                            |

| BCTRL  | Voltage regulator external NPN Ballast base control pin | 47 | 69  | 81                         |

| Table 5. | Supply | pins |

|----------|--------|------|

|----------|--------|------|

d. Availability of port pin alternate functions depends on product selection.

- 2. LQFP176 available only as development package.

- 3. In this pin there is an internal pull; refer to JTAGC chapter in the device reference manual for pull direction.

- 4. Its configuration can be set up by the PCR[108] register inside the SIU module. See SIUL chapter in the device reference manual.

## 2.2.3 Pin muxing

*Table 7* defines the pin list and muxing for the SPC56xP54x/SPC56xP60x devices relative to Full-featured version.

Each row of *Table 7* shows all the possible ways of configuring each pin, via "alternate functions". The default function assigned to each pin after reset is the ALTO function.

Pins marked as external interrupt capable can also be used to resume from STOP and HALT mode.

SPC56xP54x/SPC56xP60x devices provide four main I/O pad types depending on the associated functions:

- *Slow pads* are the most common, providing a compromise between transition time and low electromagnetic emission.

- Medium pads provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- *Fast pads* provide maximum speed. They are used for improved NEXUS debugging capability.

- Symmetric pads are designed to meet FlexRay requirements.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

| Port | Port PCR<br>pin No. | Alternate                       |                                       | Peripheral | I/O     | Pad s   | peed <sup>(6)</sup> |             | Pin                        |    |  |

|------|---------------------|---------------------------------|---------------------------------------|------------|---------|---------|---------------------|-------------|----------------------------|----|--|

|      |                     | function <sup>(2),</sup><br>(3) | cuon <i>"</i> Functions (4) airection |            | SRC = 0 | SRC = 1 | LQFP<br>100         | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |    |  |

|      |                     |                                 |                                       | Po         | ort A   |         |                     |             |                            |    |  |

|      |                     | ALT0                            | GPIO[0]                               | SIUL       | I/O     |         |                     |             |                            |    |  |

|      |                     | ALT1                            | ETC[0]                                | eTimer_0   | I/O     |         |                     |             |                            |    |  |

| A[0] | PCR[0]              | ALT2                            | SCK_2                                 | DSPI_2     | I/O     | Slow    | Medium              | 51          | 73                         | 89 |  |

|      |                     | ALT3                            | F[0]                                  | FCCU       | 0       |         |                     |             |                            |    |  |

|      |                     | —                               | EIRQ[0]                               | SIUL       | I       |         |                     |             |                            |    |  |

|      |                     | ALT0                            | GPIO[1]                               | SIUL       | I/O     |         |                     |             |                            |    |  |

|      |                     | ALT1                            | ETC[1]                                | eTimer_0   | I/O     |         |                     |             |                            |    |  |

| A[1] | PCR[1]              | ALT2                            | SOUT_2                                | DSPI_2     | 0       | Slow    | Medium              | 52          | 74                         | 90 |  |

|      |                     | ALT3                            | F[1]                                  | FCCU       | 0       |         |                     |             |                            |    |  |

|      |                     | —                               | EIRQ[1]                               | SIUL       | I       |         |                     |             |                            |    |  |

### Table 7. Pin muxing<sup>(1)</sup>

|             |            | Alternate                              |                                                                | e 7. Pin mux                                            | I/O                       | ,       | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|----------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3)        | Functions                                                      | Peripheral<br>(4)                                       | direction<br>(5)          | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             | Port B     |                                        |                                                                |                                                         |                           |         |                     |             |             |                            |

| B[0]        | PCR[16]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[16]<br>TXD<br>ETC[2]<br>DEBUG[0]<br>EIRQ[15]              | SIUL<br>FlexCAN_0<br>eTimer_1<br>SSCM<br>SIUL           | I/O<br>O<br>I/O<br>I      | Slow    | Medium              | 76          | 109         | 133                        |

| B[1]        | PCR[17]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[17]<br>CS7_1<br>ETC[3]<br>DEBUG[1]<br>RXD<br>EIRQ[16]     | SIUL<br>DSPI_1<br>eTimer_1<br>SSCM<br>FlexCAN_0<br>SIUL | I/O<br>O<br>I/O<br>I<br>I | Slow    | Medium              | 77          | 110         | 134                        |

| B[2]        | PCR[18]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[18]<br>TXD<br>SOUT_4<br>DEBUG[2]<br>EIRQ[17]              | SIUL<br>LINFlex_0<br>DSPI_4<br>SSCM<br>SIUL             | 1/0<br>0<br>1/0<br>-      | Slow    | Medium              | 79          | 114         | 138                        |

| B[3]        | PCR[19]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[19]<br>—<br>SCK_4<br>DEBUG[3]<br>RXD                      | SIUL<br>—<br>DSPI_4<br>SSCM<br>LINFlex_0                | ₩<br>₩<br>₩<br>₩<br>₩     | Slow    | Medium              | 80          | 116         | 140                        |

| B[6]        | PCR[22]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[22]<br>clk_out<br>CS2_2<br>clk_out_div2<br>56<br>EIRQ[18] | SIUL<br>MC_CGL<br>DSPI_2<br>MC_CGL<br>SIUL              | ₩<br>0<br>0<br>1          | Slow    | Medium              | 96          | 138         | 162                        |

| B[7]        | PCR[23]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[23]<br>—<br>—<br>AN[0]<br>RXD                             | SIUL<br>—<br>—<br>ADC_0<br>LINFlex_0                    | Input Only                | —       | _                   | 29          | 43          | 51                         |

| B[8]        | PCR[24]    | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[24]<br>—<br>—<br>—<br>AN[1]<br>ETC[5]                     | SIUL<br>—<br>—<br>ADC_0<br>eTimer_0                     | Input Only                | _       | _                   | 31          | 47          | 55                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|                     |    |                                                                          | <b>-</b> · |     |                    |      |

|---------------------|----|--------------------------------------------------------------------------|------------|-----|--------------------|------|

| Symbol              |    | Parameter                                                                | Conditions | Min | Max <sup>(2)</sup> | Unit |

| I <sub>INJSUM</sub> | SR | Absolute sum of all injected input<br>currents during overload condition | _          | -50 | 50                 | mA   |

| I <sub>VDD_LV</sub> | SR | Low voltage static current sink through $V_{DD_LV}$                      | _          | _   | 155                | mA   |

| T <sub>STG</sub>    | SR | Storage temperature                                                      | —          | -55 | 150                | °C   |

| TJ                  | SR | Junction temperature under bias                                          | —          | -40 | 150                | °C   |

Table 9. Absolute maximum ratings<sup>(1)</sup> (continued)

Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

2. Absolute maximum voltages are currently maximum burn-in voltages. Absolute maximum specifications for device stress have not yet been determined.

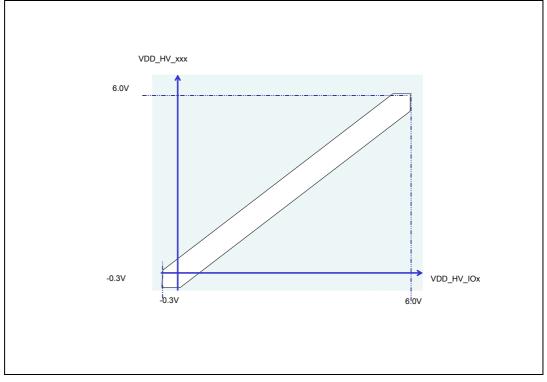

- 3. The difference between each couple of voltage supplies must be less than 300 mV,  $|V_{DD_HV_IOy} V_{DD_HV_IOx}| < 300$  mV.

- 4. Guaranteed by device validation.

- 5. Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD HV REG</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>).

Figure 5 shows the constraints of the different power supplies.

Figure 5. Power supplies constraints

The SPC56xP54x/SPC56xP60x supply architecture provides an ADC supply that is managed independently of standard  $V_{DD_HV}$  supply. *Figure 6* shows the constraints of the ADC power supply.

# 3.6 Electromagnetic interference (EMI) characteristics

|                     |                                                                    |                           |                                    |                 | 1              |      |

|---------------------|--------------------------------------------------------------------|---------------------------|------------------------------------|-----------------|----------------|------|

| Parameter           | Symbol                                                             | Conditions                | f <sub>OSC</sub> /f <sub>BUS</sub> | Frequency       | Level<br>(Max) | Unit |

|                     |                                                                    | V <sub>DD</sub> = 5 V;    | 8 MHz crystal                      | 150 kHz–150 MHz | 18             | dBμV |

|                     |                                                                    | T <sub>A</sub> = 25 °C    | 64 MHz bus<br>No PLL frequency     | 150–1000 MHz    | 12             | υσμν |

|                     | Radiated                                                           | nissions, RBW 9 kHz, Step | modulation                         | IEC Level       | М              | _    |

| V <sub>RE_TEM</sub> | emissions,                                                         |                           | 8 MHz crystal                      | 150 kHz–150 MHz | 18             | dBμV |

|                     | electric field<br>30 MHz–1 GHz<br>RBW 120 kHz,<br>Step Size 80 kHz | 64 MHz bus                | 150–1000 MHz                       | 12              | υσμν           |      |

|                     |                                                                    | RBW 120 kHz,              | ±2% PLL<br>frequency<br>modulation | IEC Level       | М              | _    |

### Table 14. EMI testing specifications

# 3.7 Electrostatic discharge (ESD) characteristics

| Symbol                 |        | Parameter                                      | Conditions | Value         | Unit |

|------------------------|--------|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub>  | SR     | Electrostatic discharge (Human Body Model)     | —          | 2000          | V    |

| N/                     | SR FIA | Electrostatic discharge (Charged Device Model) |            | 750 (corners) | V    |

| V <sub>ESD</sub> (CDM) | SK     | Electrostatic discharge (Charged Device Model) | _          | 500 (other)   | v    |

## Table 15. ESD ratings<sup>(1)(2)</sup>

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## 3.8 **Power management electrical characteristics**

## 3.8.1 Voltage regulator electrical characteristics

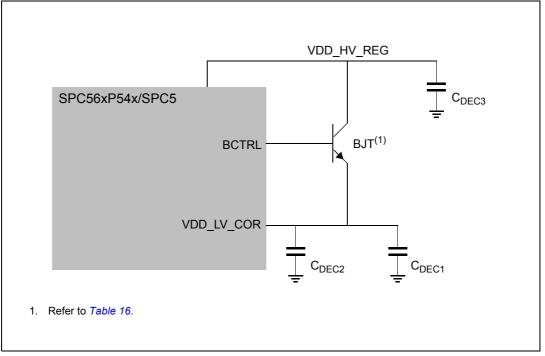

The internal voltage regulator requires an external NPN ballast to be connected as shown in *Figure 9. Table 16* contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the V<sub>DD\_HV\_REG</sub>, BCTRL and V<sub>DD\_LV\_CORx</sub> pins to less than L<sub>Reg</sub>, see *Table 17*.

*Note:* The voltage regulator output cannot be used to drive external circuits. Output pins are used only for decoupling capacitances.

$V_{DD\_LV\_COR}$  must be generated using internal regulator and external NPN transistor. It is not possible to provide  $V_{DD\_LV\_COR}$  through external regulator.

For the SPC56xP54x/SPC56xP60x microcontroller, capacitors, with total values not below  $C_{DEC1}$ , should be placed between  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  close to external ballast transistor emitter. 4 capacitors, with total values not below  $C_{DEC2}$ , should be placed close to microcontroller pins between each  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  supply pairs and the

$V_{DD\_LV\_REGCOR}/V_{SS\_LV\_REGCOR}$  pair. Additionally, capacitors with total values not below  $C_{DEC3}$ , should be placed between the  $V_{DD\_HV\_REG}/V_{SS\_HV\_REG}$  pins close to ballast collector. Capacitors values have to take into account capacitor accuracy, aging and variation versus temperature.

All reported information are valid for voltage and temperature ranges described in recommended operating condition, *Table 10* and *Table 11*.

Figure 9. Voltage regulator configuration

| Part  | Manufacturer | Approved derivatives <sup>(1)</sup> |  |

|-------|--------------|-------------------------------------|--|

|       | ON Semi      | BCP68                               |  |

| BCP68 | NXP          | BCP68-25                            |  |

|       | Infineon     | BCP68-25                            |  |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25          |  |

| BC868 | NXP          | BC868                               |  |

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;          |  |

| BCOT  | NXP          | BC817-16;BC817-25                   |  |

|       | ST           | BCP56-16                            |  |

| BCP56 | Infineon     | BCP56-10;BCP56-16                   |  |

| BCF30 | ON Semi      | BCP56-10                            |  |

|       | NXP          | BCP56-10;BCP56-16                   |  |

#### Table 16. Approved NPN ballast components

1. For automotive applications please check with the appropriate transistor vendor for automotive grade certification.

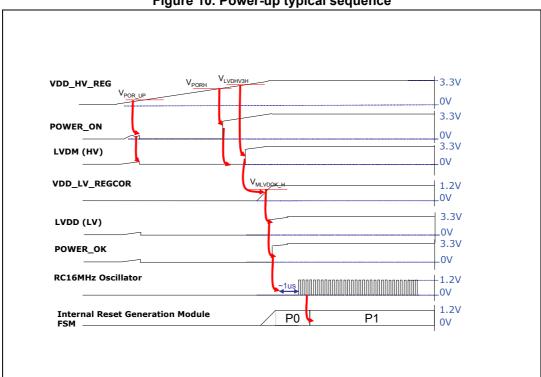

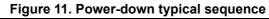

Figure 10. Power-up typical sequence

## 3.11 DC electrical characteristics

## 3.11.1 DC electrical characteristics (5 V)

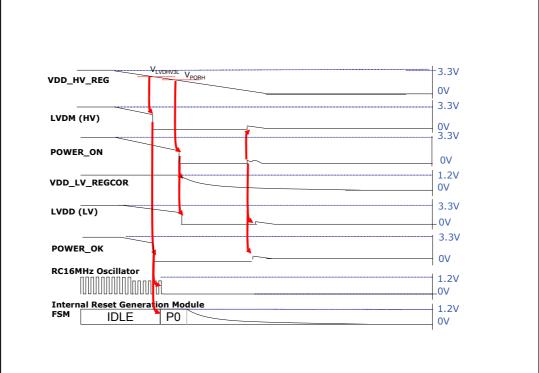

*Table 20* gives the DC electrical characteristics at 5 V ( $4.5 \text{ V} < \text{V}_{\text{DD}_{\text{HV}_{\text{IOX}}}} < 5.5 \text{ V}$ , NVUSRO[PAD3V5V]=0) as described in *Figure 13*.

### Figure 13. I/O input DC electrical characteristics definition

| Table 20. DC electrical chara | acteristics (5.0 V, | NVUSRO[PAD3 | V5V]=0) |

|-------------------------------|---------------------|-------------|---------|

|                               |                     |             |         |

| Symbol              | I | Parameter                            | Conditions              | Min                         | Мах                         | Unit |

|---------------------|---|--------------------------------------|-------------------------|-----------------------------|-----------------------------|------|

| V <sub>IL</sub>     | D | Minimum low level input voltage      | —                       | -0.1 <sup>(1)</sup>         | —                           | V    |

| V <sub>IL</sub>     | Ρ | Maximum level input voltage          | —                       | —                           | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>     | Ρ | Minimum high level input voltage     | —                       | 0.65 V <sub>DD_HV_IOx</sub> | —                           | V    |

| V <sub>IH</sub>     | D | Maximum high level input voltage     | —                       | _                           | $V_{DD_HV_IOx} + 0.1^{(1)}$ | V    |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis           | —                       | 0.1 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_S</sub>   | Ρ | Slow, low level output voltage       | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8V <sub>DD_HV_IOx</sub>   | —                           | V    |

| V <sub>OL_M</sub>   | Ρ | Medium, low level output voltage     | I <sub>OL</sub> = 3 mA  | —                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_M</sub>   | Ρ | Medium, high level output voltage    | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>OL_F</sub>   | Ρ | Fast, low level output voltage       | I <sub>OL</sub> = 3 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_F</sub>   | Ρ | Fast, high level output voltage      | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |

| V <sub>OL_SYM</sub> | Ρ | Symmetric, low level output voltage  | I <sub>OL</sub> = 3 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OH</sub> = –3 mA | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |

| Symbol          |   | Parameter                                           | Conditions                        | Min  | Мах | Unit |

|-----------------|---|-----------------------------------------------------|-----------------------------------|------|-----|------|

| 1               | Р | P Equivalent pull-up current                        | $V_{IN} = V_{IL}$                 | -130 | _   |      |

| I <sub>PU</sub> | 1 | Equivalent puil-up current                          | $V_{IN} = V_{IH}$                 | _    | -10 | μA   |

|                 | Р | Equivalent pull-down current                        | $V_{IN} = V_{IL}$                 | 10   | _   |      |

| I <sub>PD</sub> | Г | Equivalent puil-down current                        | $V_{IN} = V_{IH}$                 |      | 130 | μA   |

| Ι <sub>ΙL</sub> | Ρ | Input leakage current<br>(all bidirectional ports)  | T <sub>A</sub> =40 to 125 °C      | -1   | 1   | μA   |

| IIL             | Ρ | Input leakage current<br>(all ADC input-only ports) | T <sub>A</sub> = -40 to 125 °C    | -0.5 | 0.5 | μA   |

| C <sub>IN</sub> | D | Input capacitance                                   | —                                 | _    | 10  | pF   |

| 1               | D |                                                     | V <sub>IN</sub> = V <sub>IL</sub> | -130 | _   |      |

| I <sub>PU</sub> |   | RESET, equivalent pull-up current                   | $V_{IN} = V_{IH}$                 | —    | -10 | μA   |

| 1               | D | RESET, equivalent pull-down                         | V <sub>IN</sub> = V <sub>IL</sub> | 10   | _   |      |

| I <sub>PD</sub> |   | current                                             | V <sub>IN</sub> = V <sub>IH</sub> | _    | 130 | μA   |

## Table 20. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V]=0) (continued)

1. "SR" parameter values must not exceed the absolute maximum ratings shown in *Table 9*.

| Symbol                |        |         | Dovomotov                                                                         | Conditions                                                                                      |        | Value                                   |                                | Unit                     |                                                       |    |     |    |

|-----------------------|--------|---------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|-----------------------------------------|--------------------------------|--------------------------|-------------------------------------------------------|----|-----|----|

| Symbol                | Cymbol |         | Parameter                                                                         | Conditions                                                                                      |        | Тур                                     | Max                            | Unit                     |                                                       |    |     |    |

|                       |        |         | RUN — Maximum Mode <sup>(1)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V<br>ADC Freq = 32 MHz<br>PLL Freq = 64 MHz | 64 MHz | 90                                      | 120                            |                          |                                                       |    |     |    |

|                       |        |         |                                                                                   |                                                                                                 | 16 MHz | 21                                      | 37                             |                          |                                                       |    |     |    |

|                       | Т      |         | RUN - Platform consumption, single core <sup>(2)</sup>                            |                                                                                                 | 40 MHz | 35                                      | 55                             |                          |                                                       |    |     |    |

|                       |        |         | 5                                                                                 | VDD_LV_CORE                                                                                     | 64 MHz | 48                                      | 72                             |                          |                                                       |    |     |    |

|                       |        |         |                                                                                   |                                                                                                 |        | 24                                      | 41                             |                          |                                                       |    |     |    |

| IDD_LV_CORE           |        |         | RUN - Platform consumption, dual core <sup>(3)</sup>                              |                                                                                                 | 40 MHz | 42                                      | 64                             | -                        |                                                       |    |     |    |

|                       |        |         |                                                                                   |                                                                                                 | 64 MHz | 58                                      | 85                             |                          |                                                       |    |     |    |

|                       | Ρ      | Supply  | RUN — Maximum Mode <sup>(4)</sup>                                                 | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V                                           | 64 MHz | 85                                      | 113                            | mA                       |                                                       |    |     |    |

|                       |        | current | HALT Mode <sup>(5)</sup>                                                          | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V                                           | _      | 5.5                                     | 15                             |                          |                                                       |    |     |    |

|                       |        |         |                                                                                   |                                                                                                 |        |                                         |                                | STOP Mode <sup>(6)</sup> | V <sub>DD_LV_CORE</sub><br>externally forced at 1.3 V | _  | 4.5 | 13 |

|                       | т      |         |                                                                                   |                                                                                                 |        | Flash memory supply current during read | V <sub>DD_HV_FL</sub> at 5.0 V | _                        |                                                       | 14 |     |    |

| I <sub>DD_FLASH</sub> |        |         | Flash memory supply current<br>during erase operation on 1<br>flash memory module | V <sub>DD_HV_FL</sub> at 5.0 V                                                                  | _      | _                                       | 42                             |                          |                                                       |    |     |    |

| I <sub>DD_ADC</sub>   | т      |         | ADC supply current —<br>Maximum Mode                                              | V <sub>DD_HV_AD</sub> at 5.0 V<br>ADC Freq = 16 MHz                                             | _      | 3                                       | 4                              |                          |                                                       |    |     |    |

| I <sub>DD_OSC</sub>   | Т      |         | OSC supply current                                                                | V <sub>DD_OSC</sub> at 5.0 V                                                                    | 8 MHz  | 2.6                                     | 3.2                            |                          |                                                       |    |     |    |

Maximum mode configuration: Code fetched from Flash executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

RAM, Code and Data Flash powered, code fetched from Flash executed by single core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- RAM, Code and Data Flash powered, code fetched from Flash executed by dual core, all peripherals gated; IRC16MHz on, PLL64MHz OFF (except for code running at 64 MHz). Code is performing continuous data transfer from Flash to RAM.

- Maximum mode configuration: Code fetched from RAM executed by dual core, SIUL, PIT, ADC\_0, eTimer\_0/1, LINFlex\_0/1, STM, INTC\_0/1, DSPI\_0/1/2/3/4, FlexCAN\_0/1, FlexRay (static consumption), CRC\_0/1, FCCU, SRAM enabled. I/O supply current excluded.

5. HALT mode configuration, only for the "P" classification: Code Flash memory in low power mode, data Flash memory in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

STOP mode configuration, only for the "P" classification: Code and data Flash memories in power down mode, OSC/PLL are OFF, FIRC is ON, Core clock gated, all peripherals are disabled.

## 3.11.2 DC electrical characteristics (3.3 V)

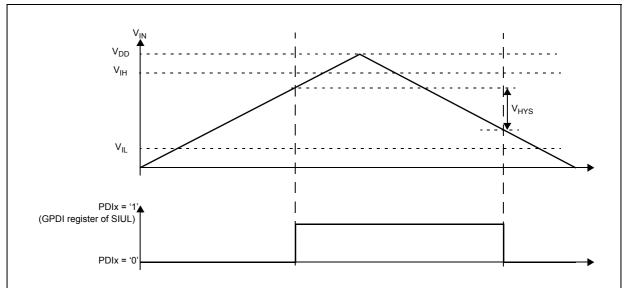

*Table 22* gives the DC electrical characteristics at 3.3 V ( $3.0 \text{ V} < \text{V}_{\text{DD}_{\text{HV}_{\text{IOx}}}} < 3.6 \text{ V}$ , NVUSRO[PAD3V5V]=1) as described in *Figure 14*.

### Figure 14. I/O input DC electrical characteristics definition

| Symbo               | I | Parameter                            | Conditions                        | Min                          | Мах                         | Unit |

|---------------------|---|--------------------------------------|-----------------------------------|------------------------------|-----------------------------|------|

| V <sub>IL</sub>     | D | Minimum low level input voltage      | —                                 | -0.1 <sup>(2)</sup>          | _                           | V    |

| V <sub>IL</sub>     | Ρ | Maximum low level input voltage      | —                                 | —                            | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>     | Ρ | Minimum high level input voltage     | —                                 | 0.65 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>IH</sub>     | D | Maximum high level input voltage     | —                                 | —                            | $V_{DD_HV_IOx} + 0.1^{(2)}$ | V    |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis           | —                                 | 0.1 V <sub>DD_HV_IOx</sub>   | —                           | V    |

| V <sub>OL_S</sub>   | Ρ | Slow, low level output voltage       | I <sub>OL</sub> = 1.5 mA          | —                            | 0.5                         | V    |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage      | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_M</sub>   | Ρ | Medium, low level output voltage     | I <sub>OL</sub> = 2 mA            | —                            | 0.5                         | V    |

| V <sub>OH_M</sub>   | Ρ | Medium, high level output voltage    | I <sub>OH</sub> = -2 mA           | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_F</sub>   | Ρ | Fast, high level output voltage      | I <sub>OL</sub> = 11 mA           | —                            | 0.5                         | V    |

| V <sub>OH_F</sub>   | Ρ | Fast, high level output voltage      | I <sub>OH</sub> = –11 mA          | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OL</sub> = 1.5 mA          | _                            | 0.5                         | V    |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage | I <sub>OH</sub> = –1.5 mA         | V <sub>DD_HV_IOx</sub> - 0.8 | _                           | V    |

| 1                   | D | Equivalant pull un current           | V <sub>IN</sub> = V <sub>IL</sub> | -130                         | —                           |      |

| I <sub>PU</sub>     | Р | P Equivalent pull-up current         | V <sub>IN</sub> = V <sub>IH</sub> | —                            | -10                         | μA   |

## 3.11.3 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in *Table 25*.

| Package | Supply segment   |                  |                  |                  |                  |                   |                  |  |  |  |

|---------|------------------|------------------|------------------|------------------|------------------|-------------------|------------------|--|--|--|

|         | 1                | 2                | 3                | 4                | 5                | 6                 | 7                |  |  |  |

| LQFP144 | pin8 – pin20     | pin23 –<br>pin38 | pin39 –<br>pin55 | pin58 –<br>pin68 | pin73 –<br>pin89 | pin92 –<br>pin125 | pin128 –<br>pin5 |  |  |  |

| LQFP100 | pin15 –<br>pin26 | pin27 –<br>pin38 | pin41 –<br>pin46 | pin51 –<br>pin61 | pin64 –<br>pin86 | pin89 – pin10     | —                |  |  |  |

| Table 25 | I/O supply | segment |

|----------|------------|---------|

|----------|------------|---------|

### Table 26. I/O consumption

| Symbol                             |          | с | Parameter                         | Conditions <sup>(1)</sup>                     |                                               |     |     |      | Unit  |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|------------------------------------|----------|---|-----------------------------------|-----------------------------------------------|-----------------------------------------------|-----|-----|------|-------|----|---|-------------------------------|---|---|-----------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------|-----|-----|----|

| Gymbol                             |          |   | i arameter                        | Contractors                                   |                                               | Min | Тур | Мах  |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| I <sub>SWTSLW</sub> <sup>(2)</sup> | CC       | П | Dynamic I/O current<br>for SLOW   | C <sub>1</sub> = 25 pF                        | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _   | 20   | mA    |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| SWISLW                             | 00       | נ | configuration                     | 0 <u> </u>                                    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |     | 16   | 110 ( |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| I <sub>SWTMED</sub> <sup>(2)</sup> | CC       | П | Dynamic I/O current<br>for MEDIUM | C <sub>1</sub> = 25 pF                        | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | _   | 29   | mA    |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| SWIMED                             | , CC     | D | configuration                     | 0L - 20 pi                                    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |     | 17   | 110 ( |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| I <sub>SWTFST</sub> <sup>(2)</sup> | сс       | П | Dynamic I/O current<br>for FAST   | C <sub>1</sub> = 25 pF                        | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _   | 110  | mA    |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| SWIFST                             |          |   | D                                 | U                                             |                                               |     |     | D    | D     |    | D | D                             | D | D | configuration                           |                                               | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |                               | _   | 50  |    |

|                                    |          | D | D                                 | D                                             | D                                             | D   | D   | D    | D     | D  |   | C <sub>L</sub> = 25 pF, 2 MHz |   |   | _                                       | 2.3                                           |                                               |                               |     |     |    |

|                                    |          |   |                                   |                                               |                                               |     |     |      |       |    | D | D                             | D |   | C <sub>L</sub> = 25 pF, 4 MHz           | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |                                               | _                             | 3.2 |     |    |

| I <sub>RMSSLW</sub>                | <u> </u> |   |                                   |                                               |                                               |     |     |      |       |    |   |                               |   | D | Root medium square I/O current for SLOW | C <sub>L</sub> = 100 pF, 2 MHz                |                                               | _                             | _   | 6.6 | mA |

| 'RMSSLW                            | 00       |   |                                   |                                               |                                               |     |     |      |       |    |   |                               |   |   |                                         | U                                             | configuration                                 | C <sub>L</sub> = 25 pF, 2 MHz |     | _   | —  |

|                                    |          |   |                                   | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —                                             |     | 2.3 | 1    |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|                                    |          |   |                                   | C <sub>L</sub> = 100 pF, 2 MHz                |                                               | _   | _   | 4.7  | 1     |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|                                    |          |   |                                   | C <sub>L</sub> = 25 pF, 13 MHz                |                                               | _   |     | 6.6  |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|                                    |          |   | Root medium square                | C <sub>L</sub> = 25 pF, 40 MHz                | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | _   | 13.4 |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| 1                                  | сс       |   |                                   | I/O current for                               | C <sub>L</sub> = 100 pF, 13 MHz               |     | _   | —    | 18.3  | mA |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

| RMSMED                             |          |   | MEDIUM<br>configuration           | C <sub>L</sub> = 25 pF, 13 MHz                |                                               | _   | _   | 5    |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|                                    |          |   | garation                          | C <sub>L</sub> = 25 pF, 40 MHz                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _   | 8.5  |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

|                                    |          |   |                                   | C <sub>L</sub> = 100 pF, 13 MHz               |                                               |     | —   | 11   |       |    |   |                               |   |   |                                         |                                               |                                               |                               |     |     |    |

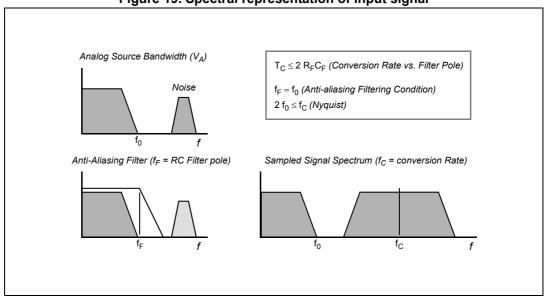

$C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_F C_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing.

Figure 19. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

### **Equation 11**

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### **Equation 12**

$$C_F > 2048 \times C_S$$

57

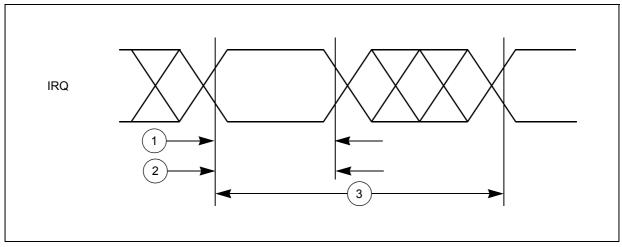

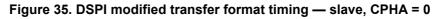

## 3.18.5 DSPI timing

| No. | Symbol                  |          | Symbol |                             | Symbol                                |                             | Symbol               |                            | С     | Parameter | Conditions | Min | Max | Unit |

|-----|-------------------------|----------|--------|-----------------------------|---------------------------------------|-----------------------------|----------------------|----------------------------|-------|-----------|------------|-----|-----|------|

| 4   |                         | + 000    |        |                             | Master (MTFE = 0)                     | 60                          | _                    |                            |       |           |            |     |     |      |

| 1   | 1 t <sub>SCK</sub> CC D |          | D      | DSPI cycle time             | Slave (MTFE = 0)                      | 60                          | _                    | ns                         |       |           |            |     |     |      |

| 2   | t <sub>CSC</sub>        | СС       | D      | PCS to SCK delay            |                                       | 16                          | _                    | ns                         |       |           |            |     |     |      |

| 3   | t <sub>ASC</sub>        | СС       | D      | After SCK delay             | —                                     | 26                          |                      | ns                         |       |           |            |     |     |      |

| 4   | t <sub>SDC</sub>        | СС       | D      | SCK duty cycle              | —                                     | 0.4 × t <sub>SCK</sub>      | $0.6 \times t_{SCK}$ | ns                         |       |           |            |     |     |      |

| 5   | t <sub>A</sub>          | СС       | D      | Slave access time           | SS active to SOUT valid               | —                           | 30                   | ns                         |       |           |            |     |     |      |

| 6   | t <sub>DIS</sub>        | сс       | D      | Slave SOUT disable time     | SS inactive to SOUT High-Z or invalid | _                           | 16                   | ns                         |       |           |            |     |     |      |

| 7   | t <sub>PCSC</sub>       | СС       | D      | PCSx to PCSS time           | —                                     | 13                          | _                    | ns                         |       |           |            |     |     |      |

| 8   | t <sub>PASC</sub>       | СС       | D      | PCSS to PCSx time           | _                                     | 13                          | _                    | ns                         |       |           |            |     |     |      |

|     | 9 t <sub>SUI</sub> CC   | 66       |        |                             |                                       |                             |                      | Master (MTFE = 0)          | 35    | _         |            |     |     |      |

| 0   |                         |          |        | <u> </u>                    | cc                                    | <u> </u>                    | П                    | Data setup time for inputs | Slave | 4         |            | ns  |     |      |

| 9   |                         | 00       |        |                             | Master (MTFE = 1, CPHA = 0)           | 35                          | _                    | 115                        |       |           |            |     |     |      |

|     |                         |          |        |                             |                                       | Master (MTFE = 1, CPHA = 1) | 35                   | -                          |       |           |            |     |     |      |

|     |                         |          |        |                             | Master (MTFE = 0)                     | -5                          |                      |                            |       |           |            |     |     |      |

| 10  | ÷                       | сс       |        | Data hold time for inputs   | Slave                                 | 4                           | -                    |                            |       |           |            |     |     |      |

| 10  | 10 t <sub>HI</sub> C    | 00       |        |                             | Master (MTFE = 1, CPHA = 0)           | 11                          |                      | ns                         |       |           |            |     |     |      |

|     |                         |          |        |                             | Master (MTFE = 1, CPHA = 1)           | -5                          |                      |                            |       |           |            |     |     |      |

|     | 11 t <sub>SUO</sub> (   |          |        |                             | Master (MTFE = 0)                     | —                           | 12                   |                            |       |           |            |     |     |      |

| 11  |                         | <u> </u> | П      | Data valid (after SCK edge) | Slave                                 |                             | 36                   | ns                         |       |           |            |     |     |      |

|     |                         |          |        |                             | Master (MTFE = 1, CPHA = 0)           | —                           | 12                   | 115                        |       |           |            |     |     |      |

|     |                         |          |        |                             | Master (MTFE = 1, CPHA = 1)           | _                           | 12                   |                            |       |           |            |     |     |      |

Table 41. DSPI timing<sup>(1)</sup>

Figure 34. DSPI modified transfer format timing — master, CPHA = 1

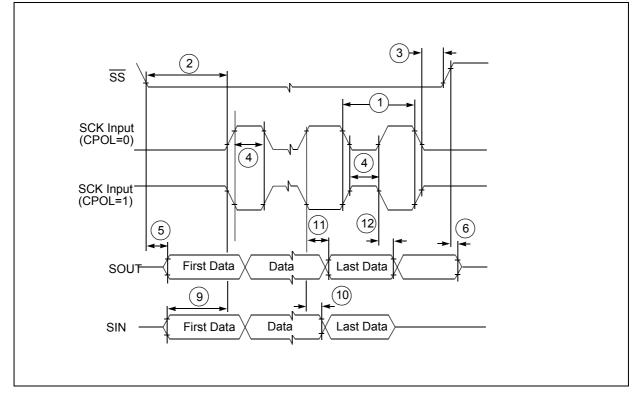

# 5 Ordering information

## Figure 40. Ordering information scheme<sup>(h)</sup>

h. Not all configurations are available on the market. Please contact your ST sales representative to get the list of orderable commercial part number.

# 6 Revision history

Table 44 summarizes revisions to this document.

| Date        | Revision | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Dec-2010 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18-Oct-2011 | 2        | In the Feature list:<br>Revised the first bullet.<br>Changed "Up to 82 GPIO" to "Up to 80 GPIO"<br>Changed "and 82 GPIO" to "and 49 GPIO"<br>Changed "FlexRay module" to "1 FlexRay™ module".<br>Added Section 1.5: Feature details<br>Table 4: SPC56xP54x/SPC56xP60x series block summary, added<br>FlexRay entry.<br>In the "LQFP176 pinout (top view)" figure:<br>– Pin 104 now is TDI, was PB[5]<br>– Pin 107 now is TDO, was PB[4]<br>– Pin 71 now is NC, was OKOUT<br>– Pin 72 now is NC, was OKOUT B<br>– Pin 87 now is NC, was OKOUT B<br>– Pin 87 now is NC, was OKOUT B<br>– Pin 87 now is NC, was IPP_LIVI_B_VDDIO<br>Table 7: Pin muxing:<br>PB[6] was clk_out_div5, is now clk_out_div256<br>Removed PB[4] and PB[5] rows<br>In the A[3] row, changed ABS[2] to ABS[1]<br>Section 3.11: DC electrical characteristics, added "Peripherals supply<br>current (5 V and 3.3 V)" table<br>Table 13: Thermal characteristics for 144-pin LQFP and<br>Table 13: Thermal characteristics for 144-pin LQFP and<br>Table 30: PLLMRFM electrical specifications (V <sub>DDPLL</sub> = 1.08 V to<br>1.32 V, V <sub>SS</sub> = V <sub>SSPLL</sub> = 0 V, TA = TL to TH), changed the max value<br>of f <sub>SVS</sub> from 120 to 64<br>Table 33: Program and erase specifications:<br>Removed all TBC<br>changed the max value of T <sub>BKPRG</sub> (Data Flash) from 3.0 to 500 µs<br>Added t <sub>ESRT</sub> row<br>Table 17: Voltage regulator electrical characteristics, updated<br>V <sub>DD_LV</sub> REGCOR values<br>Updated Table 18: Low voltage monitor electrical characteristics<br>Updated Table 21: Supply current (5.0 V, NVUSRO[PAD3V5V]=0) and<br>Table 23: Supply current (3.3 V, NVUSRO[PAD3V5V]=1)<br>Removed orderable parts tables. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved