#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56ap54l5befar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | -                          | ,                          |  |  |  |

|---------|----------------------------|----------------------------|--|--|--|

| Package | Part number                |                            |  |  |  |

|         | 768 KB Flash               | 1 MB Flash                 |  |  |  |

| LQFP144 | SPC560P54L5<br>SPC56AP54L5 | SPC560P60L5<br>SPC56AP60L5 |  |  |  |

| LQFP100 | SPC560P54L3<br>SPC56AP54L3 | SPC560P60L3<br>SPC56AP60L3 |  |  |  |

#### Table 1. Device summary

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | Block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                          |

| Clock generation module<br>(MC_CGM)               | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Controller area network<br>(FlexCAN)              | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                            | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.                                                                                                                                                   |

| Cyclic redundancy checker<br>(CRC) unit           | Is dedicated to the computation of CRC off-loading the CPU. Each context has<br>a separate CRC computation engine in order to allow the concurrent<br>computation of the CRC of multiple data streams.                                                                                                            |

| Deserial serial peripheral<br>interface (DSPI)    | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)              | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels                                                                                                                                                                                                     |

| Enhanced timer (eTimer)                           | Provides enhanced programmable up/down modulo counting                                                                                                                                                                                                                                                            |

| Error correction status module (ECSM)             | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| External oscillator (XOSC)                        | Provides an output clock used as input reference for FMPLL_0 or as reference clock for specific modules depending on system needs                                                                                                                                                                                 |

| Fault collection and control unit (FCCU)          | Provides functional safety to the device                                                                                                                                                                                                                                                                          |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexRay (FlexRay communication controller)        | Provides high-speed distributed control for advanced automotive applications                                                                                                                                                                                                                                      |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                   | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode<br>transition sequences in all functional states; also manages the power control<br>unit, reset generation module and clock generation module, and holds the<br>configuration, control and status registers accessible for applications |

### Table 4. SPC56xP54x/SPC56xP60x series block summary

The crossbar provides the following features:

- 6 master ports:

- 2 e200z0 core complex Instruction ports

- 2 e200z0 core complex Load/Store Data ports

- eDMA

- FlexRay

- 6 slave ports:

- 2 Flash memory (code flash and data flash)

- 2 SRAM (48 KB + 32 KB)

- 2 PBRIDGE

- 32-bit internal address, 32-bit internal data paths

- Fixed Priority Arbitration based on Port Master

- Temporary dynamic priority elevation of masters

### 1.5.3 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size.

The eDMA module provides the following features:

- 16 channels support independent 8, 16 or 32-bit single value or block transfers

- Supports variable sized queues and circular queues

- Source and destination address registers are independently configured to postincrement or remain constant

- Each transfer is initiated by a peripheral, CPU, or eDMA channel request

- Each eDMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer

- DMA transfers possible between system memories, DSPIs, ADC, eTimer and CTU

- Programmable DMA Channel Multiplexer for assignment of any DMA source to any available DMA channel with up to 30 potential request sources

- eDMA abort operation through software

#### 1.5.4 On-chip flash memory with ECC

The SPC56xP54x/SPC56xP60x provides up to 1024 KB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used for instruction and/or data storage. The flash memory module interfaces the system bus to a dedicated flash memory array controller. It supports a 32-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains a four-entry, 4x128-bit prefetch buffers. Prefetch buffer hits allow no-wait responses. Normal flash memory array accesses are registered and are forwarded to the system bus on the following cycle, incurring 2 wait states.

| Table 6. System pins (continued) |                                                                                                                                                                                      |                   |        |                     |             |             |                            |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|---------------------|-------------|-------------|----------------------------|--|--|--|--|

|                                  |                                                                                                                                                                                      |                   | Pad Sp | beed <sup>(1)</sup> | Pin         |             |                            |  |  |  |  |

| Symbol                           | Description                                                                                                                                                                          | Direction         | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |  |  |  |  |

| MDO5                             | Nexus Message Data Output—line 5                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 8                          |  |  |  |  |

| MDO6                             | Nexus Message Data Output—line 6                                                                                                                                                     | Output<br>Only    | Fast   |                     | _           | _           | 9                          |  |  |  |  |

| MDO7                             | Nexus Message Data Output—line 7                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 110                        |  |  |  |  |

| MDO8                             | Nexus Message Data Output—line 8                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 111                        |  |  |  |  |

| MDO9                             | Nexus Message Data Output—line 9                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 112                        |  |  |  |  |

| MDO10                            | Nexus Message Data Output—line 10                                                                                                                                                    | Output<br>Only    | Fa     | ist                 | _           | _           | 166                        |  |  |  |  |

| MDO11                            | Nexus Message Data Output—line 11                                                                                                                                                    | Output<br>Only    | Fa     | ist                 | _           | _           | 171                        |  |  |  |  |

| RDY                              | Nexus ready output                                                                                                                                                                   | Output<br>Only    | _      | _                   | _           | _           | 172                        |  |  |  |  |

| NMI                              | Non-Maskable Interrupt                                                                                                                                                               | Input Only        | _      | _                   | 1           | 1           | 1                          |  |  |  |  |

| XTAL                             | Analog output of the oscillator amplifier<br>circuit. Needs to be grounded if oscillator is<br>used in bypass mode.                                                                  | _                 | _      | _                   | 18          | 29          | 37                         |  |  |  |  |

| EXTAL                            | Analog input of the oscillator amplifier<br>circuit, when the oscillator is not in bypass<br>mode.<br>Analog input for the clock generator when<br>the oscillator is in bypass mode. | _                 | _      |                     | 19          | 30          | 38                         |  |  |  |  |

| TMS <sup>(3)</sup>               | JTAG state machine control                                                                                                                                                           | Input Only        |        | _                   | 59          | 87          | 105                        |  |  |  |  |

| TCK <sup>(3)</sup>               | JTAG clock                                                                                                                                                                           | Input Only        | —      | _                   | 60          | 88          | 106                        |  |  |  |  |

| TDI <sup>(3)</sup>               | JTAG data input                                                                                                                                                                      | Input Only        | —      | —                   | 58          | 86          | 104                        |  |  |  |  |

| TDO <sup>(3)</sup>               | JTAG data output                                                                                                                                                                     | Output<br>Only    | _      | _                   | 61          | 89          | 107                        |  |  |  |  |

|                                  | Reset                                                                                                                                                                                | pin               |        |                     |             |             |                            |  |  |  |  |

| RESET <sup>(4)</sup>             | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                                            | Bidirection<br>al | Medium | _                   | 20          | 31          | 39                         |  |  |  |  |

|                                  | Test p                                                                                                                                                                               | in                |        |                     |             |             |                            |  |  |  |  |

| V <sub>PP TEST</sub>             | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | —                 | _      | _                   | 74          | 107         | 131                        |  |  |  |  |

| V <sub>REG_BYPASS</sub>          | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | _                 | _      |                     | 34          | 51          | 59                         |  |  |  |  |

|                                  |                                                                                                                                                                                      |                   |        |                     |             |             |                            |  |  |  |  |

#### Table 6. System pins (continued)

1. SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

- 2. LQFP176 available only as development package.

- 3. In this pin there is an internal pull; refer to JTAGC chapter in the device reference manual for pull direction.

- 4. Its configuration can be set up by the PCR[108] register inside the SIU module. See SIUL chapter in the device reference manual.

### 2.2.3 Pin muxing

*Table 7* defines the pin list and muxing for the SPC56xP54x/SPC56xP60x devices relative to Full-featured version.

Each row of *Table 7* shows all the possible ways of configuring each pin, via "alternate functions". The default function assigned to each pin after reset is the ALTO function.

Pins marked as external interrupt capable can also be used to resume from STOP and HALT mode.

SPC56xP54x/SPC56xP60x devices provide four main I/O pad types depending on the associated functions:

- *Slow pads* are the most common, providing a compromise between transition time and low electromagnetic emission.

- Medium pads provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- *Fast pads* provide maximum speed. They are used for improved NEXUS debugging capability.

- Symmetric pads are designed to meet FlexRay requirements.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

| Port    | PCR                             | Alternate |         | Peripheral       | I/O     | Pad speed <sup>(6)</sup> |             | Pin         |                            |    |

|---------|---------------------------------|-----------|---------|------------------|---------|--------------------------|-------------|-------------|----------------------------|----|

| pin No. | function <sup>(2),</sup><br>(3) | Functions | (4)     | direction<br>(5) | SRC = 0 | SRC = 1                  | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |    |

|         |                                 |           |         | Po               | ort A   |                          |             |             |                            |    |

|         |                                 | ALT0      | GPIO[0] | SIUL             | I/O     |                          |             |             |                            |    |

|         |                                 | ALT1      | ETC[0]  | eTimer_0         | I/O     |                          |             |             |                            |    |

| A[0]    | PCR[0]                          | ALT2      | SCK_2   | DSPI_2           | I/O     | Slow                     | Medium 51   | 51          | 73                         | 89 |

|         |                                 | ALT3      | F[0]    | FCCU             | 0       |                          |             |             |                            |    |

|         |                                 | —         | EIRQ[0] | SIUL             | I       |                          |             |             |                            |    |

|         |                                 | ALT0      | GPIO[1] | SIUL             | I/O     |                          |             |             |                            |    |

|         |                                 | ALT1      | ETC[1]  | eTimer_0         | I/O     |                          |             |             |                            |    |

| A[1]    | PCR[1]                          | ALT2      | SOUT_2  | DSPI_2           | 0       | Slow                     | Medium      | 52          | 74                         | 90 |

|         |                                 | ALT3      | F[1]    | FCCU             | 0       |                          |             |             |                            |    |

|         |                                 | —         | EIRQ[1] | SIUL             | I       |                          |             |             |                            |    |

#### Table 7. Pin muxing<sup>(1)</sup>

|              |            | Alternate                       |           |                   | 1/0              | -       | peed <sup>(6)</sup> |             | Pin         |                            |

|--------------|------------|---------------------------------|-----------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin  | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|              | <u>.</u>   |                                 |           | Po                | ort E            |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[64]  | SIUL              |                  |         |                     |             |             |                            |

|              |            | ALT1                            | —         | —                 |                  |         |                     |             |             |                            |

| E[0]         | PCR[64]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 46          | 68          | 80                         |

|              |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|              |            | —                               | AN[21]    | ADC_0             |                  |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[65]  | SIUL              |                  |         |                     |             |             |                            |

|              |            | ALT1                            | —         | —                 |                  |         |                     |             |             |                            |

| E[1]         | PCR[65]    | ALT2                            | —         | —                 | Input Only       | —       |                     | 27          | 39          | 47                         |

|              |            | ALT3                            |           |                   |                  |         |                     |             |             |                            |

|              |            | —                               | AN[4]     | ADC_0             |                  |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[66]  | SIUL              |                  |         |                     |             |             |                            |

| <b>F</b> (0) | DODIOO     | ALT1                            | —         | —                 |                  |         |                     |             | 40          |                            |

| E[2]         | PCR[66]    | ALT2<br>ALT3                    | —         | —                 | Input Only       | —       |                     | 32          | 49          | 57                         |

|              |            | ALT3                            | <br>AN[5] | ADC_0             |                  |         |                     |             |             |                            |

|              |            |                                 |           |                   |                  |         |                     |             |             |                            |

|              |            | ALT0<br>ALT1                    | GPIO[67]  | SIUL              |                  |         |                     |             |             |                            |

| E[3]         | PCR[67]    | ALT1<br>ALT2                    |           | _                 | Input Only       |         | _                   |             | 40          | 48                         |

|              |            | ALT2<br>ALT3                    | _         | _                 |                  |         |                     |             | 40          | -0                         |

|              |            | _                               | AN[6]     | ADC_0             |                  |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[68]  | SIUL              |                  |         |                     |             |             |                            |

|              |            | ALT1                            |           | _                 |                  |         |                     |             |             |                            |

| E[4]         | PCR[68]    | ALT2                            | _         | _                 | Input Only       | _       | _                   |             | 42          | 50                         |

|              |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|              |            | —                               | AN[7]     | ADC_0             |                  |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[69]  | SIUL              |                  |         |                     |             |             |                            |

|              |            | ALT1                            | _         | —                 |                  |         |                     |             |             |                            |

| E[5]         | PCR[69]    | ALT2                            | —         | —                 | Input Only       | —       | —                   |             | 44          | 52                         |

|              |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|              |            | —                               | AN[8]     | ADC_0             |                  |         |                     |             |             |                            |

|              |            | ALT0                            | GPIO[70]  | SIUL              |                  |         |                     |             |             |                            |

|              |            | ALT1                            | —         | _                 |                  |         |                     |             |             |                            |

| E[6]         | PCR[70]    | ALT2                            | —         | -                 | Input Only       | -       | —                   | —           | 46          | 54                         |

|              |            | ALT3                            |           | -                 |                  |         |                     |             |             |                            |

|              |            | —                               | AN[9]     | ADC_0             |                  |         |                     |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             |              | Alternate                       |           |                   | J/O              | -       | peed <sup>(6)</sup> |              | Pin         |                            |  |

|-------------|--------------|---------------------------------|-----------|-------------------|------------------|---------|---------------------|--------------|-------------|----------------------------|--|

| Port<br>pin | PCR<br>No.   | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100  | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |

|             |              | •                               |           | Po                | ort G            |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[96]  | SIUL              | I/O              |         |                     |              |             |                            |  |

|             |              | ALT1                            | F[0]      | FCCU              | 0                |         |                     |              |             |                            |  |

| G[0]        | PCR[96]      | ALT2                            | —         | —                 | —                | Slow    | Medium              | —            | 38          | 46                         |  |

|             |              | ALT3                            | —         | —                 | —                |         |                     |              |             |                            |  |

|             |              | —                               | EIRQ[30]  | SIUL              | I                |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[97]  | SIUL              | I/O              |         |                     |              |             |                            |  |

|             |              | ALT1                            | F[1]      | FCCU              | 0                |         |                     |              |             |                            |  |

| G[1]        | PCR[97]      | ALT2                            | —         | —                 | —                | Slow    | Medium              |              | 141         | 173                        |  |

|             |              | ALT3                            |           | _                 | _                |         |                     |              |             |                            |  |

|             |              |                                 | EIRQ[31]  | SIUL              | I                |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[98]  | SIUL              | I/O              |         |                     |              |             |                            |  |

|             |              | ALT1                            | —         | —                 | —                | Slow    |                     |              |             |                            |  |

| G[2]        | G[2] PCR[98] | ALT2                            | —         | —                 | —                |         | Medium              | _            | 102         | 126                        |  |

|             |              | ALT3                            | —         | —                 |                  |         |                     |              |             |                            |  |

|             |              | —                               | SIN_4     | DSPI_4            | I                |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[99]  | SIUL              | I/O              |         |                     | ledium — 104 |             |                            |  |

| G[3]        | PCR[99]      | ALT1                            |           | —                 | _                | Slow    | w Medium            |              | 104         | 128                        |  |

|             |              | ALT2                            | SOUT_4    | DSPI_4            | 0                |         |                     |              |             |                            |  |

|             |              | ALT3                            |           | —                 | —                |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[100] | SIUL              | I/O              |         |                     |              |             |                            |  |

| G[4]        | PCR[100]     | ALT1                            | —         | —                 | —                | Slow    | Medium              |              | 100         | 124                        |  |

|             |              | ALI2                            | SCK_4     | DSPI_4            | I/O              |         |                     |              |             |                            |  |

|             |              | ALT3                            |           | —                 |                  |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[101] | SIUL              | I/O              |         |                     |              |             |                            |  |

| G[5]        | PCR[101]     | ALT1                            | _         |                   | —                | Slow    | Medium              |              | 85          | 103                        |  |

|             |              | ALIZ                            | CS0_4     | DSPI_4            | I/O              |         |                     |              |             |                            |  |

|             |              | ALT3                            |           |                   |                  |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[102] | SIUL              | I/O              |         |                     |              |             |                            |  |

| G[6]        | PCR[102]     | ALT1                            |           |                   | _                | Slow    | w Medium —          |              | 98          | 122                        |  |

|             |              | ALT2                            | CS1_4     | DSPI_4            | 0                |         |                     |              |             |                            |  |

|             |              | ALT3                            | _         |                   |                  |         |                     |              |             |                            |  |

|             |              | ALT0                            | GPIO[103] | SIUL              | I/O              |         |                     |              |             | 101                        |  |

| G[7]        | PCR[103]     | ALT1                            |           |                   |                  | Slow    | Medium              | ledium —     | 83          |                            |  |

|             |              | ALT2<br>ALT3                    | CS2_4     | DSPI_4            | 0                |         |                     |              |             |                            |  |

|             |              | ALIS                            | _         | _                 | _                |         |                     |              |             |                            |  |

## Table 7. Pin muxing<sup>(1)</sup> (continued)

| Port  | PCR      | Alternate                         |                                 | Peripheral                  | I/O                     | Pad s   | peed <sup>(6)</sup> | Pin         |             |                            |

|-------|----------|-----------------------------------|---------------------------------|-----------------------------|-------------------------|---------|---------------------|-------------|-------------|----------------------------|

| pin   | No.      | function <sup>(2),</sup><br>(3)   | Functions                       | (4)                         | direction<br>(5)        | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

| G[8]  | PCR[104] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[104]<br><br>CS3_4<br>      | SIUL<br>—<br>DSPI_4<br>—    | I/O<br>—<br>0<br>—      | Slow    | Medium              | _           | 81          | 97                         |

| G[9]  | PCR[105] | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[105]<br>—<br>—<br>—<br>RXD | SIUL<br>—<br>—<br>FlexCAN_1 | I/O<br>—<br>—<br>—<br>— | Slow    | Medium              | _           | 79          | 95                         |

| G[10] | PCR[106] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[106]<br>—<br>TXD<br>—      | SIUL<br>—<br>FlexCAN_1<br>— | V<br>0                  | Slow    | Medium              | _           | 77          | 93                         |

| G[11] | PCR[107] | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[107]<br>—<br>—<br>—        | SIUL<br>—<br>—<br>—         | I/O<br>—<br>—           | Slow    | Medium              | _           | 75          | 91                         |

Table 7. Pin muxing<sup>(1)</sup> (continued)

1. This table concerns Enhanced Full-featured version. Please refer to "SPC56xP54x/SPC56xP60x device configuration difference" table for difference between Enhanced Full-featured, Full-featured, and Airbag configuration.

2. ALT0 is the primary (default) function for each port after reset.

3. Alternate functions are chosen by setting the values of the PCR[PA] bitfields inside the SIU module. PCR[PA] = 00 → ALT0; PCR[PA] = 01 → ALT1; PCR[PA] = 10 → ALT2; PCR[PA] = 11 → ALT3. This is intended to select the output functions; to use one of the input-only functions, the PCR[IBE] bit must be written to '1', regardless of the values selected in the PCR[PA] bitfields. For this reason, the value corresponding to an input only function is reported as "—".

4. Module included on the MCU.

5. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMI[PADSELx] bitfields inside the SIUL module.

6. Programmable via the SRC (Slew Rate Control) bits in the respective Pad Configuration Register.

7. LQFP176 available only as development package.

8. Weak pull down during reset.

| Symbol                                       |    | Parameter                                      | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |  |  |  |

|----------------------------------------------|----|------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|--|--|--|

|                                              |    |                                                | —                                     | 4.5                          | 5.5                          |      |  |  |  |

| $V_{DD_HV_REG}$                              | SR | 5.0 V voltage regulator<br>supply voltage      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |  |  |  |

|                                              |    |                                                | —                                     | 4.5                          | 5.5                          |      |  |  |  |

| $V_{DD_HV_AD}$                               | SR | 5.0 V ADC supply and high<br>reference voltage | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> -0.1  | _                            | V    |  |  |  |

| V <sub>SS_HV_AD</sub>                        | SR | ADC ground and low reference voltage           | _                                     | 0                            | 0                            | V    |  |  |  |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR | Internal supply voltage                        | —                                     | _                            | —                            | V    |  |  |  |

| $V_{SS_{LV}_{REGCOR}}^{(3)}$                 | SR | Internal reference voltage                     | —                                     | 0                            | 0                            | V    |  |  |  |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR | Internal supply voltage                        | —                                     | —                            | —                            | V    |  |  |  |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR | Internal reference voltage                     | —                                     | 0                            | 0                            | V    |  |  |  |

| T <sub>A</sub>                               | SR | Ambient temperature under bias                 | _                                     | -40                          | 125                          | °C   |  |  |  |

| Table 10. Recommended | operating conditions | (5.0 V) | (continued) |

|-----------------------|----------------------|---------|-------------|

|                       | operating containers | (0.0.0) | (001101000) |

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

| Symbol                                |    | Parameter                                               | Conditions                            | Min                         | Max <sup>(1)</sup>           | Unit |

|---------------------------------------|----|---------------------------------------------------------|---------------------------------------|-----------------------------|------------------------------|------|

| V <sub>SS_HV</sub>                    | SR | Digital ground                                          | —                                     | 0                           | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 3.3 V input/output supply voltage                       | _                                     | 3.0                         | 3.6                          | V    |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                             | —                                     | 0                           | 0                            | V    |

|                                       |    | 2.2.V code and date flach                               | —                                     | 3.0                         | 3.6                          |      |

| V <sub>DD_HV_FL</sub>                 | SR | 3.3 V code and data flash<br>memory supply voltage      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_FL</sub>                 | SR | Code and data flash<br>memory ground                    | _                                     | 0                           | 0                            | V    |

|                                       |    | 3.3 V crystal oscillator                                | —                                     | 3.0                         | 3.6                          |      |

|                                       |    | amplifier supply voltage                                | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_OSC</sub>                | SR | 3.3 V crystal oscillator<br>amplifier reference voltage | _                                     | 0                           | 0                            | V    |

#### Table 11. Recommended operating conditions (3.3 V)

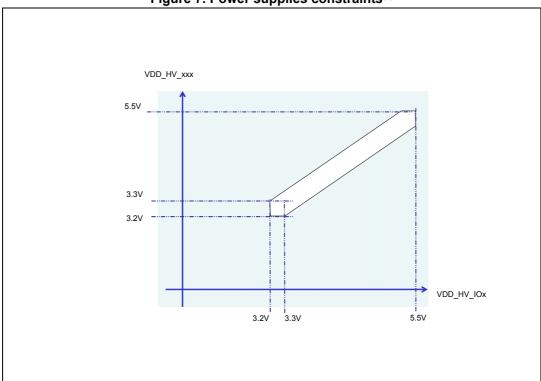

Figure 7. Power supplies constraints<sup>(f)</sup>

The SPC56xP54x/SPC56xP60x supply architecture provides an ADC supply that is managed independently of standard  $V_{DD_HV}$  supply. *Figure 8* shows the constraints of the ADC power supply.

f. IO AC and DC characteristics are guaranteed only in the range 3.0 V–3.6 V when PAD3V5V is low, and in the range 4.5 V–5.5 V when PAD3V5V is high.

## 3.11.2 DC electrical characteristics (3.3 V)

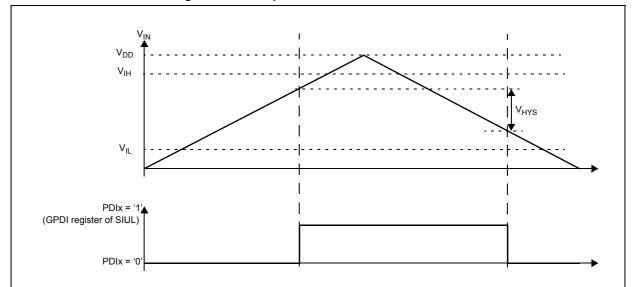

*Table 22* gives the DC electrical characteristics at 3.3 V ( $3.0 \text{ V} < \text{V}_{\text{DD}_{\text{HV}_{\text{IOx}}}} < 3.6 \text{ V}$ , NVUSRO[PAD3V5V]=1) as described in *Figure 14*.

#### Figure 14. I/O input DC electrical characteristics definition

| Symbo               | I                            | Parameter                            | Conditions                        | Min                          | Мах                         | Unit |

|---------------------|------------------------------|--------------------------------------|-----------------------------------|------------------------------|-----------------------------|------|

| V <sub>IL</sub>     | D Minimum low level input vo |                                      | —                                 | -0.1 <sup>(2)</sup>          | _                           | V    |

| V <sub>IL</sub>     | Ρ                            | Maximum low level input voltage      | —                                 | —                            | 0.35 V <sub>DD_HV_IOx</sub> | V    |

| V <sub>IH</sub>     | Ρ                            | Minimum high level input voltage     | —                                 | 0.65 V <sub>DD_HV_IOx</sub>  | —                           | V    |

| V <sub>IH</sub>     | D                            | Maximum high level input voltage     | —                                 | —                            | $V_{DD_HV_IOx} + 0.1^{(2)}$ | V    |

| V <sub>HYS</sub>    | Т                            | Schmitt trigger hysteresis           | —                                 | 0.1 V <sub>DD_HV_IOx</sub>   | —                           | V    |

| V <sub>OL_S</sub>   | Ρ                            | Slow, low level output voltage       | I <sub>OL</sub> = 1.5 mA          | —                            | 0.5                         | V    |

| V <sub>OH_S</sub>   | Ρ                            | Slow, high level output voltage      | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_M</sub>   | Ρ                            | Medium, low level output voltage     | I <sub>OL</sub> = 2 mA            | —                            | 0.5                         | V    |

| V <sub>OH_M</sub>   | Ρ                            | Medium, high level output voltage    | I <sub>OH</sub> = -2 mA           | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_F</sub>   | Ρ                            | Fast, high level output voltage      | I <sub>OL</sub> = 11 mA           | —                            | 0.5                         | V    |

| V <sub>OH_F</sub>   | Ρ                            | Fast, high level output voltage      | I <sub>OH</sub> = –11 mA          | $V_{DD_HV_IOx} - 0.8$        | —                           | V    |

| V <sub>OL_SYM</sub> | Ρ                            | Symmetric, high level output voltage | I <sub>OL</sub> = 1.5 mA          | _                            | 0.5                         | V    |

| V <sub>OH_SYM</sub> | Ρ                            | Symmetric, high level output voltage | I <sub>OH</sub> = –1.5 mA         | V <sub>DD_HV_IOx</sub> - 0.8 | _                           | V    |

| 1                   | Р                            | Equivalent pull-up current           | V <sub>IN</sub> = V <sub>IL</sub> | -130                         | —                           |      |

| I <sub>PU</sub>     | r.                           |                                      | V <sub>IN</sub> = V <sub>IH</sub> | —                            | -10                         | μA   |

| Ш        |

|----------|

| ē        |

| <u>₽</u> |

| <u>-</u> |

| <u>હ</u> |

| ົ        |

| ž        |

| ar       |

| a        |

| Ť        |

| ž.       |

| ş        |

| ត        |

| "        |

DocID18340 Rev 6

70/105

| Symbol                      |   |                                                  |                                                                                                                                                                                                                         |                                                                                                                                                                      | Value                             |                                   |        |

|-----------------------------|---|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--------|

|                             |   | Parameter                                        | Conditions                                                                                                                                                                                                              |                                                                                                                                                                      | Тур                               | Max                               | - Unit |

| I <sub>DD_HV</sub> (CAN)    | т | CAN (FlexCAN)<br>supply current on<br>VDD_HV_REG | 500 Kbyte/s                                                                                                                                                                                                             | Total (static + dynamic)<br>consumption:<br>– FlexCAN in loop-back mode<br>– XTAL@ 8 MHz used as CAN<br>engine clock source<br>– Message sending period is 580<br>μs | 21.6 * f <sub>periph</sub>        | 28.1* f <sub>periph</sub>         |        |

| I <sub>DD_HV</sub> (SCI)    | т | SCI (LINFlex) supply<br>current on<br>VDD_HV_REG | Total (static + dynamic) consumption:<br>– LIN mode<br>– Baudrate: 115.2 Kbyte/s<br>Ballast dynamic consumption (continuous<br>communication):<br>– Baudrate: 2 Mbit/s<br>– Transmission every 8 μs<br>– Frame: 16 bits |                                                                                                                                                                      | 10.8 * f <sub>periph</sub>        | 14.1 * f <sub>periph</sub>        | μА     |

| I <sub>DD_HV(SPI)</sub>     | т | SPI (DSPI) supply<br>current on<br>VDD_HV_REG    |                                                                                                                                                                                                                         |                                                                                                                                                                      | 4.8 * f <sub>periph</sub>         | 6.3 * f <sub>periph</sub>         |        |

| I <sub>DD_HV(ADC)</sub>     | т | ADC supply current<br>on VDD_HV_REG              | VDD = 5.5 V                                                                                                                                                                                                             | Ballast dynamic consumption (continuous conversion)                                                                                                                  | 120 * f <sub>periph</sub>         | 156 * f <sub>periph</sub>         |        |

| DD_HV_ADC(ADC)              | т | ADC supply current<br>on VDD_HV_ADC              | VDD = 5.5 V                                                                                                                                                                                                             | Analog dynamic consumption (continuous conversion)                                                                                                                   | 0.005 * f <sub>periph</sub> + 2.8 | 0.007 * f <sub>periph</sub> + 3.4 | mA     |

| I <sub>DD_HV</sub> (eTimer) | т | eTimer supply current<br>on VDD_HV_REG           | PWM signals generation<br>on all 1 channel @10kHz                                                                                                                                                                       | Dynamic consumption does not change varying the frequency                                                                                                            | 1.8                               | 2.4                               | mA     |

| I <sub>DD_HV(FlexRay)</sub> | т | FlexRay supply<br>current on<br>VDD_HV_REG       | Static consumption                                                                                                                                                                                                      |                                                                                                                                                                      | 4.2 * f <sub>periph</sub>         | 5.5 * f <sub>periph</sub>         | μA     |

1. Operating conditions:  $f_{periph} = 8 \text{ MHz}$  to 64 MHz

| Symbol              |    | с | Parameter                              | Condit                                     | Conditions <sup>(1)</sup> |     | Value |     |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

|---------------------|----|---|----------------------------------------|--------------------------------------------|---------------------------|-----|-------|-----|------|--|--|--|--|--|--|--|--|--|--|--------------------------------|-----------------------------------------------|---|---|----|

| Symbol              |    | C | Farameter                              | Conucions, 7                               |                           | Min | Тур   | Мах | Unit |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

|                     |    |   |                                        | C <sub>L</sub> = 25 pF, 40 MHz             |                           | _   | _     | 22  |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

|                     |    |   |                                        | C <sub>L</sub> = 25 pF, 64 MHz             |                           |     |       | 33  | mA   |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

| 1                   | сс | D | Root medium square                     | C <sub>L</sub> = 100 pF, 40 MHz            |                           |     |       | 56  |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

| IRMSFST             | 00 |   | configuration                          | C <sub>L</sub> = 25 pF, 40 MHz             |                           | _   | _     | 14  |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

|                     |    |   |                                        |                                            |                           |     |       |     |      |  |  |  |  |  |  |  |  |  |  | C <sub>L</sub> = 25 pF, 64 MHz | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _ | _ | 20 |

|                     |    |   |                                        | C <sub>L</sub> = 100 pF, 40 MHz            |                           | _   | _     | 35  |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

| 1                   | 00 |   | Sum of all the static                  | V <sub>DD</sub> = 5.0 V ± 10%, P           | AD3V5V = 0                | _   | _     | 70  |      |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

| I <sub>AVGSEG</sub> | SR | ט | I/O current within a<br>supply segment | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |                           | _   | _     | 65  | mA   |  |  |  |  |  |  |  |  |  |  |                                |                                               |   |   |    |

#### Table 26. I/O consumption (continued)

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

2. Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

# 3.12 Main oscillator electrical characteristics

The SPC56xP54x/SPC56xP60x provides an oscillator/resonator driver.

| Symbol           |                         | Parameter                          | Min | Max | Unit |

|------------------|-------------------------|------------------------------------|-----|-----|------|

|                  |                         |                                    |     | Шал |      |

| f <sub>OSC</sub> | SR Oscillator frequency |                                    | 4   | 40  | MHz  |

| 9 <sub>m</sub>   | Ρ                       | Transconductance                   | 6.5 | 25  | mA/V |

| V <sub>OSC</sub> | Т                       | Oscillation amplitude on EXTAL pin | 1   | _   | V    |

| toscsu           | Т                       | Start-up time <sup>(1),(2)</sup>   | 8   | —   | ms   |

#### Table 27. Main oscillator electrical characteristics (5.0 V, NVUSRO[PAD3V5V]=0)

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of EXTAL.

| Symbol                                   |                                                       | Parameter            |   | Мах | Unit |

|------------------------------------------|-------------------------------------------------------|----------------------|---|-----|------|

| f <sub>OSC</sub> SR Oscillator frequency |                                                       | Oscillator frequency | 4 | 40  | MHz  |

| 9 <sub>m</sub>                           | P Transconductance                                    |                      | 4 | 20  | mA/V |

| V <sub>OSC</sub>                         | T Oscillation amplitude on EXTAL pin                  |                      | 1 | _   | V    |

| t <sub>oscsu</sub>                       | t <sub>OSCSU</sub> T Start-up time <sup>(1),(2)</sup> |                      | 8 |     | ms   |

1. The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of EXTAL.

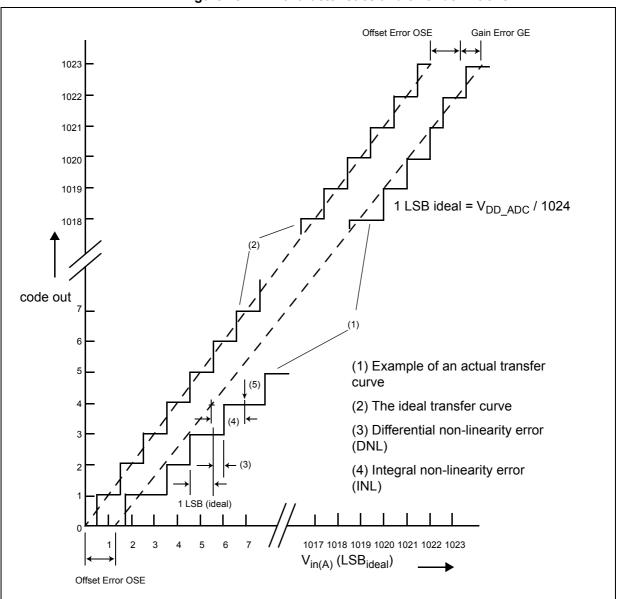

Figure 15. ADC characteristics and error definitions

### 3.15.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high-frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuate the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

DocID18340 Rev 6

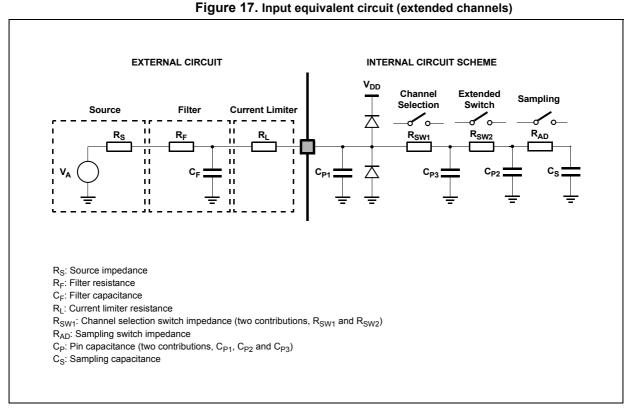

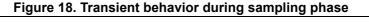

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_{F}$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 16*): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

DocID18340 Rev 6

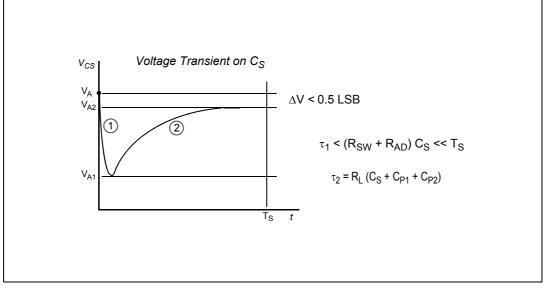

$C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_F C_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing.

Figure 19. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### **Equation 12**

$$C_F > 2048 \times C_S$$

57

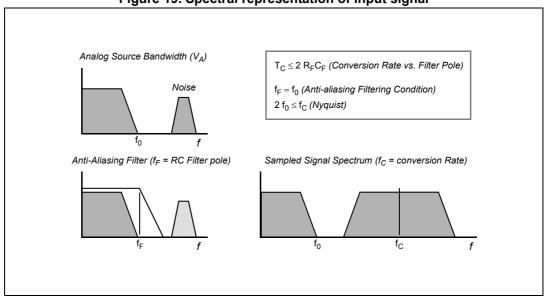

g. The output drive provided is open drain and hence must be terminated by an external resistor of value 1 k $\Omega$ .

## 3.18.5 DSPI timing

| No. | Sym               | bol      | С        | Parameter                   | Conditions                            | Min                    | Max                  | Unit                        |    |   |     |

|-----|-------------------|----------|----------|-----------------------------|---------------------------------------|------------------------|----------------------|-----------------------------|----|---|-----|

| 4   |                   | ~~~      | <b>_</b> |                             | Master (MTFE = 0)                     | 60                     | 60 —                 |                             |    |   |     |

| 1   | t <sub>SCK</sub>  | CC       | D        | DSPI cycle time             | Slave (MTFE = 0)                      | 60                     | _                    | ns                          |    |   |     |

| 2   | t <sub>CSC</sub>  | СС       | D        | PCS to SCK delay            |                                       | 16                     | _                    | ns                          |    |   |     |

| 3   | t <sub>ASC</sub>  | СС       | D        | After SCK delay             | —                                     | 26                     |                      | ns                          |    |   |     |

| 4   | t <sub>SDC</sub>  | СС       | D        | SCK duty cycle              | —                                     | 0.4 × t <sub>SCK</sub> | $0.6 \times t_{SCK}$ | ns                          |    |   |     |

| 5   | t <sub>A</sub>    | СС       | D        | Slave access time           | SS active to SOUT valid               | —                      | 30                   | ns                          |    |   |     |

| 6   | t <sub>DIS</sub>  | сс       | D        | Slave SOUT disable time     | SS inactive to SOUT High-Z or invalid | _                      | 16                   | ns                          |    |   |     |

| 7   | t <sub>PCSC</sub> | СС       | D        | PCSx to PCSS time           | —                                     | 13                     | _                    | ns                          |    |   |     |

| 8   | t <sub>PASC</sub> | СС       | D        | PCSS to PCSx time           | _                                     | 13                     | _                    | ns                          |    |   |     |

|     |                   |          |          |                             | Master (MTFE = 0)                     | 35                     | _                    |                             |    |   |     |

| 9   | +.                | сс       | П        | Data setup time for inputs  | Slave                                 | 4                      |                      | ns                          |    |   |     |

| 9   | t <sub>SUI</sub>  | 00       |          |                             |                                       | , ,                    |                      | Master (MTFE = 1, CPHA = 0) | 35 | _ | 110 |

|     |                   |          |          |                             | Master (MTFE = 1, CPHA = 1)           | 35                     |                      |                             |    |   |     |

|     |                   |          |          |                             | Master (MTFE = 0)                     | -5                     |                      |                             |    |   |     |

| 10  | ÷                 | сс       |          | Data hold time for inputs   | Slave                                 | 4                      |                      |                             |    |   |     |

| 10  | t <sub>HI</sub>   | 00       |          |                             | Master (MTFE = 1, CPHA = 0)           | 11                     |                      | ns                          |    |   |     |

|     |                   |          |          |                             | Master (MTFE = 1, CPHA = 1)           | -5                     |                      |                             |    |   |     |

|     |                   |          |          |                             | Master (MTFE = 0)                     | —                      | 12                   |                             |    |   |     |

| 11  |                   | <u> </u> | П        | Data valid (after SCK edge) | Slave                                 |                        | 36                   | ne                          |    |   |     |

|     | t <sub>SUO</sub>  |          |          |                             | Master (MTFE = 1, CPHA = 0)           | —                      | 12                   | ns                          |    |   |     |

|     |                   |          |          |                             | Master (MTFE = 1, CPHA = 1)           | _                      | 12                   |                             |    |   |     |

Table 41. DSPI timing<sup>(1)</sup>

| Querra ha ch       |        | mm     |        | inches <sup>(1)</sup> |        |        |  |

|--------------------|--------|--------|--------|-----------------------|--------|--------|--|

| Symbol             | Min    | Тур    | Мах    | Min                   | Тур    | Мах    |  |

| А                  | —      | —      | 1.600  | —                     | —      | 0.0630 |  |

| A1                 | 0.050  | —      | 0.150  | 0.0020                | —      | 0.0059 |  |

| A2                 | 1.350  | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b                  | 0.170  | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| с                  | 0.090  | —      | 0.200  | 0.0035                | —      | 0.0079 |  |

| D                  | 21.800 | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| D1                 | 19.800 | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| D3                 | —      | 17.500 | _      | _                     | 0.6890 | _      |  |

| E                  | 21.800 | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| E1                 | 19.800 | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| E3                 | —      | 17.500 | _      | _                     | 0.6890 | _      |  |

| е                  | —      | 0.500  | —      | —                     | 0.0197 | —      |  |

| L                  | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1                 | —      | 1.000  | —      | —                     | 0.0394 | —      |  |

| k                  | 0.0 °  | 3.5 °  | 7.0°   | 3.5 °                 | 0.0 °  | 7.0 °  |  |

| ccc <sup>(2)</sup> |        | 0.080  |        |                       | 0.0031 | •      |  |

| Table 42. LQFP144 n | nechanical data |

|---------------------|-----------------|

|---------------------|-----------------|