#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 80K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56ap60l5befay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SPC56xP54x/SPC56xP60x is present on the market in two different options enabling different features: Full-featured, and Airbag configuration. *Table 3* shows the main differences between the two versions.

### Table 3. SPC56xP54x/SPC56xP60x device configuration difference

| Feature                                             | Enhanced<br>Full-featured | Full-featured | Airbag |

|-----------------------------------------------------|---------------------------|---------------|--------|

| FlexCAN (controller area network)                   | 3                         | 2             | 2      |

| CTU (cross triggering unit)                         | Ye                        | No            |        |

| FlexRay                                             | Yes (64 mes               | No            |        |

| DSPI (deserial serial peripheral interface) modules | Į                         | 4             |        |

| CRC (cyclic redundancy check) unit                  | 2                         | 2             | 1      |

# 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC56xP54x/SPC56xP60x MCU. *Table 4* summarizes the functions of the blocks.

| Block                                         | Function                                                                                                                                                                                                                                |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral bridge (PBRIDGE)                   | Is the interface between the system bus and on-chip peripherals                                                                                                                                                                         |

| Periodic interrupt timer (PIT)                | Produces periodic interrupts and triggers                                                                                                                                                                                               |

| Power control unit (MC_PCU)                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                           |

| Semaphore unit (SEMA4)                        | Provides the hardware support needed in multi-core systems for implementing semaphores and provide a simple mechanism to achieve lock/unlock operations via a single write access                                                       |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                             |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration                |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable        |

| System timer module (STM)                     | Provides a set of output compare events to support $AUTOSAR^{(1)}$ and operating system tasks                                                                                                                                           |

| System watchdog timer (SWT)                   | Provides protection from runaway code                                                                                                                                                                                                   |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                                                |

1. AUTOSAR: AUTomotive Open System ARchitecture (see autosar.org web site).

# 1.5 Feature details

### 1.5.1 High performance e200z0h core processor

The e200z0h Power Architecture core provides the following features:

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16-bit and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit

- 1-cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non maskable Interrupt support

### 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between six master ports and six slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.

The crossbar allows for two concurrent transactions to occur from any master port to any slave port; but one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grant it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions. Requesting masters are treated with equal priority and will be granted access to a slave port in round-robin fashion, based upon the ID of the last master to be granted access.

|                         | Supply                                                                                                                                             |             |             |                            |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------|--|--|

| Symbol                  | Description                                                                                                                                        | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(1)</sup> |  |  |

| V <sub>SS_LV_COR0</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR0}$ pin.         | 11          | 17          | 25                         |  |  |

| V <sub>DD_LV_COR1</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{\rm SS\_LV\_COR1}$ pin. | 65          | 93          | 117                        |  |  |

| V <sub>SS_LV_COR1</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR1}$ pin.         | 66          | 94          | 118                        |  |  |

| V <sub>DD_LV_COR2</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR2}$ pin.     | 92          | 131         | 155                        |  |  |

| V <sub>SS_LV_COR2</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR\ 2}$ pin.       | 93          | 132         | 156                        |  |  |

| V <sub>DD_LV_COR3</sub> | 1.2 V Decoupling pins for core logic supply. Decoupling capacitor must be connected between these pins and the nearest $V_{SS\_LV\_COR3}$ pin.     | 25          | 36          | 44                         |  |  |

| V <sub>SS_LV_COR3</sub> | 1.2 V Decoupling pins for core logic GND. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV\_COR~3}$ pin.        | 24          | 35          | 43                         |  |  |

| Table | 5  | Supply | v nins  | (continued) |

|-------|----|--------|---------|-------------|

| Table | э. | Suppi  | y pilis | (continueu) |

1. LQFP176 available only as development package.

2. See datasheet Voltage Regulator Electrical Characteristics section for more details.

### 2.2.2 System pins

*Table 6* and *Table 7* contain information on pin functions for the SPC56xP54x/SPC56xP60x devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective Pad Configuration Register (PCR) values.

|        |                                  |                | Pad Sp | beed <sup>(1)</sup> | Pin         |             |                            |

|--------|----------------------------------|----------------|--------|---------------------|-------------|-------------|----------------------------|

| Symbol | Description                      | Direction      | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |

|        | Dedicated                        | d pins         |        |                     |             |             |                            |

| MDO0   | Nexus Message Data Output—line 0 | Output<br>Only | Fa     | st                  | _           | 9           | 17                         |

| MDO4   | Nexus Message Data Output—line 4 | Output<br>Only | Fast   |                     | _           | _           | 7                          |

### Table 6. System pins

| Table 6. System pins (continued) |                                                                                                                                                                                      |                   |        |                     |             |             |                            |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|---------------------|-------------|-------------|----------------------------|

|                                  |                                                                                                                                                                                      |                   | Pad Sp | beed <sup>(1)</sup> | Pin         |             |                            |

| Symbol                           | Description                                                                                                                                                                          | Direction         | SRC=0  | SRC=1               | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(2)</sup> |

| MDO5                             | Nexus Message Data Output—line 5                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 8                          |

| MDO6                             | Nexus Message Data Output—line 6                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 9                          |

| MDO7                             | Nexus Message Data Output—line 7                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 110                        |

| MDO8                             | Nexus Message Data Output—line 8                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 111                        |

| MDO9                             | Nexus Message Data Output—line 9                                                                                                                                                     | Output<br>Only    | Fa     | ist                 | _           | _           | 112                        |

| MDO10                            | Nexus Message Data Output—line 10                                                                                                                                                    | Output<br>Only    | Fa     | ist                 | _           | _           | 166                        |

| MDO11                            | Nexus Message Data Output—line 11         Output<br>Only         Fast                                                                                                                |                   |        |                     | _           | _           | 171                        |

| RDY                              | Nexus ready output                                                                                                                                                                   | Output<br>Only    | _      | _                   | _           | _           | 172                        |

| NMI                              | Non-Maskable Interrupt                                                                                                                                                               | Input Only        | _      | _                   | 1           | 1           | 1                          |

| XTAL                             | Analog output of the oscillator amplifier<br>circuit. Needs to be grounded if oscillator is<br>used in bypass mode.                                                                  | _                 | _      | _                   | 18          | 29          | 37                         |

| EXTAL                            | Analog input of the oscillator amplifier<br>circuit, when the oscillator is not in bypass<br>mode.<br>Analog input for the clock generator when<br>the oscillator is in bypass mode. | _                 | _      |                     | 19          | 30          | 38                         |

| TMS <sup>(3)</sup>               | JTAG state machine control                                                                                                                                                           | Input Only        |        | _                   | 59          | 87          | 105                        |

| TCK <sup>(3)</sup>               | JTAG clock                                                                                                                                                                           | Input Only        | —      | _                   | 60          | 88          | 106                        |

| TDI <sup>(3)</sup>               | JTAG data input                                                                                                                                                                      | Input Only        | —      | —                   | 58          | 86          | 104                        |

| TDO <sup>(3)</sup>               | JTAG data output                                                                                                                                                                     | Output<br>Only    | _      | _                   | 61          | 89          | 107                        |

|                                  | Reset                                                                                                                                                                                | pin               |        |                     |             |             |                            |

| RESET <sup>(4)</sup>             | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                                            | Bidirection<br>al | Medium | _                   | 20          | 31          | 39                         |

|                                  | Test p                                                                                                                                                                               | in                |        |                     |             |             |                            |

| V <sub>PP TEST</sub>             | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | —                 | _      | _                   | 74          | 107         | 131                        |

| V <sub>REG_BYPASS</sub>          | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                         | _                 | _      |                     | 34          | 51          | 59                         |

|                                  |                                                                                                                                                                                      |                   |        |                     |             |             |                            |

### Table 6. System pins (continued)

1. SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

| Table 7. Pin muxing <sup>(1)</sup> (continued) |         |                                 |           |             |                  |         |                     |             |             |                            |  |

|------------------------------------------------|---------|---------------------------------|-----------|-------------|------------------|---------|---------------------|-------------|-------------|----------------------------|--|

| Port                                           | PCR     | Alternate                       |           | Peripheral  | I/O              | Pad s   | peed <sup>(6)</sup> | Pin         |             |                            |  |

| pin                                            | No.     | function <sup>(2),</sup><br>(3) | Functions | (4)         | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |

|                                                |         | ALT0                            | GPIO[9]   | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | CS1_2     | DSPI_2      | 0                |         |                     |             |             |                            |  |

| A[9]                                           | PCR[9]  | ALT2                            | —         | —           | —                | Slow    | Medium              | 94          | 134         | 158                        |  |

|                                                |         | ALT3                            | —         | —           | —                |         |                     |             |             |                            |  |

|                                                |         | —                               | SIN_4     | DSPI_4      |                  |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPIO[10]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | CS0_2     | DSPI_2      | I/O              |         |                     |             |             |                            |  |

| A[10]                                          | PCR[10] | ALT2                            | —         | —           | —                | Slow    | Medium              | 81          | 118         | 142                        |  |

|                                                |         | ALT3                            | —         | —           | —                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[9]   | SIUL        | Ι                |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPI0[11]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | SCK_2     | DSPI_2      | I/O              |         |                     |             |             |                            |  |

| A[11]                                          | PCR[11] | ALT2                            | —         | —           | —                | Slow    | Medium              | 82          | 120         | 144                        |  |

|                                                |         | ALT3                            | —         | —           | —                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[10]  | SIUL        | I                |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPIO[12]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | SOUT_2    | DSPI_2      | 0                |         |                     |             |             |                            |  |

| A[12]                                          | PCR[12] | ALT2                            | _         | _           | —                | Slow    | Medium              | 83          | 122         | 146                        |  |

|                                                |         | ALT3                            | —         | —           | —                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[11]  | SIUL        | I                |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPIO[13]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | CS4_1     | DSPI_1      | 0                |         |                     |             |             |                            |  |

| A [4 0]                                        | DODIAN  | ALT2                            | _         | _           | —                | 0       | Mar allowed         | 05          | 400         | 100                        |  |

| A[13]                                          | PCR[13] | ALT3                            | —         | —           | —                | Slow    | Medium              | 95          | 136         | 160                        |  |

|                                                |         | —                               | SIN_2     | DSPI_2      | I                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[12]  | SIUL        | I                |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPIO[14]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | TXD       | Safety Port | 0                |         |                     |             |             |                            |  |

| A[14]                                          | PCR[14] | ALT2                            | ETC[4]    | eTimer_1    | I/O              | Slow    | Medium              | 99          | 143         | 175                        |  |

|                                                |         | ALT3                            | CS5_1     | DSPI_1      | 0                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[13]  | SIUL        | I                |         |                     |             |             |                            |  |

|                                                |         | ALT0                            | GPIO[15]  | SIUL        | I/O              |         |                     |             |             |                            |  |

|                                                |         | ALT1                            | CS6_1     | DSPI_1      | 0                |         |                     |             |             |                            |  |

| A 1 4 53                                       |         | ALT2                            | ETC[5]    | eTimer_1    | I/O              | 01      | Mart                | 400         | 144         | 470                        |  |

| A[15]                                          | PCR[15] | ALT3                            | _         |             | —                | Slow    | Medium              | ium 100     |             | 176                        |  |

|                                                |         | —                               | RXD       | Safety Port | I                |         |                     |             |             |                            |  |

|                                                |         | —                               | EIRQ[14]  | SIUL        | I                |         |                     |             |             |                            |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|       | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                   |                                          |                                         |                         |         |                      |             |             |                            |  |

|-------|------------------------------------------------|-----------------------------------|------------------------------------------|-----------------------------------------|-------------------------|---------|----------------------|-------------|-------------|----------------------------|--|

| Port  | PCR                                            | Alternate                         |                                          | Devinhenel                              | I/O                     | Pad s   | speed <sup>(6)</sup> | Pin         |             |                            |  |

| pin   | No.                                            | function <sup>(2),</sup><br>(3)   | Functions                                | Peripheral<br>(4)                       | direction<br>(5)        | SRC = 0 | SRC = 1              | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |  |

| D[7]  | PCR[55]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[55]<br>CS3_1<br>—<br>CS4_0<br>SIN_3 | SIUL<br>DSPI_1<br>—<br>DSPI_0<br>DSPI_3 | I/O<br>O<br>—<br>O<br>I | Slow    | Medium               | 26          | 37          | 45                         |  |

| D[8]  | PCR[56]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[56]<br>CS2_1<br>RDY<br>CS5_0        | SIUL<br>DSPI_1<br>nexus_0<br>DSPI_0     | I/O<br>O<br>O           | Slow    | Medium               | 21          | 32          | 40                         |  |

| D[9]  | PCR[57]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>—<br>TXD<br>CS6_1            | SIUL<br>—<br>LINFlex_1<br>DSPI_1        | I/O<br>  0<br>0         | Slow    | Medium               | 15          | 26          | 34                         |  |

| D[10] | PCR[58]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>—<br>CS0_3<br>—              | SIUL<br>—<br>DSPI_3<br>—                | I/O<br>—<br>I/O<br>—    | Slow    | Medium               | 53          | 76          | 92                         |  |

| D[11] | PCR[59]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>—<br>CS1_3<br>SCK_3          | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>0<br>I/O    | Slow    | Medium               | 54          | 78          | 94                         |  |

| D[12] | PCR[60]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>—<br>CS7_1<br>RXD            | SIUL<br>—<br>—<br>DSPI_1<br>LINFlex_1   | I/O<br>—<br>—<br>0<br>I | Slow    | Medium               | 70          | 99          | 123                        |  |

| D[13] | PCR[61]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>—<br>CS2_3<br>SOUT_3         | SIUL<br>—<br>DSPI_3<br>DSPI_3           | I/O<br>—<br>O<br>O      | Slow    | Medium               | 67          | 95          | 119                        |  |

| D[14] | PCR[62]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[62]<br>—<br>CS3_3<br>—<br>SIN_3     | SIUL<br>—<br>DSPI_3<br>—<br>DSPI_3      | I/O<br>—<br>—<br>—<br>— | Slow    | Medium               | 73          | 105         | 129                        |  |

| D[15] | PCR[63]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[63]<br>—<br>—<br>—<br>AN[20]        | SIUL<br>—<br>—<br>—<br>ADC_0            | Input Only              | _       | _                    | 41          | 58          | 66                         |  |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Symbol              |   | Parameter                                                                 | Conditions            | Typical value | Unit |  |

|---------------------|---|---------------------------------------------------------------------------|-----------------------|---------------|------|--|

| $R_{	hetaJA}$       | D | Thermal resistance junction-to-ambient, natural convection <sup>(1)</sup> | Single layer board—1s | 47.3          | °C/W |  |

| ιν <sub>θ</sub> JΑ  | D | natural convection <sup>(1)</sup>                                         | Four layer board—2s2p | 35.6          | °C/W |  |

| $R_{	hetaJB}$       | D | Thermal resistance junction-to-board <sup>(2)</sup>                       | Four layer board—2s2p | 19.1          | °C/W |  |

| R <sub>0JCtop</sub> | D | Thermal resistance junction-to-case (top) <sup>(3)</sup>                  | Single layer board—1s | 9.1           | °C/W |  |

| $\Psi_{JB}$         | D | Junction-to-board, natural convection <sup>(4)</sup>                      | Operating conditions  | 19.1          | °C/W |  |

| $\Psi_{JC}$         | D | Junction-to-case, natural convection <sup>(5)</sup>                       | Operating conditions  | 1.1           | °C/W |  |

Table 13. Thermal characteristics for 100-pin LQFP

1. Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

2. Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

4. Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

5. Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

### 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

Equation 1  $T_J = T_A + (R_{\theta JA} \times P_D)$

where:

$T_A$  = ambient temperature for the package (<sup>o</sup>C)

$R_{\theta JA}$ = junction to ambient thermal resistance (<sup>o</sup>C/W)

$P_D$ = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

## Equation 2 $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta,JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta,IC}$ = junction to case thermal resistance (°C/W)

$R_{\theta CA}$ = case to ambient thermal resistance (°C/W)

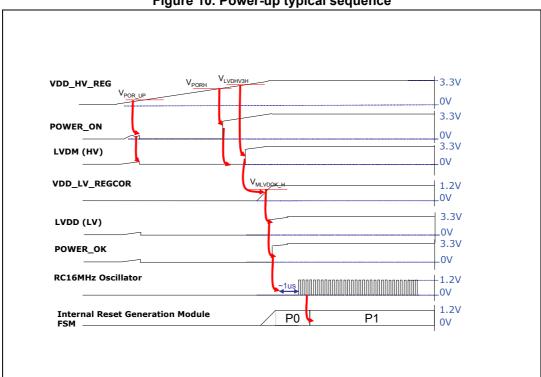

Figure 10. Power-up typical sequence

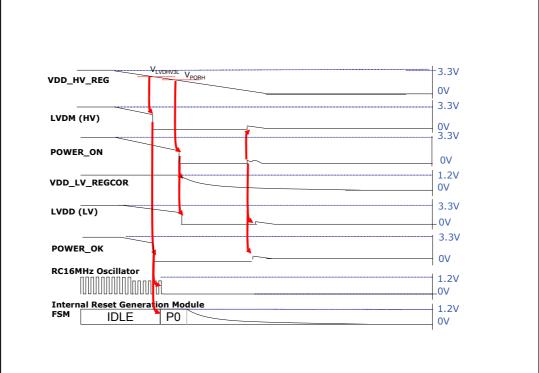

Figure 12. Brown-out typical sequence

#### 3.10 **NVUSRO** register

Portions of the device configuration, such as high voltage supply, and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options register (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

#### 3.10.1 NVUSRO[PAD3V5V] field description

Table 19 shows how NVUSRO[PAD3V5V] controls the device configuration.

|   | Value <sup>(2)</sup> | Description                  |  |

|---|----------------------|------------------------------|--|

| I | 0                    | High voltage supply is 5.0 V |  |

|   | 1                    | High voltage supply is 3.3 V |  |

Table 19. PAD3V5V field description<sup>(1)</sup>

1. See the device reference manual for more information on the NVUSRO register.

2. '1' is delivery value. It is part of shadow Flash, thus programmable by customer.

The DC electrical characteristics are dependent on the PAD3V5V bit value.

| Electrical      |

|-----------------|

| characteristics |

DocID18340 Rev 6

70/105

| Symbol                                                                        |   | Demonstern                                       |                                                                                                                         |                                                                                                                                                                      | Value                             |                                   |    |  |

|-------------------------------------------------------------------------------|---|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|----|--|

| Symbol                                                                        |   | Parameter                                        |                                                                                                                         | Conditions                                                                                                                                                           | Тур                               | Мах                               |    |  |

| I <sub>DD_HV</sub> (CAN)                                                      | т | CAN (FlexCAN)<br>supply current on<br>VDD_HV_REG | 500 Kbyte/s                                                                                                             | Total (static + dynamic)<br>consumption:<br>– FlexCAN in loop-back mode<br>– XTAL@ 8 MHz used as CAN<br>engine clock source<br>– Message sending period is 580<br>μs | 21.6 * f <sub>periph</sub>        | 28.1* f <sub>periph</sub>         |    |  |

| I <sub>DD HV(SCI)</sub> T current on                                          |   | SCI (LINFlex) supply<br>current on<br>VDD_HV_REG | Total (static + dynamic) consumption:<br>– LIN mode<br>– Baudrate: 115.2 Kbyte/s                                        |                                                                                                                                                                      | 10.8 * f <sub>periph</sub>        | 14.1 * f <sub>periph</sub>        | μA |  |

| I <sub>DD_HV(SPI)</sub>                                                       |   | SPI (DSPI) supply<br>current on<br>VDD_HV_REG    | Ballast dynamic consumption<br>communication):<br>– Baudrate: 2 Mbit/s<br>– Transmission every 8 µs<br>– Frame: 16 bits | on (continuous                                                                                                                                                       | 4.8 * f <sub>periph</sub>         | 6.3 * f <sub>periph</sub>         |    |  |

| I <sub>DD_HV(ADC)</sub>                                                       | т | ADC supply current<br>on VDD_HV_REG              | VDD = 5.5 V                                                                                                             | Ballast dynamic consumption (continuous conversion)                                                                                                                  | 120 * f <sub>periph</sub>         | 156 * f <sub>periph</sub>         |    |  |

| DD_HV_ADC(ADC)                                                                | Т | ADC supply current<br>on VDD_HV_ADC              | VDD = 5.5 V                                                                                                             | Analog dynamic consumption (continuous conversion)                                                                                                                   | 0.005 * f <sub>periph</sub> + 2.8 | 0.007 * f <sub>periph</sub> + 3.4 | mA |  |

| I <sub>DD_HV(eTimer)</sub>                                                    | т | eTimer supply current<br>on VDD_HV_REG           | PWM signals generation<br>on all 1 channel @10kHz                                                                       | Dynamic consumption does not change varying the frequency                                                                                                            | 1.8                               | 2.4                               | mA |  |

| I <sub>DD_HV(FlexRay)</sub> T FlexRay supply<br>VDD_HV_REG Static consumption |   |                                                  | ·                                                                                                                       | 4.2 * f <sub>periph</sub>                                                                                                                                            | 5.5 * f <sub>periph</sub>         | μA                                |    |  |

1. Operating conditions:  $f_{periph} = 8 \text{ MHz}$  to 64 MHz

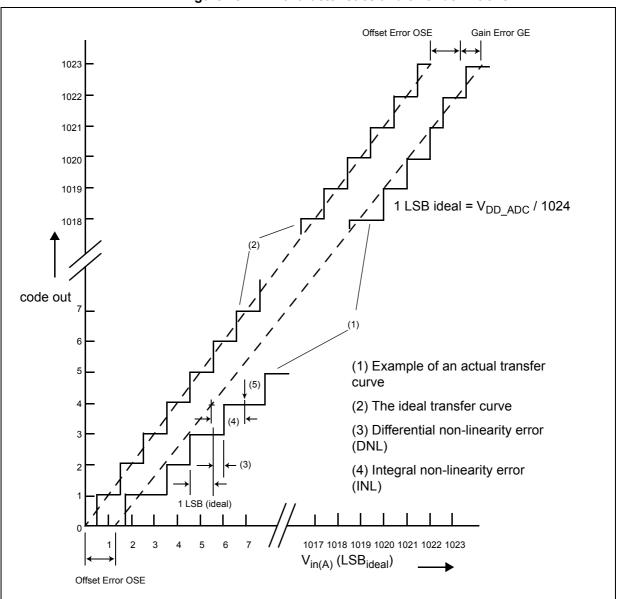

Figure 15. ADC characteristics and error definitions

### 3.15.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high-frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuate the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a highimpedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured.

### **Electrical characteristics**

- 3. The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

- 4. Actual hardware programming times. This does not include software overhead.

- 5. Typical bank programming time assumes that all cells are programmed in a single pulse. In reality some cells will require more than one pulse, adding a small overhead to total bank programming time (see Initial Max column).

- 6. Time between erase suspend resume and next erase suspend.

| Symbol    |   | Parameter                                                                                                                        | Conditions                            | Val   | Unit   |        |  |  |  |  |  |

|-----------|---|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|--------|--------|--|--|--|--|--|

|           |   | Farameter                                                                                                                        | Conditions                            | Min   | Тур    | Unit   |  |  |  |  |  |

| P/E       | С | Number of program/erase cycles per block for 16 KB blocks over the operating temperature range $(T_J)$                           | for 16 KB blocks over the operating — |       | 100000 | cycles |  |  |  |  |  |

| P/E       | С | Number of program/erase cycles per block         for 32 KB blocks over the operating         temperature range (T <sub>J</sub> ) |                                       | 10000 | 100000 | cycles |  |  |  |  |  |

| P/E       | С | Number of program/erase cycles per block for 64 KB blocks over the operating temperature range $(T_J)$                           | _                                     | 10000 | 100000 | cycles |  |  |  |  |  |

| P/E       | С | Number of program/erase cycles per block for 128 KB blocks over the operating temperature range $(T_J)$                          | _                                     | 1000  | 100000 | cycles |  |  |  |  |  |

|           |   |                                                                                                                                  | Blocks with 0 – 1000<br>P/E cycles    | 20    | _      | years  |  |  |  |  |  |

| Retention | С | C Minimum data retention at 85 °C average ambient temperature <sup>(1)</sup>                                                     | Blocks with 10000 P/E cycles          | 10    | _      | years  |  |  |  |  |  |

|           |   |                                                                                                                                  | Blocks with 100000 P/E cycles         | 5     | _      | years  |  |  |  |  |  |

### Table 34. Flash memory module life

1. Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

### Table 35. Flash read access timing

| Symbol C Parameter |   | Conditions <sup>(1)</sup>                                                          | Max           | Unit |     |  |

|--------------------|---|------------------------------------------------------------------------------------|---------------|------|-----|--|

| Fmax               | С | Maximum working frequency for Code Flash                                           | 2 wait states | 66   | MHz |  |

| Fillax C           |   | at given number of WS in worst conditions                                          | 0 wait states | 22   |     |  |

| Fmax               | С | Maximum working frequency for Data Flash at given number of WS in worst conditions | 8 wait states | 66   | MHz |  |

1. VDD =  $3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ , TA = -40 to 125 °C, unless otherwise specified.

# 3.17 AC specifications

## 3.17.1 Pad AC specifications

| Symt                            | Symbol |   | mbol                                             |                                                         | Parameter                                     |                                | Conditions <sup>(1)</sup> |     | Valu | 9   | Unit |

|---------------------------------|--------|---|--------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------|---------------------------|-----|------|-----|------|

| Synt                            |        |   | Falameter                                        | Conditions                                              |                                               |                                | Тур                       | Max |      |     |      |

|                                 |        | D |                                                  | C <sub>L</sub> = 25 pF                                  |                                               | -                              |                           | 50  |      |     |      |

|                                 |        | Т |                                                  | C <sub>L</sub> = 50 pF                                  | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | —                              | —                         | 100 |      |     |      |

| T <sub>tr</sub>                 | сс     | D | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                                 |                                               | —                              | —                         | 125 | ns   |     |      |

| ' tr                            | 00     | D | SLOW configuration                               | C <sub>L</sub> = 25 pF                                  |                                               | —                              |                           | 40  | 115  |     |      |

|                                 |        | Т |                                                  | C <sub>L</sub> = 50 pF                                  | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —                              | —                         | 50  |      |     |      |

|                                 |        | D |                                                  | C <sub>L</sub> = 100 pF                                 |                                               | —                              | _                         | 75  |      |     |      |

|                                 |        | D |                                                  | C <sub>L</sub> = 25 pF                                  | V <sub>DD</sub> = 5.0 V ± 10%,                | —                              | —                         | 10  |      |     |      |

|                                 |        | Т | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 50 pF                                  | PAD3V5V = 0                                   | —                              | _                         | 20  |      |     |      |

| T <sub>tr</sub>                 | сс     | D |                                                  | C <sub>L</sub> = 100 pF                                 | SIUL.PCRx.SRC = 1                             | —                              | —                         | 40  | ns   |     |      |

| 'tr                             | 00     | D | D                                                |                                                         | C <sub>L</sub> = 25 pF                        | V <sub>DD</sub> = 3.3 V ± 10%, | —                         | _   | 12   | 115 |      |

|                                 |        | Т |                                                  | C <sub>L</sub> = 50 pF                                  | PAD3V5V = 1                                   | —                              | _                         | 25  |      |     |      |

|                                 |        | D |                                                  | C <sub>L</sub> = 100 pF                                 | SIUL.PCRx.SRC = 1                             | —                              |                           | 40  | 1    |     |      |

|                                 |        |   |                                                  | $C_L = 25 \text{ pF}$ $V_{DD} = 5.0 \text{ V} \pm 10\%$ | V <sub>DD</sub> = 5.0 V ± 10%,                | -                              | _                         | 4   |      |     |      |

|                                 |        |   |                                                  | C <sub>L</sub> = 50 pF                                  | PAD3V5V = 0                                   | — —                            | 6                         | 1   |      |     |      |

| T <sub>tr</sub>                 | сс     | П | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF                                 | SIUL.PCRx.SRC = 1                             | —                              | —                         | 12  | ns   |     |      |

| 'tr                             | 00     |   | FAST configuration                               | C <sub>L</sub> = 25 pF                                  | $V_{DD} = 3.3 V \pm 10\%$                     | —                              | _                         | 4   | 115  |     |      |

|                                 |        |   |                                                  | $C_1 = 50 \text{ pF}$                                   | PAD3V5V = 1                                   | —                              |                           | 7   |      |     |      |

|                                 |        |   |                                                  |                                                         | C <sub>L</sub> = 100 pF                       | SIUL.PCRx.SRC = 1              | —                         | —   | 12   |     |      |

| T <sub>sim</sub> <sup>(3)</sup> | CC     | т | Symmetric, same drive strength                   | V <sub>DD</sub> = 5.0 V                                 | ± 10%, PAD3V5V = 0                            | —                              | —                         | 4   | ns   |     |      |

| ·SIM                            |        |   | between N and P transistor                       | V <sub>DD</sub> = 3.3 V                                 | ± 10%, PAD3V5V = 1                            | —                              | —                         | 5   |      |     |      |

### Table 36. Output pin transition times

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 °C to T\_A  $_{MAX}$ , unless otherwise specified.

2.  $C_L$  includes device and package capacitances ( $C_{PKG}$  < 5 pF).

3. Transition timing of both positive and negative slopes will differ maximum 50 %.

# 3.18 AC timing characteristics

# 3.18.1 RESET pin characteristics

The SPC56xP54x/SPC56xP60x implements a dedicated bidirectional RESET pin.

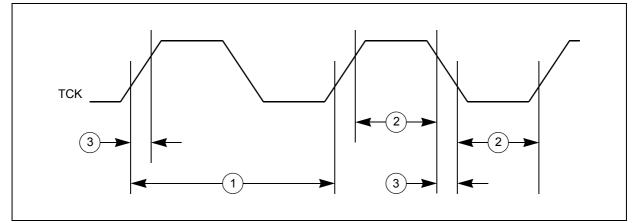

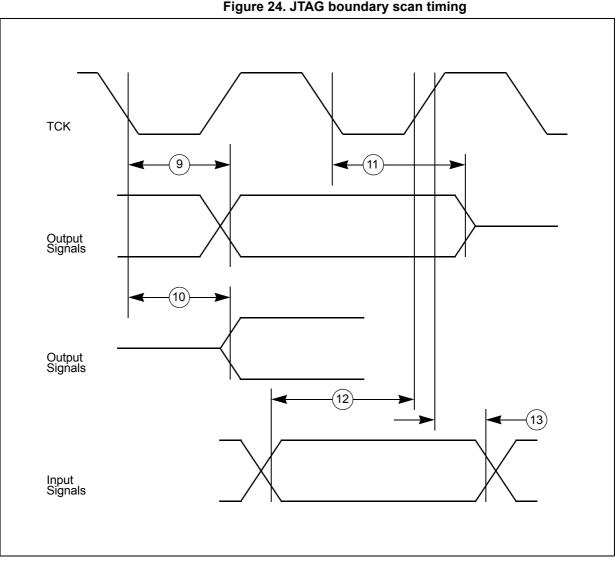

# 3.18.2 IEEE 1149.1 interface timing

|     | Table 30. JTAG pill AC electrical characteristics                    |                                                  |                    |                                                        |            |     |     |      |  |  |  |

|-----|----------------------------------------------------------------------|--------------------------------------------------|--------------------|--------------------------------------------------------|------------|-----|-----|------|--|--|--|

| No. | . Symbol                                                             |                                                  | Symbol C Parameter |                                                        | Conditions | Min | Мах | Unit |  |  |  |

| 1   | t <sub>JCYC</sub>                                                    | CC D TCK cycle time                              |                    | —                                                      | 100        | —   | ns  |      |  |  |  |

| 2   | t <sub>JDC</sub>                                                     | СС                                               | D                  | TCK clock pulse width (measured at $V_{DD_HV_IOx}/2$ ) | —          | 40  | 60  | ns   |  |  |  |

| 3   | t <sub>TCKRISE</sub>                                                 | СС                                               | D                  | TCK rise and fall times (40% – 70%)                    | —          | —   | 3   | ns   |  |  |  |

| 4   | t <sub>TMSS,</sub> t <sub>TDIS</sub>                                 | СС                                               | D                  | TMS, TDI data setup time                               | —          | 5   | _   | ns   |  |  |  |

| 5   | t <sub>TMSH,</sub> t <sub>TDIH</sub>                                 | СС                                               | D                  | TMS, TDI data hold time                                | —          | 25  | _   | ns   |  |  |  |

| 6   | t <sub>TDOV</sub>                                                    | t <sub>TDOV</sub> CC D TCK low to TDO data valid |                    | —                                                      | —          | 40  | ns  |      |  |  |  |

| 7   | t <sub>TDOI</sub>                                                    | СС                                               | D                  | TCK low to TDO data invalid                            | —          | 0   | _   | ns   |  |  |  |

| 8   | t <sub>TDOHZ</sub>                                                   | СС                                               | D                  | TCK low to TDO high impedance                          | —          | 40  | _   | ns   |  |  |  |

| 9   | t <sub>BSDV</sub>                                                    | СС                                               | D                  | TCK falling edge to output valid                       | —          | —   | 50  | ns   |  |  |  |

| 10  | t <sub>BSDVZ</sub>                                                   | СС                                               | D                  | TCK falling edge to output valid out of high impedance | —          | —   | 50  | ns   |  |  |  |

| 11  | t <sub>BSDHZ</sub> CC D TCK falling edge to output high impedance    |                                                  | —                  |                                                        | 50         | ns  |     |      |  |  |  |

| 12  | t <sub>BSDST</sub> CC D Boundary scan input valid to TCK rising edge |                                                  | —                  | 50                                                     | _          | ns  |     |      |  |  |  |

| 13  | t <sub>BSDHT</sub>                                                   | СС                                               | D                  | TCK rising edge to boundary scan input invalid         | —          | 50  | _   | ns   |  |  |  |

Table 38. JTAG pin AC electrical characteristics

### Figure 22. JTAG test clock input timing

### Figure 24. JTAG boundary scan timing

#### 3.18.3 **Nexus timing**

## Table 39. Nexus debug port timing<sup>(1)</sup>

| No  | No. Symbol         |    | с                   | Doromotor                    |                              | Value |                          | Unit |

|-----|--------------------|----|---------------------|------------------------------|------------------------------|-------|--------------------------|------|

| NO. |                    |    | /mbol C Parameter – |                              |                              |       | Тур                      | Max  |

| 1   | t <sub>MCYC</sub>  | CC | D                   | MCKO cycle time              | 32                           | —     | —                        | ns   |

| 2   | t <sub>MDOV</sub>  | сс | D                   | MCKO edge to MDO data valid  | _<br>0.1 × t <sub>MCYC</sub> | _     | 0.25 × t <sub>MCYC</sub> | ns   |

| 3   | t <sub>MSEOV</sub> | СС | D                   | MCKO edge to MSEO data valid | _<br>0.1 × t <sub>MCYC</sub> | _     | 0.25 × t <sub>MCYC</sub> | ns   |

| 4   | t <sub>EVTOV</sub> | СС | D                   | MCKO edge to EVTO data valid | _<br>0.1 × t <sub>MCYC</sub> | _     | 0.25 × t <sub>MCYC</sub> | ns   |

| 5   | t <sub>TCYC</sub>  | CC | D                   | TCK cycle time               | 64 <sup>(2)</sup>            | —     | —                        | ns   |

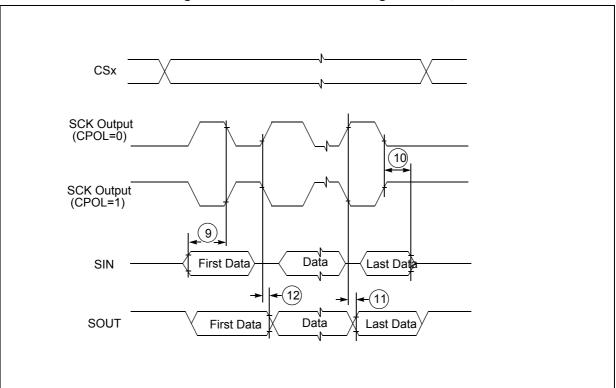

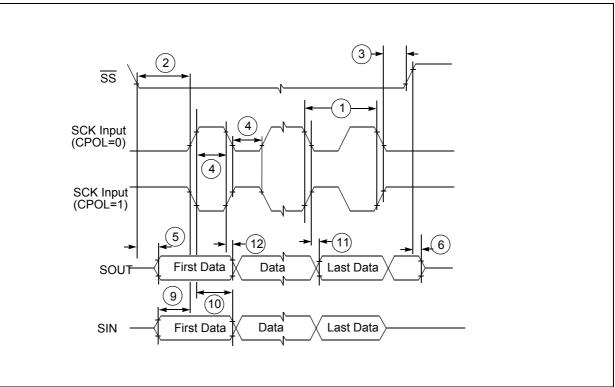

Figure 30. DSPI classic SPI timing — master, CPHA = 1

Figure 31. DSPI classic SPI timing — slave, CPHA = 0

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 4.2 Package mechanical data

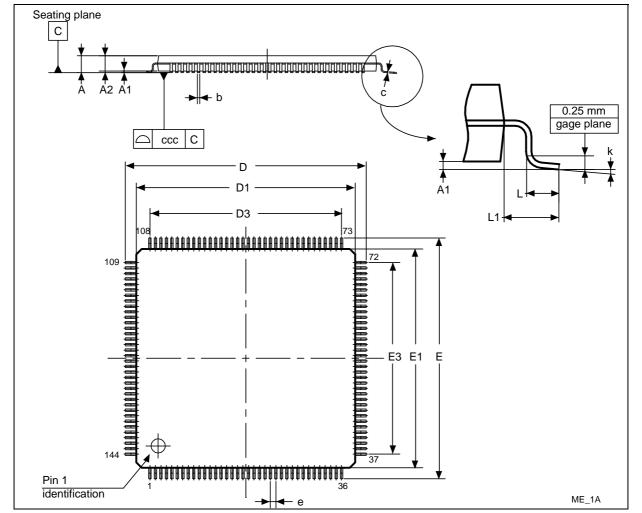

### 4.2.1 LQFP144 mechanical outline drawing

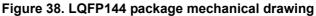

## 4.2.2 LQFP100 mechanical outline drawing

### Figure 39. LQFP100 package mechanical drawing

| Symbol |       | mm    |       | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------|-------|-------|-----------------------|--------|--------|--|--|

| Symbol | Min   | Тур   | Мах   | Min                   | Тур    | Max    |  |  |

| A      | —     | —     | 1.600 | —                     | —      | 0.0630 |  |  |

| A1     | 0.050 | —     | 0.150 | 0.0020                | —      | 0.0059 |  |  |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |  |

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved