#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 80K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56ap60l5cefby |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                             | Table 2. SPC56xP54                  | Table 2. SPC56xP54x/SPC56xP60x device comparison (continued) |                    |                        |           |  |  |  |  |  |

|-----------------------------|-------------------------------------|--------------------------------------------------------------|--------------------|------------------------|-----------|--|--|--|--|--|

|                             | Feature                             | SPC560P54                                                    | SPC560P60          | SPC56AP54              | SPC56AP60 |  |  |  |  |  |

| Enhanced D<br>access) cha   | MA (direct memory nnels             | 16                                                           |                    |                        |           |  |  |  |  |  |

| FlexRay                     |                                     |                                                              | Yes (64 mes        | ssage buffer)          |           |  |  |  |  |  |

| FlexCAN (co                 | ontroller area network)             |                                                              | 3 <sup>(1</sup>    | ),(2)                  |           |  |  |  |  |  |

| Safety port                 |                                     |                                                              | Yes (via third Fl  | exCAN module)          |           |  |  |  |  |  |

| FCCU (fault                 | collection and control unit)        |                                                              | Ye                 | s <sup>(3)</sup>       |           |  |  |  |  |  |

| CTU (cross                  | triggering unit)                    |                                                              | Y                  | es                     |           |  |  |  |  |  |

| eTimer char                 | inels                               |                                                              | 2 :                | × 6                    |           |  |  |  |  |  |

| FlexPWM (p<br>channels      | oulse-width modulation)             | Νο                                                           |                    |                        |           |  |  |  |  |  |

| Analog-to-di                | gital converters (ADC)              | One (10-bit, 27-channel) <sup>(4)</sup>                      |                    |                        |           |  |  |  |  |  |

| LINFlex mod                 | dules                               | 2 (1 × Master/Slave, 1 × Master only) <sup>(5)</sup>         |                    |                        |           |  |  |  |  |  |

| DSPI (deser<br>interface) m | ial serial peripheral<br>odules     | 5 <sup>(6)</sup>                                             |                    |                        |           |  |  |  |  |  |

| CRC (cyclic                 | redundancy check) units             | 2 <sup>(7)</sup>                                             |                    |                        |           |  |  |  |  |  |

| JTAG interfa                | ace                                 | Yes                                                          |                    |                        |           |  |  |  |  |  |

| Nexus port of               | controller (NPC)                    |                                                              | Yes (Lev           | vel 2+) <sup>(8)</sup> |           |  |  |  |  |  |

|                             | Digital power supply <sup>(9)</sup> | 3.3 V                                                        | or 5 V single supp | ly with external trar  | nsistor   |  |  |  |  |  |

| Cummba                      | Analog power supply                 | 3.3 V or 5 V                                                 |                    |                        |           |  |  |  |  |  |

| Supply                      | Internal RC oscillator              |                                                              | 16 I               | MHz                    |           |  |  |  |  |  |

|                             | External crystal oscillator         | 4–40 MHz                                                     |                    |                        |           |  |  |  |  |  |

| Packages                    |                                     | LQFP100 LQFI<br>LQFP144 LQFP                                 |                    |                        |           |  |  |  |  |  |

| Temperature                 | Standard ambient temperature        | –40 to 125 °C                                                |                    |                        |           |  |  |  |  |  |

Table 2. SPC56xP54x/SPC56xP60x device comparison (continued)

1. Each FlexCAN module has 32 message buffers.

2. One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

3. Enhanced FCCU version.

4. Same amount of ADC channels as on SPC560P44/50 not considering the internally connected ones. 26 channels on LQFP144 and 16 channels on LQFP100.

- 5. LinFlex\_1 is Master Only.

- 6. Increased number of CS for DSPI\_1.

- 7. Upgraded specification with addition of 8-bits polynomial (CRC-8 VDA CAN) support and 3rd context.

- 8. Improved debugging capability with data trace capability and increased Nexus throughput available on emulation package.

- 9. 3.3 V range and 5 V range correspond to different orderable parts.

- 10. Software development package only. Not available for production.

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency)

Programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

# 1.5.9 Main oscillator

The main oscillator provides these features:

- Input frequency range 4 MHz to 40 MHz

- Crystal input mode or Oscillator input mode

- PLL reference

# 1.5.10 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC Oscillator provides these features:

- Nominal frequency 16 MHz

- ±6% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

# **1.5.11 Periodic interrupt timer (PIT)**

The PIT module implements these features:

- Up to four general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

# 1.5.12 System timer module (STM)

The STM module implements these features:

- 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

The STM module is replicated for each processor.

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a six-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

## 1.5.19 Safety port (FlexCAN)

The SPC56xP54x/SPC56xP60x MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate as fast as 7.5 Mb at 60 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 Message buffers of 0 to 8 bytes data length

- Can be used as a third independent CAN module

# 1.5.20 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 64 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

It implements the following features:

- Double buffered trigger generation unit with up to eight independent triggers generated from external triggers

- Trigger generation unit configurable in sequential mode or in triggered mode

- Each Trigger can be appropriately delayed to compensate the delay of external low pass filter

- Double buffered global trigger unit allowing eTimer synchronization and/or ADC command generation

- Double buffered ADC command list pointers to minimize ADC-trigger unit update

- Double buffered ADC conversion command list with up to 24 ADC commands

- Each trigger has the capability to generate consecutive commands

- ADC conversion command allows to control ADC channel from each ADC, single or synchronous sampling, independent result queue selection

## 1.5.26 Cyclic redundancy check (CRC)

- 3 contexts for the concurrent CRC computation

- Separate CRC engine for each context

- Zero-wait states during the CRC computation (pipeline scheme)

- 3 hard-wired polynomials (CRC-8 VDA CAN, CRC-32 Ethernet and CRC-16-CCITT)

- Support for byte/half-word/word width of the input data stream

- Support for expected and actual CRC comparison

## 1.5.27 Nexus development interface (NDI)

The NDI block provides real-time development support capabilities for the SPC56xP54x/SPC56xP60x Power Architecture based MCU in compliance with the IEEE-ISTO 5001-2003 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility. The NDI block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal buses to provide development support as per the IEEE-ISTO 5001-2003 Class 2+ standard. The development support provided includes access to the MCU's internal memory map and access to the processor's internal registers during run time.

The Nexus Interface provides the following features:

- Configured via the IEEE 1149.1

- All Nexus port pins operate at V<sub>DDIO</sub> (no dedicated power supply)

- Nexus 2+ features supported

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or keep executing and allow overwrite of information

- Watchpoint triggering, watchpoint triggers program tracing

- DDR

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin<sup>(a)</sup>

# 1.5.28 IEEE 1149.1 (JTAG) controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with four pins (TDI, TMS, TCK, TDO)

- Selectable modes of operation include JTAGC/debug or normal system operation.

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC, ACCESS\_AUX\_TAP\_CORE0, ACCESS\_AUX\_TAP\_CORE1, ACCESS\_AUX\_TAP\_NASPS\_0, ACCESS\_AUX\_TAP\_NASPS\_1

- Three test data registers: a bypass register, a boundary scan register, and a device identification register.

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry.

# 1.5.29 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN transistor

- Regulates external 3.3 V to 5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

a. At least one TCK clock is necessary for the EVTI signal to be recognized by the MCU.

|          | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                 |           |             |                  |         |                     |             |             |                            |

|----------|------------------------------------------------|---------------------------------|-----------|-------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port     | PCR                                            | Alternate                       |           | Peripheral  | I/O              | Pad s   | peed <sup>(6)</sup> | Pin         |             |                            |

| pin      | No.                                            | function <sup>(2),</sup><br>(3) | Functions | (4)         | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|          |                                                | ALT0                            | GPIO[9]   | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | CS1_2     | DSPI_2      | 0                |         |                     |             |             |                            |

| A[9]     | PCR[9]                                         | ALT2                            | —         | —           | —                | Slow    | Medium              | 94          | 134         | 158                        |

|          |                                                | ALT3                            | —         | —           | —                |         |                     |             |             |                            |

|          |                                                | —                               | SIN_4     | DSPI_4      |                  |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPIO[10]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | CS0_2     | DSPI_2      | I/O              |         |                     |             |             |                            |

| A[10]    | PCR[10]                                        | ALT2                            | —         | —           | —                | Slow    | Medium              | 81          | 118         | 142                        |

|          |                                                | ALT3                            | —         | —           | —                |         |                     |             |             |                            |

|          |                                                |                                 | EIRQ[9]   | SIUL        | Ι                |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPI0[11]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | SCK_2     | DSPI_2      | I/O              |         | Medium              | 82          | 120         |                            |

| A[11]    | PCR[11]                                        | ALT2                            | —         | —           | —                | Slow    |                     |             |             | 144                        |

|          |                                                | ALT3                            | —         | —           | —                |         |                     |             |             |                            |

|          |                                                | —                               | EIRQ[10]  | SIUL        | I                |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPIO[12]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | SOUT_2    | DSPI_2      | 0                |         |                     |             |             | 146                        |

| A[12]    | PCR[12]                                        | ALT2                            | _         | _           | —                | Slow    | Medium              | 83          | 122         |                            |

|          |                                                | ALT3                            | —         | —           | —                |         |                     |             |             |                            |

|          |                                                | —                               | EIRQ[11]  | SIUL        | I                |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPIO[13]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | CS4_1     | DSPI_1      | 0                |         |                     | 0.5         | 400         |                            |

| A [4 0]  | DODIAN                                         | ALT2                            | _         | _           | —                | 0       |                     |             |             | 100                        |

| A[13]    | PCR[13]                                        | ALT3                            | —         | —           | —                | Slow    | Medium              | 95          | 136         | 160                        |

|          |                                                | —                               | SIN_2     | DSPI_2      | I                |         |                     |             |             |                            |

|          |                                                | —                               | EIRQ[12]  | SIUL        | I                |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPIO[14]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | TXD       | Safety Port | 0                |         |                     |             |             |                            |

| A[14]    | PCR[14]                                        | ALT2                            | ETC[4]    | eTimer_1    | I/O              | Slow    | Medium              | 99          | 143         | 175                        |

|          |                                                | ALT3                            | CS5_1     | DSPI_1      | 0                |         |                     |             |             |                            |

|          |                                                | —                               | EIRQ[13]  | SIUL        | I                |         |                     |             |             |                            |

|          |                                                | ALT0                            | GPIO[15]  | SIUL        | I/O              |         |                     |             |             |                            |

|          |                                                | ALT1                            | CS6_1     | DSPI_1      | 0                |         |                     |             |             |                            |

| A 1 4 53 |                                                | ALT2                            | ETC[5]    | eTimer_1    | I/O              | 01      |                     |             |             | 470                        |

| A[15]    | PCR[15]                                        | ALT3                            | _         |             | —                | Slow    | Medium              | 100         | 144         | 176                        |

|          |                                                | —                               | RXD       | Safety Port | I                |         |                     |             |             |                            |

|          |                                                | —                               | EIRQ[14]  | SIUL        | I                |         |                     |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Dent        | DOD        | Alternate                       |           | Parinkanal        | I/O              | -       | peed <sup>(6)</sup> |             | Pin         |                            |

|-------------|------------|---------------------------------|-----------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port<br>pin | PCR<br>No. | function <sup>(2),</sup><br>(3) | Functions | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             | <u>.</u>   |                                 |           | Po                | ort C            |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[32]  | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                            | —         | —                 |                  |         |                     |             |             |                            |

| C[0]        | PCR[32]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 45          | 66          | 78                         |

|             |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|             |            |                                 | AN[19]    | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[33]  | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                            | —         | —                 |                  |         |                     |             |             |                            |

| C[1]        | PCR[33]    | ALT2                            | —         | —                 | Input Only       | —       | —                   | 28          | 41          | 49                         |

|             |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|             |            |                                 | AN[2]     | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[34]  | SIUL              |                  |         |                     |             |             |                            |

|             |            | ALT1                            | —         | —                 |                  |         |                     |             |             |                            |

| C[2]        | PCR[34]    | ALT2                            | —         | —                 | Input Only       | —       | _                   | 30          | 45          | 53                         |

|             |            | ALT3                            | —         | —                 |                  |         |                     |             |             |                            |

|             |            | —                               | AN[3]     | ADC_0             |                  |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[35]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | CS1_0     | DSPI_0            | 0                |         |                     |             |             |                            |

| C[3]        | PCR[35]    | ALT2                            | ETC[4]    | eTimer_1          | I/O              | Slow    | Medium              | 10          | 16          | 24                         |

|             |            | ALT3                            | TXD       | LINFlex_1         | 0                |         |                     |             |             |                            |

|             |            |                                 | EIRQ[21]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[36]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | CS0_0     | DSPI_0            | I/O              |         |                     |             |             |                            |

| C[4]        | PCR[36]    | ALT2                            | —         | —                 | —                | Slow    | Medium              | 5           | 11          | 19                         |

|             |            | ALT3                            | DEBUG[4]  | SSCM              | —                |         |                     |             |             |                            |

|             |            |                                 | EIRQ[22]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[37]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | SCK_0     | DSPI_0            | I/O              |         |                     |             |             |                            |

| C[5]        | PCR[37]    | ALT2                            | SCK_4     | DSPI_4            | I/O              | Slow    | Medium              | 7           | 13          | 21                         |

|             |            | ALT3                            | DEBUG[5]  | SSCM              | —                |         |                     |             |             |                            |

|             |            | —                               | EIRQ[23]  | SIUL              | I                |         |                     |             |             |                            |

|             |            | ALT0                            | GPIO[38]  | SIUL              | I/O              |         |                     |             |             |                            |

|             |            | ALT1                            | SOUT_0    | DSPI_0            | 0                |         |                     |             |             |                            |

| C[6]        | PCR[38]    | ALT2                            | —         | —                 | —                | Slow    | Medium              | 98          | 142         | 174                        |

|             |            | ALT3                            | DEBUG[6]  | SSCM              | —                |         |                     |             |             |                            |

|             |            | —                               | EIRQ[24]  | SIUL              | I                |         |                     |             |             |                            |

Table 7. Pin muxing<sup>(1)</sup> (continued)

|             | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                 |                    |                   |                  |         |                     |             |             |                            |

|-------------|------------------------------------------------|---------------------------------|--------------------|-------------------|------------------|---------|---------------------|-------------|-------------|----------------------------|

|             |                                                | Alternate                       |                    |                   | I/O              | Pad s   | peed <sup>(6)</sup> |             | Pin         |                            |

| Port<br>pin | PCR<br>No.                                     | function <sup>(2),</sup><br>(3) | Functions          | Peripheral<br>(4) | direction<br>(5) | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

|             |                                                | ALT0                            | GPIO[71]           | SIUL              |                  |         |                     |             |             |                            |

|             | E[7] PCR[71]                                   | ALT1                            |                    | —                 |                  |         |                     |             |             |                            |

| E[7]        |                                                | ALT2<br>ALT3                    |                    | —                 | Input Only       | —       | _                   |             | 48          | 56                         |

|             |                                                | ALI 3                           | <br>AN[10]         | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                | ALT0                            | GPIO[72]           | SIUL              |                  |         |                     |             |             |                            |

|             |                                                | ALT1                            |                    |                   |                  |         |                     |             |             |                            |

| E[8]        | PCR[72]                                        | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 59          | 67                         |

|             |                                                | ALT3                            | _                  | _                 |                  |         |                     |             |             |                            |

|             |                                                | —                               | AN[22]             | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                | ALT0                            | GPIO[73]           | SIUL              |                  |         |                     |             |             |                            |

|             |                                                | ALT1                            | —                  | —                 |                  |         |                     |             |             |                            |

| E[9]        | PCR[73]                                        | ALT2                            | —                  | —                 | Input Only       | —       | —                   | _           | 61          | 69                         |

|             |                                                | ALT3                            | —<br>AN[23]        | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                |                                 |                    |                   |                  |         |                     |             |             |                            |

|             | E[10] PCR[74]                                  | ALT0<br>ALT1                    | GPIO[74]           | SIUL              |                  |         |                     |             |             |                            |

| E[10]       |                                                | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 63          | 75                         |

|             |                                                | ALT3                            | _                  | _                 | r · · · J        |         |                     |             |             | -                          |

|             |                                                | —                               | AN[24]             | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                | ALT0                            | GPIO[75]           | SIUL              |                  |         |                     |             |             |                            |

|             |                                                | ALT1                            | —                  | —                 |                  |         |                     |             |             |                            |

| E[11]       | PCR[75]                                        | ALT2                            | —                  | —                 | Input Only       | —       | —                   |             | 65          | 77                         |

|             |                                                | ALT3                            | —<br>AN[25]        | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                | ALT0                            |                    | SIUL              |                  |         |                     |             |             |                            |

|             |                                                | ALTU<br>ALT1                    | GPIO[76]           | 510L              |                  |         |                     |             |             |                            |

| E[12]       | PCR[76]                                        | ALT2                            | _                  | _                 | Input Only       | _       | _                   |             | 67          | 79                         |

|             |                                                | ALT3                            | —                  | —                 | . ,              |         |                     |             |             |                            |

|             |                                                | —                               | AN[26]             | ADC_0             |                  |         |                     |             |             |                            |

|             |                                                | ALT0                            | GPIO[77]           | SIUL              | I/O              |         |                     |             |             |                            |

|             |                                                | ALT1                            | SCK_3              | DSPI_3            | I/O              |         |                     |             |             |                            |

| E[13]       | PCR[77]                                        | ALT2                            | —                  | -                 | —                | Slow    | Medium              | —           | 117         | 141                        |

|             |                                                | ALT3                            |                    | <br>SIUL          | —<br>I           |         |                     |             |             |                            |

|             |                                                | -                               | EIRQ[25]           |                   |                  |         |                     |             |             |                            |

|             |                                                | ALT0<br>ALT1                    | GPIO[78]<br>SOUT_3 | SIUL<br>DSPI_3    | I/O<br>O         |         |                     |             |             |                            |

| E[14]       | PCR[78]                                        | ALT1<br>ALT2                    |                    |                   | _                | Slow    | Medium              | _           | 119         | 143                        |

| ]           |                                                | ALT3                            | _                  | _                 | _                | 0.011   |                     |             |             |                            |

|             |                                                | _                               | EIRQ[26]           | SIUL              | I                |         |                     |             |             |                            |

Table 7 Bin muxing<sup>(1)</sup> (continued)

|             | Table 7. Pin muxing <sup>(1)</sup> (continued) |                                   |                                |                             |                    |         |                     |             |             |                            |

|-------------|------------------------------------------------|-----------------------------------|--------------------------------|-----------------------------|--------------------|---------|---------------------|-------------|-------------|----------------------------|

| Port        | DCD                                            | Alternate                         |                                | Borinhoral                  | I/O                | Pad s   | peed <sup>(6)</sup> | Pin         |             |                            |

| Port<br>pin | PCR<br>No.                                     | function <sup>(2),</sup><br>(3)   | Functions                      | Peripheral<br>(4)           | direction<br>(5)   | SRC = 0 | SRC = 1             | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 <sup>(7)</sup> |

| F[7]        | PCR[87]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[87]<br>—<br>MCKO<br>—     | SIUL<br>—<br>nexus_0<br>—   | I/O<br>  O         | Slow    | Fast                | _           | 19          | 27                         |

| F[8]        | PCR[88]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[88]<br><br>MSEO1<br>      | SIUL<br>—<br>nexus_0<br>—   | I/O<br>—<br>—<br>— | Slow    | Fast                | _           | 20          | 28                         |

| F[9]        | PCR[89]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[89]<br>—<br>MSEO0<br>—    | SIUL<br>—<br>nexus_0<br>—   | /O<br>  O<br>      | Slow    | Fast                | _           | 23          | 31                         |

| F[10]       | PCR[90]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[90]<br><br>EVTO<br>       | SIUL<br>—<br>nexus_0<br>—   | I/O<br>  0<br>     | Slow    | Fast                | _           | 24          | 32                         |

| F[11]       | PCR[91]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[91]<br>EVTI<br>—          | SIUL<br>nexus_0<br>—        | I/O<br>I<br>—      | Slow    | Medium              | _           | 25          | 33                         |

| F[12]       | PCR[92]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[92]<br>ETC[3]<br>—        | SIUL<br>eTimer_1<br>—       | I/O<br>I/O<br>—    | Slow    | Medium              | _           | 106         | 130                        |

| F[13]       | PCR[93]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[93]<br>ETC[4]<br>—        | SIUL<br>eTimer_1<br>—       | I/O<br>I/O<br>—    | Slow    | Medium              | _           | 112         | 136                        |

| F[14]       | PCR[94]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[94]<br>TXD<br>—           | SIUL<br>LINFlex_1<br>       | I/O<br>O           | Slow    | Medium              | _           | 115         | 139                        |

| F[15]       | PCR[95]                                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[95]<br>—<br>—<br>—<br>RXD | SIUL<br>—<br>—<br>LINFlex_1 | VO<br>   <br>      | Slow    | Medium              | _           | 113         | 137                        |

Table 7. Pin muxing<sup>(1)</sup> (continued)

| Symbol                                       |    | Parameter                                     | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |

|----------------------------------------------|----|-----------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

|                                              |    | 5.0 V voltage regulator                       | —                                     | 4.5                          | 5.5                          |      |

| $V_{DD_HV_REG}$                              | SR | supply voltage                                | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

|                                              |    | 5.0 V ADC supply and high                     | —                                     | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_AD</sub> SF                     | SR | R 5.0 V ADC supply and high reference voltage | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | _                            | V    |

| V <sub>SS_HV_AD</sub>                        | SR | ADC ground and low reference voltage          | _                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR | Internal supply voltage                       | —                                     | _                            | —                            | V    |

| $V_{SS_{LV}_{REGCOR}}^{(3)}$                 | SR | Internal reference voltage                    | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR | Internal supply voltage                       | —                                     | —                            | —                            | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR | Internal reference voltage                    | —                                     | 0                            | 0                            | V    |

| T <sub>A</sub>                               | SR | Ambient temperature under bias                | _                                     | -40                          | 125                          | °C   |

| Table 10. Recommended | operating conditions | (5.0 V) | (continued) |

|-----------------------|----------------------|---------|-------------|

|                       | operating containers | (0.0.0) | (001101000) |

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

| Symbol                                |    | Parameter                                               | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |

|---------------------------------------|----|---------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| V <sub>SS_HV</sub>                    | SR | Digital ground                                          | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 3.3 V input/output supply voltage                       | _                                     | 3.0                          | 3.6                          | V    |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                             | —                                     | 0                            | 0                            | V    |

|                                       |    |                                                         | —                                     | 3.0                          | 3.6                          |      |

| V <sub>DD_HV_FL</sub>                 | SR | 3.3 V code and data flash<br>memory supply voltage      | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_FL</sub>                 | SR | Code and data flash<br>memory ground                    | _                                     | 0                            | 0                            | V    |

|                                       |    | 3.3 V crystal oscillator                                | —                                     | 3.0                          | 3.6                          |      |

| V <sub>DD_HV_OSC</sub>                | SR | amplifier supply voltage                                | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

| V <sub>SS_HV_OSC</sub>                | SR | 3.3 V crystal oscillator<br>amplifier reference voltage | _                                     | 0                            | 0                            | V    |

## Table 11. Recommended operating conditions (3.3 V)

| Symbol                                       |    | Parameter                                 | Conditions                            | Min                          | Max <sup>(1)</sup>           | Unit |

|----------------------------------------------|----|-------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

|                                              |    | 2.2.V/voltage regulator                   | —                                     | 3.0                          | 3.6                          |      |

| $V_{DD_HV_REG}$                              | SR | 3.3 V voltage regulator<br>supply voltage | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

|                                              |    |                                           | —                                     | 3.0                          | 5.5                          |      |

| V <sub>DD_HV_AD</sub> SR                     | SR | reference voltage                         | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | 5.5                          | V    |

| V <sub>SS_HV_AD</sub>                        | SR | ADC ground and low reference voltage      | _                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>(3),(4)</sup> | SR | Internal supply voltage                   | —                                     | —                            | —                            | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>(3)</sup>     | SR | Internal reference voltage                | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>   | SR | Internal supply voltage                   | —                                     | —                            | —                            | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>       | SR | Internal reference voltage                | —                                     | 0                            | 0                            | V    |

| T <sub>A</sub>                               | SR | Ambient temperature under bias            | _                                     | -40                          | 125                          | °C   |

Table 11. Recommended operating conditions (3.3 V) (continued)

1. Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_HV_IOy} - V_{DD_HV_IOx}| < 100 mV$ .

To be connected to emitter of external NPN. Low voltage supplies are not under user control—these are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_REGCORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

Figure 7 shows the constraints of the different power supplies.

$\mathsf{R}_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $\mathsf{R}_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using *Equation 3*:

Equation 3  $T_J = T_T + (\Psi_{JT} \times P_D)$

where:

T<sub>T</sub>= thermocouple temperature on top of the package (°C)

$\Psi_{JT}$ = thermal characterization parameter (°C/W)

$P_D$ = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 3.5.1.1 References

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 U.S.A. (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at jedec.org web site.

1. C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53-58, March 1998.

3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

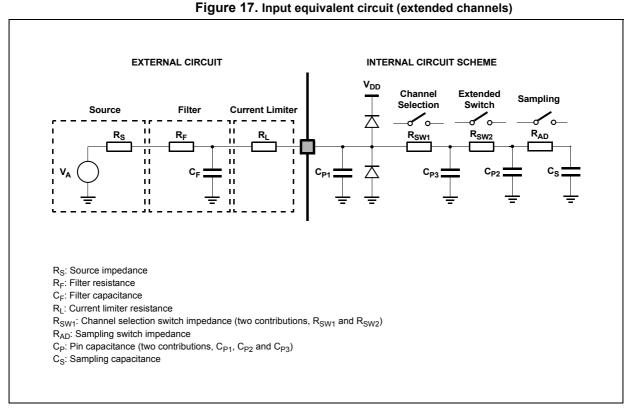

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_{F}$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 16*): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

DocID18340 Rev 6

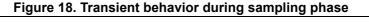

In particular two different transient periods can be distinguished:

• A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

#### **Equation 5**

$$\tau_{1} = (R_{SW} + R_{AD}) \times \frac{C_{P} \times C_{S}}{C_{P} + C_{S}}$$

*Equation 5* can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

#### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \times C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation* 7:

#### **Equation 7**

$$V_{A1} \times (C_S + C_{P1} + C_{P2}) = V_A \times (C_{P1} + C_{P2})$$

• A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance  $R_L$ : again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2 \! < \! R_L \! \times (C_S \! + C_{P1} \! + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraint on  $R_L$  sizing is obtained:

#### Equation 9

$$8.5 \times \tau_2 = 8.5 \times R_L \times (C_S + C_{P1} + C_{P2}) < T_S$$

Of course, R<sub>L</sub> shall be sized also according to the current limitation constraints, in combination with R<sub>S</sub> (source impedance) and R<sub>F</sub> (filter resistance). Being C<sub>F</sub> definitively bigger than C<sub>P1</sub>, C<sub>P2</sub> and C<sub>S</sub>, then the final voltage V<sub>A2</sub> (at the end of the charge transfer transient) will be much higher than V<sub>A1</sub>. *Equation 10* must be respected (charge balance assuming now C<sub>S</sub> already charged at V<sub>A1</sub>):

### **Equation 10**

$$V_{A2} \times (C_S + C_{P1} + C_{P2} + C_F) = V_A \times C_F + V_{A1} \times (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on

DocID18340 Rev 6

g. The output drive provided is open drain and hence must be terminated by an external resistor of value 1 k $\Omega$ .

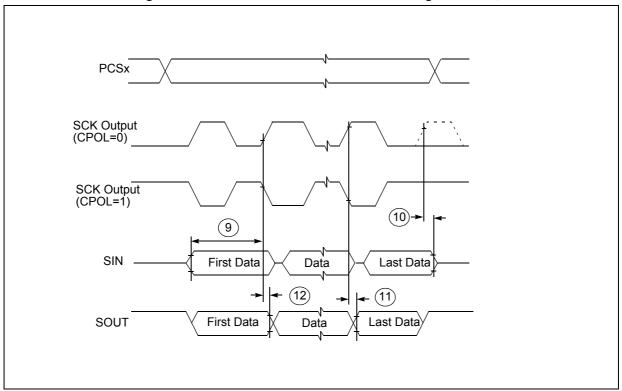

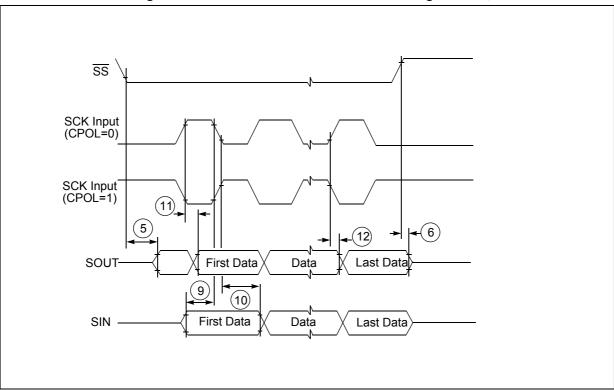

Figure 34. DSPI modified transfer format timing — master, CPHA = 1

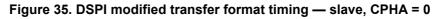

Figure 36. DSPI modified transfer format timing — slave, CPHA = 1

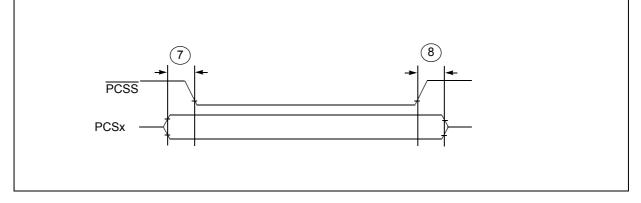

# Figure 37. DSPI PCS strobe (PCSS) timing

# 5 Ordering information

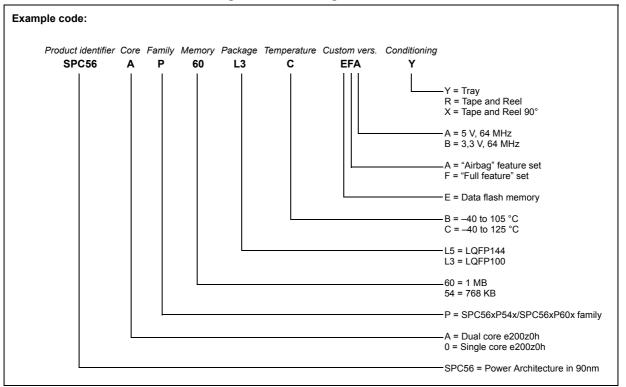

# Figure 40. Ordering information scheme<sup>(h)</sup>

h. Not all configurations are available on the market. Please contact your ST sales representative to get the list of orderable commercial part number.

| Date        | Revision | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Nov-2012 | 4        | <ul> <li>In the cover page, replaced "64 MHz, dual issue, 32-bit CPU core complex" with "64 MHz, single issue, 32-bit CPU core complex"</li> <li><i>Table 9: Absolute maximum ratings</i>, updated TV<sub>DD</sub> entry</li> <li><i>Table 22: DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V]=1)</i>: Updated conditions value of V<sub>OL_F</sub> to 11 mA</li> <li>Updated conditions value of V<sub>OH_F</sub> to -11 mA</li> <li><i>Table 24: Peripherals supply current (5 V and 3.3 V)</i>: Replaced all occurrences of I<sub>DD_BV</sub> in this table with I<sub>DD_HV</sub></li> <li>Replaced all occurrences of VDD_BV in this table with VDD_HV_REG.</li> <li><i>Figure 40: Ordering information scheme</i>, fixed typo in the footnote.</li> </ul>                                                                                                                                                                                                                                                                     |

| 18-Sep-2013 | 5        | Updated Disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15-Jun-2016 | 6        | <ul> <li>Added "AEC-Q10x qualified" in <i>Features</i> section.</li> <li>In <i>Table 2: SPC56xP54x/SPC56xP60x device comparison</i> added footnote "LinFlex_1 is Master Only." related to row "LINFlex modules"</li> <li>Updated <i>Table 3: SPC56xP54x/SPC56xP60x device configuration difference</i></li> <li><i>Figure 2: LQFP176 pinout (top view)</i>: <ul> <li>Changed PB[4] to TDO</li> <li>Changed PB[5] to TDI</li> <li>Changed pins 71,72 to NC</li> <li>Changed pins 87,88 to NC</li> </ul> </li> <li>In <i>Section 1.5.27: Nexus development interface (NDI)</i>, added note "At least one TCK clock is necessary for the EVTI signal to be recognized by the MCU." for EVTI pin.</li> <li>In <i>Table 7: Pin muxing</i>: <ul> <li>Replaced "PCR register" with "PCR No."</li> <li>Updated "CS3" with "CS3_4" function related to A[2] port pin</li> <li>In column "I/O direction", added "O" for "DSPI_1" peripheral</li> <li>In "Functions" column related to D[12] port pin, changed DS7_1 to CS7_1</li> </ul> </li> </ul> |

# Table 44. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID18340 Rev 6