Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z380C                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                         |

| Speed                           | 20MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | -                                                      |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 144-LQFP                                               |

| Supplier Device Package         | 144-VQFP (20x20)                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8038220asc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z80382/Z8L382 Z382 Data Communications Processor

#

PS006701-0800 Conventions

# **Table of Contents**

| 200302, 20L302 high-renormance Data Communications Processors |

|---------------------------------------------------------------|

| Features                                                      |

| General Description                                           |

| Z80382 Pin Description                                        |

| Absolute Maximum Ratings                                      |

| Standard Test Conditions                                      |

| DC Characteristics                                            |

| AC Characteristics                                            |

| Pin Functions                                                 |

| Functional Description                                        |

| Central Processing Unit                                       |

| Modes of Operation                                            |

| CPU Address Spaces                                            |

| Data Types                                                    |

| Addressing Modes                                              |

| Instruction Set 54                                            |

| Host Interface                                                |

| 16550 MIMIC                                                   |

| Host DMA Mailbox                                              |

| Plug-and-Play Interface 6 <sup>2</sup>                        |

| PCMCIA Interface                                              |

| DMA Channels 67                                               |

| DMA Channel/Device Interface                                  |

| DMA Operation                                                 |

| Per-Channel Registers                                         |

| Centralized DMA Registers                                     |

| Serial Communication Channels                                 |

| Asynchronous Serial Communications Interface (ASCI)           |

| HDLC Serial Channels77                                        |

| GCI/SCIT Interface 82                                         |

| Clocked Serial I/O (CSIO)                                     |

# List of Figures

| Figure 1.  | Z80382 Block Diagram                                                                          | . 5 |

|------------|-----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Z80382 144-Pin QFP and VQFP Pin Description                                                   | . 6 |

| Figure 3.  | Test Load Diagram                                                                             | . 8 |

| Figure 4.  | 380C Processor Timing Diagram                                                                 | 16  |

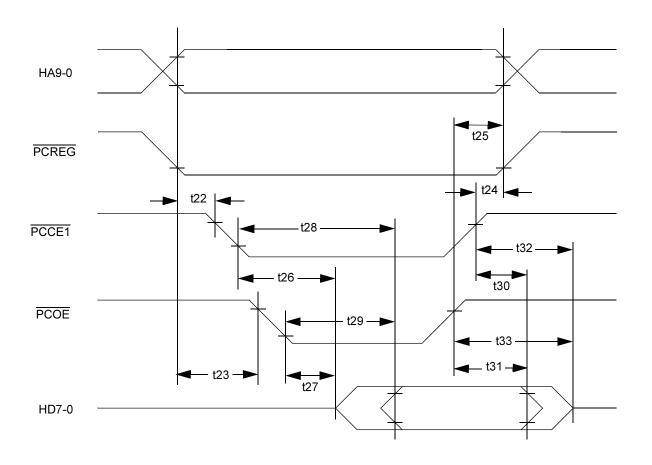

| Figure 5.  | Host - PCMCIA Attribute Memory Read Timing Diagram                                            | 18  |

| Figure 6.  | Host - PCMCIA Attribute Memory Write Timing Diagram                                           | 19  |

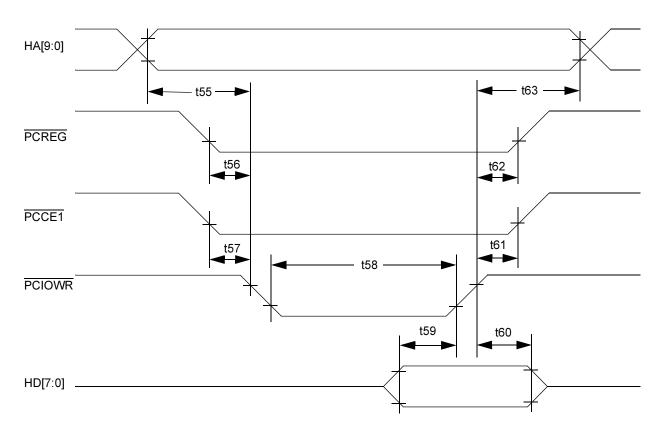

| Figure 7.  | Host - PCMCIA I/O Read Timing Diagram                                                         | 21  |

| Figure 8.  | Host - PCMCIA I/O Write Timing Diagram                                                        | 23  |

| Figure 9.  | Timer Output Timing Diagram                                                                   | 24  |

| Figure 10. | CSIO Receive/Transmit Timing Diagram                                                          | 25  |

| Figure 11. | ASCI Transmitter Timing Diagram                                                               | 26  |

| Figure 12. | ASCI Receiver Timing Diagram                                                                  | 27  |

| Figure 13. | Baud Rate Generator Timing Diagram                                                            | 28  |

| Figure 14. | CTSA and DCDA Timing Diagram                                                                  | 29  |

| Figure 15. | RTSA Timing Diagram                                                                           | 29  |

| Figure 16. | General-Purpose I/O Port Timing Diagram                                                       | 30  |

| Figure 17. | HDLC Receive Timing Diagram (Full Time HDLC, RxC Input) $\ldots$                              | 32  |

| Figure 18. | HDLC Receive Timing (Full Time HDLC, RxC Output)                                              | 32  |

| Figure 19. | HDLC Transmit Timing Diagram (Full Time HDLC)                                                 | 33  |

| Figure 20. | HDLC Timing Diagram - Non-GCI TDM Mode (for Start = 3, Length = 2, Negative Edge RxD Sampling | 35  |

| Figure 21. | GCI/SCIT Slave and Master Timing Diagram                                                      | 37  |

| Figure 22. | 380C Processor Core Register Set                                                              | 50  |

| Figure 23. | 16550 MIMIC Block Diagram                                                                     | 56  |

| Figure 24. | 16550 MIMIC Receiver FIFO Block Diagram                                                       | 57  |

| Figure 25. | 16550 MIMIC Transmitter FIFO Block Diagram                                                    | 58  |

| Figure 26. | Plug-and-Play Interface Block Diagram                                                         | 62  |

| Figure 27. | PCMCIA Interface Block Diagram                                                                | 65  |

| Figure 28. | PCMCIA Attribute Memory Organization                                                          | 66  |

| Figure 29. | General Format of a DMA List Entry                                                            | 68  |

| Figure 30. | Asynchronous Serial Communications Interface (ASCI) Block Diagram                             | 74  |

| Figure 31. | HDLC Channel Block Diagram (One of Three Channels Illustrated)                                | 78  |

| Figure 32  | GCI/SCIT Frame Structure                                                                      | 83  |

Table 1. Pin Numbers and Input/Output Classifications (Continued)

| Pin                | Input Class <sup>1</sup> | Output Class <sup>1</sup> | Pin Number(s)                        |

|--------------------|--------------------------|---------------------------|--------------------------------------|

| ĪNT0-3             | R                        |                           | 136 - 139                            |

| ĪORD               | ļ                        | 3                         | 125                                  |

| ĪORQ               | I                        | 3                         | 115                                  |

| ĪOWR               | I                        | 3                         | 123                                  |

| M1                 |                          | 3                         | 116                                  |

| MRD                | I                        | 3                         | 126                                  |

| MSIZE              | I                        | D                         | 117                                  |

| MWR                | I                        | 3                         | 124                                  |

| NMI                | R                        |                           | 135                                  |

| RAMCSL             |                          | 0                         | 43                                   |

| RESET              | R                        | D                         | 134                                  |

| ROMCS              | 0                        |                           | 42                                   |

| RTS0/HINT2/STSCHG  |                          | Н                         | 88                                   |

| STNBY              |                          | 0                         | 120                                  |

| TXEN1-0/RTS1-0     |                          | 0                         | 94 -93                               |

| WAIT               | I                        | D                         | 130                                  |

| A23-0              | I                        | 3                         | 141 - 144, 1 - 4, 6 - 13,<br>15 - 22 |

| BUSCLK             |                          | Н                         | 127                                  |

| CKA0/HDRQ1/PCRESET |                          | Н                         | 92                                   |

| CKA1/HA10          |                          | 3                         | 65                                   |

| CKS/HA11           |                          | 3                         | 64                                   |

| CLKI               | R                        |                           | 128                                  |

| CLKO               |                          | 0                         | 129                                  |

| D15-0              | I                        | 3                         | 24 - 31, 33 - 40                     |

| DCL/RXC2/BCL2      | I                        |                           | 106                                  |

| DD/TXD2            | I                        | D (DD)<br>O (TXD2)        | 107                                  |

| DU/TXC2/FSC2       | I                        | D (DU)<br>O (TXC2, FSC2)  | 105                                  |

| FSC/RXD2           | 1                        |                           | 108                                  |

18

Figure 5. Host - PCMCIA Attribute Memory Read Timing Diagram

Figure 8. Host - PCMCIA I/O Write Timing Diagram

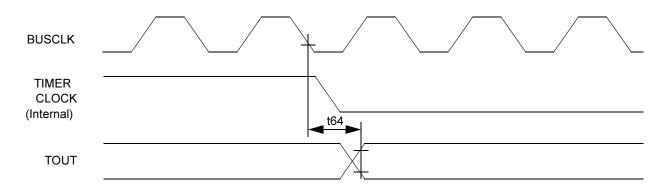

### **Timer Output Timing (See Figure 9)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF for outputs.}$

**Table 10. Timer Output Timing**

|        |                          | Z80382 |      | Z8L382 |      |       |  |

|--------|--------------------------|--------|------|--------|------|-------|--|

| Symbol | Parameter                | Min.   | Max. | Min.   | Max. | Units |  |

| t64    | BUSCLK Low to TOUT Valid |        | 20   |        | 20   | ns    |  |

Figure 9. Timer Output Timing Diagram

34

# HDLC Timing - Non-GCI TDM mode (See Figure 20)

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF}$  for outputs

Table 18. HDLC Timing - Non-GCI TDM Mode

|             |                                            | Z80382          |               | Z8L382      |         |       |

|-------------|--------------------------------------------|-----------------|---------------|-------------|---------|-------|

| Symbol      | Parameter                                  | Min.            | Max.          | Min.        | Max.    | Units |

| t120        | FSC Setup to BCL Fall                      | 30              |               | 50          |         | ns    |

| t121        | FSC Hold from BCL Low                      | 20              |               | 30          |         | ns    |

| t122        | BCL Period                                 | 50              |               | 50          |         | ns    |

| t123        | BCL High Time                              | 15              |               | 15          |         | ns    |

| t124        | BCL Low Time                               | 15              |               | 15          |         | ns    |

| t125        | BCL High to TxEN Low                       |                 | 15            |             | 20      | ns    |

| t126        | BCL High to TxEN High                      |                 | 15            |             | 20      | ns    |

| t127        | BCL High to TxD Valid                      |                 | 15            |             | 20      | ns    |

| t128        | BCL High to TxD Invalid                    | 15              |               | 20          |         | ns    |

| t129        | RxD Setup to BCL Fall (Rise) <sup>1</sup>  | 15              |               | 20          |         | ns    |

| t130        | RxD Hold from BCL Low (High) <sup>1</sup>  | 5               |               | 5           |         | ns    |

| Note: 1. Re | eceive clock sampling edge is configurable | by means of RIF | Rn[6]. See Z8 | 0382 User M | lanual. |       |

Table 19. GCI/SCIT Timing - Slave Characteristics (Continued)

|        |                                         | Z80382 |      | Z8L382 |      |       |

|--------|-----------------------------------------|--------|------|--------|------|-------|

| Symbol | Parameter                               | Min.   | Max. | Min.   | Max. | Units |

| t137   | FSC High to DU/DD Transmit Data Valid   |        | 15   |        | 20   | ns    |

| t138   | DU/DD Receive Data Setup to DCL Fall    | 15     |      | 20     |      | ns    |

| t139   | DU/DD Receive Data Hold from DCL<br>Low | 0      |      | 0      |      | ns    |

# **GCI/SCIT Timing - Master Characteristics (See Figure 21)**

Specifications apply over Standard Operating Conditions unless otherwise noted.  $C_L = 50 \text{ pF for outputs.}$

Table 20. GCI/SCIT Timing - Master Characteristics

|        | _                                       | Z80  | 382  | Z8L382 |      |       |

|--------|-----------------------------------------|------|------|--------|------|-------|

| Symbol | Parameter                               | Min. | Max. | Min.   | Max. | Units |

| t131   | DCL Data Clock Rise/Fall Time           |      | 5    |        | 10   | ns    |

| t132   | DCL Clock Period                        | 50   |      | 50     |      | ns    |

| t133   | DCL Pulse Width High                    | 15   |      | 15     |      | ns    |

| t134   | FSC Setup to DCL Fall                   | 30   |      | 30     |      | ns    |

| t135   | FSC Hold from DCL Low                   | 5    |      | 10     |      | ns    |

| t136   | DCL High to DU/DD Transmit Data Valid   |      | 15   |        | 20   | ns    |

| t137   | FSC High to DU/DD Transmit Data Valid   |      | 15   |        | 20   | ns    |

| t138   | DU/DD Receive Data Setup to DCL Fall    | 15   |      | 20     |      | ns    |

| t139   | DU/DD Receive Data Hold from DCL<br>Low | 0 0  |      | ns     |      |       |

| t140   | FSC High from DCL High                  | 0    |      | 0      |      | ns    |

Table 21. Multiprocessor Unit (MPU) Signals

| Pin Name | Pin<br>Number(s)                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A23 - 0  | 141 - 144,<br>1 - 4, 6 - 13,<br>15 - 22 | Address Bus (outputs, active High, 3-state): These non-multiplexed address signals provide a linear memory address space of 16 MB. The address signals are also used to access I/O devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BUSACK   | 132                                     | Bus Acknowledge (output, active Low, 3-state): This signal, when asserted, indicates that the 380C has accepted an external bus request and has 3-stated its output drivers for the address bus, databus and the bus control signals TREFR, TREFA, TREFC, BHEN, BLEN, MRD, MWR, IORQ, IORD, and IOWR.  The 380C cannot provide any DRAM refresh transactions while it is in the bus acknowledge state.                                                                                                                                                                                                                                                                                                                                             |

| BHEN     | 118                                     | Byte High Enable (output, active Low, 3-state): This signal is asserted at the beginning of a memory or refresh transaction, to request an operation on D15-8. If software initiates a 16-bit memory operation, but MSIZE is asserted indicating a byte-wide memory, only the data on D7-0 is transferred in the current transaction, and another transaction is performed to transfer the other data byte, also on D7-0. See note in the next paragraph under BLEN pin description.                                                                                                                                                                                                                                                               |

| BLEN     | 119                                     | Byte Low Enable (output, active Low, 3-state): This signal is asserted at the beginning of a memory or refresh transaction, to request an operation on D7-0. If software initiates a 16-bit memory transaction, but MSIZE is asserted indicating a byte-wide memory, only the data on D7-0 is transferred in the current transaction, and another transaction is performed to transfer the other data byte, also on D7-0.  Note: To align Z382 documentation and terminology with historical Z80 and industry practice, the names of the BHEN and BLEN pins, as well as the D15-8 and D7-0 pins, have been swapped on the Z382 compared to the Z380. This fact should be significant only for those using a Z380 Emulator in a Z382-based project. |

| BUSREQ   | 133                                     | Bus Request (input, active Low): When this signal is asserted, an external bus master is requesting control of the bus. BREQ has higher priority than all nonmaskable and maskable interrupt requests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BUSCLK   | 127                                     | <b>Bus Clock</b> (output, active High, 3-state): This signal is the reference edge for the majority of other signals generated by the 380C. Its frequency may be that of the CLKI pin, or CLKI divided by two or times two.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 21. Multiprocessor Unit (MPU) Signals (Continued)

|                      |                    | . , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name             | Pin<br>Number(s)   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| D15-0                | 24 - 31<br>33 - 40 | <b>D15-0 Data Bus</b> (input/output, active High, 3-state): This bidirectional 16-bit data bus is used for data transfer between the 380C and memory or I/O devices. In a memory word transfer, the even-addressed (A0=0) byte is transferred on D7-0, and the odd-addressed (A0=1) byte on D15-8. 8-bit memories should be connected to D7-0, while 8-bit I/O devices should be attached to D15-8 (this difference tends to equalize electrical loading). (See note under BLEN pin description on page 38.)                                                      |  |  |

| HALT<br>STNBY        | 121<br>120         | <b>HALT, STANDBY Status</b> (outputs, active Low): These two outputs indicate the status of the Z382 as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                      |                    | STNBY HALT Mode H H Normal instruction execution H L HALT instruction L H SLEEP Mode: clock runs but is blocked from most of the chip L L STANDBY Mode: oscillator is stopped                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| INT3<br>INT2<br>INT1 | 139<br>138<br>137  | Interrupt Requests (inputs, active Low): Asynchronous maskable interrupt inputs. Can be selected as low- or high-level sensitive, or as falling- or rising-edge triggered.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| ĪNT0                 | 136                | Interrupt Request (input, active Low): INTO is logically ORed (positive-logic ANDed) with the interrupt requests from the on-chip MIMIC, DMAs, and HDLC controllers, to create the processor's INTO input.                                                                                                                                                                                                                                                                                                                                                        |  |  |

| IOCLK                | 114                | Input/Output Clock (output, active High, 3-state): This signal is a program controlled divided-down version of BUSCLK. The division factor can be two, four, six or eight with I/O transactions and interrupt-acknowledge transactions occurring relative to IOCLK. IOCLK can be disabled, in which case BUSCLK is the timing reference for I/O transactions.  Note: The INTACK output of the Z380 has been omitted on the Z382 for pinning reasons. A similar signal can be easily obtained by low-active-ANDing (positive-logic ORing) the M1 and IORQ outputs. |  |  |

| IORQ                 | 115                | <b>Input/Output Request</b> (output, active Low, 3-state): This signal is active during all I/O read and write transactions and interrupt acknowledge transactions.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| IORD                 | 125                | Input/Output Read Strobe (output, active Low, 3-state): This signal is used to strobe data from the peripherals during I/O read transactions.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| IOWR                 | 123                | Input/Output Write Strobe (output, active Low, 3-state): This signal is used to strobe data into the peripherals during I/O write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| IOCS1<br>IOCS2       | 45<br>46           | <b>Input/Output Chip Select</b> (output, active Low): These outputs may be used to access external I/O devices. The base I/O address and range are programmable.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

Table 21. Multiprocessor Unit (MPU) Signals (Continued)

| Pin Name | Pin<br>Number(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M1       | 116              | <b>Machine Cycle One</b> (output, active Low, 3-state): This signal is active during instruction fetch and interrupt acknowledge transactions. The Z382 does not support RETI decoding by Z80 peripherals (PIO, SIO, and CTC). It does support Z80-type interrupt daisy-chaining by devices that include explicit clearing of IUS (for example, SCC).                                                                                                                                                                                                                                                                                   |

| MRD      | 126              | <b>Memory Read</b> (output, active Low, 3-state): This signal indicates that the addressed memory location places its data on the data bus. MRD is active from the end of T1 until the end of T4 during memory read transactions.                                                                                                                                                                                                                                                                                                                                                                                                       |

| MSIZE    | 117              | <b>Memory Size</b> (input/open-drain output, active Low): In 16-bit memory operations, this signal indicates whether the addressed memory location is word size (logic High) or byte size (logic Low). In the latter case, the 8-bit memory is connected to the D7-0 lines, and an additional memory transaction on D7-0 automatically is generated to transfe <u>r the other byte of the word.</u> (See the note on pin name swapping after the BLEN pin description on page 38) MSIZE is driven as an open-drain output by the memory decoding modules, when they are enabled in 8-bit mode and the address falls within their range. |

| MWR      | 124              | Memory Write (output, active Low, 3-state): This signal indicates that the addressed memory location stores the data on the databus, as qualified by BHEN and BLEN. MWR is active from the end of T2 until the end of T4 during memory write transactions.                                                                                                                                                                                                                                                                                                                                                                              |

| NMI      | 135              | Nonmaskable Interrupt (input, falling edge-trigg <u>ered): This</u> input has higher priority than the maskable interrupt inputs INT3-INT0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RESET    | 134              | <b>Reset</b> (input, active Low): This input must be active <u>for a minimum</u> of five BUSCLK periods to initialize the Z382. The effect of RESET is described in detail in the Reset section.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ROMCS    | 42               | ROM Chip Select (output, active Low): After Reset, the Z382 drives this output and MSIZE Low for all memory accesses with A23=0. Software can program the chip select logic to assert ROMCS for a different range of memory addresses. If ROM is 16 bits wide and composed of two 8-bit devices, connect the Chip Select inputs of both devices to ROMCS, and program the hardware not to force MSIZE Low in the first two instructions of the ROM code.                                                                                                                                                                                |

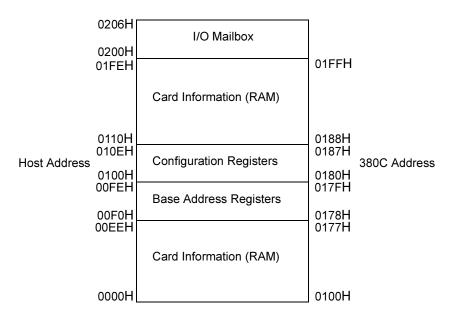

On the Host side, attribute memory is accessible only on even byte addresses. On the 380C side attribute memory can be accessed as bytes or words.

Figure 28. PCMCIA Attribute Memory Organization

#### **Base Address Registers**

These seven registers are written by the 380C with the base addresses of 8-byte windows in the host's I/O address space which the host can use to communicate with the host-accessible registers in the MIMIC.

#### **Configuration Registers**

There are five configuration registers of the PCMCIA 3.0 standard and in addition a version number register, two image base address registers, and the seven base address registers described in the previous paragraph. The Host accesses these registers to configure the interface and to retrieve status.

**Configuration Option Register.** This register is used on one side to configure the PCMCIA interface, controlling items such as type of interrupt, DMA enable, and selection of the Base Address Register. On the other side, a reset can be triggered by setting a certain bit.

**Card Configuration and Status Register.** This register contains information about the status of the interface, including whether certain signals have changed, interrupts, and power down.

#### **Monitor Channel Operation**

The monitor channels are full duplex and operate on a pseudo-asynchronous basis, in other words, data transfers take place synchronized to frame sync but the flow is controlled by a handshake procedure using the MX and MR bits. Figure 32 illustrates the handshake procedure (flow of events).

**Idle.** The MX and MR pair being held inactive (High) for two or more frames constitutes the channel being idle in that direction. The data received in the monitor channel is invalid and should be 11111111.

**Start of Transmission.** The first byte of data is placed on the bus and MX is activated (Low). MX remains active, and the data is repeated until an inactive-to-active transition of MR is received, indicating that the data has been captured by the receiver.

**Subsequent Transmissions.** The second and subsequent bytes are placed on the bus after the inactive to active transition of MR. At the time that the second byte is transmitted, MX is returned inactive for one frame time only; the data is valid in the same frame. In the following frame, MX returns active again and the same byte is transmitted. Data is repeated in subsequent frames and MX remains active until acknowledgment is detected (MR transition from inactive to active).

**Maximum Speed Case.** The transmitter is capable of minimizing the delay between bytes to achieve higher data throughput than is provided by the general case described previously. The first and second bytes are transmitted normally, However, starting with the third byte, the transmitter deactivates MX and transmits new data one frame time after MR is deactivated. In this way, the transmitter anticipates that MR is reactivated, which it accomplishes one frame time after it is deactivated, unless an abort is signalled by the receiver.

**End of Message (EOM).** The transmitter sends an EOM, normally after the last byte of data has been transmitted, by not reactivating MX after deactivating it in response to MR going inactive.

**Reception.** At the time the receiver detects the first byte, indicated by the inactive-to-active transition of MX, MR is inactive. In response to the activation of MX, the data is read off the bus and MR is activated. MR remains active until the next byte is received or an end of message is detected. Subsequent data is received from the bus on each falling edge of MX, and a monitor channel receive data available interrupt is generated. The data may be valid at the time that MX went inactive, one frame time prior to going active. MR is deactivated after the data is read and reactivated one frame time later. The transmitter detects MR going inactive and anticipates its reactivation one frame later. The reception of data is terminated by the reception of an end of message indication.

**Abort.** The abort is a signal from the receiver to the transmitter indicating that the data has been missed. It is not an abort in the classical sense, which is an indica-

107

Table 42. HDLC Registers (Continued)

| Register Name                          | I/O Address | Access |

|----------------------------------------|-------------|--------|

| HDLC1 Receive Interrupt Register       | 006DH       | R/W    |

| HDLC1 Counter Access Port              | 006EH       | R/W    |

| HDLC1 DMA Select Register              | 006FH       | R/W    |

| HDLC2 Transmit Mode Register           | 0070H       | R/W    |

| HDLC2 Transmit Interrupt Register      | 0071H       | R/W    |

| HDLC2 Transmit Control/Status Register | 0072H       | R/W    |

| HDLC2 Transmit Fill Register           | 0073H       | R/W    |

| HDLC2 Receive Mode Register            | 0074H       | R/W    |

| HDLC2 Receive Interrupt Register       | 0075H       | R/W    |

| HDLC2 Counter Access Port              | 0076H       | R/W    |

| HDLC2 DMA Select Register              | 0077H       | R/W    |

Table 43. GCI/SCIT Registers

| Register Name                 | I/O Address | Access |

|-------------------------------|-------------|--------|

| GCI Control Register          | 00C0H       | R/W    |

| GCI Status Register 1         | 00C1H       | RO     |

| GCI Status Register 2         | 00C2H       | R/W    |

| GCI Interrupt Enable Register | 00C3H       | R/W    |

| MON0 Transmit Data Register   | 00C4H       | WO     |

| MON0 Receive Data Register    | 00C4H       | RO     |

| MON1 Transmit Data Register   | 00C5H       | WO     |

| MON1 Receive Data Register    | 00C5H       | RO     |

| C/I0 Transmit Data Register   | 00C6H       | WO     |

| C/I0 Receive Data Register    | 00C6H       | RO     |

| C/I1 Transmit Data Register   | 00C7H       | WO     |

| C/I1 Receive Data Register    | 00C7H       | RO     |

| memory address space 52                               | terminate 71                            |

|-------------------------------------------------------|-----------------------------------------|

| modes of operation 48                                 | types of list entries 69                |

| on-chip and external I/O address space 52             | DRAM refresh 99                         |

| primary and working registers 50                      | DU, DD 44                               |

| processor core register set 50                        |                                         |

| program counter 51                                    | =                                       |

| program counter relative addressing 53                | E                                       |

| R register 51                                         | extended status register 67             |

| register addressing 53                                |                                         |

| register space 49                                     | _                                       |

| select register 51                                    | F                                       |

| stack pointer 51 stack pointer relative addressing 53 | features 1                              |

| CSI/O                                                 | FSC 44                                  |

| block diagram 88                                      | functional description 47               |

| receive/transmit timing 25                            | μ                                       |

| registers 89                                          |                                         |

| CTS0, 1 42                                            | G                                       |

| 0100, 1 12                                            | GCI/SCIT                                |

|                                                       | clock (DCL) signal 44                   |

| D                                                     | data upstream, downstream 44            |

| D channel 83                                          | data upstream, downstream (DU, DD) sig- |

| D15-0 39                                              | nals 44                                 |

| D15-0 data bus (D15P0) signals 39                     | frame structure 83                      |

| data carrier detect 0, 1 (DCD0, 1) signals 42         | frame structure (terminal mode) 82      |

| data types 52                                         | frame sync (FSC) signal 44              |

| DC                                                    | timing-master characteristics 36        |

| characteristics 8                                     | timing-slave characteristics 35         |

| electrical characteristics 13                         | GCI/SCIT interface                      |

| DCD0, 1 42                                            | B channels 83                           |

| DCL 44                                                | bus activation and deactivation 86      |

| decoding and routing functions 67                     | C/I channel operation 86                |

| device configuration 101                              | command/indicate channels 83            |

| direct addressing 53                                  | D channel 83                            |

| DMA                                                   | frame structure 83                      |

| control register (DMACR) 73                           |                                         |

| control/status register 72                            | frame structure (terminal mode) 82      |

| select register 82                                    | intercommunication channels 83          |

| vector register (DMAVR) 73                            | monitor channel handling 85             |

| DMA channels                                          | monitor channel operation 84            |

| centralized DMA registers 73                          | monitor channels 83                     |

| DMA channel/device interface 68                       | monitor handshake timing diagram 86     |

| general format of a DMA list entry 68                 | registers 87                            |

| per-channel registers 72                              | TIC bus 83                              |

| HRD 43<br>HWR 43                              | logic 95<br>nonmaskable 40<br>priority ranking 96<br>request 39 |

|-----------------------------------------------|-----------------------------------------------------------------|

| I                                             | requests 39                                                     |

| I/O waits register 100                        | IOCLK 39                                                        |

| IEI 47                                        | IOCS1, 2 39<br>IORD 39                                          |

| IEO 47                                        | IORD 39<br>IORQ 39                                              |

| image base address registers 67               | IOWR 39                                                         |

| immediate addressing 53 indexed addressing 53 | ISA bus signals 43                                              |

| indirect register addressing 53               | ISA port 62                                                     |

| initiation key 62                             | isolation facility 62                                           |

| INPACK 45                                     | <b>,</b>                                                        |

| input class characteristics 12                |                                                                 |

| input/output                                  | L                                                               |

| bus control 99                                | list                                                            |

| chip select (IOCS1, IOCS2) signal 39          | entries 69                                                      |

| chip select registers 93                      | list address register 72                                        |

| chip selects 93                               | lock 47                                                         |

| clock (IOCLK) signal 39                       | low power STANDBY mode 99                                       |

| read strobe (IORD) signal 39                  |                                                                 |

| request (IORQ) signal 39                      | N/I                                                             |

| write strobe (IOWR) signal 39                 | M                                                               |

| input/output clock 39                         | M1 40                                                           |

| instruction set 54 INT0                       | machine cycle one (M1) signal 40                                |

| assigned interrupt vectors mode (INT1-3,      | memory read (MRD) signal 40                                     |

| PRTs, CSI/O, ASCIs) 96                        | size (MSIZE) signal 40                                          |

| interrupt registers 98                        | write (MWR) signal 40                                           |

| nonmaskable interrupt 97                      | memory address space 52                                         |

| peripherals 96                                | MIMIC host interface 54                                         |

| RETI instruction 98                           | monitor                                                         |

| trap interrupt 97                             | channel operation 84                                            |

| INTO, 1, 2, 3 39                              | channels 83                                                     |

| INT3-1 control register 98                    | MPU signals                                                     |

| intercommunication channels 83                | address bus 38                                                  |

| interface                                     | bus acknowledge 38                                              |

| version number register 67                    | bus clock 38                                                    |

| with a TDM module 79                          | bus request 38                                                  |

| interrupt 39 enable in (IEI) signal 47        | byte high/low enable 38<br>D15-0 data bus 39                    |

| enable out (IEO) signal 47                    | HALT, STANDBY status 39                                         |

| enable register 98                            | input/output                                                    |

|                                               | .11                                                             |

| pins,BLEN 38                            | DMA control 73                      |

|-----------------------------------------|-------------------------------------|

| Plug-and-Play interface 61              | DMA control/status 72               |

| port data 93                            | DMA select 82                       |

| port data and direction registers 93    | DMA vector 73                       |

| ports, parallel 44                      | extended status 67                  |

| power supply (VDD) signal 47            | GCI/SCIT 87                         |

| processor timing, 380 14                | global HDLC vector 82               |

| program counter 51                      | host interface MIMIC programming 58 |

| relative addressing 53                  | I/O chip select 93                  |

| programmable                            | I/O waits 100                       |

| low-noise driver 102                    | image base address 67               |

| programmable reload timer 90            | INT0 interrupt 98                   |

|                                         | INT-3 control 98                    |

|                                         | interface version number 67         |

| Q                                       | interrupt enable 98                 |

| QFP package diagram 111                 | list                                |

|                                         | address 72                          |

|                                         | maps, Z382 I/O 102                  |

| R                                       | maps,DMA 105                        |

| RAM and ROM chip selects 94             | maps,GCI/SCIT 107                   |

| RAM chipselect low, high (RAMCSL, RAMC- | maps,HDLC 106                       |

| SH) signal 41                           | maps,Mimic 108                      |

| RAMCSL, RAMCSH 41                       | maps,PCMCIA memory 109              |

| ratings, absolute maximum 7             | maps,Plug-and-Play ISA 109          |

| receive                                 | maps,port and new Z80382 103        |

| data 0, 1 (RXA0, 1) signals 42          | MIMIC-host interface 59             |

| receive mode and interrupt registers 82 | output drive control 102            |

| refresh registers 100                   | peripheral function control 100     |

| register 93                             | pin multiplexing 101                |

| addressing 53                           | pin replacement 67                  |

| ASCI status FIFO 76                     | port direction 93                   |

| assigned vectors base 98                | programmable reload timer 90        |

| buffer address 72                       | PRT per channel 90, 91              |

| buffer length 72                        | RAM and ROM chip select 94          |

| card configuration and status 66        | receive data FIFO 75                |

| clock control 100                       | receive mode 82                     |

| configuration option 66                 | receive shift 75                    |

| CPU flag 51                             | refresh 0, 1, 2 100                 |

| CPU index 51                            | SCC per-channel 81                  |

| CPU interrupt 51                        | socket and copy 67                  |

| CPU primary and working 50              | STANDBY mode control 100            |

| CPU R 51                                | system configuration 101            |

| CPU select 51                           | transmit data 74                    |

| CSI/O 89                                | transmit fill 82                    |

#### Z80382/Z8L382 **Z80382 Data Communications Proccessor**

```

timing references 41

TOUT 42

transmit

fill Register 82

interrupt register 82

mode register 81

transmit data 0, 1 (TXA0, 1) signals 42

trap and break register 98

TREFA, C, R 41

Tx control/status register 81

TXA0, 142

TxC0/FSC0, TxC1/FSC1, TxC2/FSC1 44

TxD0, 1, 2 44

TxEN0, TxEN1, TxEN2 44

TXS 42

type/status bytes 80

U

UART, timer and CSIO signals 42

asynchronous clock 0, 1 42

clear to send 0, 142

clocked serial receive/transmit data 42

data carrier detect 0, 1 42

receive data 0, 1 42

request

to send 0, 1 42

serial clock 42

timer out 42

transmit

data 0, 1 42

```

### V

**VDD 47** VQFP package diagram 112 VSS 47

# W

WAIT 41 wait signal 41 watch-dog timer 91 block diagram 92 registers 92

# Z

Z380 control register 67 Z80382 block diagram 5