Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 2KB (2K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 × 8                                                                   |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 10x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny204-ssfr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9.  | Nonvolatile Memory Controller (NVMCTRL) | 57  |

|-----|-----------------------------------------|-----|

|     | 9.1. Features                           |     |

|     | 9.2. Overview                           | 57  |

|     | 9.3. Functional Description             |     |

|     | 9.4. Register Summary - NVMCTRL         |     |

|     | 9.5. Register Description               |     |

| 10  | 0. Clock Controller (CLKCTRL)           |     |

|     | 10.1. Features                          | 73  |

|     | 10.2. Overview                          | 73  |

|     | 10.3. Functional Description            |     |

|     | 10.4. Register Summary - CLKCTRL        |     |

|     | 10.5. Register Description              |     |

| 11. | . Sleep Controller (SLPCTRL)            |     |

|     | 11.1. Features                          |     |

|     | 11.2. Overview                          |     |

|     | 11.3. Functional Description            |     |

|     | 11.4. Register Summary - SLPCTRL        |     |

|     | 11.5. Register Description              |     |

| 12  | . Reset Controller (RSTCTRL)            | 95  |

|     | 12.1. Features                          |     |

|     | 12.2. Overview                          |     |

|     | 12.3. Functional Description            | 96  |

|     | 12.4. Register Summary - RSTCTRL        |     |

|     | 12.5. Register Description              |     |

| 13  | B. CPU Interrupt Controller (CPUINT)    |     |

|     | 13.1. Features                          |     |

|     | 13.2. Overview                          | 102 |

|     | 13.3. Functional Description            |     |

|     | 13.4. Register Summary - CPUINT         |     |

|     | 13.5. Register Description              |     |

| 14  | . Event System (EVSYS)                  |     |

|     | 14.1. Features                          | 116 |

|     | 14.2. Overview                          | 116 |

|     | 14.3. Functional Description            |     |

|     | 14.4. Register Summary - EVSYS          | 121 |

|     | 14.5. Register Description              |     |

| 15  | . Port Multiplexer (PORTMUX)            |     |

|     | 15.1. Overview                          | 130 |

|     | 15.2. Register Summary - PORTMUX        | 131 |

|     | 15.3. Register Description              |     |

| 16  | 6. I/O Pin Configuration (PORT)         |     |

# 5. I/O Multiplexing and Considerations

## 5.1 Multiplexed Signals

## Table 5-1. PORT Function Multiplexing

| SOIC 14-pin | Pin Name (1,2) | Other/Special | ADC0  | AC0   | USART0 | SPI0 | TWI0 | TCA0 | ТСВ0 | CCL      |

|-------------|----------------|---------------|-------|-------|--------|------|------|------|------|----------|

| 10          | PA0            | RESET/UPDI    | AIN0  |       |        |      |      |      |      | LUT0-IN0 |

| 11          | PA1            |               | AIN1  |       | TXD    | MOSI | SDA  |      |      | LUT0-IN1 |

| 12          | PA2            | EVOUT0        | AIN2  |       | RxD    | MISO | SCL  |      |      | LUT0-IN2 |

| 13          | PA3            | EXTCLK        | AIN3  |       | XCK    | SCK  |      | WO3  |      |          |

| 14          | GND            |               |       |       |        |      |      |      |      |          |

| 1           | VDD            |               |       |       |        |      |      |      |      |          |

| 2           | PA4            |               | AIN4  |       | XDIR   | SS   |      | WO4  |      | LUT0-OUT |

| 3           | PA5            |               | AIN5  | OUT   |        |      |      | WO5  | WO   |          |

| 4           | PA6            |               | AIN6  | AINN0 |        | MOSI |      |      |      |          |

| 5           | PA7            |               | AIN7  | AINP0 |        | MISO |      |      |      | LUT1-OUT |

| 6           | PB3            |               |       |       | RxD    |      |      | WOO  |      |          |

| 7           | PB2            | EVOUT1        |       |       | TxD    |      |      | WO2  |      |          |

| 8           | PB1            |               | AIN10 |       | XCK    |      | SDA  | WO1  |      |          |

| 9           | PB0            |               | AIN11 |       | XDIR   |      | SCL  | WO0  |      |          |

## Note:

- 1. Pin names are of type P*xn*, with *x* being the PORT instance (A, B) and *n* the pin number. Notation for signals is PORT*x*\_PIN*n*. All pins can be used as event input.

- 2. All pins can be used for external interrupt, where pins Px2 and Px6 of each port have full asynchronous detection.

**Tip:** Signals on alternative pin locations are in typewriter font. See PORTMUX chapter for selecting the alternative pin locations.

#### 10.5.4 Main Clock Status

| Name:     | MCLKSTATUS |

|-----------|------------|

| Offset:   | 0x03       |

| Reset:    | 0x00       |

| Property: | -          |

| Bit    | 7    | 6 | 5       | 4       | 3 | 2 | 1 | 0    |

|--------|------|---|---------|---------|---|---|---|------|

|        | EXTS |   | OSC32KS | OSC20MS |   |   |   | SOSC |

| Access | R    |   | R       | R       |   |   |   | R    |

| Reset  | 0    |   | 0       | 0       |   |   |   | 0    |

#### Bit 7 – EXTS External Clock Status

| Value | Description            |

|-------|------------------------|

| 0     | EXTCLK has not started |

| 1     | EXTCLK has started     |

#### Bit 5 - OSC32KS OSCULP32K Status

The Status bit will only be available if the source is requested as the main clock or by another module. If the oscillator RUNSTDBY bit is set but the oscillator is unused/not requested, this bit will be 0.

| Value | Description             |

|-------|-------------------------|

| 0     | OSCULP32K is not stable |

| 1     | OSCULP32K is stable     |

#### Bit 4 - OSC20MS OSC20M Status

The Status bit will only be available if the source is requested as the main clock or by another module. If the oscillator RUNSTDBY bit is set but the oscillator is unused/not requested, this bit will be 0.

| Value | Description          |

|-------|----------------------|

| 0     | OSC20M is not stable |

| 1     | OSC20M is stable     |

#### Bit 0 – SOSC Main Clock Oscillator Changing

| Value | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| 0     | The clock source for CLK_MAIN is not undergoing a switch                                                 |

| 1     | The clock source for CLK_MAIN is undergoing a switch and will change as soon as the new source is stable |

#### 13.5.1 Control A

| Name:     | CTRLA                           |

|-----------|---------------------------------|

| Offset:   | 0x00                            |

| Reset:    | 0x00                            |

| Property: | Configuration Change Protection |

| Bit    | 7 | 6     | 5   | 4 | 3 | 2 | 1 | 0      |

|--------|---|-------|-----|---|---|---|---|--------|

|        |   | IVSEL | CVT |   |   |   |   | LVL0RR |

| Access |   | R/W   | R/W |   |   |   |   | R/W    |

| Reset  |   | 0     | 0   |   |   |   |   | 0      |

#### Bit 6 – IVSEL Interrupt Vector Select

If the boot section is defined, it will be placed before the application section. The actual start address of the application section is determined by the BOOTEND fuse.

This bit is protected by the Configuration Change Protection mechanism.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | Interrupt vectors are placed at the start of the application section of the Flash |

| 1     | Interrupt vectors are placed at the start of the boot section of the Flash        |

## Bit 5 – CVT Compact Vector Table

This bit is protected by the Configuration Change Protection mechanism.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | Compact Vector Table function is disabled |

| 1     | Compact Vector Table function is enabled  |

#### **Bit 0 – LVL0RR** Round Robin Priority Enable

This bit is not protected by the Configuration Change Protection mechanism.

| Value | Description                                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| 0     | Priority is fixed for priority level 0 interrupt requests: The lowest interrupt vector address has the highest priority. |

| 1     | Round Robin priority scheme is enabled for priority level 0 interrupt requests                                           |

# 15. Port Multiplexer (PORTMUX)

## 15.1 Overview

The Port Multiplexer (PORTMUX) can either enable or disable functionality of pins, or change between default and alternative pin positions. This depends on the actual pin and property and is described in detail in the PORTMUX register map.

For available pins and functionalities, refer to the Multiplexed Signals table.

#### **Related Links**

I/O Multiplexing and Considerations

## Asynchronous Sensing Pin Properties Table 16-4. Behavior Comparison of Fully/Partly Asynchronous Sense Pin

| Property                                 | Synchronous or Partly Asynchronous Sense<br>Support                                                                                                                                                | Full Asynchronous Sense<br>Support                                 |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Minimum pulse-width to trigger interrupt | Minimum one system clock cycle                                                                                                                                                                     | Less than a system clock cycle                                     |

| Waking the device<br>from sleep          | From all interrupt sense configurations from sleep<br>modes with main clock running. Only from<br>BOTHEDGES or LEVEL interrupt sense<br>configuration from sleep modes with main clock<br>stopped. | From all interrupt sense<br>configurations from all sleep<br>modes |

| Interrupt "dead time"                    | No new interrupt for three cycles after the previous                                                                                                                                               | No limitation                                                      |

| Minimum wake-up<br>pulse length          | Value on pad must be kept until the system clock has restarted                                                                                                                                     | No limitation                                                      |

## **Related Links**

#### AVR CPU SREG

#### SREG

## 16.3.4 Events

All PORT pins are asynchronous event system generators, PORT has as many event generators as there are PORT pins in the device. Each event system output from PORT is the value present on the corresponding pin if the digital input driver is enabled. If a pin input driver is disabled, the corresponding event system output is zero.

PORT has no event inputs.

#### 16.3.5 Sleep Mode Operation

With the exception of interrupts and input synchronization, all pin configurations are independent of the Sleep mode. Peripherals connected to the ports can be affected by Sleep modes, described in the respective peripherals' documentation.

The port peripheral will always use the main clock. Input synchronization will halt when this clock stops.

#### 16.3.6 Synchronization

Not applicable.

## 16.3.7 Configuration Change Protection

Not applicable.

#### 20.5.2 Control B - Normal Mode

| Name:     | CTRLB |  |  |  |  |

|-----------|-------|--|--|--|--|

| Offset:   | 0x01  |  |  |  |  |

| Reset:    | 0x00  |  |  |  |  |

| Property: | -     |  |  |  |  |

| Bit    | 7 | 6      | 5      | 4      | 3     | 2   | 1           | 0   |

|--------|---|--------|--------|--------|-------|-----|-------------|-----|

| ĺ      |   | CMP2EN | CMP1EN | CMP0EN | ALUPD |     | WGMODE[2:0] |     |

| Access |   | R/W    | R/W    | R/W    | R/W   | R/W | R/W         | R/W |

| Reset  |   | 0      | 0      | 0      | 0     | 0   | 0           | 0   |

#### Bits 4, 5, 6 - CMPEN Compare n Enable

In the FRQ or PWM Waveform Generation mode, these bits will override the PORT output register for the corresponding pin.

| Value | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 0     | Port output settings for the pin with WOn output respected                                        |

| 1     | Port output settings for pin with WOn output overridden in FRQ or PWM Waveform<br>Generation mode |

#### Bit 3 – ALUPD Auto-Lock Update

The Auto-Lock Update feature controls the Lock Update (LUPD) bit in the TCAn.CTRLE register. When ALUPD is written to '1', LUPD will be set to '1' until the Buffer Valid (CMPnBV) bits of all enabled compare channels are '1'. This condition will clear LUPD.

It will remain cleared until the next UPDATE condition, where the buffer values will be transferred to the CMPn registers and LUPD will be set to '1' again. This makes sure that CMPnBUF register values are not transferred to the CMPn registers until all enabled compare buffers are written.

| Val | lue | Description                                     |

|-----|-----|-------------------------------------------------|

| 0   |     | LUPD in TCA.CTRLE not altered by system         |

| 1   |     | LUPD in TCA.CTRLE set and cleared automatically |

#### Bits 2:0 - WGMODE[2:0] Waveform Generation Mode

These bits select the Waveform Generation mode and control the counting sequence of the counter, TOP value, UPDATE condition, interrupt condition, and type of waveform that is generated.

No waveform generation is performed in the Normal mode of operation. For all other modes, the result from the waveform generator will only be directed to the port pins if the corresponding CMPnEN bit has been set to enable this. The port pin direction must be set as output.

| WGMODE[2:0] | Group Configuration | Mode of Operation | Тор  | Update | OVF    |

|-------------|---------------------|-------------------|------|--------|--------|

| 000         | NORMAL              | Normal            | PER  | TOP    | ТОР    |

| 001         | FRQ                 | Frequency         | CMP0 | TOP    | ТОР    |

| 010         | -                   | Reserved          | -    | -      | -      |

| 011         | SINGLESLOPE         | Single-slope PWM  | PER  | BOTTOM | ВОТТОМ |

#### Table 20-5. Timer Waveform Generation Mode

## 20.7.3 Control C - Split Mode

| Name:     | CTRLC |

|-----------|-------|

| Offset:   | 0x02  |

| Reset:    | 0x00  |

| Property: | -     |

| Bit    | 7 | 6       | 5       | 4       | 3 | 2       | 1       | 0       |

|--------|---|---------|---------|---------|---|---------|---------|---------|

| ĺ      |   | HCMP2OV | HCMP10V | HCMP0OV |   | LCMP2OV | LCMP10V | LCMP0OV |

| Access |   | R/W     | R/W     | R/W     |   | R/W     | R/W     | R/W     |

| Reset  |   | 0       | 0       | 0       |   | 0       | 0       | 0       |

**Bit 6 – HCMP2OV** High byte Compare 2 Output Value See LCMP0OV.

**Bit 5 – HCMP1OV** High byte Compare 1 Output Value See LCMP0OV.

**Bit 4 – HCMP0OV** High byte Compare 0 Output Value See LCMP0OV.

**Bit 2 – LCMP2OV** Low byte Compare 2 Output Value See LCMP0OV.

**Bit 1 – LCMP1OV** Low byte Compare 1 Output Value See LCMP0OV.

## Bit 0 – LCMP0OV Low byte Compare 0 Output Value

The LCMPnOV/HCMPn bits allow direct access to the waveform generator's output compare value when the timer/counter is not enabled. This is used to set or clear the WOn output value when the timer/counter is not running.

## 21.5.7 Debug Control

| Name:     | DBGCTRL |

|-----------|---------|

| Offset:   | 0x08    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

## Bit 0 – DBGRUN Debug Run

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | The peripheral is halted in Break Debug mode and ignores events                |

| 1     | The peripheral will continue to run in Break Debug mode when the CPU is halted |

# ATtiny204/404

Universal Synchronous and Asynchronous Recei...

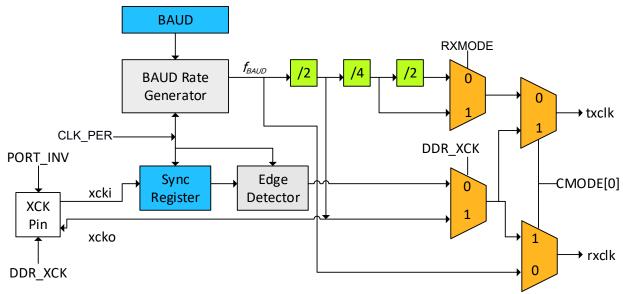

#### Figure 23-2. Clock Generation Logic Block Diagram

#### Internal Clock Generation - The Fractional Baud Rate Generator

The Baud Rate Generator is used for internal clock generation for Asynchronous modes, Asynchronous Master mode, and Master SPI mode operation. The output frequency generated ( $f_{BAUD}$ ) is determined by the baud register value (USARTn.BAUD) and the peripheral clock frequency ( $f_{CLK_PER}$ ). The following table contains equations for calculating the baud rate (in bits per second) and for calculating the USARTn.BAUD value for each mode of operation. It also shows the maximum baud rate versus peripheral clock frequency. For asynchronous operation, the USARTn.BAUD register value is 16 bits. The 10 MSb (BAUD[15:6]) hold the integer part, while the six LSb (BAUD[5:0]) hold the fractional part. In Synchronous mode, only the integer part of the BAUD register determine the baud rate.

| Operating Mode | Conditions                            | Baud Rate (Bits Per Seconds)                              | USART.BAUD Register Value<br>Calculation                  |

|----------------|---------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|

| Asynchronous   | $f_{BAUD} \le \frac{f_{CLK\_PER}}{S}$ | $f_{BAUD} = \frac{64 \times f_{CLK\_PER}}{S \times BAUD}$ | $BAUD = \frac{64 \times f_{CLK\_PER}}{S \times f_{BAUD}}$ |

| Synchronous    | $f_{BAUD} \le \frac{f_{CLK\_PER}}{2}$ | $f_{BAUD} = \frac{f_{CLK\_PER}}{2 \times BAUD[15:6]}$     | $BAUD[15:6] = \frac{f_{CLK\_PER}}{2 \times f_{BAUD}}$     |

*S* is the number of samples per bit. In Asynchronous operating mode (CMODE[0]=0), it could be set as 16 (NORMAL mode) or 8 (CLK2X mode) by RXMODE in USARTn.CTRLB. For Synchronous operating mode (CMODE[0]=1), *S* equals 2.

#### External Clock

An External clock (XCK) is used in Synchronous Slave mode operation. The XCK clock input is sampled on the peripheral clock frequency and the maximum XCK clock frequency ( $f_{XCK}$ ) is limited by the following:

$$f_{XCK} < \frac{f_{CLK\_PER}}{4}$$

© 2018 Microchip Technology Inc.

For each high and low period, the XCK clock cycles must be sampled twice by the peripheral clock. If the XCK clock has jitter, or if the high/low period duty cycle is not 50/50, the maximum XCK clock speed must be reduced accordingly.

#### Double Speed Operation

Double speed operation allows for higher baud rates under asynchronous operation with lower peripheral clock frequencies. This operation mode is enabled by writing the RXMODE bit in the Control B register (USARTn.CTRLB) to CLK2X.

When enabled, the baud rate for a given asynchronous baud rate setting shown in Table 23-2 will be doubled. In this mode, the receiver will use half the number of samples (reduced from 16 to 8) for data sampling and clock recovery. This requires a more accurate baud rate setting and peripheral clock. See Asynchronous Data Reception for more details.

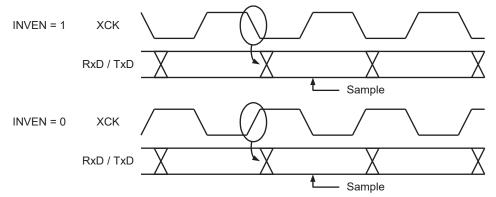

#### Synchronous Clock Operation

When Synchronous mode is used, the XCK pin controls whether the transmission clock is input (Slave mode) or output (Master mode). The corresponding port pin must be set to output for Master mode or to input for Slave mode (PORTx.DIR[n]). The normal port operation of the XCK pin will be overridden. The dependency between the clock edges and data sampling or data change is the same. Data input (on RxD) is sampled at the XCK clock edge which is opposite the edge where data output (TxD) is changed.

#### Figure 23-3. Synchronous Mode XCK Timing

The I/O pin can be inverted by writing a '1' to the Inverted I/O Enable bit (INVEN) in the Pin n Control register of the port peripheral (PORTx.PINnCTRL). Using the inverted I/O setting for the corresponding XCK port pin, the XCK clock edges used for data sampling and data change can be selected. If inverted I/O is disabled (INVEN=0), data will be changed at the rising XCK clock edge and sampled at the falling XCK clock edge. If inverted I/O is enabled (INVEN=1), data will be changed at the falling XCK clock edge and sampled at the rising XCK clock edge.

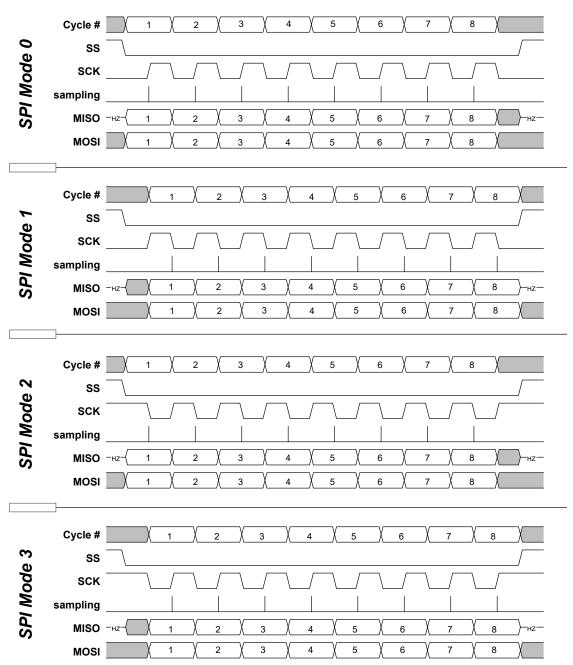

#### Master SPI Mode Clock Generation

For Master SPI mode operation, only internal clock generation is supported. This is identical to the USART Synchronous Master mode, and the baud rate or BAUD setting is calculated using the same equations (see Table 23-2).

There are four combinations of the SPI clock (SCK) phase and polarity with respect to the serial data, and these are determined by the Clock Phase bit (UCPHA) in the Control C register (USARTn.CTRLC) and the Inverted I/O Enable bit (INVEN) in the Pin n Control register of the port peripheral (PORTx.PINnCTRL). The data transfer timing diagrams are shown in Figure 23-4.

Data bits are shifted out and latched in on opposite edges of the XCK signal, ensuring sufficient time for data signals to stabilize. The settings are summarized in the table below. Changing the setting of any of these bits during transmission will corrupt both the receiver and transmitter.

© 2018 Microchip Technology Inc.

## Figure 24-5. SPI Data Transfer Modes

#### 24.3.3 Interrupts

Table 24-5. Available Interrupt Vectors and Sources

| Offset | Name | Vector Description | Conditions                                                                                                                                    |  |  |  |

|--------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0x00   | SPI  | SPI interrupt      | <ul> <li>SSI: Slave Select Trigger Interrupt</li> <li>DRE: Data Register Empty Interrupt</li> <li>TXC: Transfer Complete Interrupt</li> </ul> |  |  |  |

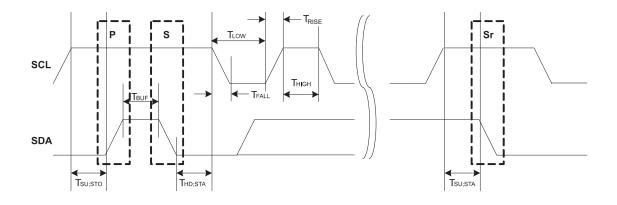

## Figure 25-14. SCL Timing

- T<sub>LOW</sub> Low period of SCL clock

- T<sub>SU:STO</sub> Setup time for Stop condition

- T<sub>BUF</sub> Bus free time between Stop and Start conditions

- T<sub>HD:STA</sub> Hold time (repeated) Start condition

- T<sub>SU:STA</sub> Setup time for repeated Start condition

- T<sub>HIGH</sub> is timed using the SCL high time count from TWI.MBAUD

- T<sub>RISE</sub> is determined by the bus impedance; for internal pull-ups. Refer to *Electrical Characteristics*.

- T<sub>FALL</sub> is determined by the open-drain current limit and bus impedance; can typically be regarded as zero. Refer to *Electrical Characteristics* for details.

The SCL frequency is given by:

$$f_{\rm SCL} = \frac{1}{T_{\rm LOW} + T_{\rm HIGH} + T_{\rm RISE}}$$

The TWI.MBAUD value is used to time both SCL high and SCL low which gives the following formula of SCL frequency:

$$f_{\rm SCL} = \frac{f_{\rm CLK\_PER}}{10 + 2BAUD + f_{\rm CLK\_PER} \cdot T_{\rm RISE}}$$

If the TWI is in Fm+ mode, only TWI.MBAUD value of three or higher is supported. This means that for Fm+ mode to achieve baud rate of 1 MHz, the peripheral clock (CLK\_PER) has to run at 16 MHz or faster.

#### **Transmitting Address Packets**

After issuing a Start condition, the master starts performing a bus transaction when the Master Address register is written with the 7-bit slave address and direction bit. If the bus is busy, the TWI master will wait until the bus becomes idle before issuing the Start condition.

Depending on arbitration and the R/W direction bit, one of four distinct cases (M1 to M4) arises following the address packet. The different cases must be handled in software.

#### Case M1: Arbitration Lost or Bus Error during Address Packet

If arbitration is lost during the sending of the address packet, both the Master Write Interrupt Flag (WIF in TWIn.MSTATUS) and Arbitration Lost Flag (ARBLOST in TWIn.MSTATUS) are set. Serial data output to the SDA line is disabled, and the SCL line is released. The master is no longer allowed to perform any operation on the bus until the bus state has changed back to idle.

0

0

#### 25.5.12 Slave Address

0

Reset

|        | Name:<br>Offset:<br>Reset:<br>Property: | SADDR<br>0x0C<br>0x00<br>- |     |      |        |     |     |     |

|--------|-----------------------------------------|----------------------------|-----|------|--------|-----|-----|-----|

| Bit    | 7                                       | 6                          | 5   | 4    | 3      | 2   | 1   | 0   |

|        |                                         |                            |     | ADDI | R[7:0] |     |     |     |

| Access | R/W                                     | R/W                        | R/W | R/W  | R/W    | R/W | R/W | R/W |

0

#### Bits 7:0 – ADDR[7:0] Address

0

0

The Slave Address register in combination with the Slave Address Mask register (TWIn.SADDRMASK) is used by the slave address match logic to determine if a master TWI device has addressed the TWI slave. The Slave Address Interrupt Flag (APIF) is set to 1 if the received address is recognized. The slave address match logic supports recognition of 7- and 10-bits addresses, and general call address.

0

0

When using 7-bit or 10-bit Address Recognition mode, the upper seven bits of the Address register (ADDR[7:1]) represents the slave address and the Least Significant bit (ADDR[0]) is used for general call address recognition. Setting the ADDR[0] bit, in this case, enables the general call address recognition logic. The TWI slave address match logic only supports recognition of the first byte of a 10-bit address (i.e., by setting ADDRA[7:1] = "0b11110aa" where "aa" represents bit 9 and 8, or the slave address). The second 10-bit address byte must be handled by software.

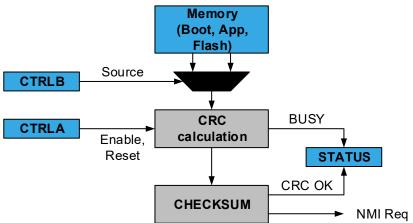

## 26.2.1 Block Diagram

Figure 26-2. Cyclic Redundancy Check Block Diagram

## 26.2.2 System Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## Table 26-1. System Product Dependencies

| Dependency                | Applicable | Peripheral |

|---------------------------|------------|------------|

| Clocks                    | Yes        | CLKCTRL    |

| I/O Lines and Connections | No         | -          |

| Interrupts                | Yes        | CPUINT     |

| Events                    | No         | -          |

| Debug                     | Yes        | UPDI       |

### **Related Links**

Clocks

Interrupts

#### 26.2.2.1 Clocks

This peripheral depends on the peripheral clock.

#### **Related Links**

Clock Controller (CLKCTRL)

## 26.2.2.2 I/O Lines and Connections

Not applicable.

## 26.2.2.3 Interrupts

Using the interrupts of this peripheral requires the interrupt controller to be configured first.

## **Related Links**

CPU Interrupt Controller (CPUINT) SREG Interrupts

## 26.5.3 Status

Name:STATUSOffset:0x02Reset:0x02Property:-

The STATUS register contains the busy and OK information. It is not writable, only readable.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0    |

|--------|---|---|---|---|---|---|----|------|

|        |   |   |   |   |   |   | OK | BUSY |

| Access |   |   |   |   | - |   | R  | R    |

| Reset  |   |   |   |   |   |   | 1  | 0    |

#### Bit 1 – OK CRC OK

When this bit is read as '1', the previous CRC completed successfully. The bit is set to '1' from Reset but is cleared to '0' when enabling. As long as the CRC module is busy, it will be read '0'. When running continuously, the CRC status must be assumed OK until it fails or is stopped by the user.

#### Bit 0 – BUSY CRC Busy

When this bit is read as '1', the CRC module is busy. As long as the module is busy, the access to the control registers is limited.

# 28. Analog Comparator (AC)

## 28.1 Features

- One Instance of the AC Controller, AC0

- Zero-Cross Detection

- Selectable Hysteresis:

- None

- 10 mV

- 25 mV

- 50 mV

- Analog Comparator Output Available on Pin

- Comparator Output Inversion Available

- Flexible Input Selection:

- One Positive pin

- One Negative pin

- Internal reference voltage

- Interrupt Generation On:

- Rising edge

- Falling edge

- Both edges

- Event Generation:

- Comparator output

## 28.2 Overview

The Analog Comparator (AC) compares the voltage levels on two inputs and gives a digital output based on this comparison. The AC can be configured to generate interrupt requests and/or events upon several different combinations of input change.

The dynamic behavior of the AC can be adjusted by a hysteresis feature. The hysteresis can be customized to optimize the operation for each application.

The input selection includes analog port pins and internal references. The analog comparator output state can also be output on a pin for use by external devices.

The AC has one positive input and one negative input. The positive input source is one of a selection of one analog input pin. The negative input is chosen either from analog input pins or from internal inputs, such as an internal voltage reference.

The digital output from the comparator is '1' when the difference between the positive and the negative input voltage is positive and '0' otherwise.

This device provides one instance of the AC controller, AC0.

#### 28.2.3.4 Events

The events of this peripheral are connected to the Event System.

#### 28.2.3.5 Debug Operation

This peripheral is unaffected by entering Debug mode.

If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during halted debugging.

## 28.3 Functional Description

#### 28.3.1 Initialization

For basic operation, follow these steps:

- Configure the desired input pins in the port peripheral

- Select the positive and negative input sources by writing the Positive and Negative Input MUX Selection bit fields (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXCTRLA)

- Optional: Enable the output to pin by writing a '1' to the Output Pad Enable bit (OUTEN) in the Control A register (AC.CTRLA)

- Enable the AC by writing a '1' to the ENABLE bit in AC.CTRLA

During the start-up time after enabling the AC, the output of the AC may be invalid.

The start-up time of the AC by itself is at most 2.5  $\mu$ s. If an internal reference is used, the reference startup time is normally longer than the AC start-up time. The VREF start-up time is 60  $\mu$ s at most.

#### 28.3.2 Operation

#### 28.3.2.1 Input Hysteresis

Applying an input hysteresis helps to prevent constant toggling of the output when the noise-afflicted input signals are close to each other.

The input hysteresis can either be disabled or have one of three levels. The hysteresis is configured by writing to the Hysteresis Mode Select bit field (HYSMODE) in the Control A register (ACn.CTRLA).

#### 28.3.2.2 Input Sources

The AC has one positive and one negative input. The inputs can be pins and internal sources, such as a voltage reference.

Each input is selected by writing to the Positive and Negative Input MUX Selection bit field (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXTRLA).

#### **Pin Inputs**

The following Analog input pins on the port can be selected as input to the analog comparator:

- AINN0

- AINP0

#### Internal Inputs

One internal input is available for the analog comparator:

AC voltage reference

#### 28.3.2.3 Low-Power Mode

For power sensitive applications, the AC provides a Low-Power mode with reduced power consumption and increased propagation delay.

#### 30.5.3 Control A

| Name:     | CTRLA |

|-----------|-------|

| Offset:   | 0x02  |

| Reset:    | 0x00  |

| Property: | -     |

| Bit    | 7     | 6 | 5    | 4   | 3   | 2   | 1          | 0   |

|--------|-------|---|------|-----|-----|-----|------------|-----|

| ĺ      | IBDLY |   | PARD | DTD | RSD |     | GTVAL[2:0] |     |

| Access | R/W   |   | R/W  | R/W | R/W | R/W | R/W        | R/W |

| Reset  | 0     |   | 0    | 0   | 0   | 0   | 0          | 0   |

#### Bit 7 – IBDLY Inter-Byte Delay Enable

Writing a '1' to this bit enables a fixed inter-byte delay between each data byte transmitted from the UPDI when doing multi-byte LD(S). The fixed length is two IDLE characters. Before the first transmitted byte, the regular GT delay used for direction change will be used.

#### Bit 5 – PARD Parity Disable

Writing this bit to '1' will disable parity detection in the UPDI by ignoring the Parity bit. This feature is recommended only during testing.

#### Bit 4 – DTD Disable Time-out Detection

Setting this bit disables the time-out detection on the PHY layer, which requests a response from the ACC layer within a specified time (65536 UPDI clock cycles).

#### Bit 3 – RSD Response Signature Disable

Writing a '1' to this bit will disable any response signatures generated by the UPDI. This is to reduce the protocol overhead to a minimum when writing large blocks of data to the NVM space. Disabling the Response Signature should be used with caution, and only when the delay experienced by the UPDI when accessing the system bus is predictable, otherwise loss of data may occur.

#### Bits 2:0 - GTVAL[2:0] Guard Time Value

This bit field selects the Guard Time Value that will be used by the UPDI when the transmission mode switches from RX to TX.

| Value | Description                           |

|-------|---------------------------------------|

| 0x0   | UPDI Guard Time: 128 cycles (default) |

| 0x1   | UPDI Guard Time: 64 cycles            |

| 0x2   | UPDI Guard Time: 32 cycles            |

| 0x3   | UPDI Guard Time: 16 cycles            |

| 0x4   | UPDI Guard Time: 8 cycles             |

| 0x5   | UPDI Guard Time: 4 cycles             |

| 0x6   | UPDI Guard Time: 2 cycles             |

| 0x7   | GT off (no extra Idle bits inserted)  |

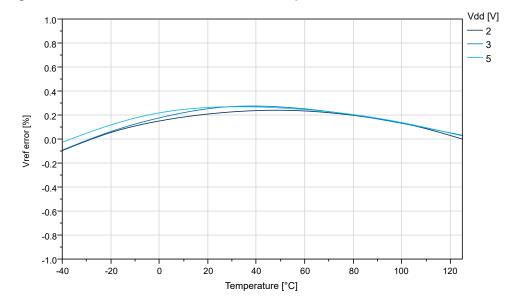

## 32.3 VREF Characteristics

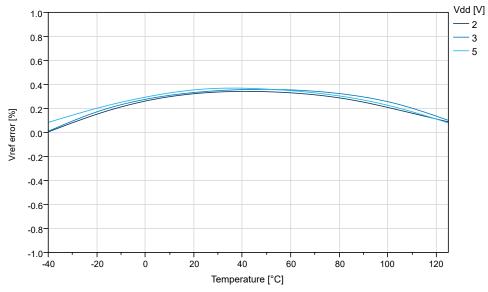

Figure 32-31. Internal 0.55V Reference vs. Temperature