Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

| 1.0   | Device Overview                             | 5    |  |  |  |  |  |

|-------|---------------------------------------------|------|--|--|--|--|--|

| 2.0   | Memory Organization                         | 9    |  |  |  |  |  |

| 3.0   | Data EEPROM and Flash Program Memory        | . 25 |  |  |  |  |  |

| 4.0   | Oscillator Configurations                   | . 33 |  |  |  |  |  |

| 5.0   | I/O Ports                                   | 39   |  |  |  |  |  |

| 6.0   | Timer0 Module                               | . 53 |  |  |  |  |  |

| 7.0   | Timer1 Module                               | . 57 |  |  |  |  |  |

| 8.0   | Timer2 Module                               | . 63 |  |  |  |  |  |

| 9.0   | Capture/Compare/PWM (CCP) Module            | . 65 |  |  |  |  |  |

| 10.0  | Synchronous Serial Port (SSP) Module        | . 71 |  |  |  |  |  |

| 11.0  | Analog-to-Digital Converter (A/D) Module    | . 81 |  |  |  |  |  |

| 12.0  | Special Features of the CPU                 | . 89 |  |  |  |  |  |

| 13.0  | Instruction Set Summary                     | 103  |  |  |  |  |  |

| 14.0  | Development Support                         | 111  |  |  |  |  |  |

| 15.0  | Electrical Characteristics                  | 115  |  |  |  |  |  |

| 16.0  | DC and AC Characteristics Graphs and Tables | 141  |  |  |  |  |  |

| 17.0  | Packaging Information                       | 155  |  |  |  |  |  |

| Appe  | ndix A: Revision History                    | 165  |  |  |  |  |  |

| Appe  | ndix B: Device Differences                  | 165  |  |  |  |  |  |

| INDE  | X                                           | 167  |  |  |  |  |  |

| The I | /icrochip Web Site                          | 173  |  |  |  |  |  |

| Custo | mer Change Notification Service             | 173  |  |  |  |  |  |

| Custo | Customer Support 173                        |      |  |  |  |  |  |

| Read  | er Response                                 | 174  |  |  |  |  |  |

| PIC1  | 6F818/819 Product Identification System     | 175  |  |  |  |  |  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

· Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### FIGURE 2-4: PIC16F819 REGISTER FILE MAP

| Д                  | File<br>ddress | ŀ                   | File<br>Address |                   | File<br>Address | A                       | File<br>ddres |

|--------------------|----------------|---------------------|-----------------|-------------------|-----------------|-------------------------|---------------|

| ndirect addr.(*)   | 00h            | Indirect addr.(*)   | 80h             | Indirect addr.(*) | 100h            | Indirect addr.(*)       | 180h          |

| TMR0               | 01h            | OPTION_REG          | 81h             | TMR0              | 101h            | OPTION_REG              | 181h          |

| PCL                | 02h            | PCL                 | 82h             | PCL               | 102h            | PCL                     | 182h          |

| STATUS             | 03h            | STATUS              | 83h             | STATUS            | 103h            | STATUS                  | 183h          |

| FSR                | 04h            | FSR                 | 84h             | FSR               | 104h            | FSR                     | 184h          |

| PORTA              | 05h            | TRISA               | 85h             |                   | 105h            |                         | 185h          |

| PORTB              | 06h            | TRISB               | 86h             | PORTB             | 106h            | TRISB                   | 186h          |

|                    | 07h            |                     | 87h             |                   | 107h            |                         | 187h          |

|                    | 08h            |                     | 88h             |                   | 108h            |                         | 188h          |

|                    | 09h            |                     | 89h             |                   | 109h            |                         | 189h          |

| PCLATH             | 0Ah            | PCLATH              | 8Ah             | PCLATH            | 10Ah            | PCLATH                  | 18Ah          |

| INTCON             | 0Bh            | INTCON              | 8Bh             | INTCON            | 10Bh            | INTCON                  | 18Bh          |

| PIR1               | 0Ch            | PIE1                | 8Ch             | EEDATA            | 10Ch            | EECON1                  | 18Ch          |

| PIR2               | 0Dh            | PIE2                | 8Dh             | EEADR             | 10Dh            | EECON2                  | 18Dh          |

| TMR1L              | 0Eh            | PCON                | 8Eh             | EEDATH            | 10Eh            | Reserved <sup>(1)</sup> | 18Eh          |

| TMR1H              | 0Fh            | OSCCON              | 8Fh             | EEADRH            | 10Fh            | Reserved <sup>(1)</sup> | 18Fh          |

| T1CON              | 10h            | OSCTUNE             | 90h             |                   | 110h            |                         | 190h          |

| TMR2               | 11h            |                     | 91h             |                   |                 |                         |               |

| T2CON              | 12h            | PR2                 | 92h             |                   |                 |                         |               |

| SSPBUF             | 13h            | SSPADD              | 93h             |                   |                 |                         |               |

| SSPCON             | 14h            | SSPSTAT             | 94h             |                   |                 |                         |               |

| CCPR1L             | 15h            |                     | 95h             |                   |                 |                         |               |

| CCPR1H             | 16h            |                     | 96h             |                   |                 |                         |               |

| CCP1CON            | 17h            |                     | 97h             |                   |                 |                         |               |

|                    | 18h            |                     | 98h             |                   |                 |                         |               |

|                    | 19h            |                     | 99h             |                   |                 |                         |               |

|                    | 1Ah            |                     | 9Ah             |                   |                 |                         |               |

|                    | 1Bh            |                     | 9Bh             |                   |                 |                         |               |

|                    | 1Ch            |                     | 9Ch             |                   |                 |                         |               |

| 4005011            | 1Dh<br>1Eb     | ADRESL              | 9Dh             |                   |                 |                         |               |

| ADRESH             | 1Eh<br>1Fh     |                     | 9Eh             |                   | 11Fh            |                         | 19Fh          |

| ADCON0             |                | ADCON1              | 9Fh             |                   | 120h            |                         | 1A0ł          |

|                    | 20h            |                     | A0h             |                   | 12011           |                         | 17101         |

|                    |                | General             |                 | General           |                 |                         |               |

| General<br>Purpose |                | Purpose<br>Register |                 | Purpose           |                 | Accesses                |               |

| Register           |                | 80 Bytes            |                 | Register          |                 | 20h-7Fh                 |               |

| 96 Bytes           |                |                     |                 | 80 Bytes          |                 |                         |               |

| ,                  |                |                     | EFh             |                   | 16Fh            |                         |               |

|                    |                | Accesses            | F0h             | Accesses          | 170h            |                         |               |

|                    | 7Fh            | 70h-7Fh             | FFh             | 70h-7Fh           | 17Fh            |                         | 1FFh          |

| Bank 0             |                | Bank 1              |                 | Bank 2            |                 | Bank 3                  |               |

|                    |                | ata memory locati   | ons, read       | <b>as</b> '0'.    |                 |                         |               |

| * Not a pł         | nysical reg    | jister.             |                 |                   |                 |                         |               |

| Address               | Name       | Bit 7                                                        | Bit 6                                              | Bit 5          | Bit 4          | Bit 3         | Bit 2                 | Bit 1           | Bit 0    | Value on<br>POR, BOR | Details on<br>page: |

|-----------------------|------------|--------------------------------------------------------------|----------------------------------------------------|----------------|----------------|---------------|-----------------------|-----------------|----------|----------------------|---------------------|

| Bank 2                | <2         |                                                              |                                                    |                |                |               |                       |                 |          |                      |                     |

| 100h <sup>(1)</sup>   | INDF       | Addressin                                                    | ng this locatio                                    | on uses conte  | ents of FSR to | address data  | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 101h                  | TMR0       | Timer0 M                                                     | lodule Regist                                      | ter            |                |               |                       |                 |          | xxxx xxxx            | 53                  |

| 102h <sup>(1</sup>    | PCL        | Program                                                      | Counter's (P                                       | C) Least Sigr  | ificant Byte   |               |                       |                 |          | 0000 0000            | 23                  |

| 103h <sup>(1)</sup>   | STATUS     | IRP                                                          | RP1                                                | RP0            | TO             | PD            | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 104h <sup>(1)</sup>   | FSR        | Indirect D                                                   | ata Memory                                         | Address Poir   | nter           |               |                       |                 |          | xxxx xxxx            | 23                  |

| 105h                  | —          | Unimpler                                                     | nented                                             |                |                |               |                       |                 |          | _                    | —                   |

| 106h                  | PORTB      | PORTB [                                                      | Data Latch w                                       | hen written; P | ORTB pins w    | hen read      |                       |                 |          | XXXX XXXX            | 43                  |

| 107h                  | —          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          | —                    | _                   |

| 108h                  | —          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          | —                    | —                   |

| 109h                  | —          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          | —                    | —                   |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _                                                            | —                                                  | _              | Write Buffer   | for the upper | 5 bits of the F       | Program Cou     | nter     | 0 0000               | 23                  |

| 10Bh <sup>(1)</sup>   | INTCON     | GIE                                                          | PEIE                                               | TMR0IE         | INTE           | RBIE          | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 10Ch                  | EEDATA     | EEPROM                                                       | I/Flash Data                                       | Register Low   | Byte           |               |                       |                 |          | xxxx xxxx            | 25                  |

| 10Dh                  | EEADR      | EEPROM                                                       | 1/Flash Addre                                      | ess Register L | ow Byte        |               |                       |                 |          | xxxx xxxx            | 25                  |

| 10Eh                  | EEDATH     | _                                                            | — EEPROM/Flash Data Register High Byte             |                |                |               |                       |                 |          | xx xxxx              | 25                  |

| 10Fh                  | EEADRH     | —                                                            | —                                                  | —              | —              | —             | EEPROM/F<br>High Byte | lash Address    | Register | xxx                  | 25                  |

| Bank 3                |            |                                                              |                                                    |                |                |               |                       |                 |          |                      |                     |

| 180h <sup>(1)</sup>   | INDF       | Addressin                                                    | ng this locatio                                    | on uses conte  | ents of FSR to | address data  | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 181h                  | OPTION_REG | RBPU                                                         | INTEDG                                             | TOCS           | TOSE           | PSA           | PS2                   | PS1             | PS0      | 1111 1111            | 17, 54              |

| 182h <sup>(1)</sup>   | PCL        | Program                                                      | Counter's (P                                       | C) Least Sigr  | ificant Byte   |               |                       |                 |          | 0000 0000            | 23                  |

| 183h <sup>(1)</sup>   | STATUS     | IRP                                                          | RP1                                                | RP0            | TO             | PD            | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 184h <sup>(1)</sup>   | FSR        | Indirect D                                                   | ata Memory                                         | Address Poir   | nter           |               |                       |                 |          | xxxx xxxx            | 23                  |

| 185h                  | —          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          | —                    | _                   |

| 186h                  | TRISB      | PORTB [                                                      | Data Direction                                     | n Register     |                |               |                       |                 |          | 1111 1111            | 43                  |

| 187h                  | _          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          | _                    | —                   |

| 188h                  | _          | Unimplen                                                     | nented                                             |                |                |               |                       |                 |          |                      | —                   |

| 189h                  | _          | Unimplen                                                     | Unimplemented                                      |                |                |               |                       |                 |          | —                    |                     |

| 18Ah <sup>(1,2)</sup> | PCLATH     | — — Write Buffer for the upper 5 bits of the Program Counter |                                                    |                |                |               |                       | 0 0000          | 23       |                      |                     |

| 18Bh <sup>(1)</sup>   | INTCON     | GIE                                                          | PEIE                                               | TMR0IE         | INTE           | RBIE          | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 18Ch                  | EECON1     | EEPGD                                                        | _                                                  | _              | FREE           | WRERR         | WREN                  | WR              | RD       | xx x000              | 26                  |

|                       | 1          |                                                              | EPROM Control Register 2 (not a physical register) |                |                |               |                       |                 |          |                      | 25                  |

| 18Dh                  | EECON2     | LEFRON                                                       | eserved; maintain clear                            |                |                |               |                       |                 |          |                      |                     |

| 18Dh<br>18Eh          | EECON2     |                                                              |                                                    |                | p, e.e         | ,             |                       |                 |          | 0000 0000            | —                   |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

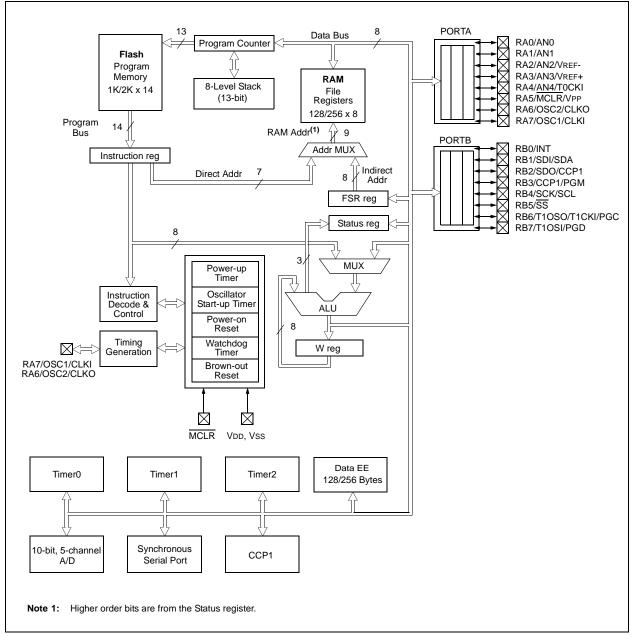

### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

| EXAMPLE 3-4: | ERASING A FLASH PROGRAM MEMORY ROW |

|--------------|------------------------------------|

|--------------|------------------------------------|

|           | BANKSEL | EEADRH      | ;        | Select Bank of EEADRH                                |

|-----------|---------|-------------|----------|------------------------------------------------------|

|           | MOVF    | ADDRH, W    | ;        |                                                      |

|           | MOVWF   | EEADRH      | ;        | MS Byte of Program Address to Erase                  |

|           | MOVF    | ADDRL, W    | ;        |                                                      |

|           | MOVWF   | EEADR       | ;        | LS Byte of Program Address to Erase                  |

| ERASE ROW |         |             |          |                                                      |

| _         | BANKSEL | EECON1      | ;        | Select Bank of EECON1                                |

|           | BSF     | EECON1, EEE | GD ;     | Point to PROGRAM memory                              |

|           | BSF     | EECON1, WRE | EN ;     | Enable Write to memory                               |

|           | BSF     | EECON1, FRE | EE ;     | Enable Row Erase operation                           |

| ;         |         |             |          |                                                      |

|           | BCF     | INTCON, GIE | s;       | Disable interrupts (if using)                        |

|           | MOVLW   | 55h         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write 55h                                            |

|           | MOVLW   | AAh         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write AAh                                            |

|           | BSF     | EECON1, WR  | ;        | Start Erase (CPU stall)                              |

|           | NOP     |             | ;        | Any instructions here are ignored as processor       |

|           |         |             | ;        | halts to begin Erase sequence                        |

|           | NOP     |             | ;        | processor will stop here and wait for Erase complete |

|           |         |             | ;        | after Erase processor continues with 3rd instruction |

|           | BCF     | EECON1, FRE | EE ;     | Disable Row Erase operation                          |

|           | BCF     | EECON1, WRE | EN ;     | Disable writes                                       |

|           | BSF     | INTCON, GIE | ·<br>; 2 | Enable interrupts (if using)                         |

|           |         |             |          |                                                      |

#### 4.5.2 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the application. This is done by writing to the OSCTUNE register (Register 4-1). The tuning sensitivity is constant throughout the tuning range. The OSCTUNE register has a tuning range of  $\pm 12.5\%$ .

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately 8 \* 32  $\mu$ s = 256  $\mu$ s); the INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the 31.25 kHz INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

#### REGISTER 4-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | ,<br>R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|------------|-------|

| —     | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1       | TUN0  |

| bit 7 |     |       |       |       |       |            | bit 0 |

bit 7-6 Unimplemented: Read as '0'

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

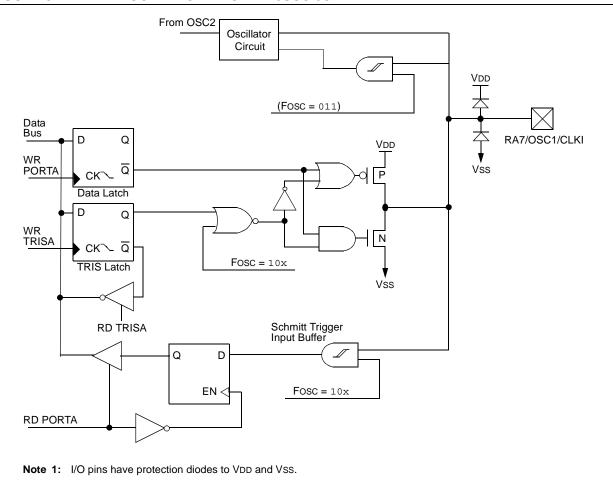

## 5.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

### 5.1 PORTA and the TRISA Register

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On    | а     | Pow    | /er-or | n Reset,   | the | pins   |

|-------|-------|-------|--------|--------|------------|-----|--------|

|       | POR   | TA<   | :4:0>  | are    | configured | as  | analog |

|       | input | ts ar | nd rea | ad as  | '0'.       |     |        |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input and with an analog input to become the RA4/AN4/ T0CKI pin. The RA4/AN4/T0CKI pin is a Schmitt Trigger input and full CMOS output driver.

Pin RA5 is multiplexed with the Master Clear module input. The RA5/MCLR/VPP pin is a Schmitt Trigger input.

Pin RA6 is multiplexed with the oscillator module input and external oscillator output. Pin RA7 is multiplexed with the oscillator module input and external oscillator input. Pin RA6/OSC2/CLKO and pin RA7/OSC1/CLKI are Schmitt Trigger inputs and full CMOS output drivers.

Pins RA<1:0> are multiplexed with analog inputs. Pins RA<3:2> are multiplexed with analog inputs and VREF inputs. Pins RA<3:0> have TTL inputs and full CMOS output drivers.

| EXAMPLE 5-1:                            | INITIALIZING PORTA |

|-----------------------------------------|--------------------|

| $L \land A W \square L L J^{-} \square$ |                    |

| BANKSEL | PORTA  | ; select bank of PORTA  |

|---------|--------|-------------------------|

| CLRF    | PORTA  | ; Initialize PORTA by   |

|         |        | ; clearing output       |

|         |        | ; data latches          |

| BANKSEL | ADCON1 | ; Select Bank of ADCON1 |

| MOVLW   | 0x06   | ; Configure all pins    |

| MOVWF   | ADCON1 | ; as digital inputs     |

| MOVLW   | 0xFF   | ; Value used to         |

|         |        | ; initialize data       |

|         |        | ; direction             |

| MOVWF   | TRISA  | ; Set RA<7:0> as inputs |

| Name          | Bit#  | Buffer                 | Function                                                                                                                                     |

|---------------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0       | bit 0 | TTL                    | Input/output or analog input.                                                                                                                |

| RA1/AN1       | bit 1 | TTL                    | Input/output or analog input.                                                                                                                |

| RA2/AN2/VREF- | bit 2 | TTL                    | Input/output, analog input or VREF                                                                                                           |

| RA3/AN3/VREF+ | bit 3 | TTL                    | Input/output, analog input or VREF+.                                                                                                         |

| RA4/AN4/T0CKI | bit 4 | ST                     | Input/output, analog input or external clock input for Timer0.                                                                               |

| RA5/MCLR/VPP  | bit 5 | ST                     | Input, Master Clear (Reset) or programming voltage input.                                                                                    |

| RA6/OSC2/CLKO | bit 6 | ST                     | Input/output, connects to crystal or resonator, oscillator output or 1/4 the frequency of OSC1 and denotes the instruction cycle in RC mode. |

| RA7/OSC1/CLKI | bit 7 | ST/CMOS <sup>(1)</sup> | Input/output, connects to crystal or resonator or oscillator input.                                                                          |

### TABLE 5-1: PORTA FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address | Name   | Bit 7  | Bit 6  | Bit 5                 | Bit 4 | Bit 3     | Bit 2      | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|---------|--------|--------|--------|-----------------------|-------|-----------|------------|--------|-------|----------------------|---------------------------|

| 05h     | PORTA  | RA7    | RA6    | RA5                   | RA4   | RA3       | RA2        | RA1    | RA0   | xxx0 0000            | uuu0 0000                 |

| 85h     | TRISA  | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | PORTA | Data Dire | ection Reg | gister |       | 1111 1111            | 1111 1111                 |

| 9Fh     | ADCON1 | ADFM   | ADCS2  |                       |       | PCFG3     | PCFG2      | PCFG1  | PCFG0 | 00 0000              | 00 0000                   |

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

NOTES:

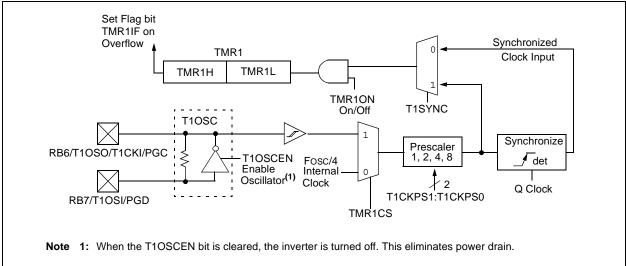

### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

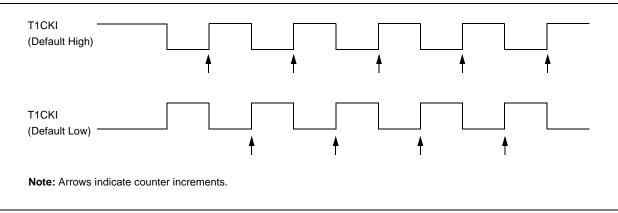

### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set, or on pin RB6/T1OSO/T1CKI/PGC when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 7-1: TIMER1 INCREMENTING EDGE

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111' | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock, |

|---------|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

|         | MOVWF                                      | TICON                                          | ; Asynchronous operation, external oscillator                                              |

|         | CLRF<br>CLRF                               | secs<br>mins                                   | ; Initialize timekeeping registers                                                         |

|         | MOVLW                                      | mins<br>.12                                    |                                                                                            |

|         | MOVLW                                      | .12<br>hours                                   |                                                                                            |

|         | BANKSEL                                    | PIE1                                           |                                                                                            |

|         | BSF                                        |                                                | ; Enable Timer1 interrupt                                                                  |

|         | RETURN                                     | ,                                              | ,                                                                                          |

| RTCisr  | BANKSEL                                    | TMR1H                                          |                                                                                            |

|         | BSF                                        | TMR1H, 7                                       | ; Preload for 1 sec overflow                                                               |

|         | BCF                                        | PIR1, TMR1IF                                   | ; Clear interrupt flag                                                                     |

|         | INCF                                       | secs, F                                        | ; Increment seconds                                                                        |

|         | MOVF                                       | secs, w                                        |                                                                                            |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | seconds                                        | ; Clear seconds                                                                            |

|         | INCF<br>MOVF                               | mins, f<br>mins, w                             | ; Increment minutes                                                                        |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     | 511105, 2                                      | ; No, done                                                                                 |

|         | CLRF                                       | mins                                           | ; Clear minutes                                                                            |

|         | INCF                                       | hours, f                                       | ; Increment hours                                                                          |

|         | MOVF                                       | hours, w                                       |                                                                                            |

|         | SUBLW                                      | .24                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 24 hours elapsed?                                                                        |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | hours                                          | ; Clear hours                                                                              |

|         | RETURN                                     |                                                | ; Done                                                                                     |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7   | Bit 6                                                                                           | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Valu<br>POR, |      | all c | e on<br>other<br>sets |

|-----------------------|--------|---------|-------------------------------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|--------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                                                                                            | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000         | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1   | _       | ADIF                                                                                            | _       | _       | SSPIF   | CCP1IF | TMR2IF | TMR1IF | - 0          | 0000 | - 0   | 0000                  |

| 8Ch                   | PIE1   | _       | ADIE                                                                                            | _       | _       | SSPIE   | CCP1IE | TMR2IE | TMR1IE | - 0          | 0000 | - 0   | 0000                  |

| 0Eh                   | TMR1L  | Holding | lolding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |         |         |         |        |        |        |              |      |       |                       |

| 0Fh                   | TMR1H  | Holding | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register                      |         |         |         |        |        |        |              |      |       |                       |

| 10h                   | T1CON  | _       | _                                                                                               | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00           | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

### 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                 | U-0        | R/W-0        | R/W-0        | R/W-0   | R/W-0      | R/W-0          | R/W-0  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|---------|------------|----------------|--------|--|--|--|

| —                                                                                                                                                                   | —          | CCP1X        | CCP1Y        | CCP1M3  | CCP1M2     | CCP1M1         | CCP1M0 |  |  |  |

| bit 7                                                                                                                                                               |            |              |              |         |            |                | bit 0  |  |  |  |

|                                                                                                                                                                     |            |              |              |         |            |                |        |  |  |  |

| Unimpleme                                                                                                                                                           |            |              |              |         |            |                |        |  |  |  |

| CCP1X:CCI                                                                                                                                                           | P1Y: PWM   | Least Signi  | ficant bits  |         |            |                |        |  |  |  |

| <u>Capture mo</u><br>Unused.                                                                                                                                        | <u>de:</u> |              |              |         |            |                |        |  |  |  |

| <u>Compare mode:</u><br>Unused.                                                                                                                                     |            |              |              |         |            |                |        |  |  |  |

| <u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                          |            |              |              |         |            |                |        |  |  |  |

| CCP1M3:CCP1M0: CCP1 Mode Select bits                                                                                                                                |            |              |              |         |            |                |        |  |  |  |

| 0000 = Capture/Compare/PWM disabled (resets CCP1 module)                                                                                                            |            |              |              |         |            |                |        |  |  |  |

| 0100 = Cap                                                                                                                                                          | ture mode, | every fallin | g edge       |         |            |                |        |  |  |  |

| 0101 <b>= Cap</b>                                                                                                                                                   |            |              |              |         |            |                |        |  |  |  |

| 0110 = Capture mode, every 4th rising edge                                                                                                                          |            |              |              |         |            |                |        |  |  |  |

| 0111 = Capture mode, every 16th rising edge                                                                                                                         |            |              |              |         |            |                |        |  |  |  |

| 1000 = Compare mode, set output on match (CCP1IF bit is set)<br>1001 = Compare mode, clear output on match (CCP1IF bit is set)                                      |            |              |              |         |            |                |        |  |  |  |

| 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)                                                               |            |              |              |         |            |                |        |  |  |  |

| 1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |            |              |              |         |            |                |        |  |  |  |

| 11xx = PWM mode                                                                                                                                                     |            |              |              |         |            |                |        |  |  |  |

|                                                                                                                                                                     |            |              |              |         |            |                |        |  |  |  |

|                                                                                                                                                                     |            |              |              |         |            |                |        |  |  |  |

| Legend:                                                                                                                                                             |            |              |              |         |            |                |        |  |  |  |

| <b>Legend:</b><br>R = Readab                                                                                                                                        | le bit     | W = V        | Vritable bit | U = Uni | mplemented | l bit, read as | s 'O'  |  |  |  |

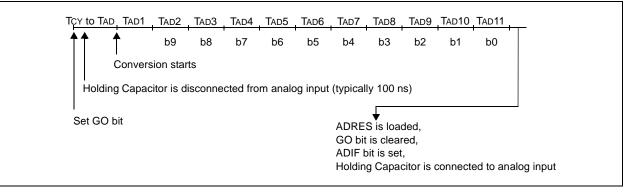

### 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2-TAD wait is required before the next acquisition is started. After this 2-TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### 11.4.1 A/D RESULT REGISTERS

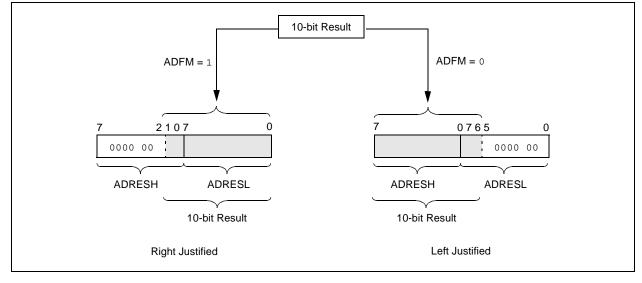

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16 bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

### FIGURE 11-3: A/D CONVERSION TAD CYCLES

### FIGURE 11-4: A/D RESULT JUSTIFICATION

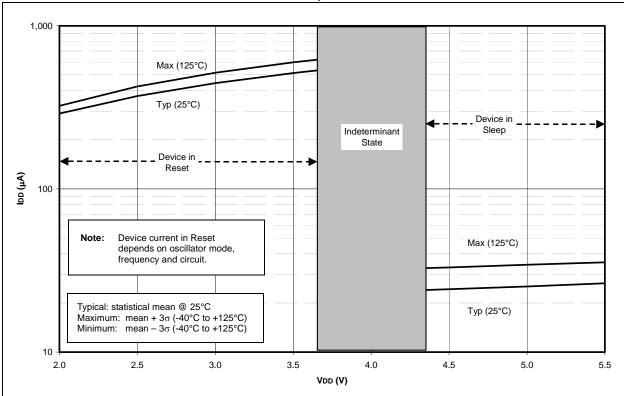

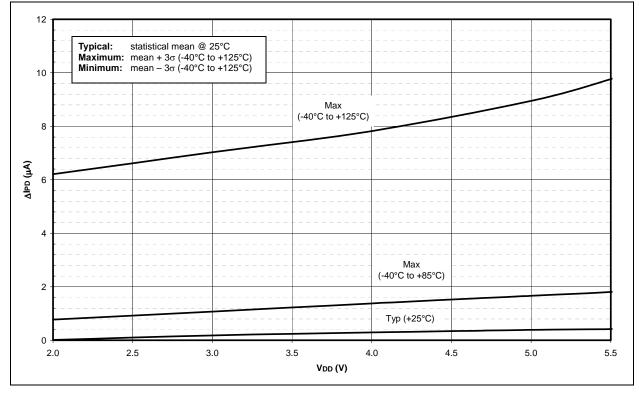

### 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF8<br>(Indus | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |     |       |        |              |                         |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|--------------|-------------------------|--|--|

| PIC16F81<br>(Indus |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |       |        |              |                         |  |  |

| Param<br>No.       | Device                                                                                                                             | Тур                                                                                                                                                                                     | Max | Units |        | Condit       | ions                    |  |  |

|                    | Supply Current (IDD) <sup>(2,3)</sup>                                                                                              |                                                                                                                                                                                         |     |       |        |              |                         |  |  |

|                    | PIC16LF818/819                                                                                                                     | .950                                                                                                                                                                                    | 1.3 | mA    | -40°C  |              |                         |  |  |

|                    |                                                                                                                                    | .930                                                                                                                                                                                    | 1.2 | mA    | +25°C  | VDD = 3.0V   |                         |  |  |

|                    |                                                                                                                                    | .930                                                                                                                                                                                    | 1.2 | mA    | +85°C  |              | Fosc = 8 MHz            |  |  |

|                    | All devices                                                                                                                        | 1.8                                                                                                                                                                                     | 3.0 | mA    | -40°C  |              | (RC_RUN mode,           |  |  |

|                    |                                                                                                                                    | 1.7                                                                                                                                                                                     | 2.8 | mA    | +25°C  | VDD = 5.0V   | Internal RC Oscillator) |  |  |

|                    |                                                                                                                                    |                                                                                                                                                                                         | 2.8 | mA    | +85°C  | י0.0∨ ≅ 5.0∨ |                         |  |  |

|                    | Extended devices                                                                                                                   | Extended devices 2.0 4.                                                                                                                                                                 |     | mA    | +125°C |              |                         |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\frac{OSC1}{MCLR}$  = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;  $\frac{MCLR}{MCLR}$  = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

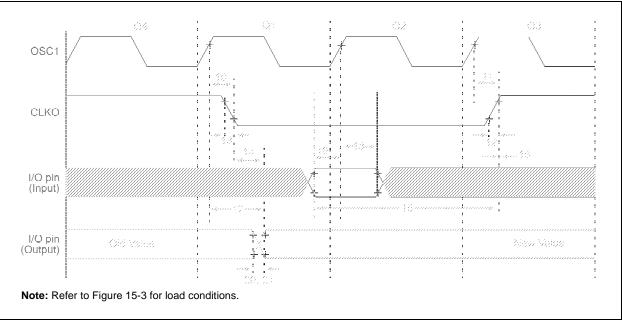

| TABLE 15-2: | CLKO AND I/O TIMING REQUIREMENTS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Param<br>No. | Symbol   | Characterist                         | Min                     | Тур† | Мах | Units        | Conditions |          |

|--------------|----------|--------------------------------------|-------------------------|------|-----|--------------|------------|----------|

| 10*          | TosH2ckL | OSC1 $\uparrow$ to CLKO $\downarrow$ |                         | _    | 75  | 200          | ns         | (Note 1) |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                     |                         | _    | 75  | 200          | ns         | (Note 1) |

| 12*          | ТскR     | CLKO Rise Time                       |                         | _    | 35  | 100          | ns         | (Note 1) |

| 13*          | ТскF     | CLKO Fall Time                       |                         | _    | 35  | 100          | ns         | (Note 1) |

| 14*          | TCKL2IOV | CLKO ↓ to Port Out Valid             |                         |      | _   | 0.5 TCY + 20 | ns         | (Note 1) |

| 15*          | ТюV2скН  | Port In Valid before CLKO 1          | Tosc + 200              | _    | —   | ns           | (Note 1)   |          |

| 16*          | TCKH2IOI | Port In Hold after CLKO ↑            | 0                       | —    | —   | ns           | (Note 1)   |          |

| 17*          | TosH2IoV | OSC1 ↑ (Q1 cycle) to Port Out        | _                       | 100  | 255 | ns           |            |          |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to Port            | PIC16F818/819           | 100  | _   | —            | ns         |          |

|              |          | Input Invalid (I/O in hold time)     | PIC16LF818/819          | 200  | —   | _            | ns         |          |

| 19*          | TIOV20SH | Port Input Valid to OSC1 1 (I/O      | in setup time)          | 0    | _   | —            | ns         |          |

| 20*          | TIOR     | Port Output Rise Time                | PIC16 <b>F</b> 818/819  |      | 10  | 40           | ns         |          |

|              |          |                                      | PIC16LF818/819          | _    | —   | 145          | ns         |          |

| 21*          | TIOF     | Port Output Fall Time                | PIC16 <b>F</b> 818/819  |      | 10  | 40           | ns         |          |

|              |          |                                      | PIC16 <b>LF</b> 818/819 |      | _   | 145          | ns         |          |

| 22††*        | TINP     | INT pin High or Low Time             | Тсү                     | —    | —   | ns           |            |          |

| 23††*        | Trbp     | RB7:RB4 Change INT High or           | Low Time                | Тсү  | -   | —            | ns         |          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events, not related to any internal clock edges.

Note 1: Measurements are taken in RC mode, where CLKO output is 4 x Tosc.

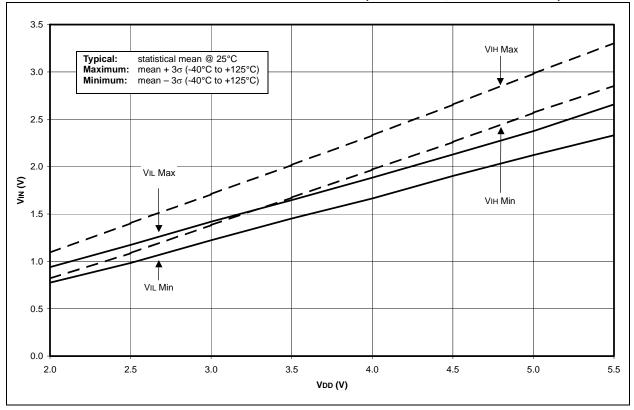

## FIGURE 16-23: MINIMUM AND MAXIMUM VIN vs. VDD (I<sup>2</sup>C<sup>™</sup> INPUT, -40°C TO +125°C)

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

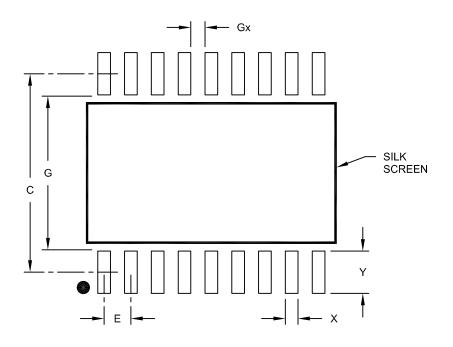

## RECOMMENDED LAND PATTERN

|                       | Units  |      |          |      |  |

|-----------------------|--------|------|----------|------|--|

| Dimension             | Limits | MIN  | NOM      | MAX  |  |

| Contact Pitch         | E      |      | 1.27 BSC |      |  |

| Contact Pad Spacing   | С      |      | 9.40     |      |  |

| Contact Pad Width     | X      |      |          | 0.60 |  |

| Contact Pad Length    | Y      |      |          | 2.00 |  |

| Distance Between Pads | Gx     | 0.67 |          |      |  |

| Distance Between Pads | G      | 7.40 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response   | Total Pages Sent                          |

|------------|-----------------------------------------------------|-------------------------------------------|

| From       | Name                                                |                                           |

|            | Company                                             |                                           |

|            | Address                                             |                                           |

|            | City / State / ZIP / Country                        |                                           |

|            | Telephone: ()                                       | FAX: ()                                   |

|            | cation (optional):                                  |                                           |

| Would      | d you like a reply?YN                               |                                           |

| Devic      | e: PIC16F818/819                                    | Literature Number: DS39598F               |

| Ques       | tions:                                              |                                           |

| 1. V       | /hat are the best features of this document?        |                                           |

|            |                                                     |                                           |

| _          |                                                     |                                           |

| 2. H       | ow does this document meet your hardware and s      | oftware development needs?                |

| _          |                                                     |                                           |

| _          |                                                     |                                           |

| 3. D       | o you find the organization of this document easy   | to follow? If not, why?                   |

|            |                                                     |                                           |

| 4 10       | /hat additions to the document do you think would   | enhance the structure and subject?        |

| 4. V       |                                                     |                                           |

| _          |                                                     |                                           |

| 5. V       | /hat deletions from the document could be made w    | vithout affecting the overall usefulness? |

|            |                                                     |                                           |

|            |                                                     |                                           |

| 6. Is      | there any incorrect or misleading information (what | at and where)?                            |

|            |                                                     |                                           |

|            |                                                     |                                           |

| 7. H       | low would you improve this document?                |                                           |

|            |                                                     |                                           |

| _          |                                                     |                                           |