Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

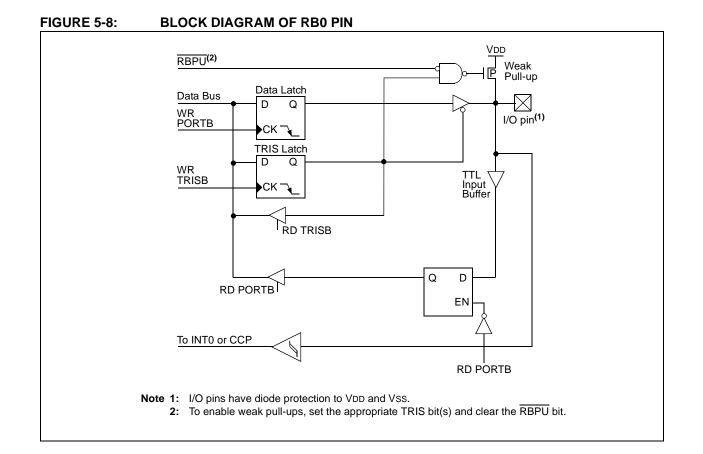

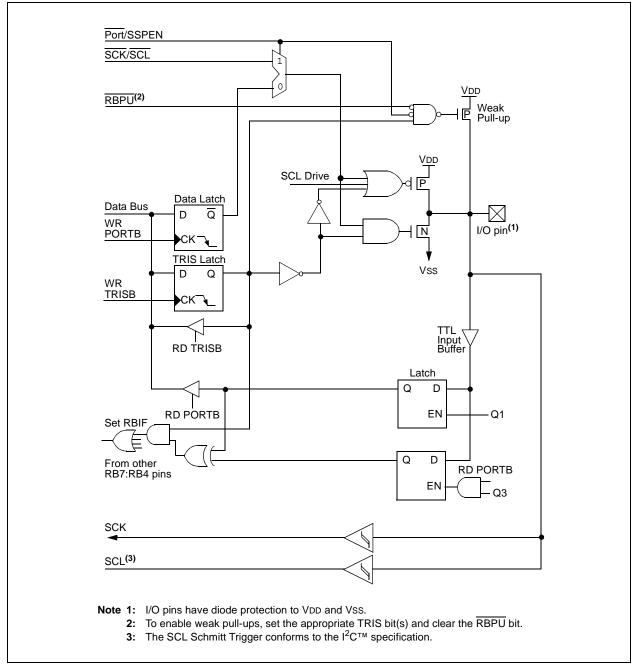

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register that contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### **REGISTER 2-2: OPTION\_REG: OPTION REGISTER (ADDRESS 81h, 181h)**

|       | R/W-1                                                                                                                 | R/W-1                                                                                                                       | R/W-1          | R/W-1      | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|------------|------------------------------------|-------|-------|-------|--|--|--|--|--|

|       | RBPU                                                                                                                  | INTEDG                                                                                                                      | TOCS           | TOSE       | PSA                                | PS2   | PS1   | PS0   |  |  |  |  |  |

|       | bit 7                                                                                                                 |                                                                                                                             |                |            |                                    |       |       | bit ( |  |  |  |  |  |

| 7     | RBPU: PO                                                                                                              | RTB Pull-up                                                                                                                 | Enable bit     |            |                                    |       |       |       |  |  |  |  |  |

|       |                                                                                                                       | <ul> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |                |            |                                    |       |       |       |  |  |  |  |  |

| t 6   | INTEDG: I                                                                                                             | INTEDG: Interrupt Edge Select bit                                                                                           |                |            |                                    |       |       |       |  |  |  |  |  |

|       | <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul> |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

| t 5   | TOCS: TMI                                                                                                             | R0 Clock Sou                                                                                                                | irce Select bi | it         |                                    |       |       |       |  |  |  |  |  |

|       | <ul> <li>1 = Transition on TOCKI pin</li> <li>0 = Internal instruction cycle clock (CLKO)</li> </ul>                  |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

| t 4   | TOSE: TM                                                                                                              | R0 Source Ec                                                                                                                | lge Select bit | t          |                                    |       |       |       |  |  |  |  |  |

|       |                                                                                                                       | nent on high-t<br>nent on low-to                                                                                            |                |            |                                    |       |       |       |  |  |  |  |  |

| t 3   | PSA: Pres                                                                                                             | PSA: Prescaler Assignment bit                                                                                               |                |            |                                    |       |       |       |  |  |  |  |  |

|       |                                                                                                                       | aler is assigne<br>aler is assigne                                                                                          |                |            |                                    |       |       |       |  |  |  |  |  |

| t 2-0 | PS2:PS0: Prescaler Rate Select bits                                                                                   |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

|       | Bit Value TMR0 Rate WDT Rate                                                                                          |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

|       | 001                                                                                                                   | 1:4                                                                                                                         | 1:2            |            |                                    |       |       |       |  |  |  |  |  |

|       | 010<br>011                                                                                                            | 1 : 8<br>1 : 16                                                                                                             | 1:4<br>1:8     |            |                                    |       |       |       |  |  |  |  |  |

|       | 100                                                                                                                   | 1:32                                                                                                                        | 1:16           |            |                                    |       |       |       |  |  |  |  |  |

|       | 101                                                                                                                   | 1:64                                                                                                                        | 1:32           |            |                                    |       |       |       |  |  |  |  |  |

|       | 110 1:128 1:64<br>111 1:256 1:128                                                                                     |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

|       |                                                                                                                       |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

|       | Legend:                                                                                                               |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

|       | R = Reada                                                                                                             | able bit                                                                                                                    | W = Wr         | itable bit | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |  |  |

|       | -n = Value at POR $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown                                    |                                                                                                                             |                |            |                                    |       |       |       |  |  |  |  |  |

#### 2.2.2.8 **PCON Register**

| Note: | Interrupt fleg bits get eet when an interrupt |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

| note: | Interrupt flag bits get set when an interrupt |  |  |  |  |  |  |  |  |

|       | condition occurs regardless of the state of   |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |  |

|       | Interrupt Enable bit, GIE (INTCON<7>).        |  |  |  |  |  |  |  |  |

|       | User software should ensure the appropri-     |  |  |  |  |  |  |  |  |

|       | ate interrupt flag bits are clear prior to    |  |  |  |  |  |  |  |  |

|       | enabling an interrupt.                        |  |  |  |  |  |  |  |  |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

-n = Value at POR

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### **REGISTER 2-8:** PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         | U-0                                                                                                                                                  | U-0 U-0      |            | U-0          | U-0      | U-0         | R/W-0        | R/W-x |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|----------|-------------|--------------|-------|--|--|--|--|--|--|

|         | _                                                                                                                                                    | _            |            | —            | _        | _           | POR          | BOR   |  |  |  |  |  |  |

|         | bit 7                                                                                                                                                |              |            |              |          |             |              |       |  |  |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                           |              |            |              |          |             |              |       |  |  |  |  |  |  |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                       |              |            |              |          |             |              |       |  |  |  |  |  |  |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>    |              |            |              |          |             |              |       |  |  |  |  |  |  |

| bit 0   | BOR: Brow                                                                                                                                            | /n-out Reset | Status bit |              |          |             |              |       |  |  |  |  |  |  |

|         | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |              |            |              |          |             |              |       |  |  |  |  |  |  |

|         | Legend:                                                                                                                                              |              |            |              |          |             |              |       |  |  |  |  |  |  |

|         | R = Reada                                                                                                                                            | able bit     | W = W      | /ritable bit | U = Unim | plemented I | bit, read as | '0'   |  |  |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

## 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| BANKSEL | EEADRH   |       | ; | Select Bank of EEADRH |

|---------|----------|-------|---|-----------------------|

| MOVF    | ADDRH, W | 1     | ; |                       |

| MOVWF   | EEADRH   |       | ; | MS Byte of Program    |

|         |          |       | ; | Address to read       |

| MOVF    | ADDRL, W | T     | ; |                       |

| MOVWF   | EEADR    |       | ; | LS Byte of Program    |

|         |          |       | ; | Address to read       |

| BANKSEL | EECON1   |       | ; | Select Bank of EECON1 |

| BSF     | EECON1,  | EEPGD | ; | Point to PROGRAM      |

|         |          |       | ; | memory                |

| BSF     | EECON1,  | RD    | ; | EE Read               |

|         |          |       | ; |                       |

| NOP     |          |       | ; | Any instructions      |

|         |          |       | ; | here are ignored as   |

| NOP     |          |       | ; | program memory is     |

|         |          |       | ; | read in second cycle  |

|         |          |       | ; | after BSF EECON1,RD   |

| BANKSEL | EEDATA   |       | ; | Select Bank of EEDATA |

| MOVF    | EEDATA,  | W     | ; | DATAL = EEDATA        |

| MOVWF   | DATAL    |       | ; |                       |

| MOVF    | EEDATH,  | W     | ; | DATAH = EEDATH        |

| MOVWF   | DATAH    |       | ; |                       |

| 1       |          |       |   |                       |

#### 3.6 Erasing Flash Program Memory

The minimum erase block is 32 words. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 32 words of program memory is erased. The Most Significant 11 bits of the EEADRH:EEADR point to the block being erased. EEADR< 4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the erase takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

#### 3.6.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load EEADRH:EEADR with address of row being erased.

- Set EEPGD bit to point to program memory; set WREN bit to enable writes and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase.

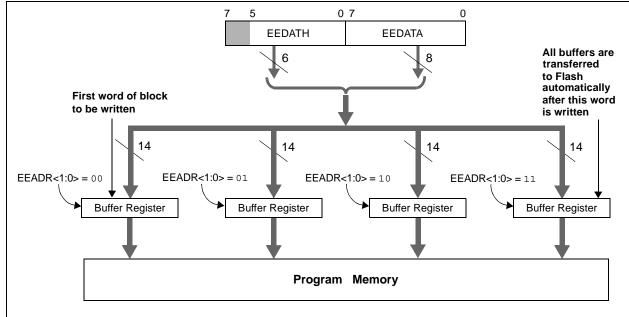

## 3.7 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device Configuration Word (Register 12-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as write-only operations. The program memory must first be erased. The write operation is edge-aligned and cannot occur across boundaries.

To write to the program memory, the data must first be loaded into the buffer registers. There are four 14-bit buffer registers and they are addressed by the low 2 bits of EEADR.

The following sequence of events illustrate how to perform a write to program memory:

- Set the EEPGD and WREN bits in the EECON1 register

- Clear the FREE bit in EECON1

- Write address to EEADRH:EEADR

- Write data to EEDATH:EEDATA

- Write 55 to EECON2

- Write AA to EECON2

- Set WR bit in EECON 1

The user must follow the same specific sequence to initiate the write for each word in the program block by writing each program word in sequence (00, 01, 10, 11).

There are 4 buffer register words and all four locations **MUST** be written to with correct data.

After the "BSF EECON1, WR" instruction, if EEADR  $\neq$  xxxxx11, then a short write will occur. This short write-only transfers the data to the buffer register. The WR bit will be cleared in hardware after one cycle.

After the "BSF EECON1, WR" instruction, if EEADR = xxxxx11, then a long write will occur. This will simultaneously transfer the data from EEDATH:EEDATA to the buffer registers and begin the write of all four words. The processor will execute the next instruction and then ignore the subsequent instruction. The user should place NOP instructions into the second words. The processor will then halt internal operations for typically 2 msec in which the write takes place. This is not a Sleep mode, as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the 3rd instruction after the EECON1 write instruction.

After each long write, the 4 buffer registers will be reset to 3FFF.

#### FIGURE 3-1: BLOCK WRITES TO FLASH PROGRAM MEMORY

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111' | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock, |

|---------|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

|         | MOVWF                                      | TICON                                          | ; Asynchronous operation, external oscillator                                              |

|         | CLRF<br>CLRF                               | secs<br>mins                                   | ; Initialize timekeeping registers                                                         |

|         | MOVLW                                      | mins<br>.12                                    |                                                                                            |

|         | MOVLW                                      | .12<br>hours                                   |                                                                                            |

|         | BANKSEL                                    | PIE1                                           |                                                                                            |

|         | BSF                                        |                                                | ; Enable Timer1 interrupt                                                                  |

|         | RETURN                                     | ,                                              | ,                                                                                          |

| RTCisr  | BANKSEL                                    | TMR1H                                          |                                                                                            |

|         | BSF                                        | TMR1H, 7                                       | ; Preload for 1 sec overflow                                                               |

|         | BCF                                        | PIR1, TMR1IF                                   | ; Clear interrupt flag                                                                     |

|         | INCF                                       | secs, F                                        | ; Increment seconds                                                                        |

|         | MOVF                                       | secs, w                                        |                                                                                            |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | seconds                                        | ; Clear seconds                                                                            |

|         | INCF<br>MOVF                               | mins, f<br>mins, w                             | ; Increment minutes                                                                        |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     | 511105, 2                                      | ; No, done                                                                                 |

|         | CLRF                                       | mins                                           | ; Clear minutes                                                                            |

|         | INCF                                       | hours, f                                       | ; Increment hours                                                                          |

|         | MOVF                                       | hours, w                                       |                                                                                            |

|         | SUBLW                                      | .24                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 24 hours elapsed?                                                                        |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | hours                                          | ; Clear hours                                                                              |

|         | RETURN                                     |                                                | ; Done                                                                                     |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7   | Bit 6     | Bit 5         | Bit 4         | Bit 3          | Bit 2       | Bit 1     | Bit 0  | Valu<br>POR, |      | all c | e on<br>other<br>sets |

|-----------------------|--------|---------|-----------|---------------|---------------|----------------|-------------|-----------|--------|--------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE      | TMR0IE        | INTE          | RBIE           | TMR0IF      | INTF      | RBIF   | 0000         | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1   | _       | ADIF      | _             | _             | SSPIF          | CCP1IF      | TMR2IF    | TMR1IF | - 0          | 0000 | - 0   | 0000                  |

| 8Ch                   | PIE1   | _       | ADIE      | _             | _             | SSPIE          | CCP1IE      | TMR2IE    | TMR1IE | - 0          | 0000 | - 0   | 0000                  |

| 0Eh                   | TMR1L  | Holding | g Registe | er for the Le | ast Signific  | ant Byte of t  | he 16-bit T | MR1 Regi  | ster   | xxxx         | xxxx | uuuu  | uuuu                  |

| 0Fh                   | TMR1H  | Holding | g Registe | er for the Me | ost Significa | ant Byte of th | ne 16-bit T | MR1 Regis | ster   | xxxx         | xxxx | uuuu  | uuuu                  |

| 10h                   | T1CON  |         | _         | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS    | TMR10N | 00           | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| REGISTER 8-1: | T2CON: TIM                                         | ER2 CONTROL     | REGISTER (      | ADDRESS       | 12h)      |              |         |  |  |  |  |

|---------------|----------------------------------------------------|-----------------|-----------------|---------------|-----------|--------------|---------|--|--|--|--|

|               | U-0 R/                                             | /W-0 R/W-0      | R/W-0           | R/W-0         | R/W-0     | R/W-0        | R/W-0   |  |  |  |  |

|               | — TOL                                              | JTPS3 TOUTPS    | 2 TOUTPS1       | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |  |  |  |  |

|               | bit 7                                              |                 |                 |               |           |              | bit 0   |  |  |  |  |

| bit 7         | Unimplement                                        | ed: Read as '0' |                 |               |           |              |         |  |  |  |  |

| bit 6-3       | TOUTPS3:TO                                         | UTPS0: Timer2 O | utput Postscale | e Select bits |           |              |         |  |  |  |  |

|               | 0000 = 1:1 Pos<br>0001 = 1:2 Pos<br>0010 = 1:3 Pos | stscale         |                 |               |           |              |         |  |  |  |  |

|               | •                                                  |                 |                 |               |           |              |         |  |  |  |  |

|               | •                                                  |                 |                 |               |           |              |         |  |  |  |  |

|               | 1111 = 1:16 P                                      | ostscale        |                 |               |           |              |         |  |  |  |  |

| bit 2         | TMR2ON: Tim                                        | er2 On bit      |                 |               |           |              |         |  |  |  |  |

|               | 1 = Timer2 is<br>0 = Timer2 is                     |                 |                 |               |           |              |         |  |  |  |  |

| bit 1-0       | T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits |                 |                 |               |           |              |         |  |  |  |  |

|               | 00 = Prescaler<br>01 = Prescaler<br>1x = Prescaler | is 4            |                 |               |           |              |         |  |  |  |  |

|               | Legend:                                            |                 |                 |               |           |              | ]       |  |  |  |  |

|               | R = Readable                                       | bit W :         | = Writable bit  | U = Unim      | plemented | bit. read as | '0'     |  |  |  |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7  | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      |      | e on<br>other<br>sets |

|-------------------------|--------|--------|-----------|---------|---------|---------|--------|---------|---------|---------------|------|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE      | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000 | 000u                  |

| 0Ch                     | PIR1   | —      | ADIF      | _       | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0           | 0000 | - 0  | 0000                  |

| 8Ch                     | PIE1   | _      | ADIE      | _       | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0           | 0000 | - 0  | 0000                  |

| 11h                     | TMR2   | Timer2 | Module Re | egister |         |         |        |         |         | 0000          | 0000 | 0000 | 0000                  |

| 12h                     | T2CON  | —      | TOUTPS3   | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000 | 0000                  |

| 92h                     | PR2    | Timer2 | Period Re | gister  |         |         |        |         |         | 1111          | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

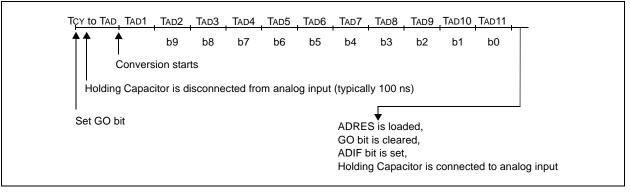

## 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2-TAD wait is required before the next acquisition is started. After this 2-TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### 11.4.1 A/D RESULT REGISTERS

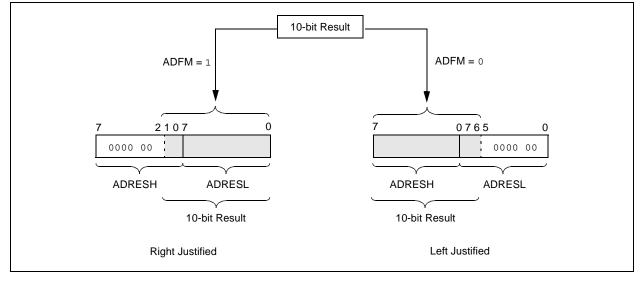

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16 bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

#### FIGURE 11-3: A/D CONVERSION TAD CYCLES

#### FIGURE 11-4: A/D RESULT JUSTIFICATION

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| R/P-1     | R/P-1 | R/P-1           | R/P-1          | R/P-1                 | R/P-1    | R/P-1    | R/P-1             | R/P-1            | R/P-1           | R/P-1                      | R/P-1        | R/P-1 | R/P-1 |

|-----------|-------|-----------------|----------------|-----------------------|----------|----------|-------------------|------------------|-----------------|----------------------------|--------------|-------|-------|

| CP        | ССРМХ | DEBUG           | WRT1           | WRT0                  | CPD      | LVP      | BOREN             | MCLRE            | FOSC2           | PWRTEN                     | WDTEN        | FOSC1 | FOSC0 |

| bit 13    |       |                 |                |                       |          |          |                   |                  |                 |                            |              |       | bit 0 |

| bit 13    |       | CD. Ela         | ch Drogr       | om Mom                |          | do Dro   | tection bit       |                  |                 |                            |              |       |       |

|           |       |                 | e protec       |                       |          |          |                   |                  |                 |                            |              |       |       |

|           |       |                 | •              | ocations              | code-p   | rotecte  | ed                |                  |                 |                            |              |       |       |

| bit 12    |       | ССРМХ           | CCP1           | Pin Seleo             | ction bi | t        |                   |                  |                 |                            |              |       |       |

|           |       |                 |                | on on RB              |          |          |                   |                  |                 |                            |              |       |       |

| bit 11    |       |                 |                | on on RB              |          | nda hit  |                   |                  |                 |                            |              |       |       |

|           |       |                 |                | uit Debuç<br>buqaer d |          |          |                   | are denei        | al purpos       | e I/O pins                 |              |       |       |

|           |       |                 |                |                       |          |          |                   |                  |                 | e debugger                 |              |       |       |

| bit 10-9  | 1     | WRT1:\          | NRTO: F        | lash Prog             | gram M   | lemory   | Write Ena         | able bits        |                 |                            |              |       |       |

|           |       |                 | <u>16F818:</u> |                       |          |          |                   |                  |                 |                            |              |       |       |

|           |       |                 | ite prote      |                       |          |          |                   |                  | as a difi a d l |                            | a a vatura l |       |       |

|           |       |                 |                | FF write-             |          |          | JU to U3FF        | may be           | moainea i       | by EECON                   | CONTROL      |       |       |

|           |       |                 | 16F819:        |                       | 0.0000   | 04       |                   |                  |                 |                            |              |       |       |

|           |       | 11 = Wr         | ite prote      | ction off             |          |          |                   |                  |                 |                            |              |       |       |

|           |       |                 |                |                       |          |          |                   |                  |                 | ified by EE                |              |       |       |

|           |       |                 |                |                       |          |          |                   |                  |                 | ified by EE<br>ified by EE |              |       |       |

| bit 8     |       |                 |                | lemory C              | -        |          |                   |                  | y 50 mou        |                            |              |       |       |

|           |       |                 | e protec       | •                     |          |          |                   |                  |                 |                            |              |       |       |

|           |       |                 |                | mory loca             |          | -        |                   |                  |                 |                            |              |       |       |

| bit 7     |       |                 |                | ge Progra             |          |          |                   | _                |                 |                            |              |       |       |

|           |       |                 |                |                       |          |          | ow-Voltag         |                  |                 | abled<br>ed for prog       | rammina      |       |       |

| bit 6     |       |                 |                | -out Rese             |          |          |                   |                  |                 | eu ior prog                | lanning      |       |       |

|           |       | -               | R enable       |                       |          |          |                   |                  |                 |                            |              |       |       |

|           |       | 0 = BOF         | R disable      | ed                    |          |          |                   |                  |                 |                            |              |       |       |

| bit 5     |       |                 |                |                       |          |          | Select bit        |                  |                 |                            |              |       |       |

|           |       |                 |                | VPP pin f             |          |          | LR<br>tal I/O, MO | <u>N P</u> intor | ally tigd t     |                            |              |       |       |

| bit 3     |       | _               |                | er-up Tim             |          | •        |                   |                  | lany neu t      |                            |              |       |       |

| DIL O     |       |                 | RT disab       | •                     |          |          |                   |                  |                 |                            |              |       |       |

|           |       |                 | RT enab        |                       |          |          |                   |                  |                 |                            |              |       |       |

| bit 2     |       | WDTEN           | I: Watch       | dog Time              | r Enab   | le bit   |                   |                  |                 |                            |              |       |       |

|           |       |                 | T enable       |                       |          |          |                   |                  |                 |                            |              |       |       |

| ь:н л л   | 0     |                 | T disable      |                       |          | ation bi |                   |                  |                 |                            |              |       |       |

| bit 4, 1- | 0     |                 |                | : Oscillator          |          |          | n on RA6/         | 0902/01          | KO nin          |                            |              |       |       |

|           |       |                 |                |                       |          |          | on on RA          |                  |                 |                            |              |       |       |

|           |       | 101 <b>=   </b> | NTRC os        | cillator; C           | CLKO f   | unctior  | on RA6/0          | DSC2/CL          | KO pin ar       | nd port I/O f              | function o   | n     |       |

|           |       |                 |                | 1/CLKI p              |          | functio  | n on hoth         |                  |                 | pin and R/                 | 10001        |       |       |

|           |       |                 |                |                       |          |          | 46/OSC2/          |                  |                 | pin anu Ki                 | 47/0301/     |       |       |

|           |       |                 | IS oscilla     |                       |          |          |                   | oop.             | •               |                            |              |       |       |

|           |       |                 | T oscilla      |                       |          |          |                   |                  |                 |                            |              |       |       |

|           |       | 000 = L         | P oscilla      | tor                   |          |          |                   |                  |                 |                            |              |       |       |

|           |       | Note            | 1: The         | erased (              | unprog   | gramm    | ed) value         | of the Co        | onfiguratio     | on Word is                 | 3FFFh.       |       |       |

|           |       |                 |                |                       |          |          |                   |                  |                 |                            |              |       |       |

#### Legend:

R = Readable bitP = Programmable bitU = Unimplemented bit, read as '1'-n = Value when device is unprogrammedu = Unchanged from programmed state

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF<br>(Indu | 818/819<br>strial)                                   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |            |             |                                                  |  |  |

|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|-------------|--------------------------------------------------|--|--|

| PIC16F8<br>(Indu | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                    |     |       |            |             |                                                  |  |  |

| Param<br>No.     | Device                                               | Тур                                                                                                                                | Max | Units | Conditions |             |                                                  |  |  |

|                  | Supply Current (IDD) <sup>(2,3)</sup>                |                                                                                                                                    |     |       |            |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 8                                                                                                                                  | 20  | μA    | -40°C      |             |                                                  |  |  |

|                  |                                                      | 7                                                                                                                                  | 15  | μA    | +25°C      | VDD = 2.0V  |                                                  |  |  |

|                  |                                                      | 7                                                                                                                                  | 15  | μA    | +85°C      |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 16                                                                                                                                 | 30  | μA    | -40°C      |             |                                                  |  |  |

|                  |                                                      |                                                                                                                                    | 25  | μΑ    | +25°C      | VDD = 3.0V  | Fosc = 31.25 kHz                                 |  |  |

|                  |                                                      | 14                                                                                                                                 | 25  | μΑ    | +85°C      | ]           | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |  |  |

|                  | All devices                                          | 32                                                                                                                                 | 40  | μA    | -40°C      |             |                                                  |  |  |

|                  |                                                      | 29                                                                                                                                 | 35  | μA    | +25°C      |             |                                                  |  |  |

|                  |                                                      | 29                                                                                                                                 | 35  | μA    | +85°C      | VDD = 5.0V  |                                                  |  |  |

|                  | Extended devices                                     | 35                                                                                                                                 | 45  | μΑ    | +125°C     |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 132                                                                                                                                | 160 | μΑ    | -40°C      |             |                                                  |  |  |

|                  |                                                      | 126                                                                                                                                | 155 | μΑ    | +25°C      | VDD = 2.0V  |                                                  |  |  |

|                  |                                                      | 126                                                                                                                                | 155 | μΑ    | +85°C      |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 260                                                                                                                                | 310 | μA    | -40°C      |             |                                                  |  |  |

|                  |                                                      | 230                                                                                                                                | 300 | μA    | +25°C      | VDD = 3.0V  | Fosc = 1 MHz                                     |  |  |

|                  |                                                      | 230                                                                                                                                | 300 | μA    | +85°C      |             | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |  |  |

|                  | All devices                                          | 560                                                                                                                                | 690 | μA    | -40°C      |             | ,                                                |  |  |

|                  |                                                      | 500                                                                                                                                | 650 | μA    | +25°C      | VDD = 5.0V  |                                                  |  |  |

|                  |                                                      | 500                                                                                                                                | 650 | μΑ    | +85°C      | 0.0v = 0.0v |                                                  |  |  |

|                  | Extended devices                                     | 570                                                                                                                                | 710 | μΑ    | +125°C     |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 310                                                                                                                                | 420 | μΑ    | -40°C      |             |                                                  |  |  |

|                  |                                                      | 300                                                                                                                                | 410 | μΑ    | +25°C      | VDD = 2.0V  |                                                  |  |  |

|                  |                                                      | 300                                                                                                                                | 410 | μΑ    | +85°C      |             |                                                  |  |  |

|                  | PIC16LF818/819                                       | 550                                                                                                                                | 650 | μΑ    | -40°C      |             | _                                                |  |  |

|                  |                                                      | 530                                                                                                                                | 620 | μΑ    | +25°C      | VDD = 3.0V  | Fosc = 4 MHz<br>( <b>RC_RUN</b> mode,            |  |  |

|                  |                                                      | 530                                                                                                                                | 620 | μA    | +85°C      |             | Internal RC Oscillator)                          |  |  |

|                  | All devices                                          | 1.2                                                                                                                                | 1.5 | mA    | -40°C      |             | ······································           |  |  |

|                  |                                                      | 1.1                                                                                                                                | 1.4 | mA    | +25°C      | VDD = 5.0V  |                                                  |  |  |

|                  |                                                      | 1.1                                                                                                                                | 1.4 | mA    | +85°C      | VD = 0.0V   |                                                  |  |  |

|                  | Extended devices                                     | 1.3                                                                                                                                | 1.6 | mA    | +125°C     |             |                                                  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

## 15.3 DC Characteristics: Internal RC Accuracy PIC16F818/819, PIC16F818/819 TSL (Industrial, Extended) PIC16LF818/819, PIC16LF818/819 TSL (Industrial)

| PIC16LF818/819 <sup>(3)</sup><br>PIC16LF818/819 TSL <sup>(3)</sup><br>(Industrial) |                                                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |            |            |            |                                |                |  |  |  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|--------------------------------|----------------|--|--|--|

| PIC16F8                                                                            | 818/819 <sup>(3)</sup><br>318/819 TSL <sup>(3)</sup><br>ustrial, Extended) | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |            |            |            |                                |                |  |  |  |

| Param<br>No.                                                                       | Device                                                                     | Min                                                                                                                                | Тур        | Мах        | Units      | с                              | onditions      |  |  |  |

|                                                                                    | INTOSC Accuracy @ F                                                        | req = 8 MHz,                                                                                                                       | 4 MHz, 2 M | Hz, 1 MHz, | 500 kHz, 2 | 50 kHz, 125 kHz <sup>(1)</sup> |                |  |  |  |

|                                                                                    | PIC16LF818/819                                                             | -5                                                                                                                                 | ±1         | 5          | %          | +25°C                          |                |  |  |  |

|                                                                                    |                                                                            | -25                                                                                                                                | —          | 25         | %          | -10°C to +85°C                 | VDD = 2.7-3.3V |  |  |  |

|                                                                                    |                                                                            | -30                                                                                                                                | _          | 30         | %          | -40°C to +85°C                 |                |  |  |  |

|                                                                                    | PIC16F818/819 <sup>(4)</sup>                                               | -5                                                                                                                                 | ±1         | 5          | %          | +25°C                          |                |  |  |  |

|                                                                                    |                                                                            | -25                                                                                                                                | —          | 25         | %          | -10°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

|                                                                                    |                                                                            | -30                                                                                                                                | —          | 30         | %          | -40°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

|                                                                                    |                                                                            | -35                                                                                                                                | —          | 35         | %          | -40°C to +125°C                |                |  |  |  |

|                                                                                    | PIC16LF818/819 TSL                                                         | -2                                                                                                                                 | ±1         | 2          | %          | +25°C                          |                |  |  |  |

|                                                                                    |                                                                            | -5                                                                                                                                 | —          | 5          | %          | -10°C to +85°C                 | VDD = 2.7-3.3V |  |  |  |

|                                                                                    |                                                                            | -10                                                                                                                                | —          | 10         | %          | -40°C to +85°C                 |                |  |  |  |

|                                                                                    | PIC16F818/819 TSL <sup>(5)</sup>                                           | -2                                                                                                                                 | ±1         | 2          | %          | +25°C                          |                |  |  |  |

|                                                                                    |                                                                            | -5                                                                                                                                 | —          | 5          | %          | -10°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

|                                                                                    |                                                                            | -10                                                                                                                                | —          | 10         | %          | -40°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

|                                                                                    |                                                                            | -15                                                                                                                                | —          | 15         | %          | -40°C to +125°C                |                |  |  |  |

|                                                                                    | INTRC Accuracy @ Freq = 31 kHz <sup>(2)</sup>                              |                                                                                                                                    |            |            |            |                                |                |  |  |  |

|                                                                                    | PIC16LF818/819                                                             | 26.562                                                                                                                             | —          | 35.938     | kHz        | -40°C to +85°C                 | VDD = 2.7-3.3V |  |  |  |

|                                                                                    | PIC16F818/819 <sup>(4)</sup>                                               | 26.562                                                                                                                             | —          | 35.938     | kHz        | -40°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

|                                                                                    | PIC16LF818/819 TSL                                                         | 26.562                                                                                                                             | —          | 35.938     | kHz        | -40°C to +85°C                 | VDD = 2.7-3.3V |  |  |  |

| PIC16F818/819 TSL <sup>(5)</sup>                                                   |                                                                            | 26.562                                                                                                                             | —          | 35.938     | kHz        | -40°C to +85°C                 | VDD = 4.5-5.5V |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: Frequency calibrated at 25°C. OSCTUNE register can be used to compensate for temperature drift.

**2:** INTRC frequency after calibration.

3: The only specification difference between a non-TSL device and a TSL device is the internal RC oscillator specifications listed above. All other specifications are maintained.

4: Example part number for the specifications listed above: PIC16F818-I/SS (PIC16F818 device, Industrial temperature, SSOP package).

5: Example part number for the specifications listed above: PIC16F818-I/SSTSL (PIC16F818 device, Industrial temperature, SSOP package).

### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| DC CHARACTERISTICS |       |                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |          |       |                                                                    |  |

|--------------------|-------|------------------------------------|------------------------------------------------------|------|----------|-------|--------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                     | Min                                                  | Тур† | Max      | Units | Conditions                                                         |  |

|                    | VIL   | Input Low Voltage                  | •                                                    |      |          |       |                                                                    |  |

|                    |       | I/O ports:                         |                                                      |      |          |       |                                                                    |  |

| D030               |       | with TTL buffer                    | Vss                                                  | _    | 0.15 Vdd | V     | For entire VDD range                                               |  |

| D030A              |       |                                    | Vss                                                  | _    | 0.8V     | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |

| D031               |       | with Schmitt Trigger buffer        | Vss                                                  | _    | 0.2 Vdd  | V     |                                                                    |  |

| D032               |       | MCLR, OSC1 (in RC mode)            | Vss                                                  | _    | 0.2 Vdd  | V     | (Note 1)                                                           |  |

| D033               |       | OSC1 (in XT and LP mode)           | Vss                                                  | _    | 0.3V     | V     |                                                                    |  |

|                    |       | OSC1 (in HS mode)                  | Vss                                                  | _    | 0.3 Vdd  | V     |                                                                    |  |

|                    |       | Ports RB1 and RB4:                 |                                                      |      |          |       |                                                                    |  |

| D034               |       | with Schmitt Trigger buffer        | Vss                                                  | _    | 0.3 Vdd  | V     | For entire VDD range                                               |  |

|                    | Vih   | Input High Voltage                 | •                                                    |      |          |       |                                                                    |  |

|                    |       | I/O ports:                         |                                                      |      |          |       |                                                                    |  |

| D040               |       | with TTL buffer                    | 2.0                                                  | _    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |

| D040A              |       |                                    | 0.25 VDD + 0.8V                                      | _    | Vdd      | V     | For entire VDD range                                               |  |

| D041               |       | with Schmitt Trigger buffer        | 0.8 Vdd                                              | _    | Vdd      | V     | For entire VDD range                                               |  |

| D042               |       | MCLR                               | 0.8 Vdd                                              | _    | Vdd      | V     |                                                                    |  |

| D042A              |       | OSC1 (in XT and LP mode)           | 1.6V                                                 | _    | Vdd      | V     |                                                                    |  |

|                    |       | OSC1 (in HS mode)                  | 0.7 Vdd                                              | _    | Vdd      | V     |                                                                    |  |

| D043               |       | OSC1 (in RC mode)                  | 0.9 Vdd                                              | _    | Vdd      | V     | (Note 1)                                                           |  |

|                    |       | Ports RB1 and RB4:                 |                                                      |      |          |       |                                                                    |  |

| D044               |       | with Schmitt Trigger buffer        | 0.7 Vdd                                              | _    | Vdd      | V     | For entire VDD range                                               |  |

| D070               | Ipurb | PORTB Weak Pull-up Current         | 50                                                   | 250  | 400      | μΑ    | VDD = 5V, VPIN = VSS                                               |  |

|                    | lı∟   | Input Leakage Current (Notes 2, 3) |                                                      |      |          |       |                                                                    |  |

| D060               |       | I/O ports                          | —                                                    | —    | ±1       | μA    | $Vss \le VPIN \le VDD$ , pin at high-impedance                     |  |

| D061               |       | MCLR                               | —                                                    | _    | ±5       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                           |  |

| D063               |       | OSC1                               | _                                                    | —    | ±5       | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

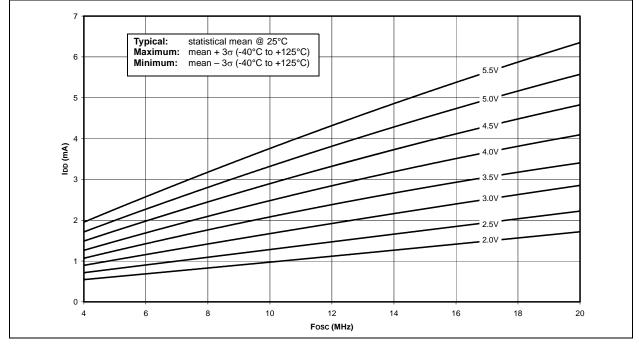

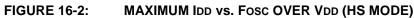

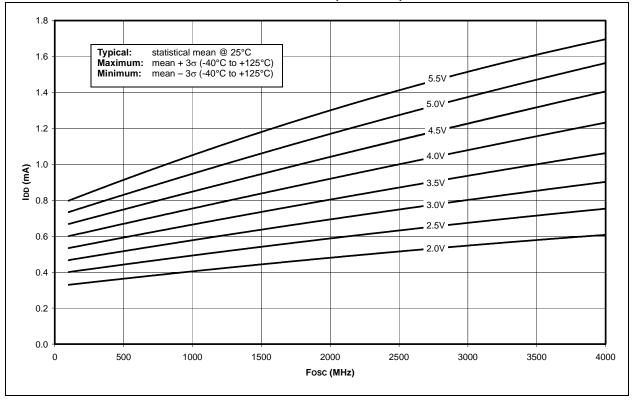

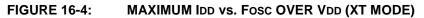

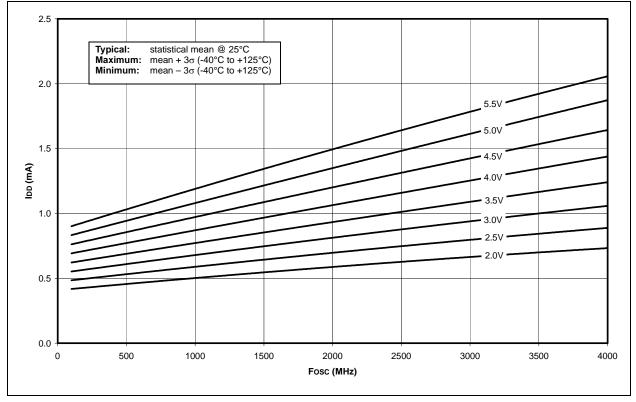

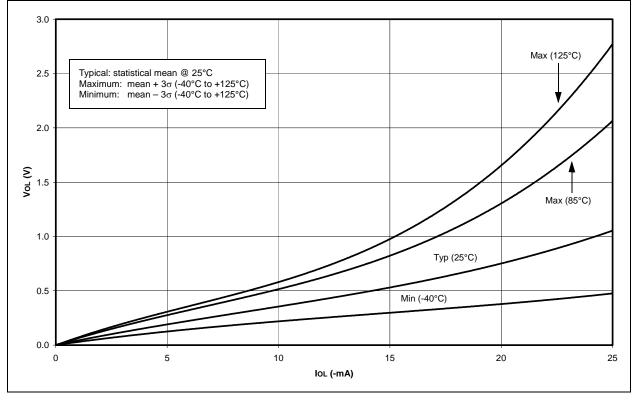

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

### FIGURE 16-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)