Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

```

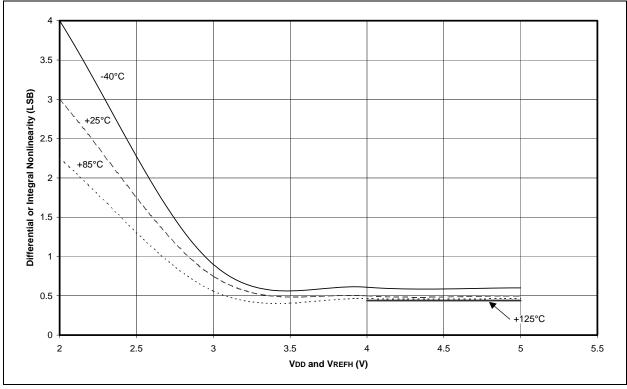

FIGURE 2-3:

```

#### PIC16F818 REGISTER FILE MAP

|                                                                                                                                                                                          | ddress      |                                | Address     | [                   | Address      |                                   | ddre       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|-------------|---------------------|--------------|-----------------------------------|------------|

| Indirect addr.(*)                                                                                                                                                                        | 00h         | Indirect addr.(*)              | 80h         | Indirect addr.(*)   | 100h         | Indirect addr.(*)                 | 180        |

| TMR0                                                                                                                                                                                     | 01h         | OPTION_REG                     | 81h         | TMR0                | 101h         | OPTION_REG                        | 181        |

| PCL                                                                                                                                                                                      | 02h         | PCL                            | 82h         | PCL                 | 102h         | PCL                               | 182        |

| STATUS                                                                                                                                                                                   | 03h         | STATUS                         | 83h         | STATUS              | 103h         | STATUS                            | 183        |

| FSR                                                                                                                                                                                      | 04h         | FSR                            | 84h         | FSR                 | 104h         | FSR                               | 184        |

| PORTA                                                                                                                                                                                    | 05h         | TRISA                          | 85h         |                     | 105h         |                                   | 185        |

| PORTB                                                                                                                                                                                    | 06h         | TRISB                          | 86h         | PORTB               | 106h         | TRISB                             | 186        |

|                                                                                                                                                                                          | 07h         |                                | 87h         |                     | 107h         |                                   | 187        |

|                                                                                                                                                                                          | 08h         |                                | 88h         |                     | 108h<br>109h |                                   | 188        |

|                                                                                                                                                                                          | 09h<br>0Ah  |                                | 89h         | PCLATH              | 1091<br>10Ah |                                   | 189        |

| PCLATH                                                                                                                                                                                   | 0An<br>0Bh  | PCLATH                         | 8Ah         | INTCON              | 10An<br>10Bh | PCLATH                            | 18/        |

|                                                                                                                                                                                          | 0Бh<br>0Ch  |                                | 8Bh         |                     | 10Dh         |                                   | 18E        |

| PIR1                                                                                                                                                                                     |             | PIE1<br>PIE2                   | 8Ch         | EEDATA<br>EEADR     | 10Ch<br>10Dh | EECON1                            | 180        |

| PIR2<br>TMR1L                                                                                                                                                                            | 0Dh<br>0Eh  |                                | 8Dh         |                     | 10Dh<br>10Eh | EECON2<br>Reserved <sup>(1)</sup> | 18[        |

| TMR1L<br>TMR1H                                                                                                                                                                           | 0En<br>0Fh  | PCON<br>OSCCON                 | 8Eh<br>8Fh  | EEDATH<br>EEADRH    | 10En<br>10Fh | Reserved <sup>(1)</sup>           | 18E<br>18F |

| TICON                                                                                                                                                                                    | 10h         | OSCTUNE                        |             | EEADKI              | 110h         | Reserved                          | 186        |

| TMR2                                                                                                                                                                                     | 1011<br>11h | USCIDINE                       | 90h<br>91h  |                     | 11011        |                                   | 190        |

| T2CON                                                                                                                                                                                    | 12h         | PR2                            | 91h<br>92h  |                     |              |                                   |            |

| SSPBUF                                                                                                                                                                                   | 13h         | SSPADD                         | 9211<br>93h |                     |              |                                   |            |

| SSPCON                                                                                                                                                                                   | 14h         | SSPSTAT                        | 931<br>94h  |                     |              |                                   |            |

| CCPR1L                                                                                                                                                                                   | 15h         |                                | 9411<br>95h |                     |              |                                   |            |

| CCPR1H                                                                                                                                                                                   | 16h         |                                | 96h         |                     |              |                                   |            |

| CCP1CON                                                                                                                                                                                  | 17h         |                                | 97h         |                     |              |                                   |            |

|                                                                                                                                                                                          | 18h         |                                | 98h         |                     |              |                                   |            |

|                                                                                                                                                                                          | 19h         |                                | 99h         |                     |              |                                   |            |

|                                                                                                                                                                                          | 1Ah         |                                | 9Ah         |                     |              |                                   |            |

|                                                                                                                                                                                          | 1Bh         |                                | 9Bh         |                     |              |                                   |            |

|                                                                                                                                                                                          | 1Ch         |                                | 9Ch         |                     |              |                                   |            |

|                                                                                                                                                                                          | 1Dh         |                                | 9Dh         |                     |              |                                   |            |

| ADRESH                                                                                                                                                                                   | 1Eh         | ADRESL                         | 9Eh         |                     |              |                                   |            |

| ADCON0                                                                                                                                                                                   | 1Fh         | ADCON1                         | 9Fh         |                     | 11Fh         |                                   | 19F        |

|                                                                                                                                                                                          | 20h         | General<br>Purpose<br>Register | A0h         |                     | 120h         |                                   | 1A)        |

| General                                                                                                                                                                                  |             | 32 Bytes                       | BFh         |                     |              |                                   |            |

| Purpose<br>Register<br>96 Bytes                                                                                                                                                          |             | Accesses<br>40h-7Fh            | C0h         | Accesses<br>20h-7Fh |              | Accesses<br>20h-7Fh               |            |

| Bank 0                                                                                                                                                                                   | 7Fh         | Bank 1                         | FFh         | Bank 2              | 17Fh         | Bank 3                            | 1FF        |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>* Not a physical register.</li> <li>Iote 1: These registers are reserved; maintain these registers clear.</li> </ul> |             |                                |             |                     |              |                                   |            |

| Address               | Name       | Bit 7      | Bit 6           | Bit 5          | Bit 4          | Bit 3          | Bit 2                 | Bit 1           | Bit 0    | Value on<br>POR, BOR | Details on<br>page: |

|-----------------------|------------|------------|-----------------|----------------|----------------|----------------|-----------------------|-----------------|----------|----------------------|---------------------|

| Bank 2                |            |            |                 |                |                |                |                       |                 |          |                      |                     |

| 100h <sup>(1)</sup>   | INDF       | Addressin  | ng this locatio | on uses conte  | ents of FSR to | address data   | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 101h                  | TMR0       | Timer0 M   | lodule Regist   | ter            |                |                |                       |                 |          | xxxx xxxx            | 53                  |

| 102h <sup>(1</sup>    | PCL        | Program    | Counter's (P    | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 103h <sup>(1)</sup>   | STATUS     | IRP        | RP1             | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 104h <sup>(1)</sup>   | FSR        | Indirect D | ata Memory      | Address Poir   | nter           |                |                       |                 |          | xxxx xxxx            | 23                  |

| 105h                  | —          | Unimpler   | nented          |                |                |                |                       |                 |          | _                    | —                   |

| 106h                  | PORTB      | PORTB [    | Data Latch w    | hen written; P | ORTB pins w    | hen read       |                       |                 |          | XXXX XXXX            | 43                  |

| 107h                  | —          | Unimplen   | nented          |                |                |                |                       |                 |          | —                    | _                   |

| 108h                  | —          | Unimplen   | nented          |                |                |                |                       |                 |          | —                    | —                   |

| 109h                  | —          | Unimplen   | nented          |                |                |                |                       |                 |          | —                    | —                   |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _          | —               | _              | Write Buffer   | for the upper  | 5 bits of the F       | Program Cou     | nter     | 0 0000               | 23                  |

| 10Bh <sup>(1)</sup>   | INTCON     | GIE        | PEIE            | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 10Ch                  | EEDATA     | EEPROM     | I/Flash Data    | Register Low   | Byte           |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Dh                  | EEADR      | EEPROM     | 1/Flash Addre   | ess Register L | ow Byte        |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Eh                  | EEDATH     | _          | —               | EEPROM/Fla     | ash Data Reg   | ister High Byt | е                     |                 |          | xx xxxx              | 25                  |

| 10Fh                  | EEADRH     | —          | —               | —              | —              | —              | EEPROM/F<br>High Byte | lash Address    | Register | xxx                  | 25                  |

| Bank 3                |            |            |                 |                |                |                |                       |                 |          |                      |                     |

| 180h <sup>(1)</sup>   | INDF       | Addressin  | ng this locatio | on uses conte  | ents of FSR to | address data   | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 181h                  | OPTION_REG | RBPU       | INTEDG          | TOCS           | TOSE           | PSA            | PS2                   | PS1             | PS0      | 1111 1111            | 17, 54              |

| 182h <sup>(1)</sup>   | PCL        | Program    | Counter's (P    | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 183h <sup>(1)</sup>   | STATUS     | IRP        | RP1             | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 184h <sup>(1)</sup>   | FSR        | Indirect D | ata Memory      | Address Poir   | nter           |                |                       |                 |          | xxxx xxxx            | 23                  |

| 185h                  | —          | Unimplen   | nented          |                |                |                |                       |                 |          | —                    | _                   |

| 186h                  | TRISB      | PORTB [    | Data Direction  | n Register     |                |                |                       |                 |          | 1111 1111            | 43                  |

| 187h                  | _          | Unimplen   | nented          |                |                |                |                       |                 |          | _                    | —                   |

| 188h                  | _          | Unimplen   | nented          |                |                |                |                       |                 |          |                      | —                   |

| 189h                  | _          | Unimplen   | Jnimplemented — |                |                |                |                       |                 |          | —                    |                     |

| 18Ah <sup>(1,2)</sup> | PCLATH     |            | _               | _              | Write Buffer   | for the upper  | 5 bits of the F       | Program Cou     | nter     | 0 0000               | 23                  |

| 18Bh <sup>(1)</sup>   | INTCON     | GIE        | PEIE            | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 18Ch                  | EECON1     | EEPGD      | _               | _              | FREE           | WRERR          | WREN                  | WR              | RD       | xx x000              | 26                  |

|                       | 1          |            |                 |                |                |                |                       |                 |          |                      | 25                  |

| 18Dh                  | EECON2     | LEFRON     |                 |                |                |                |                       |                 |          |                      |                     |

| 18Dh<br>18Eh          | EECON2     |            |                 |                | p, e.e         | ,              |                       |                 |          | 0000 0000            | —                   |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 2.2.2.6 **PIE2** Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

#### **REGISTER 2-6:** PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS 8Dh)

|         |             |              |                 |              |          | •         |                 |       |

|---------|-------------|--------------|-----------------|--------------|----------|-----------|-----------------|-------|

|         | U-0         | U-0          | U-0             | R/W-0        | U-0      | U-0       | U-0             | U-0   |

|         | —           | —            | —               | EEIE         | —        | —         | —               |       |

|         | bit 7       |              |                 |              |          |           |                 | bit 0 |

|         |             |              |                 |              |          |           |                 |       |

| bit 7-5 | Unimpleme   | ented: Rea   | <b>d as</b> '0' |              |          |           |                 |       |

| bit 4   | EEIE: EEPF  | ROM Write    | Operation Ir    | terrupt Enal | ole bit  |           |                 |       |

|         | 1 = Enable  | EE write int | terrupt         |              |          |           |                 |       |

|         | 0 = Disable | EE write in  | terrupt         |              |          |           |                 |       |

| bit 3-0 | Unimpleme   | ented: Rea   | <b>d as</b> '0' |              |          |           |                 |       |

|         |             |              |                 |              |          |           |                 |       |

|         | Legend:     |              |                 |              |          |           |                 |       |

|         | R = Readab  | ole bit      | W = W           | ritable bit  | U = Unim | plemented | bit, read as '0 | ,     |

#### 2.2.2.7 **PIR2** Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

-n = Value at POR

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs regardless of the state of<br>its corresponding enable bit or the Global<br>Interrupt Enable bit, GIE (INTCON<7>).<br>User software should ensure the appropri-<br>ate interrupt flag bits are clear prior to<br>enabling an interrupt. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

x = Bit is unknown

'0' = Bit is cleared

#### **REGISTER 2-7:** PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

'1' = Bit is set

| $\Box X Z^{-1}$ . |           |                                 |                 | INLGUL        |         | ILCIOID LIV |     | .55 0011) |

|-------------------|-----------|---------------------------------|-----------------|---------------|---------|-------------|-----|-----------|

|                   | U-0       | U-0                             | U-0             | R/W-0         | U-0     | U-0         | U-0 | U-0       |

|                   |           | —                               | —               | EEIF          | _       | _           | _   |           |

|                   | bit 7     |                                 |                 |               |         |             |     | bit 0     |

|                   |           |                                 |                 |               |         |             |     |           |

| bit 7-5           | Unimplem  | ented: Rea                      | <b>d as</b> '0' |               |         |             |     |           |

| bit 4             | EEIF: EEP | ROM Write                       | Operation Ir    | nterrupt Enal | ole bit |             |     |           |

|                   |           | e EE write int<br>e EE write in |                 |               |         |             |     |           |

| bit 3-0           | Unimplem  | ented: Rea                      | <b>d as</b> '0' |               |         |             |     |           |

|                   |           |                                 |                 |               |         |             |     |           |

|                   | Legend:   |                                 |                 |               |         |             |     |           |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.8 **PCON Register**

| Note: | Interrupt fleg bits get eet when an interrupt |

|-------|-----------------------------------------------|

| note: | Interrupt flag bits get set when an interrupt |

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the Global    |

|       | Interrupt Enable bit, GIE (INTCON<7>).        |

|       | User software should ensure the appropri-     |

|       | ate interrupt flag bits are clear prior to    |

|       | enabling an interrupt.                        |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

-n = Value at POR

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### **REGISTER 2-8:** PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         | U-0       | U-0                        | U-0             | U-0            | U-0          | U-0         | R/W-0        | R/W-x   |

|---------|-----------|----------------------------|-----------------|----------------|--------------|-------------|--------------|---------|

|         | _         | _                          |                 | —              | _            | _           | POR          | BOR     |

|         | bit 7     |                            |                 |                |              |             |              | bit 0   |

| bit 7-2 | Unimplem  | ented: Read                | <b>l as</b> '0' |                |              |             |              |         |

| bit 1   | POR: Powe | er-on Reset                | Status bit      |                |              |             |              |         |

|         |           | wer-on Rese<br>er-on Reset |                 | ust be set in  | software aft | er a Power- | on Reset o   | ccurs)  |

| bit 0   | BOR: Brow | /n-out Reset               | Status bit      |                |              |             |              |         |

|         |           | own-out Res<br>vn-out Rese |                 | nust be set in | software af  | ter a Brown | -out Reset   | occurs) |

|         | Legend:   |                            |                 |                |              |             |              |         |

|         | R = Reada | able bit                   | W = W           | /ritable bit   | U = Unim     | plemented I | bit, read as | '0'     |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

| REGISTER 3-1: | EECON1:                                                                                                     | EEPROM                                   | ACCESS C                                    | ONTROL       | REGISTER      | 1 (ADDRI      | ESS 18Ch)     |             |

|---------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------|--------------|---------------|---------------|---------------|-------------|

|               | R/W-x                                                                                                       | U-0                                      | U-0                                         | R/W-x        | R/W-x         | R/W-0         | R/S-0         | R/S-0       |

|               | EEPGD                                                                                                       |                                          | —                                           | FREE         | WRERR         | WREN          | WR            | RD          |

|               | bit 7                                                                                                       |                                          |                                             |              |               |               |               | bit 0       |

| bit 7         | EEPGD: Pr                                                                                                   | ogram/Data                               | EEPROM                                      | Select bit   |               |               |               |             |

|               | 0 = Access                                                                                                  | es program<br>es data mei<br>fter a POR; | mory                                        | not be chang | ged while a v | write operati | on is in prog | jress.      |

| bit 6-5       | Unimplem                                                                                                    | ented: Read                              | <b>d as</b> '0'                             |              |               |               |               |             |

| bit 4         | FREE: EEF                                                                                                   | PROM Force                               | ed Row Eras                                 | se bit       |               |               |               |             |

|               | 1 = Erase the program memory row addressed by EEADRH:EEADR on the next WR command<br>0 = Perform write-only |                                          |                                             |              |               |               |               |             |

| bit 3         | WRERR: E                                                                                                    | EPROM Er                                 | ror Flag bit                                |              |               |               |               |             |

|               | operat                                                                                                      | ion)                                     | s premature<br>n completed                  | -            | d (any MCLI   | R or any WI   | OT Reset du   | ring normal |

| bit 2         | WREN: EE                                                                                                    | PROM Writ                                | e Enable bit                                |              |               |               |               |             |

|               |                                                                                                             | write cycles<br>write to the             |                                             |              |               |               |               |             |

| bit 1         | WR: Write                                                                                                   | Control bit                              |                                             |              |               |               |               |             |

|               | can on                                                                                                      | ly be set (no                            | cle. The bit<br>ot cleared) ir<br>EEPROM is | n software.  | y hardware o  | once write is | s complete.   | The WR bit  |

| bit 0         | RD: Read                                                                                                    | Control bit                              |                                             |              |               |               |               |             |

|               |                                                                                                             | s an EEPR<br>d) in softwar               |                                             | D is cleared | l in hardwar  | e. The RD I   | bit can only  | be set (not |

|               | 0 = Does r                                                                                                  | not initiate a                           | n EEPROM                                    | read         |               |               |               |             |

|               | Legend:                                                                                                     |                                          |                                             |              |               |               |               | ]           |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Set only         | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

#### 4.5.3 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

#### 4.5.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF<2:0> = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.5.5 CLOCK TRANSITION SEQUENCE WHEN THE IRCF BITS ARE MODIFIED

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

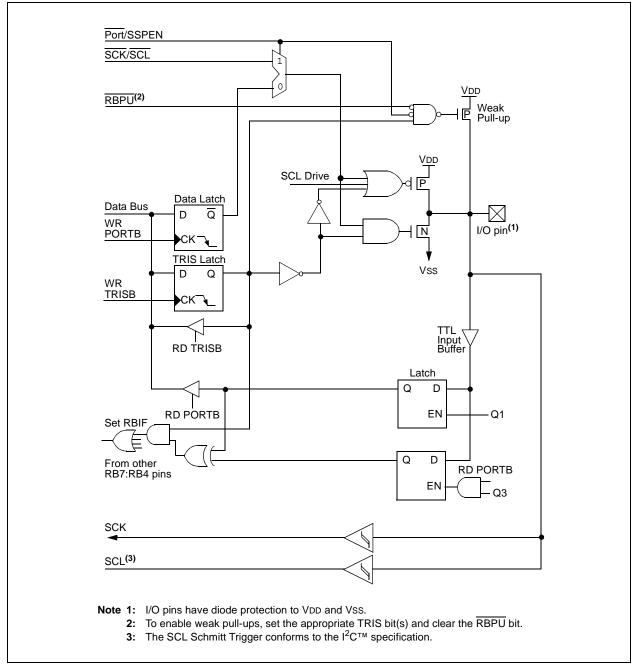

### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

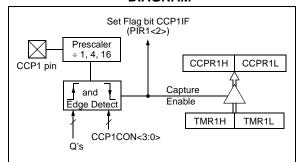

## 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW CAPT PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

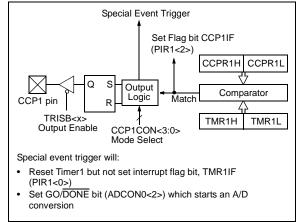

## 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 9-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 9.2.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the TRISB<x> bit.

- Note 1: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the data latch.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

### 9.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 9.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 9.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated that may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP1 module will not set interrupt flag bit, TMR1IF (PIR1<0>).

#### TABLE 9-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Address              | Name    | Bit 7                                                                       | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  |      | e on<br>BOR | all o | e on<br>other<br>sets |

|----------------------|---------|-----------------------------------------------------------------------------|-------|---------|---------|---------|--------|--------|--------|------|-------------|-------|-----------------------|

| 0Bh,8Bh<br>10BH,18Bh | INTCON  | GIE                                                                         | PEIE  | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000 | 000x        | 0000  | 000u                  |

| 0Ch                  | PIR1    | —                                                                           | ADIF  | _       | —       | SSPIF   | CCP1IF | TMR2IF | TMR1IF | - 0  | 0000        | - 0   | 0000                  |

| 8Ch                  | PIE1    | —                                                                           | ADIE  | _       | _       | SSPIE   | CCP1IE | TMR2IE | TMR1IE | - 0  | 0000        | - 0   | 0000                  |

| 86h                  | TRISB   | PORTB Data Direction Register                                               |       |         |         | 1111    | 1111   | 1111   | 1111   |      |             |       |                       |

| 0Eh                  | TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |       |         |         |         | ster   | xxxx   | xxxx   | uuuu | uuuu        |       |                       |

| 0Fh                  | TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |       |         |         | ster    | xxxx   | xxxx   | uuuu   | uuuu |             |       |                       |

| 10h                  | T1CON   | -                                                                           |       | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 00   | 0000        | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/Compare/PWM Register 1 (LSB)                                        |       |         |         | xxxx    | xxxx   | uuuu   | uuuu   |      |             |       |                       |

| 16h                  | CCPR1H  | Capture/Compare/PWM Register 1 (MSB)                                        |       |         |         | xxxx    | xxxx   | uuuu   | uuuu   |      |             |       |                       |

| 17h                  | CCP1CON | _                                                                           | _     | CCP1X   | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0 | 00   | 0000        | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

## 10.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 10.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $l^2C^{TM}$  Multi-Master Environment" (DS00578).

### 10.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RB2/SDO/CCP1

- Serial Data In (SDI)

RB1/SDI/SDA

- Serial Clock (SCK)

RB4/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RB5/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and the SSPSTAT register (SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

- Note: Before enabling the module in SPI Slave mode, the state of the clock line (SCK) must match the polarity selected for the Idle state. The clock line can be observed by reading the SCK pin. The polarity of the Idle state is determined by the CKP bit (SSPCON<4>).

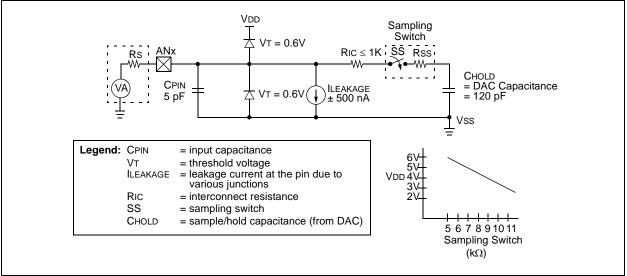

### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 2.5 k\Omega. As the impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### EQUATION 11-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient= TAMP + TC + TCOFF = 2  $\mu$ s + TC + [(Temperature - 25°C)(0.05  $\mu$ s/°C)] TC = CHOLD (RIC + Rss + Rs) In(1/2047) = -120 pF (1 k $\Omega$  + 7 k $\Omega$  + 10 k $\Omega$ ) In(0.0004885) = 16.47  $\mu$ s TACQ = 2  $\mu$ s + 16.47  $\mu$ s + [(50°C - 25°C)(0.05  $\mu$ s/°C) = 19.72  $\mu$ s

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

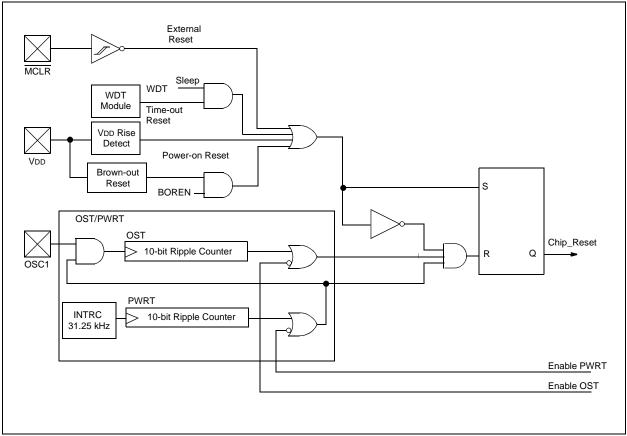

#### 12.2 Reset

The PIC16F818/819 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset during normal operation

- WDT wake-up during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 12-3. These bits are used in software to determine the nature of the Reset. Upon a POR, BOR wake-up from Sleep, the CPU requires or approximately 5-10 µs to become ready for code execution. This delay runs in parallel with any other timers. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 12-1.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| TABLE 12-4: INITIALIZATION CONDITIONS FOR ALL REGISTE |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Register   | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|------------------------------------|--------------------------|---------------------------------|

| W          | xxxx xxxx                          | นนนน นนนน                | <u>uuuu</u> uuuu                |

| INDF       | N/A                                | N/A                      | N/A                             |

| TMR0       | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL        | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS     | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <sup>(3)</sup>        |

| FSR        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA      | xxx0 0000                          | uuu0 0000                | uuuu uuuu                       |

| PORTB      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH     | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON     | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1       | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| PIR2       | 0                                  |                          | u(1)                            |

| TMR1L      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H      | xxxx xxxx                          | uuuu uuuu                | <u>uuuu</u> uuuu                |

| T1CON      | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2       | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON      | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON     | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| CCPR1L     | xxxx xxxx                          | <u>uuuu</u> uuuu         | <u>uuuu</u> uuuu                |

| CCPR1H     | xxxx xxxx                          | uuuu uuuu                | <u>uuuu</u> uuuu                |

| CCP1CON    | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRESH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA      | 1111 1111                          | 1111 1111                | <u>uuuu</u> uuuu                |

| TRISB      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1       | -0 0000                            | -0 0000                  | -u uuuu                         |

| PIE2       | 0                                  | 0                        | u                               |

| PCON       | dd                                 | uu                       |                                 |

| OSCCON     | -000 -0                            | -000 -0                  | -uuu -u                         |

| OSCTUNE    | 00 0000                            | 00 0000                  | uu uuuu                         |

| PR2        | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD     | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| SSPSTAT    | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| ADRESL     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON1     | 00 0000                            | 00 0000                  | uu uuuu                         |

| EEDATA     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEADR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEDATH     | xx xxxx                            | uu uuuu                  | uu uuuu                         |

| EEADRH     | xxx                                | uuu                      | uuu                             |

| EECON1     | xx x000                            | ux u000                  | uu uuuu                         |

| EECON2     |                                    |                          |                                 |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and PR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-3 for Reset value for specific conditions.

# 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDWF            | AND W with f                                                                                                                                              |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |  |  |

| ADDWF            | Add W and f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                     |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

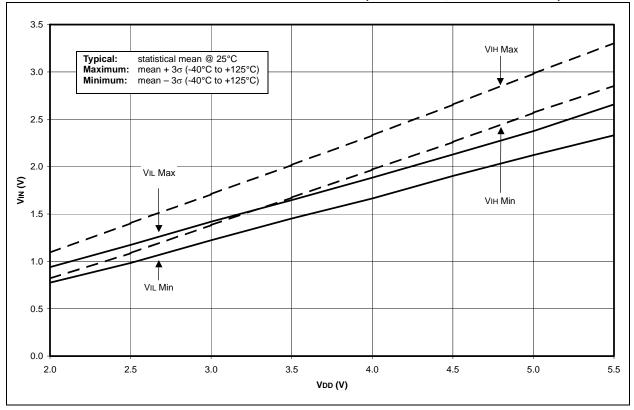

# FIGURE 16-23: MINIMUM AND MAXIMUM VIN vs. VDD (I<sup>2</sup>C<sup>™</sup> INPUT, -40°C TO +125°C)

## APPENDIX A: REVISION HISTORY

#### Revision A (May 2002)

Original version of this data sheet.

## **Revision B (August 2002)**

Added INTRC section. PWRT and BOR are independent of each other. Revised program memory text and code routine. Added QFN package. Modified PORTB diagrams.

### **Revision C (November 2002)**

Added various new feature descriptions. Added internal RC oscillator specifications. Added low-power Timer1 specifications and RTC application example.

### **Revision D (November 2003)**

Updated IRCF bit modification information and changed the INTOSC stabilization delay from 1 ms to 4 ms in Section 4.0 "Oscillator Configurations". Updated Section 12.17 "In-Circuit Serial Programming" to clarify LVP programming. In Section 15.0 "Electrical Characteristics", the DC Characteristics (Section 15.2 and Section 15.3) have been updated to include the Typ, Min and Max values and Table 15-1 "External Clock Timing Requirements" has been updated.

## **Revision E (September 2004)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in Section 16.0 "DC and AC Characteristics Graphs and Tables" have been updated and there have been minor corrections to the data sheet text.

## **Revision F (November 2011)**

This revision updated **Section 17.0** "Packaging Information".

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

#### TABLE B-1: DIFFERENCES BETWEEN THE PIC16F818 AND PIC16F819

| Features                            | PIC16F818 | PIC16F819 |

|-------------------------------------|-----------|-----------|

| Flash Program Memory (14-bit words) | 1K        | 2K        |

| Data Memory (bytes)                 | 128       | 256       |

| EEPROM Data Memory (bytes)          | 128       | 256       |

NOTES:

| Timer157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Associated Registers62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Capacitor Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Counter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |