Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 1.75КВ (1К х 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type | Buffer<br>Type | Description                                                                                |

|-------------------|-----------------------|--------------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------|

|                   |                       |              |             |               |                | PORTA is a bidirectional I/O port.                                                         |

| RA0/AN0           | 17                    | 19           | 23          |               |                |                                                                                            |

| RA0               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN0               |                       |              |             | I             | Analog         | Analog input channel 0.                                                                    |

| RA1/AN1           | 18                    | 20           | 24          |               |                |                                                                                            |

| RA1               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN1               |                       |              |             | I             | Analog         | Analog input channel 1.                                                                    |

| RA2/AN2/VREF-     | 1                     | 1            | 26          |               |                |                                                                                            |

| RA2               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN2               |                       |              |             | I             | Analog         | Analog input channel 2.                                                                    |

| VREF-             |                       |              |             | I             | Analog         | A/D reference voltage (low) input.                                                         |

| RA3/AN3/VREF+     | 2                     | 2            | 27          |               |                |                                                                                            |

| RA3               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN3               |                       |              |             | I             | Analog         | Analog input channel 3.                                                                    |

| VREF+             |                       |              |             | I             | Analog         | A/D reference voltage (high) input.                                                        |

| RA4/AN4/T0CKI     | 3                     | 3            | 28          |               |                |                                                                                            |

| RA4               |                       |              |             | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| AN4               |                       |              |             | I             | Analog         | Analog input channel 4.                                                                    |

| TOCKI             |                       |              |             | I             | ST             | Clock input to the TMR0 timer/counter.                                                     |

| RA5/MCLR/Vpp      | 4                     | 4            | 1           |               |                |                                                                                            |

| RA5               |                       |              |             | I             | ST             | Input pin.                                                                                 |

| MCLR              |                       |              |             | I             | ST             | Master Clear (Reset). Input/programming                                                    |

|                   |                       |              |             |               |                | voltage input. This pin is an active-low Reset                                             |

| Vpp               |                       |              |             | Р             |                | to the device.                                                                             |

|                   |                       | . –          |             | Р             | _              | Programming threshold voltage.                                                             |

| RA6/OSC2/CLKO     | 15                    | 17           | 20          |               | 07             |                                                                                            |

| RA6               |                       |              |             | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| OSC2              |                       |              |             | 0             | _              | Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode. |

| CLKO              |                       |              |             | 0             |                | In RC mode, this pin outputs CLKO signal                                                   |

| OLINO             |                       |              |             | Ŭ             |                | which has 1/4 the frequency of OSC1 and                                                    |

|                   |                       |              |             |               |                | denotes the instruction cycle rate.                                                        |

| RA7/OSC1/CLKI     | 16                    | 18           | 21          |               |                | ······································                                                     |

| RA7               | 10                    | 10           | 21          | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| OSC1              |                       |              |             | 1/C           | ST/CMOS(3)     | Oscillator crystal input.                                                                  |

| CLKI              |                       |              |             | I             | _              | External clock source input.                                                               |

| Legend: I = Input |                       | 0 =          | = Outp      | but           | I/O =          | Input/Output P = Power                                                                     |

| - = Not us        | sed                   |              | = TTL       |               |                | Schmitt Trigger Input                                                                      |

TABLE 1-2:PIC16F818/819 PINOUT DESCRIPTIONS

$\label{eq:Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.$

**2:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name                                            | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type      | Buffer<br>Type                       | Description                                                                                                                                              |

|-----------------------------------------------------|-----------------------|--------------|-------------|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                       |              |             |                    |                                      | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up or<br>all inputs.                                       |

| RB0/INT<br>RB0<br>INT                               | 6                     | 7            | 7           | I/O<br>I           | TTL<br>ST <sup>(1)</sup>             | Bidirectional I/O pin.<br>External interrupt pin.                                                                                                        |

| RB1/SDI/SDA<br>RB1<br>SDI<br>SDA                    | 7                     | 8            | 8           | I/O<br>I<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>SPI data in.<br>I <sup>2</sup> C™ data.                                                                                        |

| RB2/SDO/CCP1<br>RB2<br>SDO<br>CCP1                  | 8                     | 9            | 9           | I/O<br>O<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>SPI data out.<br>Capture input, Compare output, PWM output.                                                                    |

| RB3/CCP1/PGM<br>RB3<br>CCP1<br>PGM                  | 9                     | 10           | 10          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>Capture input, Compare output, PWM output.<br>Low-Voltage ICSP™ Programming enable pir                                         |

| RB4/SCK/SCL<br>RB4<br>SCK<br>SCL                    | 10                    | 11           | 12          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI<br>Synchronous serial clock input for I <sup>2</sup> C. |

| RB5/SS<br>RB5<br>SS                                 | 11                    | 12           | 13          | I/O<br>I           | TTL<br>TTL                           | Bidirectional I/O pin. Interrupt-on-change pin.<br>Slave select for SPI in Slave mode.                                                                   |

| RB6/T1OSO/T1CKI/PGC<br>RB6<br>T1OSO<br>T1CKI<br>PGC | 12                    | 13           | 15          | I/O<br>O<br>I<br>I | TTL<br>ST<br>ST<br>ST <sup>(2)</sup> | Interrupt-on-change pin.<br>Timer1 Oscillator output.<br>Timer1 clock input.<br>In-circuit debugger and ICSP programming<br>clock pin.                   |

| RB7/T1OSI/PGD<br>RB7<br>T1OSI<br>PGD                | 13                    | 14           | 16          | I/O<br>I<br>I      | TTL<br>ST<br>ST <sup>(2)</sup>       | Interrupt-on-change pin.<br>Timer1 oscillator input.<br>In-circuit debugger and ICSP programming<br>data pin.                                            |

| Vss                                                 | 5                     | 5, 6         | 3, 5        | Р                  | _                                    | Ground reference for logic and I/O pins.                                                                                                                 |

| Vdd                                                 | 14                    | 15, 16       | 17, 19      | Р                  | -                                    | Positive supply for logic and I/O pins.                                                                                                                  |

#### TABLE 1-2: PIC16F818/819 PINOUT DESCRIPTIONS (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address               | Name       | Bit 7                                                        | Bit 6                                               | Bit 5          | Bit 4          | Bit 3          | Bit 2                 | Bit 1           | Bit 0    | Value on<br>POR, BOR | Details on<br>page: |

|-----------------------|------------|--------------------------------------------------------------|-----------------------------------------------------|----------------|----------------|----------------|-----------------------|-----------------|----------|----------------------|---------------------|

| Bank 2                |            |                                                              |                                                     |                |                |                |                       |                 |          |                      |                     |

| 100h <sup>(1)</sup>   | INDF       | Addressin                                                    | ng this locatio                                     | egister)       | 0000 0000      | 23             |                       |                 |          |                      |                     |

| 101h                  | TMR0       | Timer0 M                                                     | lodule Regist                                       | ter            |                |                |                       |                 |          | xxxx xxxx            | 53                  |

| 102h <sup>(1</sup>    | PCL        | Program                                                      | Counter's (P                                        | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 103h <sup>(1)</sup>   | STATUS     | IRP                                                          | RP1                                                 | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 104h <sup>(1)</sup>   | FSR        | Indirect D                                                   | ata Memory                                          | Address Poir   | nter           |                |                       |                 |          | xxxx xxxx            | 23                  |

| 105h                  | —          | Unimpler                                                     | nented                                              |                |                |                |                       |                 |          | _                    | —                   |

| 106h                  | PORTB      | PORTB [                                                      | Data Latch w                                        | hen written; P | ORTB pins w    | hen read       |                       |                 |          | XXXX XXXX            | 43                  |

| 107h                  | —          | Unimplen                                                     | nented                                              |                |                |                |                       |                 |          | —                    | _                   |

| 108h                  | —          | Unimplen                                                     | nented                                              |                |                |                |                       |                 |          | —                    | —                   |

| 109h                  | —          | Unimplen                                                     | nented                                              |                |                |                |                       |                 |          | —                    | —                   |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _                                                            | —                                                   | _              | Write Buffer   | for the upper  | 5 bits of the F       | Program Cou     | nter     | 0 0000               | 23                  |

| 10Bh <sup>(1)</sup>   | INTCON     | GIE                                                          | PEIE                                                | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 10Ch                  | EEDATA     | EEPROM                                                       | I/Flash Data                                        | Register Low   | Byte           |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Dh                  | EEADR      | EEPROM                                                       | 1/Flash Addre                                       | ess Register L | ow Byte        |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Eh                  | EEDATH     | _                                                            | —                                                   | EEPROM/Fla     | ash Data Reg   | ister High Byt | е                     |                 |          | xx xxxx              | 25                  |

| 10Fh                  | EEADRH     | —                                                            | —                                                   | —              | —              | —              | EEPROM/F<br>High Byte | lash Address    | Register | xxx                  | 25                  |

| Bank 3                |            |                                                              |                                                     |                |                |                |                       |                 |          |                      |                     |

| 180h <sup>(1)</sup>   | INDF       | Addressin                                                    | ng this locatio                                     | on uses conte  | ents of FSR to | address data   | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 181h                  | OPTION_REG | RBPU                                                         | INTEDG                                              | TOCS           | TOSE           | PSA            | PS2                   | PS1             | PS0      | 1111 1111            | 17, 54              |

| 182h <sup>(1)</sup>   | PCL        | Program                                                      | Counter's (P                                        | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 183h <sup>(1)</sup>   | STATUS     | IRP                                                          | RP1                                                 | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 184h <sup>(1)</sup>   | FSR        | Indirect D                                                   | Indirect Data Memory Address Pointer                |                |                |                |                       |                 |          |                      | 23                  |

| 185h                  | —          | Unimplen                                                     | nented                                              |                |                |                |                       |                 |          | —                    | _                   |

| 186h                  | TRISB      | PORTB [                                                      | PORTB Data Direction Register                       |                |                |                |                       |                 |          |                      | 43                  |

| 187h                  | _          | Unimplen                                                     | Unimplemented                                       |                |                |                |                       |                 |          |                      | —                   |

| 188h                  | _          | Unimplen                                                     | Unimplemented                                       |                |                |                |                       |                 |          |                      | —                   |

| 189h                  | _          | Unimplemented                                                |                                                     |                |                |                |                       |                 |          |                      | —                   |

| 18Ah <sup>(1,2)</sup> | PCLATH     | — — Write Buffer for the upper 5 bits of the Program Counter |                                                     |                |                |                |                       |                 | 0 0000   | 23                   |                     |

| 18Bh <sup>(1)</sup>   | INTCON     | GIE                                                          | PEIE                                                | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 18Ch                  | EECON1     | EEPGD                                                        | _                                                   | _              | FREE           | WRERR          | WREN                  | WR              | RD       | xx x000              | 26                  |

|                       | 1          |                                                              | EEPROM Control Register 2 (not a physical register) |                |                |                |                       |                 |          |                      | 25                  |

| 18Dh                  | EECON2     | LEFRON                                                       | 1 0011001100                                        |                |                |                |                       |                 |          |                      |                     |

| 18Dh<br>18Eh          | EECON2     |                                                              | l; maintain cl                                      |                | p, e.e         | ,              |                       |                 |          | 0000 0000            | —                   |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

-n = Value at POR

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| EN <b>2-4</b> .                                                                                               | FIEL. FERI                                                                                                    | FHERAL      | INTERNU         |               | REGIST   |            | RE33 00      | 11)    |  |  |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------|----------|------------|--------------|--------|--|--|--|

|                                                                                                               | U-0                                                                                                           | R/W-0       | U-0             | U-0           | R/W-0    | R/W-0      | R/W-0        | R/W-0  |  |  |  |

|                                                                                                               |                                                                                                               | ADIE        | _               | _             | SSPIE    | CCP1IE     | TMR2IE       | TMR1IE |  |  |  |

|                                                                                                               | bit 7 bit 0                                                                                                   |             |                 |               |          |            |              |        |  |  |  |

| bit 7                                                                                                         | Unimplemer                                                                                                    | nted: Read  | <b>d as</b> '0' |               |          |            |              |        |  |  |  |

| bit 6                                                                                                         | ADIE: A/D C                                                                                                   | onverter Ir | nterrupt Enab   | ole bit       |          |            |              |        |  |  |  |

| <ul> <li>1 = Enables the A/D converter interrupt</li> <li>0 = Disables the A/D converter interrupt</li> </ul> |                                                                                                               |             |                 |               |          |            |              |        |  |  |  |

| bit 5-4                                                                                                       | Unimplemer                                                                                                    | nted: Read  | <b>d as</b> '0' |               |          |            |              |        |  |  |  |

| bit 3                                                                                                         | SSPIE: Sync                                                                                                   | hronous S   | erial Port Int  | errupt Enable | e bit    |            |              |        |  |  |  |

|                                                                                                               | 1 = Enables the SSP interrupt                                                                                 |             |                 |               |          |            |              |        |  |  |  |

|                                                                                                               | 0 = Disables                                                                                                  | s the SSP i | nterrupt        |               |          |            |              |        |  |  |  |

| bit 2                                                                                                         | CCP1IE: CC                                                                                                    | P1 Interru  | ot Enable bit   |               |          |            |              |        |  |  |  |

|                                                                                                               | 1 = Enables the CCP1 interrupt                                                                                |             |                 |               |          |            |              |        |  |  |  |

|                                                                                                               | 0 = Disables                                                                                                  |             |                 |               |          |            |              |        |  |  |  |

| bit 1                                                                                                         | TMR2IE: TM                                                                                                    |             |                 |               | bit      |            |              |        |  |  |  |

|                                                                                                               | 1 = Enables the TMR2 to PR2 match interrupt                                                                   |             |                 |               |          |            |              |        |  |  |  |

| <b>h</b> :+ 0                                                                                                 | 0 = Disables the TMR2 to PR2 match interrupt                                                                  |             |                 |               |          |            |              |        |  |  |  |

| bit 0                                                                                                         | TMR1IE: TMR1 Overflow Interrupt Enable bit                                                                    |             |                 |               |          |            |              |        |  |  |  |

|                                                                                                               | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |             |                 |               |          |            |              |        |  |  |  |

|                                                                                                               |                                                                                                               |             |                 | unupt         |          |            |              |        |  |  |  |

|                                                                                                               | Legend:                                                                                                       |             |                 |               |          |            |              |        |  |  |  |

|                                                                                                               | R = Readab                                                                                                    | ole bit     | W = W           | Vritable bit  | U = Unin | nplemented | bit, read as | ʻ0'    |  |  |  |

|                                                                                                               |                                                                                                               |             |                 |               |          |            |              |        |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

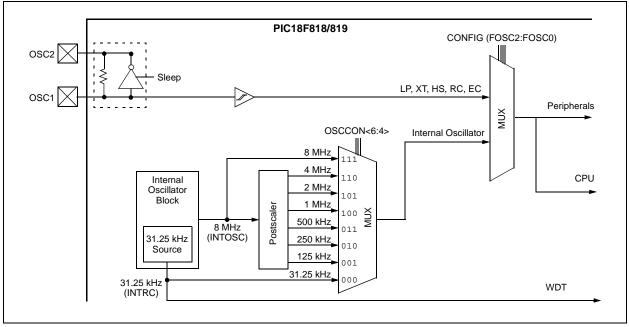

#### FIGURE 4-6: PIC16F818/819 CLOCK DIAGRAM

#### **REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)**

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | R-0  | U-0 | U-0   |

|-------|-------|-------|-------|-----|------|-----|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | —   | IOFS | _   | _     |

| bit 7 |       |       |       |     |      |     | bit 0 |

#### bit 7 Unimplemented: Read as '0'

| bit 6-4 | IRCF2:IRCF0: Internal Oscillator Frequency Select bits |

|---------|--------------------------------------------------------|

|         | 111 = 8 MHz (8 MHz source drives clock directly)       |

|         | 110 <b>= 4 MHz</b>                                     |

|         | 101 = 2  MHz                                           |

|         | 100 = 1 MHz                                            |

|         | 011 = 500 kHz                                          |

|         | 010 = 250 kHz                                          |

|         | 001 = 125  kHz                                         |

|         | 000 = 31.25 kHz (INTRC source drives clock directly)   |

| bit 3   | Unimplemented: Read as '0'                             |

| bit 2   | IOFS: INTOSC Frequency Stable bit                      |

|         | 1 = Frequency is stable                                |

|         | 0 = Frequency is not stable                            |

| bit 1-0 | Unimplemented: Read as '0'                             |

|         | Legend:                                                |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

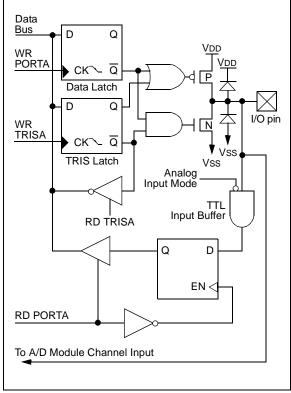

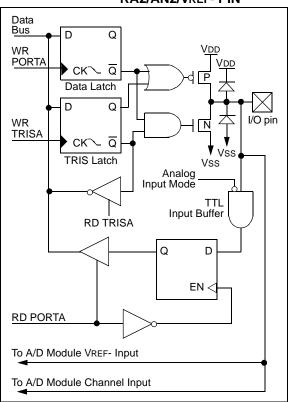

FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

FIGURE 5-2:

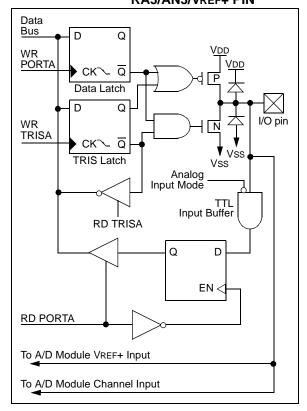

#### BLOCK DIAGRAM OF RA3/AN3/VREF+ PIN

#### FIGURE 5-3: BLOCK DIAGRAM OF RA2/AN2/VREF- PIN

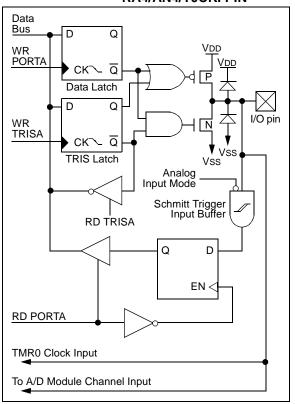

FIGURE 5-4:

#### BLOCK DIAGRAM OF RA4/AN4/T0CKI PIN

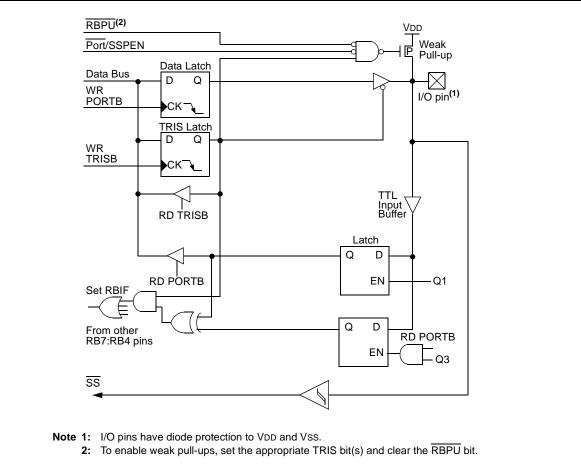

#### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

| Name                        | Bit#  | Buffer                | Function                                                                                                                                                                       |

|-----------------------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                     | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                                                                                  |

| RB1/SDI/SDA                 | bit 1 | TTL/ST <sup>(5)</sup> | Input/output pin, SPI data input pin or I <sup>2</sup> C™ data I/O pin.<br>Internal software programmable weak pull-up.                                                        |

| RB2/SDO/CCP1                | bit 2 | TTL/ST <sup>(4)</sup> | Input/output pin, SPI data output pin or<br>Capture input/Compare output/PWM output pin.<br>Internal software programmable weak pull-up.                                       |

| RB3/CCP1/PGM <sup>(3)</sup> | bit 3 | TTL/ST <sup>(2)</sup> | Input/output pin, Capture input/Compare output/PWM output pin<br>or programming in LVP mode. Internal software programmable<br>weak pull-up.                                   |

| RB4/SCK/SCL                 | bit 4 | TTL/ST <sup>(5)</sup> | Input/output pin or SPI and I <sup>2</sup> C clock pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                             |

| RB5/SS                      | bit 5 | TTL                   | Input/output pin or SPI slave select pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                           |

| RB6/T1OSO/T1CKI/<br>PGC     | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator output pin, Timer1 clock input pin or serial programming clock (with interrupt-on-change).<br>Internal software programmable weak pull-up. |

| RB7/T1OSI/PGD               | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator input pin or serial programming data<br>(with interrupt-on-change).<br>Internal software programmable weak pull-up.                        |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: Low-Voltage ICSP<sup>™</sup> Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 18-pin mid-range devices.

- 4: This buffer is a Schmitt Trigger input when configured for CCP or SSP mode.

- **5:** This buffer is a Schmitt Trigger input when configured for SPI or I<sup>2</sup>C mode.

| TABLE 5-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx            | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111            | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

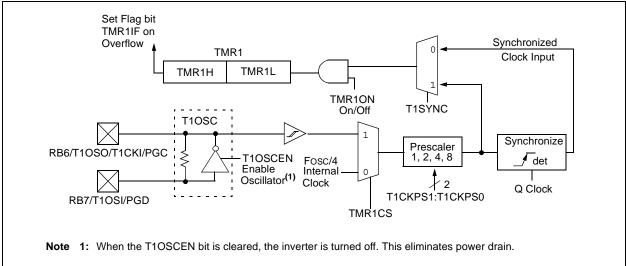

#### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

#### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode depending on the setting of the TMR1CS bit.

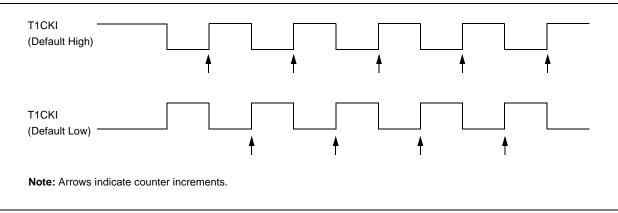

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set, or on pin RB6/T1OSO/T1CKI/PGC when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 7-1: TIMER1 INCREMENTING EDGE

#### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. The seven possible options for TAD are:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu$ s and not greater than 6.4  $\mu$ s.

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 11.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current out of the device specification.

#### TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (F))

|                       | AD Clock Source (TAD) |           |                          |  |  |  |  |

|-----------------------|-----------------------|-----------|--------------------------|--|--|--|--|

| Operation             | ADCS<2>               | ADCS<1:0> | Maximum Device Frequency |  |  |  |  |

| 2 Tosc                | 0                     | 00        | 1.25 MHz                 |  |  |  |  |

| 4 Tosc                | 1                     | 00        | 2.5 MHz                  |  |  |  |  |

| 8 Tosc                | 0                     | 01        | 5 MHz                    |  |  |  |  |

| 16 Tosc               | 1                     | 01        | 10 MHz                   |  |  |  |  |

| 32 Tosc               | 0                     | 10        | 20 MHz                   |  |  |  |  |

| 64 Tosc               | 1                     | 10        | 20 MHz                   |  |  |  |  |

| RC <sup>(1,2,3)</sup> | Х                     | 11        | (Note 1)                 |  |  |  |  |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for Sleep operation.

3: For extended voltage devices (LF), please refer to Section 15.0 "Electrical Characteristics".

NOTES:

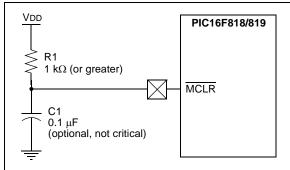

### 12.3 MCLR

PIC16F818/819 device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-2, is suggested.

The RA5/MCLR/VPP pin can be configured for  $\overline{\text{MCLR}}$  (default) or as an I/O pin (RA5). This is configured through the MCLRE bit in the Configuration Word register.

#### FIGURE 12-2: RECOMMENDED MCLR CIRCUIT

#### 12.4 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V-1.7V). To take advantage of the POR, tie the  $\underline{MCLR}$  pin to VDD as described in Section 12.3 "MCLR". A maximum rise time for VDD is specified. See Section 15.0 "Electrical Characteristics" for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. For more information, see Application Note *AN607, "Power-up Trouble Shooting"* (DS00607).

### 12.5 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC16F818/819 is a counter that uses the INTRC oscillator as the clock input. This yields a count of 72 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC and will vary from chip-to-chip due to temperature and process variation. See DC parameter #33 for details.

The PWRT is enabled by clearing configuration bit, PWRTEN.

### 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### 12.7 Brown-out Reset (BOR)

The configuration bit, BOREN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter #D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ s), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer (if enabled) will keep the device in Reset for TPWRT (parameter #33, about 72 ms). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. Unlike previous PIC16 devices, the PWRT is no longer automatically enabled when the Brown-out Reset circuit is enabled. The PWRTEN and BOREN configuration bits are independent of each other.

#### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F818/819 device operating in parallel.

Table 12-3 shows the Reset conditions for the Status, PCON and PC registers, while Table 12-4 shows the Reset conditions for all the registers.

#### 14.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 14.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 14.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 14.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 14.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### 14.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 14.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 14.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 15.1 DC Characteristics: Supply Voltage PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| PIC16LF818/819<br>(Industrial)          |      |                                                                     | Standard Operating Condition |     |       |            | ons (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial                                               |  |  |

|-----------------------------------------|------|---------------------------------------------------------------------|------------------------------|-----|-------|------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F818/819<br>(Industrial, Extended) |      |                                                                     | Operating temperature        |     |       |            | ons (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |  |  |

| Param<br>No. Symbol Characteristic      |      | Min                                                                 | Тур                          | Max | Units | Conditions |                                                                                                                            |  |  |

|                                         | Vdd  | Supply Voltage                                                      |                              |     |       |            |                                                                                                                            |  |  |

| D001                                    |      | PIC16LF818/819                                                      | 2.0                          |     | 5.5   | V          | HS, XT, RC and LP Oscillator mode                                                                                          |  |  |

| D001                                    |      | PIC16F818/819                                                       | 4.0                          |     | 5.5   | V          |                                                                                                                            |  |  |

| D002                                    | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5                          | —   | _     | V          |                                                                                                                            |  |  |

| D003                                    | VPOR | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                            | —   | 0.7   | V          | See Section 12.4 "Power-on Reset (POR)"<br>for details                                                                     |  |  |

| D004                                    | SVDD | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                         | —   | _     | V/ms       | See Section 12.4 "Power-on Reset (POR)"<br>for details                                                                     |  |  |

|                                         | VBOR | Brown-out Reset Voltage                                             |                              |     |       | •          |                                                                                                                            |  |  |

| D005                                    |      | PIC16LF818/819                                                      | 3.65                         | _   | 4.35  | V          |                                                                                                                            |  |  |

| D005                                    |      | PIC16F818/819                                                       | 3.65                         |     | 4.35  | V          | FMAX = 14 MHz <sup>(2)</sup>                                                                                               |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data

2: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

#### 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF818/819<br>(Industrial)<br>PIC16F818/819<br>(Industrial, Extended) |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |    |        |            |                                                                  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|----|--------|------------|------------------------------------------------------------------|--|--|--|

|                                                                           |                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |     |    |        |            |                                                                  |  |  |  |

| Param<br>No.                                                              | Device                                | Typ Max Units Conditions                                                                                                           |     |    |        |            |                                                                  |  |  |  |

|                                                                           | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                    |     |    |        |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 8                                                                                                                                  | 20  | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 7                                                                                                                                  | 15  | μA | +25°C  | VDD = 2.0V |                                                                  |  |  |  |

|                                                                           |                                       | 7                                                                                                                                  | 15  | μA | +85°C  |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 16                                                                                                                                 | 30  | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 14                                                                                                                                 | 25  | μΑ | +25°C  | VDD = 3.0V | Fosc = 31.25 kHz                                                 |  |  |  |

|                                                                           |                                       | 14                                                                                                                                 | 25  | μΑ | +85°C  |            | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator)                 |  |  |  |

|                                                                           | All devices                           | 32                                                                                                                                 | 40  | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 29                                                                                                                                 | 35  | μA | +25°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 29                                                                                                                                 | 35  | μA | +85°C  | VDD = 5.0V |                                                                  |  |  |  |

|                                                                           | Extended devices                      | 35                                                                                                                                 | 45  | μA | +125°C |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 132                                                                                                                                | 160 | μA | -40°C  |            | Fosc = 1 MHz<br>( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |  |  |  |

|                                                                           |                                       | 126                                                                                                                                | 155 | μA | +25°C  | VDD = 2.0V |                                                                  |  |  |  |

|                                                                           |                                       | 126                                                                                                                                | 155 | μA | +85°C  |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 260                                                                                                                                | 310 | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 230                                                                                                                                | 300 | μA | +25°C  | VDD = 3.0V |                                                                  |  |  |  |

|                                                                           |                                       | 230                                                                                                                                | 300 | μA | +85°C  |            |                                                                  |  |  |  |

|                                                                           | All devices                           | 560                                                                                                                                | 690 | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 500                                                                                                                                | 650 | μA | +25°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 500                                                                                                                                | 650 | μA | +85°C  | VDD = 5.0V |                                                                  |  |  |  |

|                                                                           | Extended devices                      | 570                                                                                                                                | 710 | μA | +125°C |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 310                                                                                                                                | 420 | μA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 300                                                                                                                                | 410 | μA | +25°C  | VDD = 2.0V |                                                                  |  |  |  |

|                                                                           |                                       | 300                                                                                                                                | 410 | μΑ | +85°C  |            |                                                                  |  |  |  |

|                                                                           | PIC16LF818/819                        | 550                                                                                                                                | 650 | μA | -40°C  |            | Fosc = 4 MHz<br>( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |  |  |  |

|                                                                           |                                       | 530                                                                                                                                | 620 | μA | +25°C  | VDD = 3.0V |                                                                  |  |  |  |

|                                                                           |                                       | 530                                                                                                                                | 620 | μA | +85°C  |            |                                                                  |  |  |  |

|                                                                           | All devices                           | 1.2                                                                                                                                | 1.5 | mA | -40°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 1.1                                                                                                                                | 1.4 | mA | +25°C  |            |                                                                  |  |  |  |

|                                                                           |                                       | 1.1                                                                                                                                | 1.4 | mA | +85°C  | VDD = 5.0V |                                                                  |  |  |  |

|                                                                           | Extended devices                      | 1.3                                                                                                                                | 1.6 | mA | +125°C |            |                                                                  |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

### 15.5 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2ppS           |                                        | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|----------------------------------------|-----------|----------------------------------------|