Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-i-ptsl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name       | Bit 7                                  | Bit 6           | Bit 5                     | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0     | Value on<br>POR, BOR | Details on<br>page: |

|----------------------|------------|----------------------------------------|-----------------|---------------------------|----------------|----------------|---------------|---------------|-----------|----------------------|---------------------|

| Bank 1               |            |                                        |                 |                           |                |                |               |               |           |                      |                     |

| 80h <sup>(1)</sup>   | INDF       | Addressir                              | ng this locati  | on uses conte             | ents of FSR to | o address dat  | ta memory (n  | ot a physical | register) | 0000 0000            | 23                  |

| 81h                  | OPTION_REG | RBPU                                   | INTEDG          | TOCS                      | TOSE           | PSA            | PS2           | PS1           | PS0       | 1111 1111            | 17, 54              |

| 82h <sup>(1)</sup>   | PCL        | Program                                | Counter's (F    | PC) Least Sig             | nificant Byte  |                |               | •             | •         | 0000 0000            | 23                  |

| 83h <sup>(1)</sup>   | STATUS     | IRP                                    | RP1             | RP0                       | TO             | PD             | Z             | DC            | С         | 0001 1xxx            | 16                  |

| 84h <sup>(1)</sup>   | FSR        | Indirect D                             | ata Memory      | Address Poi               | nter           | •              | •             | •             | •         | xxxx xxxx            | 23                  |

| 85h                  | TRISA      | TRISA7                                 | TRISA6          | TRISA5 <sup>(3)</sup>     | PORTA Data     | a Direction Re | egister (TRIS | A<4:0>        |           | 1111 1111            | 39                  |

| 86h                  | TRISB      | PORTB D                                | Data Directio   | n Register                |                |                |               |               |           | 1111 1111            | 43                  |

| 87h                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 88h                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | -                   |

| 89h                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 8Ah <sup>(1,2)</sup> | PCLATH     | —                                      | —               | _                         | Write Buffer   | for the upper  | 5 bits of the | PC            |           | 0 0000               | 23                  |

| 8Bh <sup>(1)</sup>   | INTCON     | GIE                                    | PEIE            | TMR0IE                    | INTE           | RBIE           | TMR0IF        | INTF          | RBIF      | 0000 000x            | 18                  |

| 8Ch                  | PIE1       | _                                      | ADIE            | _                         | _              | SSPIE          | CCP1IE        | TMR2IE        | TMR1IE    | -0 0000              | 19                  |

| 8Dh                  | PIE2       |                                        | _               | _                         | EEIE           |                |               | _             | _         | 0                    | 21                  |

| 8Eh                  | PCON       | —                                      | —               | _                         | —              | —              | —             | POR           | BOR       | dd                   | 22                  |

| 8Fh                  | OSCCON     | _                                      | IRCF2           | IRCF1                     | IRCF0          | —              | IOFS          | _             | _         | -000 -0              | 38                  |

| 90h <sup>(1)</sup>   | OSCTUNE    | —                                      | —               | TUN5                      | TUN4           | TUN3           | TUN2          | TUN1          | TUN0      | 00 0000              | 36                  |

| 91h                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 92h                  | PR2        |                                        | eriod Regist    |                           |                |                |               |               |           | 1111 1111            | 68                  |

| 93h                  | SSPADD     | Synchron                               | ous Serial P    | ort (I <sup>2</sup> C™ mo | de) Address    | Register       | T             | r             | r         | 0000 0000            | 71, 76              |

| 94h                  | SSPSTAT    | SMP                                    | CKE             | D/A                       | Р              | S              | R/W           | UA            | BF        | 0000 0000            | 72                  |

| 95h                  | _          | Unimplen                               | nented          |                           |                |                |               |               |           | _                    |                     |

| 96h                  | _          | Unimplen                               | nented          |                           |                |                |               |               |           | _                    |                     |

| 97h                  |            | Unimplen                               | Unimplemented — |                           |                |                |               |               | _         | —                    |                     |

| 98h                  | —          | Unimplen                               | Unimplemented — |                           |                |                |               |               | —         | —                    |                     |

| 99h                  | —          | Unimplen                               | Unimplemented — |                           |                |                |               |               | —         |                      |                     |

| 9Ah                  | _          | Unimplen                               | Unimplemented — |                           |                |                |               |               | —         | —                    |                     |

| 9Bh                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 9Ch                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 9Dh                  | —          | Unimplen                               | nented          |                           |                |                |               |               |           | —                    | —                   |

| 9Eh                  | ADRESL     | A/D Result Register Low Byte xxxx xxxx |                 |                           |                |                |               | 81            |           |                      |                     |

| 9Fh                  | ADCON1     | ADFM                                   | ADCS2           | —                         | —              | PCFG3          | PCFG2         | PCFG1         | PCFG0     | 00 0000              | 82                  |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:Legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.$

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

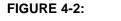

## CERAMIC RESONATOR OPERATION (HS OR XT

**OSC CONFIGURATION)**

- **2:** A series resistor (Rs) may be required.

- 3: RF varies with the resonator chosen (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

#### TABLE 4-2: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |                     |       |       |  |  |  |

|--------------------------------|---------------------|-------|-------|--|--|--|

| Mode                           | Mode Freq OSC1 OSC2 |       |       |  |  |  |

| ХТ                             | 455 kHz             | 56 pF | 56 pF |  |  |  |

|                                | 2.0 MHz             | 47 pF | 47 pF |  |  |  |

|                                | 4.0 MHz             | 33 pF | 33 pF |  |  |  |

| HS                             | 8.0 MHz             | 27 pF | 27 pF |  |  |  |

|                                | 16.0 MHz            | 22 pF | 22 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

Note: When using resonators with frequencies above 3.5 MHz, the use of HS mode rather than XT mode is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is  $330\Omega$ .

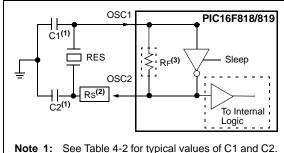

### 4.3 External Clock Input

The ECIO Oscillator mode requires an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the ECIO Oscillator mode, the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 4-3 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

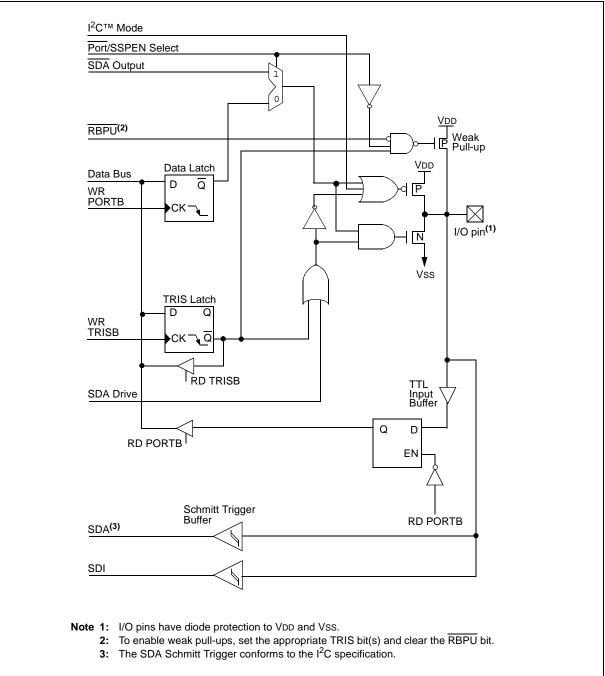

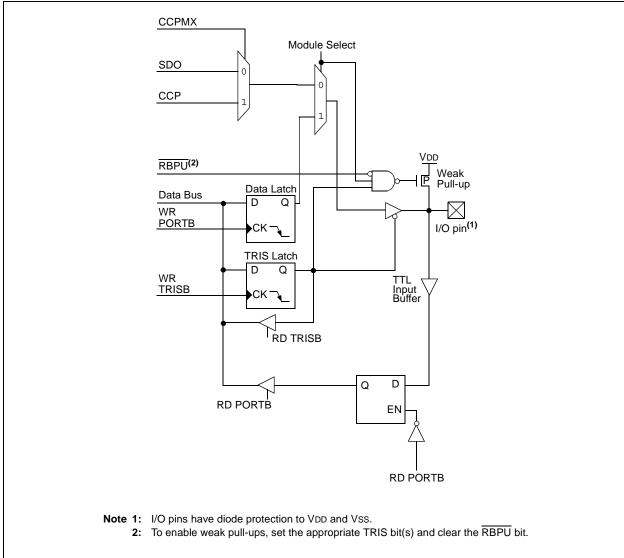

#### FIGURE 5-9: BLOCK DIAGRAM OF RB1 PIN

NOTES:

## 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                 | U-0        | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-0          | R/W-0       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|---------------|--------------|----------------|-------------|--|

| —                                                                                                                                                                   | —          | CCP1X        | CCP1Y        | CCP1M3        | CCP1M2       | CCP1M1         | CCP1M0      |  |

| bit 7                                                                                                                                                               |            |              |              |               |              |                | bit 0       |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |

| Unimpleme                                                                                                                                                           |            |              |              |               |              |                |             |  |

| CCP1X:CCI                                                                                                                                                           | P1Y: PWM   | Least Signi  | ficant bits  |               |              |                |             |  |

| <u>Capture mo</u><br>Unused.                                                                                                                                        | <u>de:</u> |              |              |               |              |                |             |  |

| <u>Compare mo</u><br>Unused.                                                                                                                                        | ode:       |              |              |               |              |                |             |  |

| <u>PWM mode:</u><br>These bits a                                                                                                                                    | -          | LSbs of the  | PWM duty     | cycle. The e  | eight MSbs a | re found in (  | CCPRxL.     |  |

| CCP1M3:CO                                                                                                                                                           | CP1M0: CC  | P1 Mode S    | elect bits   |               |              |                |             |  |

| 0000 <b>= Cap</b>                                                                                                                                                   | ture/Compa | are/PWM di   | sabled (res  | ets CCP1 m    | odule)       |                |             |  |

| 0100 = Cap                                                                                                                                                          | ture mode, | every fallin | g edge       |               |              |                |             |  |

| 0101 = Capture mode, every rising edge                                                                                                                              |            |              |              |               |              |                |             |  |

| 0110 = Capture mode, every 4th rising edge                                                                                                                          |            |              |              |               |              |                |             |  |

| 0111 = Capture mode, every 16th rising edge<br>1000 = Compare mode, set output on match (CCP1IF bit is set)                                                         |            |              |              |               |              |                |             |  |

| 1000 = Compare mode, set output on match (CCP11F bit is set)<br>1001 = Compare mode, clear output on match (CCP11F bit is set)                                      |            |              |              |               |              |                |             |  |

| 1010 <b>= Com</b>                                                                                                                                                   |            |              |              | terrupt on ma |              | F bit is set,  | CCP1 pin is |  |

| 1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |            |              |              |               |              |                |             |  |

| 11xx = PWI                                                                                                                                                          |            |              |              |               | ,            |                | ,           |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |

| Legend:                                                                                                                                                             |            |              |              |               |              |                |             |  |

| <b>Legend:</b><br>R = Readab                                                                                                                                        | le bit     | W = V        | Vritable bit | U = Uni       | mplemented   | l bit, read as | s 'O'       |  |

NOTES:

#### 10.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<4,1> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

Either or both of the following conditions will cause the SSP module not to give this ACK pulse:

- a) The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- b) The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF but bit, SSPIF (PIR1<3>), is set. Table 10-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

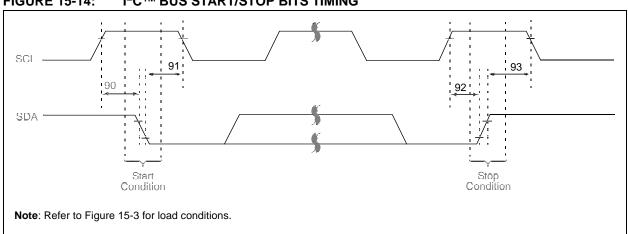

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, are shown in timing parameter #100 and parameter #101.

#### 10.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF, is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

#### 10.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit, BF (SSPSTAT<0>), is set or bit, SSPOV (SSPCON<6>), is set.

An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 10.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RB4/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RB4/SCK/SCL should be enabled by setting bit, CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 10-7).

## 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                     |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| RETFIE           | Return from Interrupt  | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE         | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | None                   | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $TOS \rightarrow PC$ , |                  | d ∈ [0,1]                                                                                                                                                                                                      |

|                  | $1 \rightarrow GIE$    | Operation:       | See description below                                                                                                                                                                                          |

| Status Affected: | None                   | Status Affected: | С                                                                                                                                                                                                              |

|                  |                        | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| RETLW                   | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [label] RRF f,d                                                                                                                                                                                                 |

| Operands:<br>Operation: | $0 \le k \le 255$<br>k $\rightarrow$ (W);                                                                                                                                           | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                 |

| oporation               | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                           |

| Status Affected:        | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                               |

| Description:            | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |

| <b>─→</b> C <b>→</b> | Register f |  |

|----------------------|------------|--|

|                      |            |  |

| RETURN           | Return from Subroutine                                                                                     | SLEEP            | Enter Sleep mode                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                             | Syntax:          | [label] SLEEP                                                                                                                                                                                              |

| Operands:        | None                                                                                                       | Operands:        | None                                                                                                                                                                                                       |

| Operation:       | $TOS \rightarrow PC$                                                                                       | Operation:       | $00h \rightarrow WDT$ ,                                                                                                                                                                                    |

| Status Affected: | None                                                                                                       |                  | $0 \rightarrow WDT$ prescaler,<br>1 $\rightarrow TO$ ,                                                                                                                                                     |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program |                  | $0 \rightarrow PD$                                                                                                                                                                                         |

|                  |                                                                                                            | Status Affected: | TO, PD                                                                                                                                                                                                     |

|                  | counter. This is a two-cycle instruction.                                                                  | Description:     | The Power-Down status bit, PD,<br>is cleared. Time-out status bit,<br>TO, is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

### 14.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 14.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 14.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 14.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 14.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 14.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| DC CHA       | ARACTI | ERISTICS                              | Operating temp | perature    | -40°<br>40°<br>range as | C ≤ TA<br>C ≤ TA<br>descril | ess otherwise stated)<br>≤ +85°C for industrial<br>≤ +125°C for extended<br>bed in Section 15.1 "DC |

|--------------|--------|---------------------------------------|----------------|-------------|-------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                        | Min            | Тур†        | Max                     | Units                       | Conditions                                                                                          |

|              | Vol    | Output Low Voltage                    |                |             |                         |                             |                                                                                                     |

| D080         |        | I/O ports                             | —              | —           | 0.6                     | V                           | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                        |

| D083         |        | OSC2/CLKO<br>(RC oscillator config)   | —              | —           | 0.6                     | V                           | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                                                        |

|              | Vон    | Output High Voltage                   |                |             |                         |                             |                                                                                                     |

| D090         |        | I/O ports <b>(Note 3)</b>             | Vdd - 0.7      | —           | —                       | V                           | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                       |

| D092         |        | OSC2/CLKO<br>(RC oscillator config)   | Vdd - 0.7      | —           | —                       | V                           | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                                                       |

|              |        | Capacitive Loading Specs on           | Output Pins    |             |                         |                             |                                                                                                     |

| D100         | Cosc2  | OSC2 pin                              | _              | —           | 15                      | pF                          | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1                              |

| D101         | Сю     | All I/O pins and OSC2<br>(in RC mode) | —              | —           | 50                      | pF                          |                                                                                                     |

| D102         | Св     | SCL, SDA in I <sup>2</sup> C™ mode    |                | —           | 400                     | pF                          |                                                                                                     |

|              |        | Data EEPROM Memory                    |                |             |                         |                             |                                                                                                     |

| D120         | ED     | Endurance                             | 100K           | 1M          | _                       | E/W                         | -40°C to +85°C                                                                                      |

|              |        |                                       | 10K            | 100K        | _                       | E/W                         | +85°C to +125°C                                                                                     |

| D121         | Vdrw   | VDD for read/write                    | Vmin           | —           | 5.5                     | V                           | Using EECON to read/write,<br>VMIN = min. operating<br>voltage                                      |

| D122         | TDEW   | Erase/write cycle time                |                | 4           | 8                       | ms                          |                                                                                                     |

|              |        | Program Flash Memory                  | 1              |             |                         |                             |                                                                                                     |

| D130         | Eр     | Endurance                             | 10K<br>1K      | 100K<br>10K | _                       | E/W<br>E/W                  | -40°C to +85°C<br>+85°C to +125°C                                                                   |

| D131         | Vpr    | VDD for read                          | VMIN           | _           | 5.5                     | V                           |                                                                                                     |

| D132A        |        | VDD for erase/write                   | Vmin           | -           | 5.5                     | V                           | Using EECON to read/write,<br>VMIN = min. operating<br>voltage                                      |

| D133         | Тре    | Erase cycle time                      | —              | 2           | 4                       | ms                          |                                                                                                     |

| D134         | TPW    | Write cycle time                      | —              | 2           | 4                       | ms                          |                                                                                                     |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

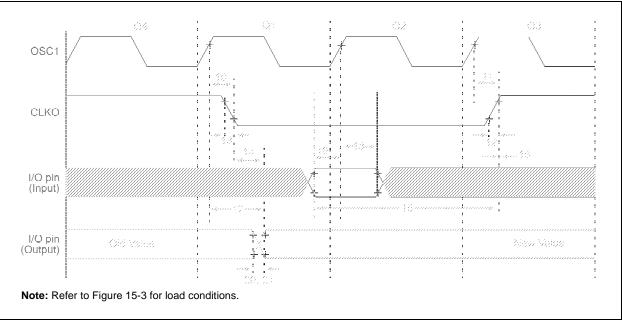

| TABLE 15-2: | CLKO AND I/O TIMING REQUIREMENTS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Param<br>No. | Symbol   | Characterist                         | ic                      | Min        | Тур† | Мах          | Units | Conditions |

|--------------|----------|--------------------------------------|-------------------------|------------|------|--------------|-------|------------|

| 10*          | TosH2ckL | OSC1 $\uparrow$ to CLKO $\downarrow$ |                         | _          | 75   | 200          | ns    | (Note 1)   |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                     |                         | _          | 75   | 200          | ns    | (Note 1)   |

| 12*          | ТскR     | CLKO Rise Time                       |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 13*          | ТскF     | CLKO Fall Time                       |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 14*          | TCKL2IOV | CLKO ↓ to Port Out Valid             |                         |            | _    | 0.5 TCY + 20 | ns    | (Note 1)   |

| 15*          | ТюV2скН  | Port In Valid before CLKO 1          |                         | Tosc + 200 | _    | —            | ns    | (Note 1)   |

| 16*          | TCKH2IOI | Port In Hold after CLKO ↑            |                         | 0          | —    | —            | ns    | (Note 1)   |

| 17*          | TosH2IoV | OSC1 ↑ (Q1 cycle) to Port Out        | Valid                   | _          | 100  | 255          | ns    |            |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to Port            | PIC16F818/819           | 100        | _    | —            | ns    |            |

|              |          | Input Invalid (I/O in hold time)     | PIC16LF818/819          | 200        | —    | _            | ns    |            |

| 19*          | TIOV20sH | Port Input Valid to OSC1 1 (I/O      | in setup time)          | 0          | _    | —            | ns    |            |

| 20*          | TIOR     | Port Output Rise Time                | PIC16 <b>F</b> 818/819  |            | 10   | 40           | ns    |            |

|              |          |                                      | PIC16LF818/819          | _          | —    | 145          | ns    |            |

| 21*          | TIOF     | Port Output Fall Time                | PIC16 <b>F</b> 818/819  |            | 10   | 40           | ns    |            |

|              |          |                                      | PIC16 <b>LF</b> 818/819 |            | _    | 145          | ns    |            |

| 22††*        | TINP     | INT pin High or Low Time             |                         | Тсү        | -    | —            | ns    |            |

| 23††*        | Trbp     | RB7:RB4 Change INT High or           | Low Time                | Тсү        | -    | —            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events, not related to any internal clock edges.

Note 1: Measurements are taken in RC mode, where CLKO output is 4 x Tosc.

| Param<br>No. | Symbol                | Characteristic                                                         |                                                   | Min          | Тур†     | Max       | Units    | Conditions |

|--------------|-----------------------|------------------------------------------------------------------------|---------------------------------------------------|--------------|----------|-----------|----------|------------|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |                                                   | Тсү          | -        | -         | ns       |            |

| 71*          | TscH                  | SCK Input High Time (Slave mode)                                       |                                                   | Tcy + 20     | _        | _         | ns       |            |

| 72*          | TscL                  | SCK Input Low Time (Slave mode)                                        |                                                   | Tcy + 20     | -        | —         | ns       |            |

| 73*          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input to SC                                     | K Edge                                            | 100          | _        | -         | ns       |            |

| 74*          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDI Data Input to SCK Edge                                |                                                   | 100          | —        | -         | ns       |            |

| 75*          | TDOR                  | SDO Data Output Rise Time                                              | PIC16 <b>F</b> 818/819<br>PIC16 <b>LF</b> 818/819 |              | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 76*          | TDOF                  | SDO Data Output Fall Time                                              |                                                   | _            | 10       | 25        | ns       |            |

| 77*          | TssH2doZ              | SS ↑ to SDO Output High-Impedan                                        | се                                                | 10           | _        | 50        | ns       |            |

| 78*          | TscR                  | SCK Output Rise Time<br>(Master mode)                                  | PIC16 <b>F</b> 818/819<br>PIC16 <b>LF</b> 818/819 | _            | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 79*          | TscF                  | SCK Output Fall Time (Master mod                                       | e)                                                | —            | 10       | 25        | ns       |            |

| 80*          | TSCH2DOV,<br>TSCL2DOV | SDO Data Output Valid after SCK<br>Edge                                | PIC16 <b>F</b> 818/819<br>PIC16 <b>LF</b> 818/819 | _            | _        | 50<br>145 | ns<br>ns |            |

| 81*          | TDOV2scH,<br>TDOV2scL | SDO Data Output Setup to SCK Edge                                      |                                                   | Тсү          | —        | -         | ns       |            |

| 82*          | TssL2doV              | SDO Data Output Valid after $\overline{SS} \downarrow Edge$            |                                                   | —            | _        | 50        | ns       |            |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                                    |                                                   | 1.5 Tcy + 40 | —        | -         | ns       |            |

#### TABLE 15-6: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 15-14: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

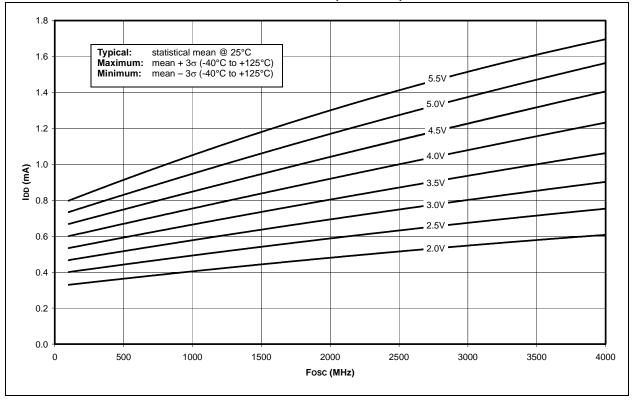

### FIGURE 16-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

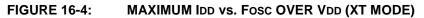

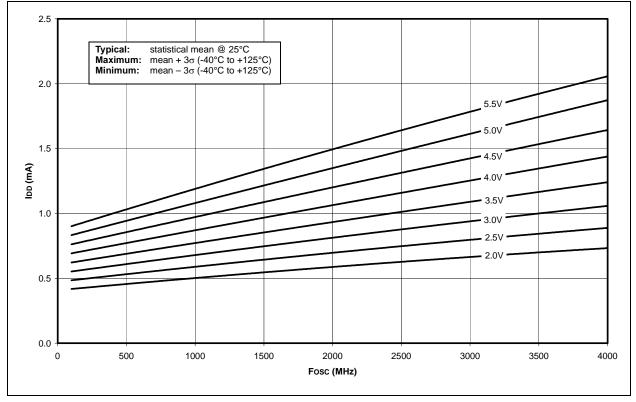

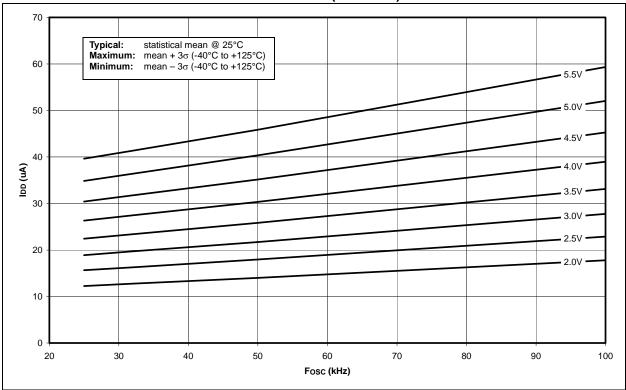

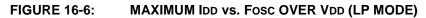

FIGURE 16-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

NOTES:

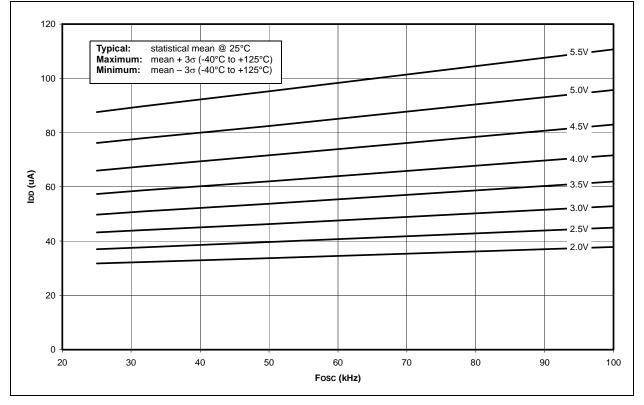

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          | S    |

|--------------------------|------------------|------|----------|------|

| Dimension                | Dimension Limits |      |          | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X20)  | X1               |      |          | 0.45 |

| Contact Pad Length (X20) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

| Writing to Flash Program Memory           | 31        |

|-------------------------------------------|-----------|

| Code Protection                           | . 89, 100 |

| Computed GOTO                             | 23        |

| Configuration Bits                        |           |

| Crystal Oscillator and Ceramic Resonators |           |

| Customer Change Notification Service      | 173       |

| Customer Notification Service             | 173       |

| Customer Support                          | 173       |

## D

| Data EEPROM Memory                     | 25  |

|----------------------------------------|-----|

| Associated Registers                   |     |

| EEADR Register                         |     |

| EEADRH Register                        |     |

| EECON1 Register                        |     |

| EECON2 Register                        |     |

| EEDATA Register                        |     |

| EEDATH Register                        |     |

| Operation During Code-Protect          |     |

| Protection Against Spurious Writes     |     |

| Reading                                |     |

| Write Interrupt Enable Flag (EEIF Bit) |     |

| Writing                                |     |

| Data Memory                            |     |

| Special Function Registers             | 13  |

| DC and AC Characteristics              |     |

| Graphs and Tables                      |     |

| DC Characteristics                     |     |

| Internal RC Accuracy                   | 125 |

| PIC16F818/819, PIC16LF818/819          | 126 |

| Power-Down and Supply Current          |     |

| Supply Voltage                         |     |

| Development Support                    | 111 |

| Device Differences                     | 165 |

| Device Overview                        |     |

| Direct Addressing                      | 24  |

## Е

| EEADR Register25                                           |

|------------------------------------------------------------|

| EEADRH Register25                                          |

| EECON1 Register25                                          |

| EECON2 Register25                                          |

| EEDATA Register25                                          |

| EEDATH Register25                                          |

| Electrical Characteristics115                              |

| Endurance1                                                 |

| Errata3                                                    |

| External Clock Input34                                     |

| External Interrupt Input (RB0/INT). See Interrupt Sources. |

#### F

|                               | ~~   |

|-------------------------------|------|

| Flash Program Memory          | .25  |

| Associated Registers          | . 32 |

| EEADR Register                | .25  |

| EEADRH Register               | .25  |

| EECON1 Register               | .25  |

| EECON2 Register               | .25  |

| EEDATA Register               | .25  |

| EEDATH Register               | .25  |

| Erasing                       | .28  |

| Reading                       | .28  |

| Writing                       | .30  |

| FSR Register13, 14, 15,       | 23   |

| G                             |      |

| General Purpose Register File | .10  |

## I

| /O Ports                                       | 2 |

|------------------------------------------------|---|

| <sup>2</sup> C                                 |   |

| Associated Registers                           | ) |

| Master Mode Operation79                        | ) |

|                                                |   |

| Mode Selection                                 |   |

| Multi-Master Mode Operation                    |   |

| Slave Mode                                     |   |

| Addressing                                     |   |

| Reception                                      |   |

| SCL, SDA Pins                                  |   |

| Transmission                                   |   |

| D Locations                                    |   |

| n-Circuit Debugger                             |   |

| n-Circuit Serial Programming                   |   |

| n-Circuit Serial Programming (ICSP)            |   |

|                                                |   |

| NDF Register                                   |   |

| ndirect Addressing                             |   |

| Instruction Format                             |   |

| Instruction Set                                |   |

| Descriptions                                   |   |

| Read-Modify-Write Operations                   |   |

| Summary Table 104                              |   |

| ADDLW 105                                      |   |

| ADDWF 105                                      |   |

| ANDLW 105                                      | 5 |

| ANDWF 105                                      | 5 |

| BCF 105                                        | 5 |

| BSF 105                                        | 5 |

| BTFSC 106                                      | 3 |

| BTFSS                                          | 3 |

| CALL                                           |   |

| CLRF                                           |   |

| CLRW                                           |   |

| CLRWDT                                         |   |

| COMF                                           |   |

| DECF                                           |   |

| DECFSZ                                         |   |

| GOTO                                           |   |

| INCF                                           |   |

| INCF                                           |   |

| IORLW                                          |   |

| IORUV                                          |   |

| MOVF                                           |   |

|                                                |   |

|                                                |   |

| MOVWF                                          |   |

| NOP                                            |   |

| RETFIE                                         |   |

| RETLW                                          |   |

| RETURN                                         |   |

| RLF 109                                        |   |

| RRF 109                                        |   |

| SLEEP 109                                      |   |

| SUBLW 110                                      |   |

| SUBWF 110                                      | ) |

| SWAPF 110                                      | ) |

| XORLW 110                                      |   |

| XORWF 110                                      | ) |

| NT Interrupt (RB0/INT). See Interrupt Sources. |   |

| NTCON Register                                 | 5 |

| GIE Bit                                        |   |

| INTE Bit                                       |   |

| INTF Bit                                       |   |

| RBIF Bit                                       |   |

|                                                |   |