Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

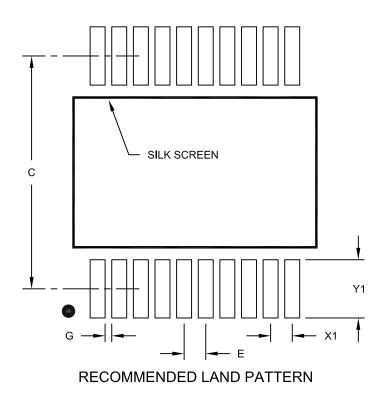

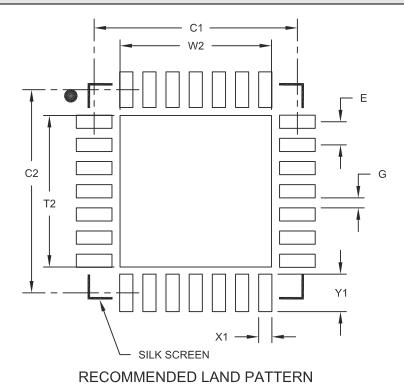

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-i-sotsl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank for code reduction and quicker access (e.g., the Status register is in Banks 0-3).

| Note: | EEPROM data memory description can be found in Section 3.0 "Data EEPROM and |

|-------|-----------------------------------------------------------------------------|

|       | Flash Program Memory" of this data sheet.                                   |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register, FSR.

| Address              | Name       | Bit 7      | Bit 6          | Bit 5                     | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0     | Value on<br>POR, BOR | Details on<br>page: |

|----------------------|------------|------------|----------------|---------------------------|----------------|----------------|---------------|---------------|-----------|----------------------|---------------------|

| Bank 1               |            |            |                |                           |                |                |               |               |           |                      |                     |

| 80h <sup>(1)</sup>   | INDF       | Addressir  | ng this locati | on uses conte             | ents of FSR to | o address dat  | ta memory (n  | ot a physical | register) | 0000 0000            | 23                  |

| 81h                  | OPTION_REG | RBPU       | INTEDG         | TOCS                      | TOSE           | PSA            | PS2           | PS1           | PS0       | 1111 1111            | 17, 54              |

| 82h <sup>(1)</sup>   | PCL        | Program    | Counter's (F   | PC) Least Sig             | nificant Byte  |                |               | •             | •         | 0000 0000            | 23                  |

| 83h <sup>(1)</sup>   | STATUS     | IRP        | RP1            | RP0                       | TO             | PD             | Z             | DC            | С         | 0001 1xxx            | 16                  |

| 84h <sup>(1)</sup>   | FSR        | Indirect D | ata Memory     | Address Poi               | nter           | •              | •             | •             | •         | xxxx xxxx            | 23                  |

| 85h                  | TRISA      | TRISA7     | TRISA6         | TRISA5 <sup>(3)</sup>     | PORTA Data     | a Direction Re | egister (TRIS | A<4:0>        |           | 1111 1111            | 39                  |

| 86h                  | TRISB      | PORTB D    | Data Directio  | n Register                |                |                |               |               |           | 1111 1111            | 43                  |

| 87h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 88h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | -                   |

| 89h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 8Ah <sup>(1,2)</sup> | PCLATH     | —          | —              | _                         | Write Buffer   | for the upper  | 5 bits of the | PC            |           | 0 0000               | 23                  |

| 8Bh <sup>(1)</sup>   | INTCON     | GIE        | PEIE           | TMR0IE                    | INTE           | RBIE           | TMR0IF        | INTF          | RBIF      | 0000 000x            | 18                  |

| 8Ch                  | PIE1       | _          | ADIE           | _                         | _              | SSPIE          | CCP1IE        | TMR2IE        | TMR1IE    | -0 0000              | 19                  |

| 8Dh                  | PIE2       |            | _              | _                         | EEIE           |                |               | _             | _         | 0                    | 21                  |

| 8Eh                  | PCON       | —          | —              | _                         | —              | —              | —             | POR           | BOR       | dd                   | 22                  |

| 8Fh                  | OSCCON     | _          | IRCF2          | IRCF1                     | IRCF0          | —              | IOFS          | _             | _         | -000 -0              | 38                  |

| 90h <sup>(1)</sup>   | OSCTUNE    | —          | —              | TUN5                      | TUN4           | TUN3           | TUN2          | TUN1          | TUN0      | 00 0000              | 36                  |

| 91h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 92h                  | PR2        |            | eriod Regist   |                           |                |                |               |               |           | 1111 1111            | 68                  |

| 93h                  | SSPADD     | Synchron   | ous Serial P   | ort (I <sup>2</sup> C™ mo | de) Address    | Register       | T             | r             | r         | 0000 0000            | 71, 76              |

| 94h                  | SSPSTAT    | SMP        | CKE            | D/A                       | Р              | S              | R/W           | UA            | BF        | 0000 0000            | 72                  |

| 95h                  | _          | Unimplen   | nented         |                           |                |                |               |               |           | _                    |                     |

| 96h                  | _          | Unimplen   | nented         |                           |                |                |               |               |           | _                    |                     |

| 97h                  |            | Unimplen   | nented         |                           |                |                |               |               |           | _                    | —                   |

| 98h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 99h                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 9Ah                  | _          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 9Bh                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 9Ch                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 9Dh                  | —          | Unimplen   | nented         |                           |                |                |               |               |           | —                    | —                   |

| 9Eh                  | ADRESL     | A/D Resu   | It Register L  | ow Byte                   |                | 1              | 1             | n             | n         | XXXX XXXX            | 81                  |

| 9Fh                  | ADCON1     | ADFM       | ADCS2          | —                         | —              | PCFG3          | PCFG2         | PCFG1         | PCFG0     | 00 0000              | 82                  |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:Legend: Legend: Legend: u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.$

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM, with an address range from 00h to 0FFh. Addresses from 80h to FFh are unimplemented on the PIC16F818 device and will read 00h. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. These devices have 1K or 2K words of program Flash, with an address range from 0000h to 03FFh for the PIC16F818 and 0000h to 07FFh for the PIC16F819. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

## 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when Reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

| EXAMPLE 3-4: | ERASING A FLASH PROGRAM MEMORY ROW |

|--------------|------------------------------------|

|--------------|------------------------------------|

|           | BANKSEL | EEADRH      | ;        | Select Bank of EEADRH                                |

|-----------|---------|-------------|----------|------------------------------------------------------|

|           | MOVF    | ADDRH, W    | ;        |                                                      |

|           | MOVWF   | EEADRH      | ;        | MS Byte of Program Address to Erase                  |

|           | MOVF    | ADDRL, W    | ;        |                                                      |

|           | MOVWF   | EEADR       | ;        | LS Byte of Program Address to Erase                  |

| ERASE ROW |         |             |          |                                                      |

| _         | BANKSEL | EECON1      | ;        | Select Bank of EECON1                                |

|           | BSF     | EECON1, EEF | GD ;     | Point to PROGRAM memory                              |

|           | BSF     | EECON1, WRE | EN ;     | Enable Write to memory                               |

|           | BSF     | EECON1, FRE | EE ;     | Enable Row Erase operation                           |

| ;         |         |             |          |                                                      |

|           | BCF     | INTCON, GIE | s;       | Disable interrupts (if using)                        |

|           | MOVLW   | 55h         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write 55h                                            |

|           | MOVLW   | AAh         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write AAh                                            |

|           | BSF     | EECON1, WR  | ;        | Start Erase (CPU stall)                              |

|           | NOP     |             | ;        | Any instructions here are ignored as processor       |

|           |         |             | ;        | halts to begin Erase sequence                        |

|           | NOP     |             | ;        | processor will stop here and wait for Erase complete |

|           |         |             | ;        | after Erase processor continues with 3rd instruction |

|           | BCF     | EECON1, FRE | EE ;     | Disable Row Erase operation                          |

|           | BCF     | EECON1, WRE | EN ;     | Disable writes                                       |

|           | BSF     | INTCON, GIE | ·<br>; 2 | Enable interrupts (if using)                         |

|           |         |             |          |                                                      |

### 4.5.3 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

#### 4.5.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF<2:0> = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.5.5 CLOCK TRANSITION SEQUENCE WHEN THE IRCF BITS ARE MODIFIED

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

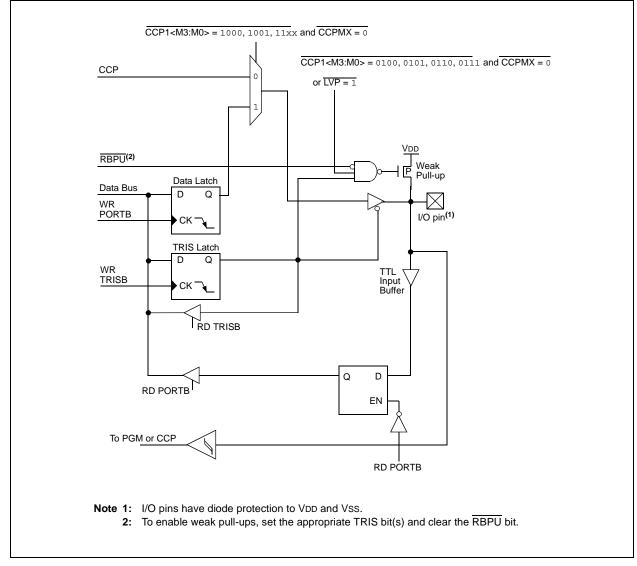

## FIGURE 5-11: BLOCK DIAGRAM OF RB3 PIN

## 6.0 TIMER0 MODULE

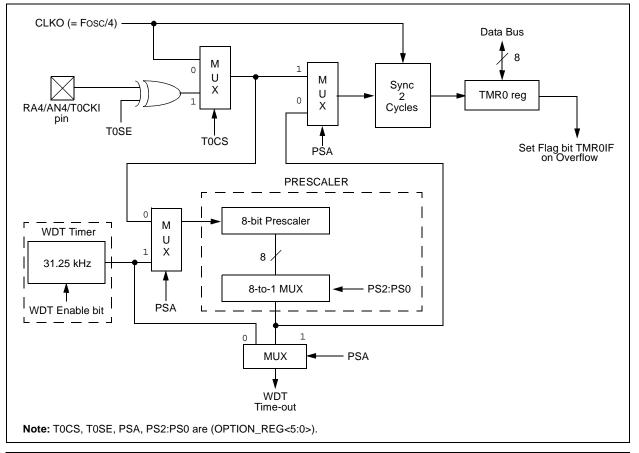

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt-on-overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

Figure 6-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

### 6.1 Timer0 Operation

Timer0 operation is controlled through the OPTION\_REG register (see Register 2-2). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/AN4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.3 "Using Timer0 with an External Clock".

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. **Section 6.4** "**Prescaler**" details the operation of the prescaler.

### 6.2 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit, TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit, TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut-off during Sleep.

#### FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

© 2001-2013 Microchip Technology Inc.

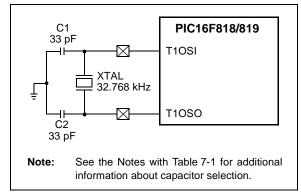

## 7.6 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note: The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) may not function correctly (high-voltage or lowvoltage) or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

#### TABLE 7-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |

|----------|--------|-------|-------|

| LP       | 32 kHz | 33 pF | 33 pF |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- 2: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

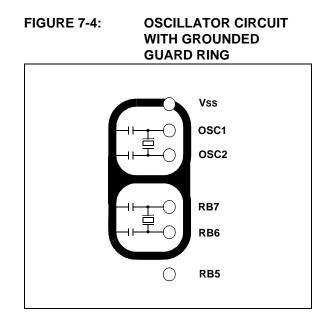

## 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

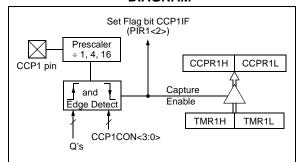

## 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW CAPT PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

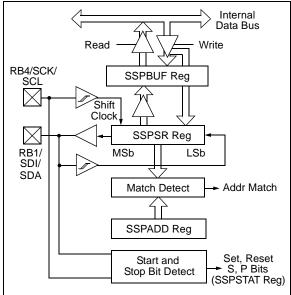

## 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/SCK/SCL pin, which is the clock (SCL) and the RB1/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits.

To ensure proper communication of the I<sup>2</sup>C Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the I<sup>2</sup>C pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the I<sup>2</sup>C pins (PORTx [SDA, SCL]) are changed in software during I<sup>2</sup>C communication using a Read-Modify-Write instruction (BSF, BCF), then the I<sup>2</sup>C mode may stop functioning properly and I<sup>2</sup>C communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the I<sup>2</sup>C pins) using the instruction BSF or BCF during I<sup>2</sup>C communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

#### EXAMPLE 10-1:

| MOVF  | TRISC, W    | ; Example for an 18-pin part such as the PIC16F818/819              |

|-------|-------------|---------------------------------------------------------------------|

| IORLW | 0x18        | ; Ensures <4:3> bits are `11'                                       |

| ANDLW | B'11111001' | ; Sets <2:1> as output, but will not alter other bits               |

|       |             | ; User can use their own logic here, such as IORLW, XORLW and ANDLW |

| MOVWF | TRISC       |                                                                     |

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

FIGURE 10-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for  $I^2C$  operation:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Firmware Controlled Master mode with Start and Stop bit interrupts enabled, slave is Idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation may be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

#### REGISTER 11-2: ADCON1: A/D CONTROL REGISTER 1 (ADDRESS 9Fh)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | —   | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified, 6 Most Significant bits of ADRESH are read as '0'

$_{\rm 0}$  = Left justified, 6 Least Significant bits of ADRESL are read as '0'

bit 6 ADCS2: A/D Clock Divide by 2 Select bit

1 = A/D clock source is divided by 2 when system clock is used 0 = Disabled

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG<3:0>: A/D Port Configuration Control bits

| PCFG | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|------|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000 | Α   | Α     | Α     | Α   | Α   | AVdd  | AVss  | 5/0 |

| 0001 | A   | VREF+ | А     | Α   | А   | AN3   | AVss  | 4/1 |

| 0010 | A   | A     | Α     | Α   | A   | AVdd  | AVss  | 5/0 |

| 0011 | A   | VREF+ | Α     | Α   | A   | AN3   | AVss  | 4/1 |

| 0100 | D   | A     | D     | Α   | A   | AVdd  | AVss  | 3/0 |

| 0101 | D   | VREF+ | D     | Α   | A   | AN3   | AVss  | 2/1 |

| 011x | D   | D     | D     | D   | D   | AVdd  | AVss  | 0/0 |

| 1000 | Α   | VREF+ | Vref- | Α   | A   | AN3   | AN2   | 3/2 |

| 1001 | Α   | Α     | Α     | Α   | A   | AVdd  | AVss  | 5/0 |

| 1010 | A   | VREF+ | A     | Α   | A   | AN3   | AVss  | 4/1 |

| 1011 | Α   | VREF+ | VREF- | Α   | A   | AN3   | AN2   | 3/2 |

| 1100 | A   | VREF+ | VREF- | Α   | A   | AN3   | AN2   | 3/2 |

| 1101 | D   | VREF+ | Vref- | Α   | А   | AN3   | AN2   | 2/2 |

| 1110 | D   | D     | D     | D   | A   | AVdd  | AVss  | 1/0 |

| 1111 | D   | VREF+ | VREF- | D   | A   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = Number of analog input channels/Number of A/D voltage references

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| PMX       DEBUG       WRT1       WRT0       CPD       LVP       BOREN       MCLRE       FOSC2       PWRTEN       WDTEN       FOSC1       FOSC1< |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP: Flash Program Memory Code Protection bit<br>1 = Code protection off<br>0 = All memory locations code-protected<br>CCPMX: CCP1 Pin Selection bit<br>1 = CCP1 function on RB2<br>0 = CCP1 function on RB3<br>DEBUG: In-Circuit Debugger Mode bit<br>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger<br>WRT1:WRT0: Flash Program Memory Write Enable bits<br>For PIC16F818:<br>11 = Write protection off<br>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control<br>01 = 000h to 03FF write-protected<br>For PIC16F819:<br>11 = Write protection off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>1 = Code protection off</li> <li>0 = All memory locations code-protected</li> <li>CCPMX: CCP1 Pin Selection bit</li> <li>1 = CCP1 function on RB2</li> <li>0 = CCP1 function on RB3</li> <li>DEBUG: In-Circuit Debugger Mode bit</li> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>1 = Code protection off</li> <li>0 = All memory locations code-protected</li> <li>CCPMX: CCP1 Pin Selection bit</li> <li>1 = CCP1 function on RB2</li> <li>0 = CCP1 function on RB3</li> <li>DEBUG: In-Circuit Debugger Mode bit</li> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>0 = All memory locations code-protected</li> <li>CCPMX: CCP1 Pin Selection bit</li> <li>1 = CCP1 function on RB2</li> <li>0 = CCP1 function on RB3</li> <li>DEBUG: In-Circuit Debugger Mode bit</li> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>1 = CCP1 function on RB2</li> <li>0 = CCP1 function on RB3</li> <li>DEBUG: In-Circuit Debugger Mode bit</li> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>0 = CCP1 function on RB3</li> <li>DEBUG: In-Circuit Debugger Mode bit</li> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>DEBUG: In-Circuit Debugger Mode bit<br/>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br/>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger<br/>WRT1:WRT0: Flash Program Memory Write Enable bits<br/><u>For PIC16F818:</u><br/>11 = Write protection off<br/>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control<br/>01 = 000h to 03FF write-protected<br/><u>For PIC16F819:</u><br/>11 = Write protection off</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins</li> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger</li> <li>WRT1:WRT0: Flash Program Memory Write Enable bits</li> <li>For PIC16F818:</li> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| For PIC16F818:<br>11 = Write protection off<br>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control<br>01 = 000h to 03FF write-protected<br>For PIC16F819:<br>11 = Write protection off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>11 = Write protection off</li> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>10 = 000h to 01FF write-protected, 0200 to 03FF may be modified by EECON control</li> <li>01 = 000h to 03FF write-protected</li> <li>For PIC16F819:</li> <li>11 = Write protection off</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 01 = 000h to 03FF write-protected<br><u>For PIC16F819:</u><br>11 = Write protection off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| For PIC16F819:<br>11 = Write protection off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10 = 0000h to 01EEh write-protected 0200h to 07EEh may be modified by EECON control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>01 = 0000h to 03FFh write-protected, 0400h to 07FFh may be modified by EECON control</li> <li>00 = 0000h to 05FFh write-protected, 0600h to 07FFh may be modified by EECON control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>CPD:</b> Data EE Memory Code Protection bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 = Code protection off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 = Data EE memory locations code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LVP: Low-Voltage Programming Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>1 = RB3/PGM pin has PGM function, Low-Voltage Programming enabled</li> <li>0 = RB3/PGM pin has digital I/O function, HV on MCLR must be used for programming</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BOREN: Brown-out Reset Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 = BOR enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0 = BOR disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MCLRE: RA5/MCLR/VPP Pin Function Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 = RA5/MCLR/VPP pin function is MCLR<br>0 = RA5/MCLR/VPP pin function is digital I/O, MCLR internally tied to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>PWRTEN:</b> Power-up Timer Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 = PWRT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0 = PWRT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WDTEN: Watchdog Timer Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 = WDT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0 = WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |