Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

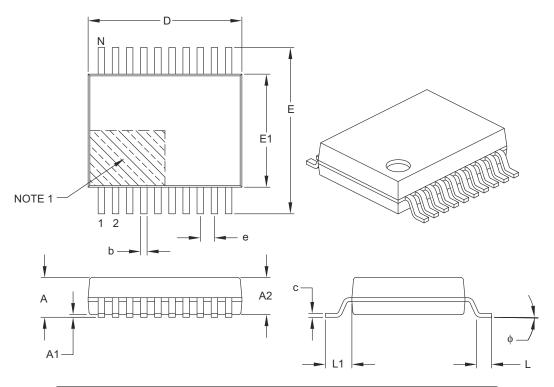

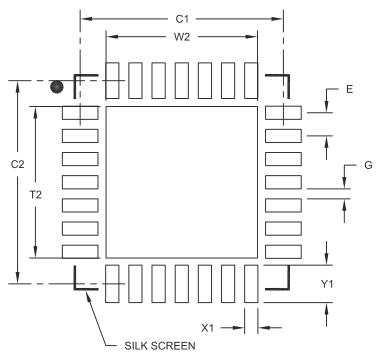

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818-i-ss |

TABLE 1-2: PIC16F818/819 PINOUT DESCRIPTIONS (CONTINUED)

| Pin Name                                            | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type      | Buffer<br>Type                       | Description                                                                                                                                         |

|-----------------------------------------------------|-----------------------|--------------|-------------|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                       |              |             |                    |                                      | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                        |

| RB0/INT<br>RB0<br>INT                               | 6                     | 7            | 7           | I/O<br>I           | TTL<br>ST <sup>(1)</sup>             | Bidirectional I/O pin. External interrupt pin.                                                                                                      |

| RB1/SDI/SDA<br>RB1<br>SDI<br>SDA                    | 7                     | 8            | 8           | I/O<br>I<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>SPI data in.<br>I <sup>2</sup> C™ data.                                                                                   |

| RB2/SDO/CCP1<br>RB2<br>SDO<br>CCP1                  | 8                     | 9            | 9           | I/O<br>O<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin. SPI data out. Capture input, Compare output, PWM output.                                                                     |

| RB3/CCP1/PGM<br>RB3<br>CCP1<br>PGM                  | 9                     | 10           | 10          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin. Capture input, Compare output, PWM output. Low-Voltage ICSP™ Programming enable pin.                                         |

| RB4/SCK/SCL<br>RB4<br>SCK<br>SCL                    | 10                    | 11           | 12          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin. Interrupt-on-change pin. Synchronous serial clock input/output for SPI. Synchronous serial clock input for I <sup>2</sup> C. |

| RB5/SS<br>RB5<br>SS                                 | 11                    | 12           | 13          | I/O<br>I           | TTL<br>TTL                           | Bidirectional I/O pin. Interrupt-on-change pin. Slave select for SPI in Slave mode.                                                                 |

| RB6/T1OSO/T1CKI/PGC<br>RB6<br>T1OSO<br>T1CKI<br>PGC | 12                    | 13           | 15          | I/O<br>O<br>-<br>- | TTL<br>ST<br>ST<br>ST <sup>(2)</sup> | Interrupt-on-change pin. Timer1 Oscillator output. Timer1 clock input. In-circuit debugger and ICSP programming clock pin.                          |

| RB7/T1OSI/PGD<br>RB7<br>T1OSI<br>PGD                | 13                    | 14           | 16          | I/O<br> <br>       | TTL<br>ST<br>ST <sup>(2)</sup>       | Interrupt-on-change pin. Timer1 oscillator input. In-circuit debugger and ICSP programming data pin.                                                |

| Vss                                                 | 5                     | 5, 6         | 3, 5        | Р                  | _                                    | Ground reference for logic and I/O pins.                                                                                                            |

| VDD                                                 | 14                    | 15, 16       | 17, 19      | Р                  | -                                    | Positive supply for logic and I/O pins.                                                                                                             |

**Legend:** I = Input O = Output I/O = Input

I/O = Input/Output P = Power

- = Not used TTL = TTL Input

ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

**2:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### 2.2.2.8 PCON Register

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### REGISTER 2-8: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 **Unimplemented:** Read as '0'

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | d bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM TIMER0 TO WDT**

```

BANKSEL OPTION REG ; Select Bank of OPTION REG

MOVLW b'xx0x0xxx' ; Select clock source and prescale value of

MOVWF OPTION_REG ; other than 1:1

BANKSEL TMR0 ; Select Bank of TMR0

CLRF TMR0

; Clear TMR0 and prescaler

; Select Bank of OPTION_REG

; Select WDT, do not change prescale value

BANKSEL OPTION_REG

MOVLW

b'xxxx1xxx'

MOVWF

OPTION REG

CLRWDT

; Clears WDT and prescaler

b'xxxx1xxx'

MOVLW

; Select new prescale value and WDT

MOVWF OPTION REG

```

#### **EXAMPLE 6-2: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0**

```

CLRWDT ; Clear WDT and prescaler

BANKSEL OPTION_REG ; Select Bank of OPTION_REG

MOVLW b'xxxx0xxx' ; Select TMR0, new prescale

MOVWF OPTION_REG ; value and clock source

```

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|------------------------|--------|--------|-------|-------|--------|-------|-----------|----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 Module Register |        |        |       |       |        |       | xxxx xxxx | uuuu uuuu            |                                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE                    | PEIE   | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF      | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU                   | INTEDG | T0CS   | T0SE  | PSA   | PS2    | PS1   | PS0       | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

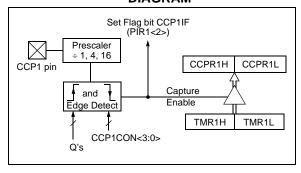

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

**Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

# FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW_CAPT_PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

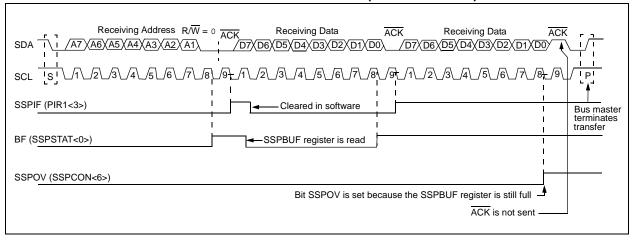

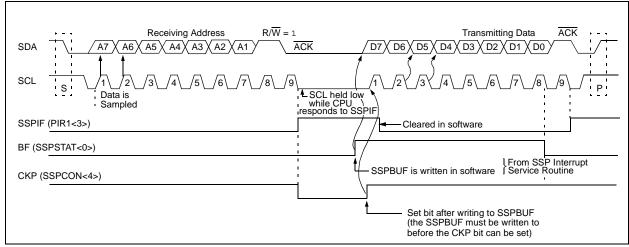

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave device, the slave logic is reset (resets SSPSTAT register) and the slave device then monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RB4/SCK/SCL should be enabled by setting bit, CKP.

TABLE 10-2: DATA TRANSFER RECEIVED BYTE ACTIONS

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK Pulse | Set bit SSPIF (SSP interrupt occurs if enabled) |  |

|---------------------------------------------|-------|--------------------|--------------------|-------------------------------------------------|--|

| BF                                          | SSPOV |                    |                    | (33F interrupt occurs if enabled)               |  |

| 0                                           | 0     | Yes                | Yes                | Yes                                             |  |

| 1                                           | 0     | No                 | No                 | Yes                                             |  |

| 1                                           | 1     | No                 | No                 | Yes                                             |  |

| 0                                           | 1     | No                 | No                 | Yes                                             |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### FIGURE 10-6: I<sup>2</sup>C™ WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

#### FIGURE 10-7: I<sup>2</sup>C™ WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. The seven possible options for TAD are:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu s$  and not greater than 6.4  $\mu s$ .

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 11.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current out of the device specification.

TABLE 11-1: TAD vs. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (F))

|                       | Maximum Davice Erequency |           |                          |

|-----------------------|--------------------------|-----------|--------------------------|

| Operation             | ADCS<2>                  | ADCS<1:0> | Maximum Device Frequency |

| 2 Tosc                | 0                        | 00        | 1.25 MHz                 |

| 4 Tosc                | 1                        | 00        | 2.5 MHz                  |

| 8 Tosc                | 0                        | 01        | 5 MHz                    |

| 16 Tosc               | 1                        | 01        | 10 MHz                   |

| 32 Tosc               | 0                        | 10        | 20 MHz                   |

| 64 Tosc               | 1                        | 10        | 20 MHz                   |

| RC <sup>(1,2,3)</sup> | Х                        | 11        | (Note 1)                 |

- **Note 1:** The RC source has a typical TAD time of 4  $\mu$ s but can vary between 2-6  $\mu$ s.

- 2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for Sleep operation.

- 3: For extended voltage devices (LF), please refer to Section 15.0 "Electrical Characteristics".

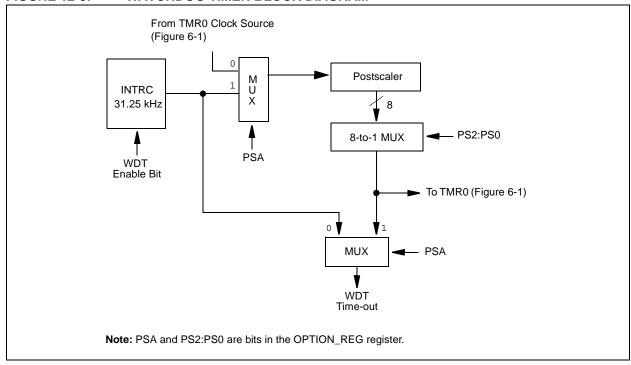

#### 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits"**).

WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | T0SE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

#### 12.14 In-Circuit Debugger

When the DEBUG bit in the Configuration Word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-6 shows which features are consumed by the background debugger.

TABLE 12-6: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7                                   |  |  |

|----------------|--------------------------------------------|--|--|

| Stack          | 1 level                                    |  |  |

| Program Memory | Address 0000h must be NOP                  |  |  |

|                | Last 100h words                            |  |  |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB-0x1EF |  |  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 12.16 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the four Least Significant bits of the ID location are used.

| SUBLW            | Subtract W from Literal                                                                                                      | XORLW            | Exclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBLW k                                                                                                              | Syntax:          | [label] XORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          | Operands:        | $0 \le k \le 255$                                                                                                |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                    |

| Status Affected: | C, DC, Z                                                                                                                     | Status Affected: | Z                                                                                                                |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register are XORed with the eight-bit literal 'k'. The result is placed in the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                         | XORWF            | Exclusive OR W with f                                                                                                                                                     |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] SUBWF f,d                                                                                                                                                       | Syntax:          | [ label ] XORWF f,d                                                                                                                                                       |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        |  |  |

| Operation:       | $(f) - (W) \rightarrow (destination)$                                                                                                                                     | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  | Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                           |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                         |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |  |  |  |  |  |

### 14.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 14.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 14.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 14.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 14.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### 15.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40°C to +125°C                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3 to +14V                        |

| Total power dissipation (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1W                                 |

| Maximum current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200 mA                             |

| Maximum current into VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |

| Input clamp current, lik (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ±20 mA                             |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ±20 mA                             |

| Maximum output current sunk by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25 mA                              |

| Maximum current sunk by PORTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100 mA                             |

| Maximum current sourced by PORTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 mA                             |