Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f818t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Address               | Name       | Bit 7                                    | Bit 6                                  | Bit 5           | Bit 4          | Bit 3         | Bit 2                 | Bit 1         | Bit 0    | Value on<br>POR, BOR | Details on page: |

|-----------------------|------------|------------------------------------------|----------------------------------------|-----------------|----------------|---------------|-----------------------|---------------|----------|----------------------|------------------|

| Bank 2                |            |                                          |                                        |                 |                |               |                       |               |          |                      |                  |

| 100h <sup>(1)</sup>   | INDF       | Addressin                                | ng this locatio                        | on uses conte   | ents of FSR to | address data  | memory (not           | a physical re | egister) | 0000 0000            | 23               |

| 101h                  | TMR0       | Timer0 M                                 | lodule Regist                          | ter             |                |               |                       |               |          | XXXX XXXX            | 53               |

| 102h <sup>(1</sup>    | PCL        | Program                                  | Counter's (P                           | C) Least Sigr   | nificant Byte  |               |                       |               |          | 0000 0000            | 23               |

| 103h <sup>(1)</sup>   | STATUS     | IRP                                      | RP1                                    | RP0             | TO             | PD            | Z                     | DC            | С        | 0001 1xxx            | 16               |

| 104h <sup>(1)</sup>   | FSR        | Indirect D                               | ata Memory                             | Address Poir    | nter           |               |                       |               |          | XXXX XXXX            | 23               |

| 105h                  | —          | Unimpler                                 | nented                                 |                 |                |               |                       |               |          | —                    | _                |

| 106h                  | PORTB      | PORTB [                                  | Data Latch w                           | hen written; P  | ORTB pins w    | hen read      |                       |               |          | XXXX XXXX            | 43               |

| 107h                  | —          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          | —                    | _                |

| 108h                  | —          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          | —                    | _                |

| 109h                  | —          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          | —                    | _                |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _                                        | _                                      | _               | Write Buffer   | for the upper | 5 bits of the F       | Program Cour  | nter     | 0 0000               | 23               |

| 10Bh <sup>(1)</sup>   | INTCON     | GIE                                      | PEIE                                   | TMR0IE          | INTE           | RBIE          | TMR0IF                | INTF          | RBIF     | 0000 000x            | 18               |

| 10Ch                  | EEDATA     | EEPROM                                   | 1/Flash Data                           | Register Low    | Byte           |               |                       |               |          | XXXX XXXX            | 25               |

| 10Dh                  | EEADR      | EEPROM                                   | EEPROM/Flash Address Register Low Byte |                 |                |               |                       |               |          | XXXX XXXX            | 25               |

| 10Eh                  | EEDATH     | — — EEPROM/Flash Data Register High Byte |                                        |                 |                |               |                       | xx xxxx       | 25       |                      |                  |

| 10Fh                  | EEADRH     | —                                        | —                                      | —               | —              | —             | EEPROM/F<br>High Byte | lash Address  | Register | XXX                  | 25               |

| Bank 3                |            |                                          |                                        |                 |                |               |                       |               |          |                      |                  |

| 180h <sup>(1)</sup>   | INDF       | Addressin                                | ng this locatio                        | on uses conte   | ents of FSR to | address data  | memory (not           | a physical re | egister) | 0000 0000            | 23               |

| 181h                  | OPTION_REG | RBPU                                     | INTEDG                                 | TOCS            | TOSE           | PSA           | PS2                   | PS1           | PS0      | 1111 1111            | 17, 54           |

| 182h <sup>(1)</sup>   | PCL        | Program                                  | Counter's (P                           | C) Least Sigr   | ificant Byte   |               |                       |               |          | 0000 0000            | 23               |

| 183h <sup>(1)</sup>   | STATUS     | IRP                                      | RP1                                    | RP0             | TO             | PD            | Z                     | DC            | С        | 0001 1xxx            | 16               |

| 184h <sup>(1)</sup>   | FSR        | Indirect D                               | ata Memory                             | Address Poir    | nter           |               |                       |               |          | XXXX XXXX            | 23               |

| 185h                  | _          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          | _                    | —                |

| 186h                  | TRISB      | PORTB [                                  | Data Direction                         | n Register      |                |               |                       |               |          | 1111 1111            | 43               |

| 187h                  | _          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          | _                    | —                |

| 188h                  | _          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          |                      | —                |

| 189h                  | _          | Unimplen                                 | nented                                 |                 |                |               |                       |               |          |                      | —                |

| 18Ah <sup>(1,2)</sup> | PCLATH     |                                          | _                                      | _               | Write Buffer   | for the upper | 5 bits of the F       | Program Cour  | nter     | 0 0000               | 23               |

| 18Bh <sup>(1)</sup>   | INTCON     | GIE                                      | PEIE                                   | TMR0IE          | INTE           | RBIE          | TMR0IF                | INTF          | RBIF     | 0000 000x            | 18               |

| 18Ch                  | EECON1     | EEPGD                                    | —                                      | —               | FREE           | WRERR         | WREN                  | WR            | RD       | xx x000              | 26               |

| 18Dh                  | EECON2     | EEPRON                                   | Control Reg                            | gister 2 (not a | physical regis | ter)          |                       |               |          |                      | 25               |

| 18Eh                  | _          | Reserved                                 | l; maintain cl                         | ear             |                |               |                       |               |          | 0000 0000            | —                |

|                       |            |                                          | eserved; maintain clear 0000 0000      |                 |                |               |                       |               |          |                      |                  |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-          | 0 R/                      | W-0      | R/W-0                              | R/W-0        | R/W-0         | R/W-0         | R/W-0        | R/W-x     |

|---------------|---------------------------|----------|------------------------------------|--------------|---------------|---------------|--------------|-----------|

| GIE           | Р                         | EIE      | TMR0IE                             | INTE         | RBIE          | TMR0IF        | INTF         | RBIF      |

| bit 7         |                           |          |                                    |              |               |               |              | bit (     |

| GIE: G        | lobal Inter               | rupt En  | able bit                           |              |               |               |              |           |

|               | ables all u<br>sables all |          | ed interrupts<br>its               |              |               |               |              |           |

| PEIE:         | Peripheral                | Interru  | pt Enable bit                      |              |               |               |              |           |

|               |                           |          | ed periphera<br>ral interrupts     |              |               |               |              |           |

| TMR0I         | E: TMR0                   | Overflov | w Interrupt E                      | nable bit    |               |               |              |           |

|               | ables the sables the      |          | •                                  |              |               |               |              |           |

| INTE:         | RB0/INT E                 | External | Interrupt En                       | able bit     |               |               |              |           |

|               |                           |          | IT external in<br>NT external ir   |              |               |               |              |           |

| <b>RBIE:</b>  | RB Port C                 | hange    | Interrupt Ena                      | ble bit      |               |               |              |           |

|               |                           | •        | t change inte<br>rt change inte    | •            |               |               |              |           |

| TMR0I         | F: TMR0                   | Overflov | w Interrupt F                      | lag bit      |               |               |              |           |

|               |                           |          | overflowed (r<br>ot overflow       | must be clea | ared in softv | vare)         |              |           |

| INTF:         | RB0/INT E                 | External | Interrupt Fla                      | g bit        |               |               |              |           |

|               |                           |          | nal interrupt on<br>al interrupt o | ·            |               | ed in softwa  | ire)         |           |

| <b>RBIF</b> : | RB Port C                 | hange l  | nterrupt Flag                      | g bit        |               |               |              |           |

|               |                           |          | ll continue to<br>bit RBIF to b    | •            | RBIF. Read    | ing PORTB     | will end the | e mismatc |

|               |                           |          | RB7:RB4 pin<br>34 pins have        |              |               | be cleared in | n software)  |           |

| Leger         | d:                        |          |                                    |              |               |               |              |           |

| R = R         | eadable bi                | it       | W = Wr                             | itable bit   | U = Unim      | plemented     | bit, read as | '0'       |

| - L           |                           |          | (4) D'                             | • •          |               |               | D'' '        |           |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

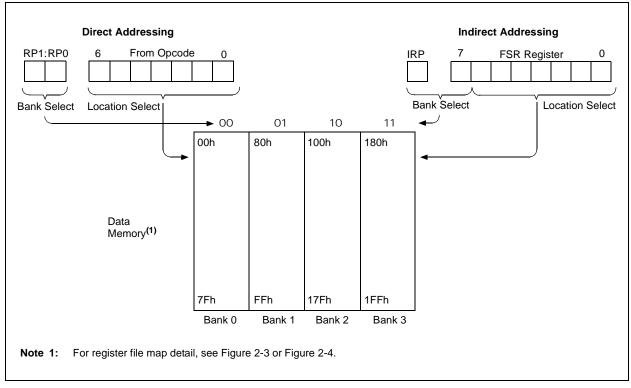

#### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

#### 6.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 6.4 Prescaler

There is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDTinstruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

| ER 6-1: | OPTION_                                                                                                      | REG: OPTI                       | ON REGI     | STER (AD     | DRESS 81h,           | 181h)      |               |                     |

|---------|--------------------------------------------------------------------------------------------------------------|---------------------------------|-------------|--------------|----------------------|------------|---------------|---------------------|

|         | R/W-1                                                                                                        | R/W-1                           | R/W-1       | R/W-1        | R/W-1                | R/W-1      | R/W-1         | R/W-1               |

|         | RBPU                                                                                                         | INTEDG                          | T0CS        | TOSE         | PSA                  | PS2        | PS1           | PS0                 |

|         | bit 7                                                                                                        |                                 |             |              |                      |            |               | bit 0               |

| bit 7   | RBPU: PC                                                                                                     | ORTB Pull-up                    | Enable bit  | t            |                      |            |               |                     |

|         |                                                                                                              | 「B pull-ups a<br>「B pull-ups a  |             |              | I port latch valu    | ues        |               |                     |

| bit 6   | INTEDG:                                                                                                      | Interrupt Edg                   | e Select bi | t            |                      |            |               |                     |

|         |                                                                                                              | upt on rising<br>upt on falling |             |              |                      |            |               |                     |

| bit 5   | <b>T0CS</b> : TM                                                                                             | R0 Clock So                     | urce Selec  | t bit        |                      |            |               |                     |

|         | 1 = Transi                                                                                                   | tion on TOCK                    | (I pin      |              |                      |            |               |                     |

|         | 0 = Interna                                                                                                  | al instruction                  | cycle clock | (CLKO)       |                      |            |               |                     |

| bit 4   | TOSE: TM                                                                                                     | R0 Source E                     | dge Select  | bit          |                      |            |               |                     |

|         | 1 = Increment on high-to-low transition on T0CKI pin<br>O = Increment on low-to-high transition on T0CKI pin |                                 |             |              |                      |            |               |                     |

| bit 3   | PSA: Pres                                                                                                    | scaler Assign                   | ment bit    |              |                      |            |               |                     |

|         | 1 = Prescaler is assigned to the WDT<br>O = Prescaler is assigned to the Timer0 module                       |                                 |             |              |                      |            |               |                     |

| bit 2-0 |                                                                                                              | Prescaler Ra                    |             |              |                      |            |               |                     |

|         | Bit Value<br>000                                                                                             | TMR0 Rate<br>1:2                | WDT Rat     | <u>te</u>    |                      |            |               |                     |

|         | 000                                                                                                          | 1:4                             | 1:2         |              |                      |            |               |                     |

|         | 010                                                                                                          | 1:8                             | 1:4         |              |                      |            |               |                     |

|         | 011<br>100                                                                                                   | 1 : 16<br>1 : 32                | 1:8<br>1:16 |              |                      |            |               |                     |

|         | 100                                                                                                          | 1:64                            | 1:32        |              |                      |            |               |                     |

|         | 110                                                                                                          | 1:128                           | 1:64        |              |                      |            |               |                     |

|         | 111                                                                                                          | 1 : 256                         | 1 : 128     |              |                      |            |               |                     |

|         | Legend:                                                                                                      |                                 |             |              |                      |            |               |                     |

|         | R = Reada                                                                                                    | able bit                        | W = V       | Nritable bit | U = Unimp            | lemented b | it, read as ' | 0'                  |

|         | -n = Value                                                                                                   | at POR                          | '1' = E     | Bit is set   | '0' = Bit is o       |            | x = Bit is u  |                     |

|         | Note:                                                                                                        | To avoid an                     | unintende   | d device Res | set, the instruct    | ion seauen | ce shown ir   | n the <i>"PIC</i> ® |

|         |                                                                                                              |                                 |             |              | e <i>Manual"</i> (DS |            |               |                     |

|         |                                                                                                              |                                 |             |              | t from Timer0        | to the WDT | . This sequ   | ence must           |

|         |                                                                                                              | be followed                     | even if the | WDT is disa  | abled.               |            |               |                     |

#### **REGISTER 6-1:** OPTION\_REG: OPTION REGISTER (ADDRESS 81h, 181h)

NOTES:

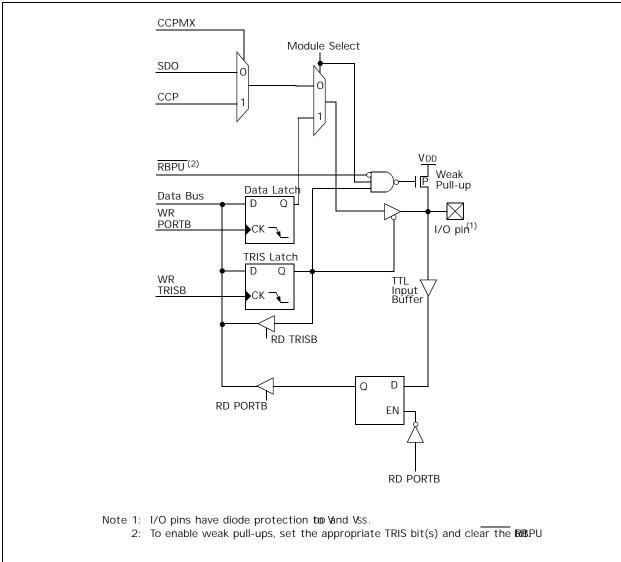

### 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                | U-0        | R/W-0           | R/W-0        | R/W-0        | R/W-0       | R/W-0           | R/W-0       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|--------------|--------------|-------------|-----------------|-------------|--|--|

| _                                                                                                                                                                  | _          | CCP1X           | CCP1Y        | CCP1M3       | CCP1M2      | CCP1M1          | CCP1M0      |  |  |

| bit 7                                                                                                                                                              |            |                 |              |              |             |                 | bit 0       |  |  |

|                                                                                                                                                                    |            |                 |              |              |             |                 |             |  |  |

| Jnimpleme                                                                                                                                                          | nted: Read | <b>d as</b> 'O' |              |              |             |                 |             |  |  |

| CCP1X:CCF                                                                                                                                                          | P1Y: PWM   | Least Signi     | ficant bits  |              |             |                 |             |  |  |

| <u>Capture moo</u><br>Jnused.                                                                                                                                      | <u>de:</u> |                 |              |              |             |                 |             |  |  |

| <u>Compare mo</u><br>Jnused.                                                                                                                                       | ode:       |                 |              |              |             |                 |             |  |  |

| <u>PWM mode:</u><br>These bits a                                                                                                                                   |            | LSbs of the     | PWM duty     | cycle. The e | ight MSbs a | re found in (   | CCPRxL.     |  |  |

| CCP1M3:CO                                                                                                                                                          | CP1M0: CC  | P1 Mode S       | elect bits   |              |             |                 |             |  |  |

| 0000 <b>= Ca</b> p                                                                                                                                                 | ture/Compa | are/PWM di      | sabled (res  | ets CCP1 m   | odule)      |                 |             |  |  |

| 0100 <b>= Cap</b>                                                                                                                                                  | ture mode, | every fallin    | g edge       |              |             |                 |             |  |  |

| 0101 = Cap                                                                                                                                                         |            |                 |              |              |             |                 |             |  |  |

| 0110 = Cap                                                                                                                                                         |            | •               | • •          |              |             |                 |             |  |  |

| 0111 = Cap<br>1000 = Cor                                                                                                                                           |            | •               | • •          |              | ic cot)     |                 |             |  |  |

| 1000= Compare mode, set output on match (CCP1IF bit is set)<br>1001 = Compare mode, clear output on match (CCP1IF bit is set)                                      |            |                 |              |              |             |                 |             |  |  |

| 1010 <b>= Cor</b>                                                                                                                                                  |            |                 |              | terrupt on m |             | F bit is set, ( | CCP1 pin is |  |  |

| 1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected)<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |            |                 |              |              |             |                 |             |  |  |

| 11xx = PWM mode                                                                                                                                                    |            |                 |              |              | ,           |                 |             |  |  |

| 11xx = PWI                                                                                                                                                         | vi mode    |                 |              |              |             |                 |             |  |  |

| 11xx = PW                                                                                                                                                          | w mode     |                 |              |              |             |                 |             |  |  |

| 11xx = PWI                                                                                                                                                         |            |                 |              |              |             |                 |             |  |  |

|                                                                                                                                                                    |            | W = V           | Vritable bit | U = Uni      | mplemented  | l bit, read as  | · '0'       |  |  |

| REGISTER 11-2: | ADCON1: A/D CONTROL REGISTER 1 (ADDRESS 9Fh) |

|----------------|----------------------------------------------|

|----------------|----------------------------------------------|

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | —   | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified, 6 Most Significant bits of ADRESH are read as '0' O = Left justified, 6 Least Significant bits of ADRESL are read as '0'

bit 6 ADCS2: A/D Clock Divide by 2 Select bit

1 = A/D clock source is divided by 2 when system clock is used O = Disabled

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG<3:0>: A/D Port Configuration Control bits

| PCFG | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|------|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000 | А   | Α     | А     | Α   | Α   | AVdd  | AVss  | 5/0 |

| 0001 | А   | VREF+ | А     | A   | А   | AN3   | AVss  | 4/1 |

| 0010 | А   | A     | А     | A   | А   | AVdd  | AVss  | 5/0 |

| 0011 | А   | VREF+ | А     | A   | А   | AN3   | AVss  | 4/1 |

| 0100 | D   | A     | D     | A   | А   | AVdd  | AVss  | 3/0 |

| 0101 | D   | VREF+ | D     | A   | А   | AN3   | AVss  | 2/1 |

| 011x | D   | D     | D     | D   | D   | AVdd  | AVss  | 0/0 |

| 1000 | А   | VREF+ | Vref- | A   | А   | AN3   | AN2   | 3/2 |

| 1001 | А   | A     | А     | A   | А   | AVdd  | AVss  | 5/0 |

| 1010 | А   | VREF+ | А     | Α   | А   | AN3   | AVss  | 4/1 |

| 1011 | А   | VREF+ | Vref- | A   | А   | AN3   | AN2   | 3/2 |

| 1100 | А   | VREF+ | Vref- | A   | А   | AN3   | AN2   | 3/2 |

| 1101 | D   | VREF+ | Vref- | A   | А   | AN3   | AN2   | 2/2 |

| 1110 | D   | D     | D     | D   | А   | AVdd  | AVss  | 1/0 |

| 1111 | D   | VREF+ | Vref- | D   | А   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = Number of analog input channels/Number of A/D voltage references

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDWF            | AND W with f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                         |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                     |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |  |  |  |  |  |

| BCF              | Bit Clear f                                                         |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |

| ANDLW            | AND Literal with W                                                                                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

#### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| DC CHARACTERISTICS |       | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \\ \mbox{Operating voltage VDD range as described in Section 15.1 "DC Characteristics: Supply Voltage".} \end{array}$ |             |             |     |            |                                                                        |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----|------------|------------------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                                                                                                                                                                                     | Min         | Тур†        | Max | Units      | Conditions                                                             |

|                    | Vol   | Output Low Voltage                                                                                                                                                                                                                                                                                                                                                 |             |             |     |            |                                                                        |

| D080               |       | I/O ports                                                                                                                                                                                                                                                                                                                                                          | —           | —           | 0.6 | V          | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D083               |       | OSC2/CLKO<br>(RC oscillator config)                                                                                                                                                                                                                                                                                                                                | —           | -           | 0.6 | V          | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

|                    | Vон   | Output High Voltage                                                                                                                                                                                                                                                                                                                                                |             |             |     |            |                                                                        |

| D090               |       | I/O ports <b>(Note 3)</b>                                                                                                                                                                                                                                                                                                                                          | Vdd - 0.7   | —           | —   | V          | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +125°C                          |

| D092               |       | OSC2/CLKO<br>(RC oscillator config)                                                                                                                                                                                                                                                                                                                                | Vdd - 0.7   | -           | —   | V          | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                          |

|                    |       | Capacitive Loading Specs on                                                                                                                                                                                                                                                                                                                                        | Output Pins |             |     |            |                                                                        |

| D100               | Cosc2 | OSC2 pin                                                                                                                                                                                                                                                                                                                                                           | _           | -           | 15  | pF         | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1 |

| D101               | Сю    | All I/O pins and OSC2<br>(in RC mode)                                                                                                                                                                                                                                                                                                                              | —           | -           | 50  | pF         |                                                                        |

| D102               | Св    | SCL, SDA in I <sup>2</sup> C™ mode                                                                                                                                                                                                                                                                                                                                 |             | —           | 400 | pF         |                                                                        |

|                    |       | Data EEPROM Memory                                                                                                                                                                                                                                                                                                                                                 | •           |             |     |            |                                                                        |

| D120               | ED    | Endurance                                                                                                                                                                                                                                                                                                                                                          | 100K        | 1M          | _   | E/W        | -40°C to +85°C                                                         |

|                    |       |                                                                                                                                                                                                                                                                                                                                                                    | 10K         | 100K        | _   | E/W        | +85°C to +125°C                                                        |

| D121               | Vdrw  | VDD for read/write                                                                                                                                                                                                                                                                                                                                                 | Vmin        | -           | 5.5 | V          | Using EECON to read/write,<br>VMIN = min. operating<br>voltage         |

| D122               | TDEW  | Erase/write cycle time                                                                                                                                                                                                                                                                                                                                             |             | 4           | 8   | ms         |                                                                        |

|                    |       | Program Flash Memory                                                                                                                                                                                                                                                                                                                                               |             |             |     |            |                                                                        |

| D130               | Eр    | Endurance                                                                                                                                                                                                                                                                                                                                                          | 10K<br>1K   | 100K<br>10K | _   | E/W<br>E/W | -40°C to +85°C<br>+85°C to +125°C                                      |

| D131               | Vpr   | VDD for read                                                                                                                                                                                                                                                                                                                                                       | VMIN        | _           | 5.5 | V          |                                                                        |

| D132A              |       | VDD for erase/write                                                                                                                                                                                                                                                                                                                                                | Vmin        | -           | 5.5 | V          | Using EECON to read/write,<br>VMIN = min. operating<br>voltage         |

| D133               | Тре   | Erase cycle time                                                                                                                                                                                                                                                                                                                                                   | —           | 2           | 4   | ms         |                                                                        |

| D134               | TPW   | Write cycle time                                                                                                                                                                                                                                                                                                                                                   | —           | 2           | 4   | ms         |                                                                        |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

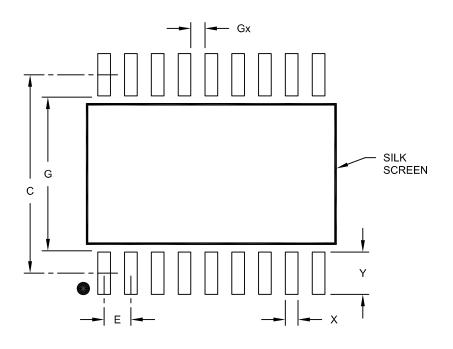

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                       | Units            | MILLIMETERS |      |      |  |  |

|-----------------------|------------------|-------------|------|------|--|--|

| Dimension             | Dimension Limits |             | NOM  | MAX  |  |  |

| Contact Pitch         | E                | 1.27 BSC    |      |      |  |  |

| Contact Pad Spacing   | С                |             | 9.40 |      |  |  |

| Contact Pad Width     | X                |             |      | 0.60 |  |  |

| Contact Pad Length    | Y                |             |      | 2.00 |  |  |

| Distance Between Pads | Gx               | 0.67        |      |      |  |  |

| Distance Between Pads | G                | 7.40        |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A