Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

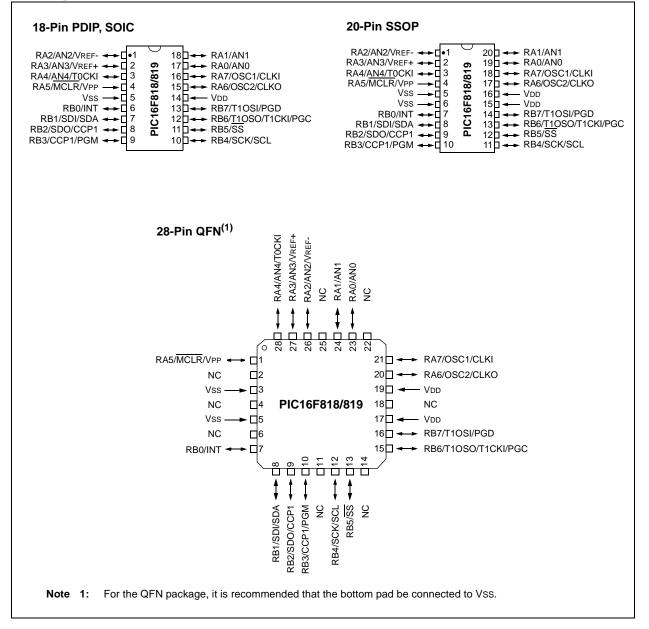

# **Pin Diagrams**

# 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0      | R/W-0                             | R/W-0           | R/W-0        | R/W-0         | R/W-0         | R/W-0        | R/W-x      |

|------------|-----------------------------------|-----------------|--------------|---------------|---------------|--------------|------------|

| GIE        | PEIE                              | TMR0IE          | INTE         | RBIE          | TMR0IF        | INTF         | RBIF       |

| bit 7      |                                   |                 |              |               |               |              | bit (      |

| GIE: Globa | al Interrupt Er                   | nable bit       |              |               |               |              |            |

|            | es all unmask<br>les all interrup |                 | ;            |               |               |              |            |

| PEIE: Peri | pheral Interru                    | ipt Enable bit  | :            |               |               |              |            |

|            | es all unmask<br>les all periphe  |                 |              |               |               |              |            |

| TMR0IE: T  | MR0 Overflo                       | w Interrupt E   | nable bit    |               |               |              |            |

|            | es the TMR0<br>les the TMR0       |                 |              |               |               |              |            |

| INTE: RB0  | /INT Externa                      | I Interrupt En  | able bit     |               |               |              |            |

|            | es the RB0/IN<br>les the RB0/II   |                 |              |               |               |              |            |

| RBIE: RB   | Port Change                       | Interrupt Ena   | able bit     |               |               |              |            |

|            | es the RB po<br>les the RB po     | •               | •            |               |               |              |            |

| TMR0IF: T  | MR0 Overflo                       | w Interrupt F   | lag bit      |               |               |              |            |

|            | register has<br>register did r    |                 | must be clea | ared in softv | vare)         |              |            |

| INTF: RB0  | /INT Externa                      | I Interrupt Fla | ng bit       |               |               |              |            |

|            | B0/INT exter<br>B0/INT exter      |                 | · ·          |               | ed in softwa  | ire)         |            |

| RBIF: RB   | Port Change                       | Interrupt Flag  | g bit        |               |               |              |            |

|            | h condition w<br>Ind allow flag   |                 | •            | RBIF. Read    | ing PORTB     | will end the | e mismatcl |

|            | st one of the of the RB7:R        | •               | •            | •             | be cleared in | n software)  |            |

| Legend:    |                                   |                 |              |               |               |              |            |

| R = Reada  | able bit                          | W = Wr          | ritable bit  | U = Unim      | plemented     | bit, read as | '0'        |

|            |                                   |                 |              |               |               |              |            |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

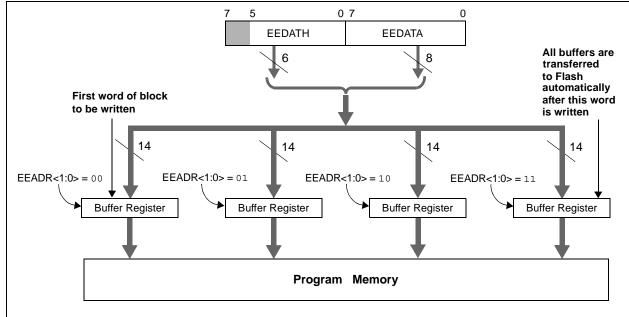

# 3.7 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device Configuration Word (Register 12-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR<1:0> = 00. At the same time, all block writes to program memory are done as write-only operations. The program memory must first be erased. The write operation is edge-aligned and cannot occur across boundaries.

To write to the program memory, the data must first be loaded into the buffer registers. There are four 14-bit buffer registers and they are addressed by the low 2 bits of EEADR.

The following sequence of events illustrate how to perform a write to program memory:

- Set the EEPGD and WREN bits in the EECON1 register

- Clear the FREE bit in EECON1

- Write address to EEADRH:EEADR

- Write data to EEDATH:EEDATA

- Write 55 to EECON2

- Write AA to EECON2

- Set WR bit in EECON 1

The user must follow the same specific sequence to initiate the write for each word in the program block by writing each program word in sequence (00, 01, 10, 11).

There are 4 buffer register words and all four locations **MUST** be written to with correct data.

After the "BSF EECON1, WR" instruction, if EEADR  $\neq$  xxxxx11, then a short write will occur. This short write-only transfers the data to the buffer register. The WR bit will be cleared in hardware after one cycle.

After the "BSF EECON1, WR" instruction, if EEADR = xxxxx11, then a long write will occur. This will simultaneously transfer the data from EEDATH:EEDATA to the buffer registers and begin the write of all four words. The processor will execute the next instruction and then ignore the subsequent instruction. The user should place NOP instructions into the second words. The processor will then halt internal operations for typically 2 msec in which the write takes place. This is not a Sleep mode, as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the 3rd instruction after the EECON1 write instruction.

After each long write, the 4 buffer registers will be reset to 3FFF.

#### FIGURE 3-1: BLOCK WRITES TO FLASH PROGRAM MEMORY

An example of the complete four-word write sequence is shown in Example 3-5. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing, assuming that a row erase sequence has already been performed.

#### EXAMPLE 3-5: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. The 32 words in the erase block have already been erased. ; 2. A valid starting address (the least significant bits = '00') is loaded into EEADRH:EEADR ; 3. This example is starting at 0x100, this is an application dependent setting. ; 4. The 8 bytes (4 words) of data are loaded, starting at an address in RAM called ARRAY. ; 5. This is an example only, location of data to program is application dependent. ; 6. word\_block is located in data memory. BANKSEL EECON1 ;prepare for WRITE procedure EECON1, EEPGD BSF ; point to program memory EECON1, WREN BSF ;allow write cycles BCF EECON1, FREE ;perform write only BANKSEL word block MOVLW .4 MOVWF word block ;prepare for 4 words to be written BANKSEL EEADRH ;Start writing at 0x100 MOVLW 0x01 MOVWF ;load HIGH address EEADRH MOVLW 0x00 MOVWF EEADR ;load LOW address BANKSEL ARRAY MOVLW ARRAY ; initialize FSR to start of data MOVWF FSR LOOP BANKSEL EEDATA MOVF INDF, W ; indirectly load EEDATA MOVWF EEDATA INCF FSR. F ; increment data pointer MOVF INDF, W ; indirectly load EEDATH MOVWF EEDATH INCE FSR, F ; increment data pointer BANKSEL EECON1 ;required sequence MOVLW 0x55 MOVWF EECON2 MOVIW 0xAA ner MOVWF EECON2 BSF EECON1, WR ;set WR bit to begin write NOP ; instructions here are ignored as processor NOP BANKSEL EEADR INCF EEADR, f ;load next word address BANKSEL word\_block DECFSZ word\_block, f ; have 4 words been written? GOTO loop ;NO, continue with writing BANKSEL EECON1 BCF EECON1, WREN ;YES, 4 words complete, disable writes BSF INTCON, GIE ;enable interrupts

# 3.8 Protection Against Spurious Write

There are conditions when the device should not write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents an EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

# 3.9 Operation During Code-Protect

When the data EEPROM is code-protected, the microcontroller can read and write to the EEPROM normally. However, all external access to the EEPROM is disabled. External write access to the program memory is also disabled.

When program memory is code-protected, the microcontroller can read and write to program memory normally as well as execute instructions. Writes by the device may be selectively inhibited to regions of the memory depending on the setting of bits, WRT1:WRT0, of the Configuration Word (see **Section 12.1 "Configuration Bits"** for additional information). External access to the memory is also disabled.

# TABLE 3-1:REGISTERS/BITS ASSOCIATED WITH DATA EEPROM AND<br/>FLASH PROGRAM MEMORIES

| Address | Name   | Bit 7                                               | Bit 6     | Bit 5       | Bit 4      | Bit 3  | Bit 2                 | Bit 1                   | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|--------|-----------------------------------------------------|-----------|-------------|------------|--------|-----------------------|-------------------------|-------|-------------------------------|---------------------------------|

| 10Ch    | EEDATA | EEPROM                                              | 1/Flash D | ata Registe | er Low By  | ⁄te    |                       |                         |       | xxxx xxxx                     | uuuu uuuu                       |

| 10Dh    | EEADR  | EEPRON                                              | 1/Flash A | ddress Reg  | gister Low | v Byte |                       |                         |       | xxxx xxxx                     | uuuu uuuu                       |

| 10Eh    | EEDATH | _                                                   | _         | EEPROM      | /Flash Da  |        | xx xxxx               | uu uuuu                 |       |                               |                                 |

| 10Fh    | EEADRH | _                                                   | _         |             | _          | —      | EEPROM/<br>Register H | Flash Addr<br>ligh Byte | ess   | xxx                           | uuu                             |

| 18Ch    | EECON1 | EEPGD                                               | _         | —           | FREE       | WRERR  | WREN                  | WR                      | RD    | xx x000                       | xx q000                         |

| 18Dh    | EECON2 | EEPROM Control Register 2 (not a physical register) |           |             |            |        |                       |                         |       |                               |                                 |

| 0Dh     | PIR2   | _                                                   | _         | _           | EEIF       | —      | —                     | _                       | _     | 0                             | 0                               |

| 8Dh     | PIE2   | _                                                   | _         | _           | EEIE       | _      | _                     | _                       | _     | 0                             | 0                               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM or Flash program memory.

# 4.0 OSCILLATOR CONFIGURATIONS

# 4.1 Oscillator Types

The PIC16F818/819 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

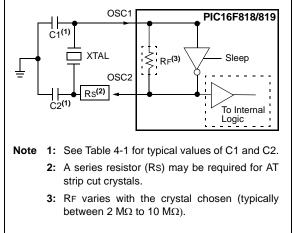

# 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F818/819 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

#### TABLE 4-1: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|---------|-------------------------------------|-------|--|--|--|

|          | Freq    | C1                                  | C2    |  |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

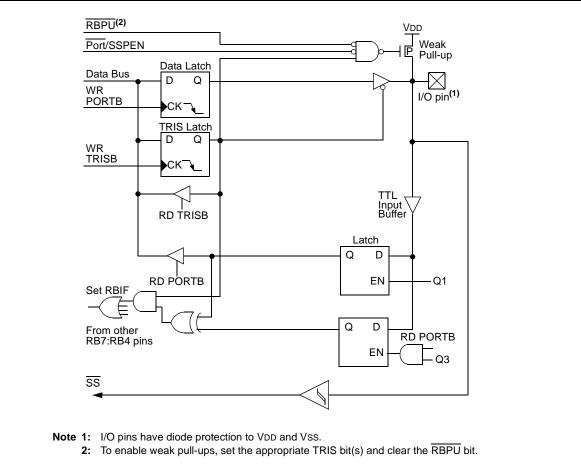

# FIGURE 5-13: BLOCK DIAGRAM OF RB5 PIN

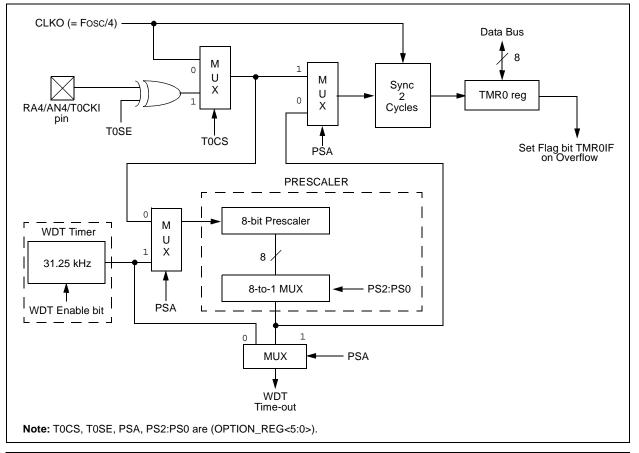

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt-on-overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

Figure 6-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

# 6.1 Timer0 Operation

Timer0 operation is controlled through the OPTION\_REG register (see Register 2-2). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/AN4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.3 "Using Timer0 with an External Clock".

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. **Section 6.4** "**Prescaler**" details the operation of the prescaler.

# 6.2 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit, TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit, TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut-off during Sleep.

### FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

© 2001-2013 Microchip Technology Inc.

# 7.5 Timer1 Operation in Asynchronous Counter Mode

If control bit,  $\overline{\text{T1SYNC}}$  (T1CON<2>), is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow that will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 7.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example codes provided in Example 7-1 and Example 7-2 demonstrate how to write to and read Timer1 while it is running in Asynchronous mode.

| EXAMPLE 7-1:   | WRITING A 16-BIT FREE RUNNING TIMER |

|----------------|-------------------------------------|

| EAAIVIFLE /-I. | WRITING A 10-DIT FREE RUNNING TIMER |

| ; All  | interrupts are | e disabled                                       |  |

|--------|----------------|--------------------------------------------------|--|

| CLRF   | TMR1L          | ; Clear Low byte, Ensures no rollover into TMR1H |  |

| MOVLW  | HI_BYTE        | ; Value to load into TMR1H                       |  |

| MOVWF  | TMR1H, F       | ; Write High byte                                |  |

| MOVLW  | LO_BYTE        | ; Value to load into TMR1L                       |  |

| MOVWF  | TMR1H, F       | ; Write Low byte                                 |  |

| ; Re-e | nable the Inte | errupt (if required)                             |  |

| CONTIN | IUE            | ; Continue with your code                        |  |

|        |                |                                                  |  |

#### EXAMPLE 7-2: READING A 16-BIT FREE RUNNING TIMER

| ; All interrupts are disabled                                            |

|--------------------------------------------------------------------------|

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL                                                               |

| MOVF TMR1H, W ; Read high byte                                           |

| SUBWF TMPH, W ; Sub 1st read with 2nd read                               |

| BTFSC STATUS, Z ; Is result = 0                                          |

| GOTO CONTINUE ; Good 16-bit read                                         |

| ; TMR1L may have rolled over between the read of the high and low bytes. |

| ; Reading the high and low bytes now will read a good value.             |

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL ; Re-enable the Interrupt (if required)                       |

| CONTINUE ; Continue with your code                                       |

|                                                                          |

# 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

## **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                 | U-0        | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-0          | R/W-0       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|---------------|--------------|----------------|-------------|--|--|

| —                                                                                                                                                                   | —          | CCP1X        | CCP1Y        | CCP1M3        | CCP1M2       | CCP1M1         | CCP1M0      |  |  |

| bit 7                                                                                                                                                               |            |              |              |               |              |                | bit 0       |  |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |  |

| Unimpleme                                                                                                                                                           |            |              |              |               |              |                |             |  |  |

| CCP1X:CCP1Y: PWM Least Significant bits                                                                                                                             |            |              |              |               |              |                |             |  |  |

| <u>Capture mo</u><br>Unused.                                                                                                                                        | <u>de:</u> |              |              |               |              |                |             |  |  |

| <u>Compare mo</u><br>Unused.                                                                                                                                        | ode:       |              |              |               |              |                |             |  |  |

| <u>PWM mode:</u><br>These bits a                                                                                                                                    | -          | LSbs of the  | PWM duty     | cycle. The e  | eight MSbs a | re found in (  | CCPRxL.     |  |  |

| CCP1M3:CO                                                                                                                                                           | CP1M0: CC  | P1 Mode S    | elect bits   |               |              |                |             |  |  |

| 0000 <b>= Cap</b>                                                                                                                                                   | ture/Compa | are/PWM di   | sabled (res  | ets CCP1 m    | odule)       |                |             |  |  |

| 0100 = Cap                                                                                                                                                          | ture mode, | every fallin | g edge       |               |              |                |             |  |  |

| 0101 <b>= Cap</b>                                                                                                                                                   |            |              |              |               |              |                |             |  |  |

| 0110 = Cap                                                                                                                                                          |            | •            | •••          |               |              |                |             |  |  |

| 0111 = Cap                                                                                                                                                          |            | •            | • •          | (CCP1IF bit   | ic cot)      |                |             |  |  |

|                                                                                                                                                                     |            | · ·          |              | h (CCP1IF b   | ,            |                |             |  |  |

| 1010 <b>= Com</b>                                                                                                                                                   |            |              |              | terrupt on ma |              | F bit is set,  | CCP1 pin is |  |  |

| 1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |            |              |              |               |              |                |             |  |  |

| 11xx = PWI                                                                                                                                                          |            |              |              |               | ,            |                | ,           |  |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |  |

|                                                                                                                                                                     |            |              |              |               |              |                |             |  |  |

| Legend:                                                                                                                                                             |            |              |              |               |              |                |             |  |  |

| <b>Legend:</b><br>R = Readab                                                                                                                                        | le bit     | W = V        | Vritable bit | U = Uni       | mplemented   | l bit, read as | s 'O'       |  |  |

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

### **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

- Note: The TRISB bit (2 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

# TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                                | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value o<br>POR, B |     | all o | e on<br>other<br>sets |

|----------------------|---------|--------|--------------------------------------|--------------|---------|---------|--------|---------|---------|-------------------|-----|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                 | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 00           | 20x | 0000  | 000u                  |

| 0Ch                  | PIR1    | _      | ADIF                                 | _            | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0 00             | 000 | - 0   | 0000                  |

| 8Ch                  | PIE1    | _      | ADIE                                 | _            | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 00             | 000 | - 0   | 0000                  |

| 86h                  | TRISB   | PORT   | B Data Dire                          | ection Regis | ter     |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 11h                  | TMR2    | Timer2 | 2 Module Re                          | gister       |         |         |        |         |         | 0000 00           | 000 | 0000  | 0000                  |

| 92h                  | PR2     | Timer2 | 2 Module Pe                          | riod Registe | er      |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 12h                  | T2CON   | _      | TOUTPS3                              | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 00           | 000 | -000  | 0000                  |

| 15h                  | CCPR1L  | Captu  | Capture/Compare/PWM Register 1 (LSB) |              |         |         |        |         |         |                   | xx  | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Captur | Capture/Compare/PWM Register 1 (MSB) |              |         |         |        |         |         | XXXX XX           | cxx | uuuu  | uuuu                  |

| 17h                  | CCP1CON |        | _                                    | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 00             | 000 | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

#### **FIGURE 12-9:** WAKE-UP FROM SLEEP THROUGH INTERRUPT

| OSC1 /<br>CLKO <sup>(4)</sup> //    | 3   Q4 ; Q1   Q2   Q3   Q4 ; Q1<br>///////// |                    |              | . Q1  Q2  Q3  Q4<br>          | Q1  Q2  Q3  Q4<br>    | Q1 Q2 Q3 Q4; |

|-------------------------------------|----------------------------------------------|--------------------|--------------|-------------------------------|-----------------------|--------------|

| INT pin                             | <u> </u>                                     |                    | I            | 1                             | 1                     |              |

| INTF Flag<br>(INTCON<1>)            |                                              | \ <u>+</u>         |              | Interrupt Latency<br>(Note 2) |                       |              |

| GIE bit<br>(INTCON<7>)              | i i i i i i i i i i i i i i i i i i i        | cessor in<br>Sleep |              |                               | ,<br>,<br>,<br>,<br>, |              |

| INSTRUCTION FLOW                    |                                              | 1                  | l<br>I       | I I                           | 1                     | 1            |

| PC Y PC                             | X PC + 1 X                                   | PC + 2             | X PC + 2     | X PC + 2                      | 0004h                 | X 0005h      |

| Fetched Inst(PC) = S                | Sleep Inst(PC + 1)                           |                    | Inst(PC + 2) | 1<br>1<br>1                   | Inst(0004h)           | Inst(0005h)  |

| Instruction<br>Executed { Inst(PC - | - 1) Sleep                                   |                    | Inst(PC + 1) | Dummy Cycle                   | Dummy Cycle           | Inst(0004h)  |

| Note 1 XT HS or IP                  | Oscillator mode assumed                      |                    |              |                               |                       |              |

2: TOST = 1024 TOSC (drawing not to scale). This delay will not be there for RC Oscillator mode.

GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line. 3:

4: CLKO is not available in these oscillator modes but shown here for timing reference.

## 12.14 In-Circuit Debugger

When the DEBUG bit in the Configuration Word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-6 shows which features are consumed by the background debugger.

| TABLE 12-6: DEB | JGGER RESOURCES |

|-----------------|-----------------|

|-----------------|-----------------|

| I/O pins       | RB6, RB7                                   |

|----------------|--------------------------------------------|

| Stack          | 1 level                                    |

| Program Memory | Address 0000h must be NOP                  |

|                | Last 100h words                            |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB-0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

# 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the four Least Significant bits of the ID location are used.

| COMF             | Complement f                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                              |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                              |

| Status Affected: | Z                                                                                                                                            |

| Description:     | The contents of register 'f' are complemented. If 'd' = 0, the result is stored in W. If 'd' = 1, the result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                         |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                            |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits<10:0>. The<br>upper bits of PC are loaded<br>from PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| DECF             | Decrement f                                                                                                                                 | INCF             | Increment f                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                   | Syntax:          | [label] INCF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                 | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                      |

| Operation:       | (f) $-1 \rightarrow$ (destination)                                                                                                          | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                  |

| Status Affected: | Z                                                                                                                                           | Status Affected: | Z                                                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' = 0,<br>the result is stored in the W<br>register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                           | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                               | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                       | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             |

| Operation:       | (f) – 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                       | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result is<br>placed in the W register. If 'd' = 1,<br>the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2 TCY<br>instruction. |

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF<br>(Indu                        |                                       | rd Oper | •       |       | s otherwise stated<br>≤ +85°C for indus |                                                              |                                                |  |

|-----------------------------------------|---------------------------------------|---------|---------|-------|-----------------------------------------|--------------------------------------------------------------|------------------------------------------------|--|

| PIC16F818/819<br>(Industrial, Extended) |                                       |         | rd Oper | •     | -40°C ≤ TA                              | s otherwise stated<br>≤ +85°C for indus<br>≤ +125°C for exte | trial                                          |  |

| Param<br>No.                            | Device                                | Тур     | Max     | Units | Conditions                              |                                                              |                                                |  |

|                                         | Supply Current (IDD) <sup>(2,3)</sup> |         |         |       |                                         |                                                              |                                                |  |

|                                         | PIC16LF818/819                        | 72      | 95      | μΑ    | -40°C                                   |                                                              |                                                |  |

|                                         |                                       | 76      | 90      | μΑ    | +25°C                                   | VDD = 2.0V                                                   |                                                |  |

|                                         |                                       | 76      | 90      | μΑ    | +85°C                                   |                                                              |                                                |  |

|                                         | PIC16LF818/819                        | 138     | 175     | μΑ    | -40°C                                   |                                                              | Fosc = 1 MHz<br>(RC Oscillator) <sup>(3)</sup> |  |

|                                         |                                       | 136     | 170     | μΑ    | +25°C                                   | VDD = 3.0V                                                   |                                                |  |

|                                         |                                       | 136     | 170     | μΑ    | +85°C                                   |                                                              |                                                |  |

|                                         | All devices                           | 310     | 380     | μΑ    | -40°C                                   |                                                              |                                                |  |

|                                         |                                       | 290     | 360     | μΑ    | +25°C                                   | VDD = 5.0V                                                   |                                                |  |

|                                         |                                       | 280     | 360     | μΑ    | +85°C                                   | VDD = 3.0V                                                   |                                                |  |

|                                         | Extended devices                      | 350     | 500     | μΑ    | +125°C                                  |                                                              |                                                |  |

|                                         | PIC16LF818/819                        | 270     | 315     | μA    | -40°C                                   |                                                              |                                                |  |

|                                         |                                       | 280     | 310     | μA    | +25°C                                   | VDD = 2.0V                                                   |                                                |  |

|                                         |                                       | 285     | 310     | μΑ    | +85°C                                   |                                                              |                                                |  |

|                                         | PIC16LF818/819                        | 460     | 610     | μΑ    | -40°C                                   |                                                              |                                                |  |

|                                         |                                       | 450     | 600     | μΑ    | +25°C                                   | VDD = 3.0V                                                   | FOSC = 4 MHz                                   |  |

|                                         |                                       | 450     | 600     | μΑ    | +85°C                                   |                                                              | (RC Oscillator) <sup>(3)</sup>                 |  |

|                                         | All devices                           | 900     | 1060    | μΑ    | -40°C                                   |                                                              |                                                |  |

|                                         |                                       | 890     | 1050    | μΑ    | +25°C                                   | VDD = 5.0V                                                   |                                                |  |

|                                         |                                       | 890     | 1050    | μΑ    | +85°C                                   |                                                              |                                                |  |

|                                         | Extended devices                      | .920    | 1.5     | mA    | +125°C                                  |                                                              |                                                |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| DC CHARACTERISTICS |       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extendedOperating voltage VDD range as described in Section 15.1 "DCCharacteristics: Supply Voltage". |                               |             |     |            |                                                                        |  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|-----|------------|------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                                                                                                       | Min Typ† Max Units Conditions |             |     |            |                                                                        |  |

|                    | Vol   | Output Low Voltage                                                                                                                                                                                                                                                                   |                               |             |     |            |                                                                        |  |

| D080               |       | I/O ports                                                                                                                                                                                                                                                                            | —                             | —           | 0.6 | V          | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |

| D083               |       | OSC2/CLKO<br>(RC oscillator config)                                                                                                                                                                                                                                                  | —                             | —           | 0.6 | V          | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |

|                    | Vон   | Output High Voltage                                                                                                                                                                                                                                                                  |                               |             |     |            |                                                                        |  |

| D090               |       | I/O ports <b>(Note 3)</b>                                                                                                                                                                                                                                                            | Vdd - 0.7                     | —           | —   | V          | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +125°C                          |  |

| D092               |       | OSC2/CLKO<br>(RC oscillator config)                                                                                                                                                                                                                                                  | Vdd - 0.7                     | —           | —   | V          | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                          |  |

|                    |       | Capacitive Loading Specs on                                                                                                                                                                                                                                                          | Output Pins                   |             |     |            |                                                                        |  |

| D100               | Cosc2 | OSC2 pin                                                                                                                                                                                                                                                                             | _                             | —           | 15  | pF         | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1 |  |

| D101               | Сю    | All I/O pins and OSC2<br>(in RC mode)                                                                                                                                                                                                                                                | —                             | —           | 50  | pF         |                                                                        |  |

| D102               | Св    | SCL, SDA in I <sup>2</sup> C™ mode                                                                                                                                                                                                                                                   |                               | —           | 400 | pF         |                                                                        |  |

|                    |       | Data EEPROM Memory                                                                                                                                                                                                                                                                   |                               |             |     |            |                                                                        |  |

| D120               | ED    | Endurance                                                                                                                                                                                                                                                                            | 100K                          | 1M          | _   | E/W        | -40°C to +85°C                                                         |  |

|                    |       |                                                                                                                                                                                                                                                                                      | 10K                           | 100K        | _   | E/W        | +85°C to +125°C                                                        |  |

| D121               | Vdrw  | VDD for read/write                                                                                                                                                                                                                                                                   | Vmin                          | _           | 5.5 | V          | Using EECON to read/write,<br>VMIN = min. operating<br>voltage         |  |

| D122               | TDEW  | Erase/write cycle time                                                                                                                                                                                                                                                               |                               | 4           | 8   | ms         |                                                                        |  |

|                    |       | Program Flash Memory                                                                                                                                                                                                                                                                 | 1                             |             |     |            |                                                                        |  |

| D130               | Eр    | Endurance                                                                                                                                                                                                                                                                            | 10K<br>1K                     | 100K<br>10K | _   | E/W<br>E/W | -40°C to +85°C<br>+85°C to +125°C                                      |  |

| D131               | Vpr   | VDD for read                                                                                                                                                                                                                                                                         | VMIN                          | _           | 5.5 | V          |                                                                        |  |

| D132A              |       | VDD for erase/write                                                                                                                                                                                                                                                                  | Vmin                          | -           | 5.5 | V          | Using EECON to read/write,<br>VMIN = min. operating<br>voltage         |  |

| D133               | Тре   | Erase cycle time                                                                                                                                                                                                                                                                     | —                             | 2           | 4   | ms         |                                                                        |  |

| D134               | TPW   | Write cycle time                                                                                                                                                                                                                                                                     | —                             | 2           | 4   | ms         |                                                                        |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# TABLE 15-9:A/D CONVERTER CHARACTERISTICS: PIC16F818/819 (INDUSTRIAL, EXTENDED)PIC16LF818/819 (INDUSTRIAL)

| Param<br>No. | Sym   | Charac                             | teristic                | Min         | Тур†                      | Max          | Units | Conditions                                                                                                                                    |  |

|--------------|-------|------------------------------------|-------------------------|-------------|---------------------------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| A01          | Nr    | Resolution                         |                         | _           | —                         | 10-bits      | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |  |

| A03          | Eı∟   | Integral Linearity                 | Error                   | _           | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |  |

| A04          | Edl   | Differential Linear                | ity Error               |             | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |  |

| A06          | EOFF  | Offset Error                       |                         | —           | —                         | <±2          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |  |

| A07          | Egn   | Gain Error                         |                         | _           | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |  |

| A10          | _     | Monotonicity                       |                         | _           | guaranteed <sup>(3)</sup> | —            | —     | $VSS \leq VAIN \leq VREF$                                                                                                                     |  |

| A20          | Vref  | Reference Voltage (VREF+ - VREF-)  |                         | 2.0         | —                         | Vdd + 0.3    | V     |                                                                                                                                               |  |

| A21          | Vref+ | Reference Voltag                   | e High                  | AVdd - 2.5V |                           | AVDD + 0.3V  | V     |                                                                                                                                               |  |

| A22          | Vref- | Reference Voltag                   | e Low                   | AVss-0.3V   |                           | VREF+ - 2.0V | V     |                                                                                                                                               |  |

| A25          | VAIN  | Analog Input Volta                 | age                     | Vss - 0.3V  | —                         | VREF + 0.3V  | V     |                                                                                                                                               |  |

| A30          | ZAIN  | Recommended Ir<br>Analog Voltage S |                         | _           | —                         | 2.5          | kΩ    | (Note 4)                                                                                                                                      |  |

| A40          | IAD   | A/D Conversion                     | PIC16 <b>F</b> 818/819  | _           | 220                       | —            | μΑ    | Average current                                                                                                                               |  |

|              |       | Current (VDD)                      | PIC16 <b>LF</b> 818/819 |             | 90                        | —            | μA    | consumption when A/D is on (Note 1)                                                                                                           |  |

| A50          | IREF  | VREF Input Current (Note 2)        |                         | _           |                           | 5            | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD,<br>see Section 11.1 "A/D<br>Acquisition Requirements". |  |

|              |       |                                    |                         |             |                           | 150          | μΑ    | During A/D conversion cycle                                                                                                                   |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

- 3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 4: Maximum allowed impedance for analog voltage source is 10 kΩ. This requires higher acquisition time.

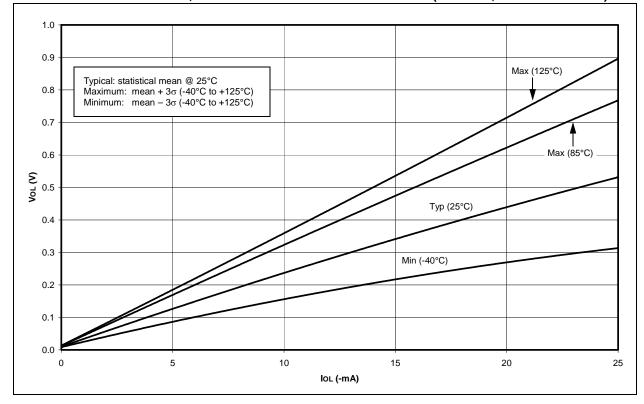

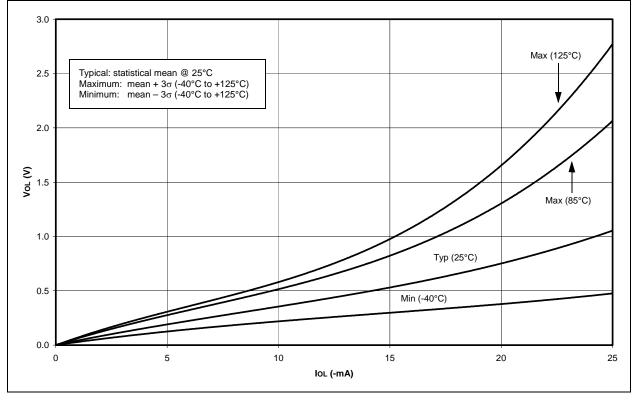

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

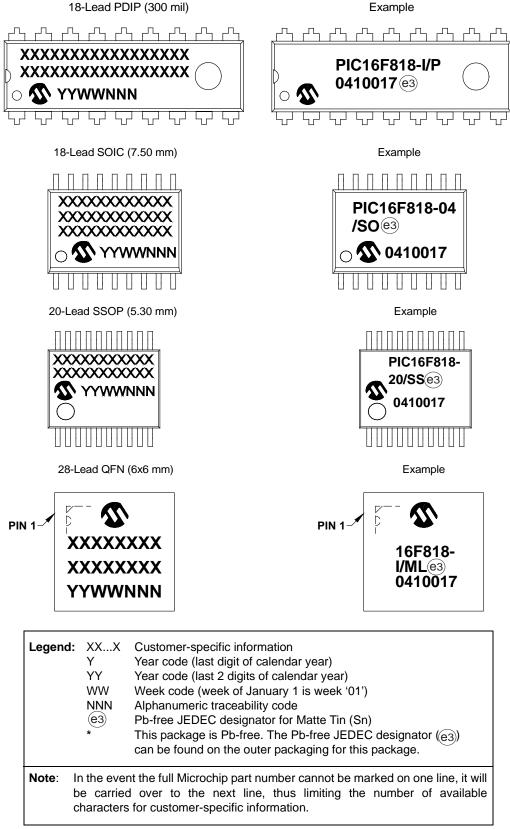

#### 17.0 **PACKAGING INFORMATION**

#### 17.1 **Package Marking Information**

18-Lead PDIP (300 mil)

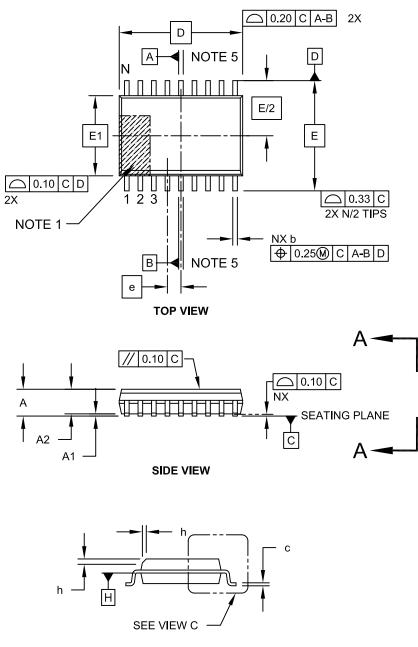

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-051C Sheet 1 of 2

| TMR0IE Bit 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Oscillator Block                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INTRC Modes35                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |