Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F818/819

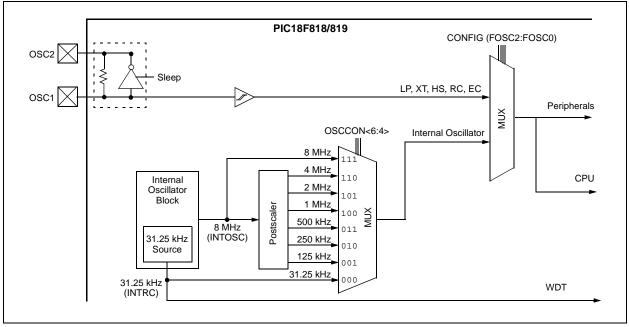

#### FIGURE 4-6: PIC16F818/819 CLOCK DIAGRAM

#### **REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)**

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | R-0  | U-0 | U-0   |

|-------|-------|-------|-------|-----|------|-----|-------|

| —     | IRCF2 | IRCF1 | IRCF0 | —   | IOFS | _   | _     |

| bit 7 |       |       |       |     |      |     | bit 0 |

#### bit 7 Unimplemented: Read as '0'

| bit 6-4 | IRCF2:IRCF0: Internal Oscillator Frequency Select bits |

|---------|--------------------------------------------------------|

|         | 111 = 8 MHz (8 MHz source drives clock directly)       |

|         | 110 <b>= 4 MHz</b>                                     |

|         | 101 = 2  MHz                                           |

|         | 100 = 1 MHz                                            |

|         | 011 = 500 kHz                                          |

|         | 010 = 250 kHz                                          |

|         | 001 = 125  kHz                                         |

|         | 000 = 31.25 kHz (INTRC source drives clock directly)   |

| bit 3   | Unimplemented: Read as '0'                             |

| bit 2   | IOFS: INTOSC Frequency Stable bit                      |

|         | 1 = Frequency is stable                                |

|         | 0 = Frequency is not stable                            |

| bit 1-0 | Unimplemented: Read as '0'                             |

|         | Legend:                                                |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

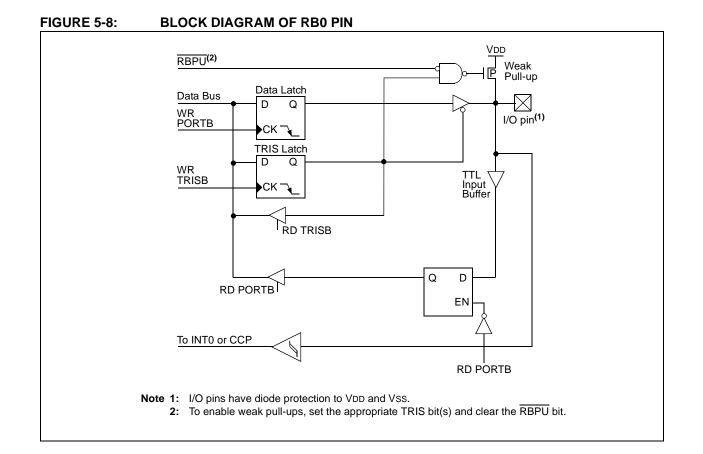

#### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### 7.5 Timer1 Operation in Asynchronous Counter Mode

If control bit,  $\overline{\text{T1SYNC}}$  (T1CON<2>), is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow that will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 7.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example codes provided in Example 7-1 and Example 7-2 demonstrate how to write to and read Timer1 while it is running in Asynchronous mode.

| EXAMPLE 7-1:   | WRITING A 16-BIT FREE RUNNING TIMER |

|----------------|-------------------------------------|

| EAAIVIFLE /-I. | WRITING A 10-DIT FREE RUNNING TIMER |

| ; All  | interrupts are | e disabled                                       |  |

|--------|----------------|--------------------------------------------------|--|

| CLRF   | TMR1L          | ; Clear Low byte, Ensures no rollover into TMR1H |  |

| MOVLW  | HI_BYTE        | ; Value to load into TMR1H                       |  |

| MOVWF  | TMR1H, F       | ; Write High byte                                |  |

| MOVLW  | LO_BYTE        | ; Value to load into TMR1L                       |  |

| MOVWF  | TMR1H, F       | ; Write Low byte                                 |  |

| ; Re-e | nable the Inte | errupt (if required)                             |  |

| CONTIN | IUE            | ; Continue with your code                        |  |

|        |                |                                                  |  |

#### EXAMPLE 7-2: READING A 16-BIT FREE RUNNING TIMER

| ; All interrupts are disabled                                            |

|--------------------------------------------------------------------------|

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL                                                               |

| MOVF TMR1H, W ; Read high byte                                           |

| SUBWF TMPH, W ; Sub 1st read with 2nd read                               |

| BTFSC STATUS, Z ; Is result = 0                                          |

| GOTO CONTINUE ; Good 16-bit read                                         |

| ; TMR1L may have rolled over between the read of the high and low bytes. |

| ; Reading the high and low bytes now will read a good value.             |

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL ; Re-enable the Interrupt (if required)                       |

| CONTINUE ; Continue with your code                                       |

|                                                                          |

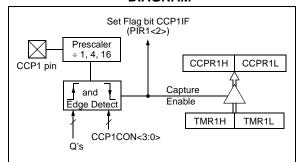

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW CAPT PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

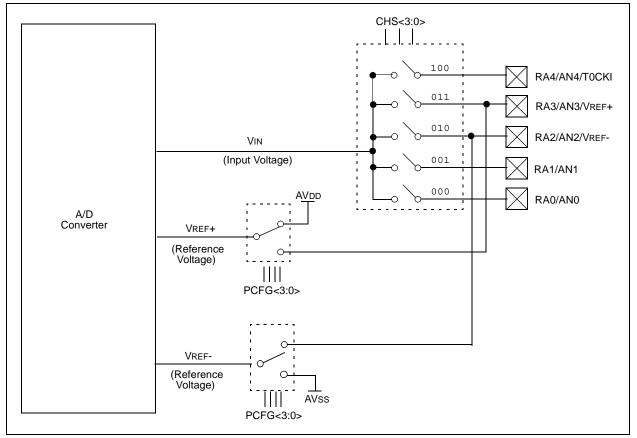

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1** "**A/D Acquisition Requirements**". After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

**FIGURE 11-1:**

#### A/D BLOCK DIAGRAM

© 2001-2013 Microchip Technology Inc.

#### 12.9 Power Control/Status Register (PCON)

The Power Control/Status register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if

# bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 12-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator           | Power-u             | p                      | Brown-out R         | Wake-up                |                               |

|----------------------|---------------------|------------------------|---------------------|------------------------|-------------------------------|

| Configuration        | PWRTE = 0           | PWRTE = 1              | PWRTE = 0           | PWRTE = 1              | from Sleep                    |

| XT, HS, LP           | TPWRT + 1024 • TOSC | 1024 • Tosc            | TPWRT + 1024 • Tosc | 1024 • Tosc            | 1024 • Tosc                   |

| EXTRC, EXTCLK, INTRC | Tpwrt               | 5-10 μs <sup>(1)</sup> | TPWRT               | 5-10 μs <sup>(1)</sup> | 5-10 μs <b><sup>(1)</sup></b> |

**Note 1:** CPU start-up is always invoked on POR, BOR and wake-up from Sleep.

#### TABLE 12-2: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

**Legend:** u = unchanged, x = unknown

#### TABLE 12-3: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of Global Interrupt Enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 12.13 "Power-Down Mode** (**Sleep**)" for details on Sleep mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>) (see **Section 6.0 "Timer0 Module"**).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). See Section 3.2 "EECON1 and EECON2 Registers".

#### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, Status registers). This will have to be implemented in software as shown in Example 12-1.

For PIC16F818 devices, the upper 64 bytes of each bank are common. Temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed here. These 64 locations do not require banking and therefore, make it easier for context save and restore.

For PIC16F819 devices, the upper 16 bytes of each bank are common.

EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

|        | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS, W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| :      |                |                                                         |

| :(ISR) |                | ;Insert user code here                                  |

| :      |                |                                                         |

| SWAPF  | STATUS_TEMP, W | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP, F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP, W      | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

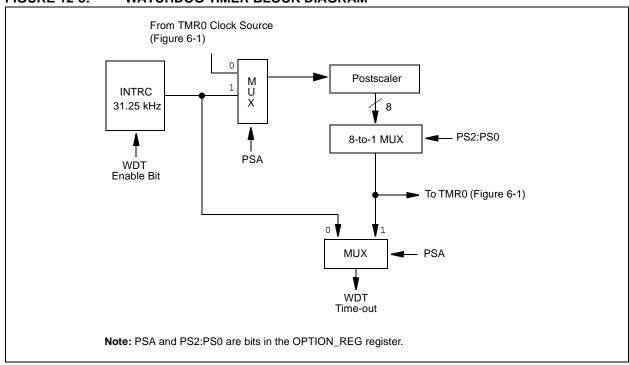

#### 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits**"). WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

#### FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | TOSE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

| COMF             | Complement f                                                                                                                                          |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                           |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                     |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' = 0, the<br>result is stored in W. If 'd' = 1, the<br>result is stored back in register 'f'. |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                            |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                            |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits<10:0>. The<br>upper bits of PC are loaded<br>from PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |

| DECF                                                                                                                                                           | Decrement f                        | INCF             | Increment f [ label ] INCF f,d                                                                                                                                       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                                                                                                                        | [ label ] DECF f,d                 | Syntax:          |                                                                                                                                                                      |  |  |

| Operands:                                                                                                                                                      | $0 \le f \le 127$<br>$d \in [0,1]$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                      |  |  |

| Operation: $(f) - 1 \rightarrow (destination)$                                                                                                                 |                                    | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                  |  |  |

| Status Affected:                                                                                                                                               | Z                                  | Status Affected: | Z                                                                                                                                                                    |  |  |

| Description: Decrement register 'f'. If 'd' = $0$ ,<br>the result is stored in the W<br>register. If 'd' = $1$ , the result is<br>stored back in register 'f'. |                                    | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                           | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                               | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                       | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             |

| Operation:       | (f) – 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                       | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result is<br>placed in the W register. If 'd' = 1,<br>the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2 TCY<br>instruction. |

| RETFIE                   | Return from Interrupt  | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|--------------------------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax: [ label ] RETFIE |                        | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:                | None                   | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:               | $TOS \rightarrow PC$ , |                  | d ∈ [0,1]                                                                                                                                                                                                      |

|                          | $1 \rightarrow GIE$    | Operation:       | See description below                                                                                                                                                                                          |

| Status Affected:         | None                   | Status Affected: | С                                                                                                                                                                                                              |

|                          |                        | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| RETLW                   | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [label] RRF f,d                                                                                                                                                                                                 |

| Operands:<br>Operation: | $0 \le k \le 255$<br>k $\rightarrow$ (W);                                                                                                                                           | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                 |

| oporation               | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                           |

| Status Affected:        | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                               |

| Description:            | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |

| <b>─→</b> C <b>→</b> | Register f |  |

|----------------------|------------|--|

|                      |            |  |

| RETURN           | Return from Subroutine                                                                                     | SLEEP            | Enter Sleep mode                                                                                                                                                                                           |  |  |

|------------------|------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETURN                                                                                             | Syntax:          | [label] SLEEP                                                                                                                                                                                              |  |  |

| Operands:        | None                                                                                                       | Operands:        | None                                                                                                                                                                                                       |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                       | Operation:       | $00h \rightarrow WDT$ ,                                                                                                                                                                                    |  |  |

| Status Affected: | Status Affected: None                                                                                      |                  | $0 \rightarrow WDT$ prescaler,<br>1 $\rightarrow \overline{TO}$ ,                                                                                                                                          |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program |                  | $0 \rightarrow PD$                                                                                                                                                                                         |  |  |

|                  |                                                                                                            | Status Affected: | TO, PD                                                                                                                                                                                                     |  |  |

|                  | counter. This is a two-cycle instruction.                                                                  | Description:     | The Power-Down status bit, PD,<br>is cleared. Time-out status bit,<br>TO, is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |

#### 14.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 14.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 14.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| DC CHA       | ARACTI | ERISTICS                     | Operating temp  | erature<br>ge VDD | e -40°(<br>-40°(<br>o range as | C ≤ TA<br>C ≤ TA<br>descri | ess otherwise stated)<br>≤ +85°C for industrial<br>≤ +125°C for extended<br>bed in Section 15.1 "DC |

|--------------|--------|------------------------------|-----------------|-------------------|--------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic               | Min             | Тур†              | Max                            | Units                      | Conditions                                                                                          |

|              | VIL    | Input Low Voltage            | •               |                   |                                |                            |                                                                                                     |

|              |        | I/O ports:                   |                 |                   |                                |                            |                                                                                                     |

| D030         |        | with TTL buffer              | Vss             | _                 | 0.15 Vdd                       | V                          | For entire VDD range                                                                                |

| D030A        |        |                              | Vss             | _                 | 0.8V                           | V                          | $4.5V \le V\text{DD} \le 5.5V$                                                                      |

| D031         |        | with Schmitt Trigger buffer  | Vss             | _                 | 0.2 Vdd                        | V                          |                                                                                                     |

| D032         |        | MCLR, OSC1 (in RC mode)      | Vss             | _                 | 0.2 Vdd                        | V                          | (Note 1)                                                                                            |

| D033         |        | OSC1 (in XT and LP mode)     | Vss             | _                 | 0.3V                           | V                          |                                                                                                     |

|              |        | OSC1 (in HS mode)            | Vss             | _                 | 0.3 Vdd                        | V                          |                                                                                                     |

|              |        | Ports RB1 and RB4:           |                 |                   |                                |                            |                                                                                                     |

| D034         |        | with Schmitt Trigger buffer  | Vss             | _                 | 0.3 Vdd                        | V                          | For entire VDD range                                                                                |

|              | Viн    | Input High Voltage           |                 |                   |                                |                            |                                                                                                     |

|              |        | I/O ports:                   |                 |                   |                                |                            |                                                                                                     |

| D040         |        | with TTL buffer              | 2.0             | _                 | Vdd                            | V                          | $4.5V \leq V\text{DD} \leq 5.5V$                                                                    |

| D040A        |        |                              | 0.25 VDD + 0.8V | —                 | Vdd                            | V                          | For entire VDD range                                                                                |

| D041         |        | with Schmitt Trigger buffer  | 0.8 Vdd         | _                 | Vdd                            | V                          | For entire VDD range                                                                                |

| D042         |        | MCLR                         | 0.8 Vdd         | _                 | Vdd                            | V                          |                                                                                                     |

| D042A        |        | OSC1 (in XT and LP mode)     | 1.6V            | _                 | Vdd                            | V                          |                                                                                                     |

|              |        | OSC1 (in HS mode)            | 0.7 Vdd         | _                 | Vdd                            | V                          |                                                                                                     |

| D043         |        | OSC1 (in RC mode)            | 0.9 Vdd         | _                 | Vdd                            | V                          | (Note 1)                                                                                            |

|              |        | Ports RB1 and RB4:           |                 |                   |                                |                            |                                                                                                     |

| D044         |        | with Schmitt Trigger buffer  | 0.7 Vdd         |                   | Vdd                            | V                          | For entire VDD range                                                                                |

| D070         | Ipurb  | PORTB Weak Pull-up Current   | 50              | 250               | 400                            | μΑ                         | VDD = 5V, VPIN = VSS                                                                                |

|              | lı∟    | Input Leakage Current (Notes | 2, 3)           |                   |                                |                            |                                                                                                     |

| D060         |        | I/O ports                    | _               | —                 | ±1                             | μΑ                         | Vss $\leq$ VPIN $\leq$ VDD, pin at high-impedance                                                   |

| D061         |        | MCLR                         | —               | —                 | ±5                             | μA                         | $V \textbf{s} \textbf{s} \leq V \textbf{PIN} \leq V \textbf{D} \textbf{D}$                          |

| D063         |        | OSC1                         | _               | —                 | ±5                             | μA                         | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

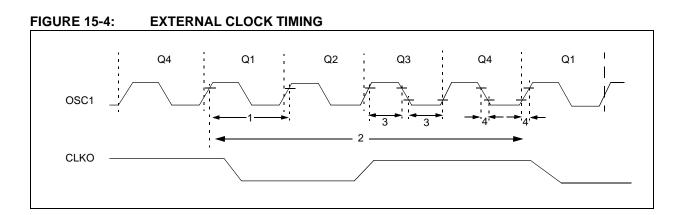

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                |

|--------------|-------|----------------------------------|------|------|--------|-------|---------------------------|

|              | Fosc  | External CLKI Frequency (Note 1) | DC   | _    | 1      | MHz   | XT and RC Oscillator mode |

|              |       |                                  | DC   | _    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | DC   | _    | 32     | kHz   | LP Oscillator mode        |

|              |       | Oscillator Frequency (Note 1)    | DC   |      | 4      | MHz   | RC Oscillator mode        |

|              |       |                                  | 0.1  | _    | 4      | MHz   | XT Oscillator mode        |

|              |       |                                  | 4    | —    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | 5    | _    | 200    | kHz   | LP Oscillator mode        |

| 1            | Tosc  | External CLKI Period (Note 1)    | 1000 | —    | —      | ns    | XT and RC Oscillator mode |

|              |       |                                  | 50   | —    | —      | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | —    | —      | ms    | LP Oscillator mode        |

|              |       | Oscillator Period (Note 1)       | 250  | _    | —      | ns    | RC Oscillator mode        |

|              |       |                                  | 250  |      | 10,000 | ns    | XT Oscillator mode        |

|              |       |                                  | 50   | _    | 250    | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | —    | —      | ms    | LP Oscillator mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200  | TCY  | DC     | ns    | TCY = 4/FOSC              |

| 3            | TosL, | External Clock in (OSC1) High    | 500  |      | —      | ns    | XT Oscillator             |

|              | TosH  | or Low Time                      | 2.5  | _    | _      | ms    | LP Oscillator             |

|              |       |                                  | 15   | _    | _      | ns    | HS Oscillator             |

| 4            | TosR, | External Clock in (OSC1) Rise or | —    |      | 25     | ns    | XT Oscillator             |

|              | TosF  | Fall Time                        | —    | _    | 50     | ns    | LP Oscillator             |

|              |       |                                  | —    | _    | 15     | ns    | HS Oscillator             |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

# PIC16F818/819

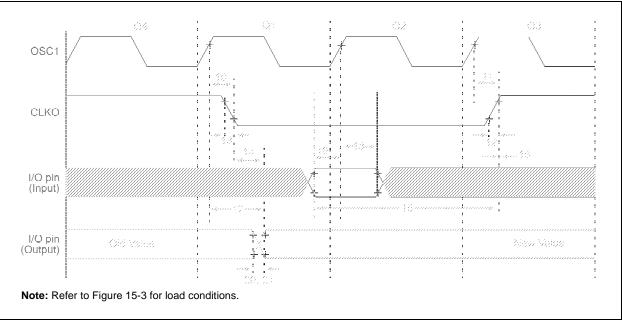

| TABLE 15-2: | CLKO AND I/O TIMING REQUIREMENTS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Param<br>No. | Symbol                                                                                     | Characterist                                   | ic                      | Min        | Тур† | Мах          | Units | Conditions |

|--------------|--------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------|------------|------|--------------|-------|------------|

| 10*          | TosH2ckL                                                                                   | OSC1 $\uparrow$ to CLKO $\downarrow$           |                         |            | 75   | 200          | ns    | (Note 1)   |

| 11*          | TosH2ckH                                                                                   | OSC1 ↑ to CLKO ↑                               |                         | _          | 75   | 200          | ns    | (Note 1)   |

| 12*          | ТскR                                                                                       | CLKO Rise Time                                 |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 13*          | ТскF                                                                                       | CLKO Fall Time                                 |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 14*          | TCKL2IOV                                                                                   | CLKO ↓ to Port Out Valid                       |                         | _          |      | 0.5 TCY + 20 | ns    | (Note 1)   |

| 15*          | ТюV2скН                                                                                    | Port In Valid before CLKO 1                    |                         | Tosc + 200 |      | _            | ns    | (Note 1)   |

| 16*          | TCKH2IOI                                                                                   | Port In Hold after CLKO ↑                      |                         | 0          | _    | —            | ns    | (Note 1)   |

| 17*          | TosH2IoV                                                                                   | OSC1 ↑ (Q1 cycle) to Port Out Valid            |                         | —          | 100  | 255          | ns    |            |

| 18*          | 18*         TosH2iOI         OSC1 ↑ (Q2 cycle) to Port<br>Input Invalid (I/O in hold time) | OSC1 ↑ (Q2 cycle) to Port                      | PIC16F818/819           | 100        | _    | —            | ns    |            |

|              |                                                                                            | PIC16LF818/819                                 | 200                     | _          | _    | ns           |       |            |

| 19*          | TIOV20SH                                                                                   | Port Input Valid to OSC1 1 (I/O in setup time) |                         | 0          | _    | —            | ns    |            |

| 20* TioR     | TIOR                                                                                       |                                                | PIC16F818/819           | _          | 10   | 40           | ns    |            |

|              |                                                                                            |                                                | PIC16LF818/819          | _          | _    | 145          | ns    |            |

| 21*          | TIOF                                                                                       | Port Output Fall Time                          | PIC16F818/819           | _          | 10   | 40           | ns    |            |

|              |                                                                                            |                                                | PIC16 <b>LF</b> 818/819 | _          |      | 145          | ns    |            |

| 22††*        | TINP                                                                                       | INT pin High or Low Time                       |                         | Тсү        | —    | —            | ns    |            |

| 23††*        | Trbp                                                                                       | RB7:RB4 Change INT High or Low Time            |                         | Тсү        | _    | _            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events, not related to any internal clock edges.

Note 1: Measurements are taken in RC mode, where CLKO output is 4 x Tosc.

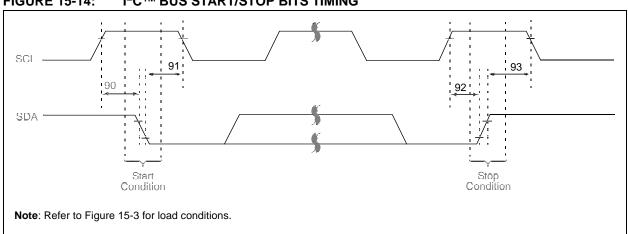

| Param<br>No. | Symbol                | Characteristic                                                         |                                                   | Min          | Тур†     | Max       | Units    | Conditions |

|--------------|-----------------------|------------------------------------------------------------------------|---------------------------------------------------|--------------|----------|-----------|----------|------------|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |                                                   | Тсү          | -        | -         | ns       |            |

| 71*          | TscH                  | SCK Input High Time (Slave mode)                                       |                                                   | Tcy + 20     | -        | _         | ns       |            |

| 72*          | TscL                  | SCK Input Low Time (Slave mode)                                        |                                                   | Tcy + 20     | -        | -         | ns       |            |

| 73*          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input to SCK Edge                               |                                                   | 100          | _        | _         | ns       |            |

| 74*          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDI Data Input to SCK Edge                                |                                                   | 100          | —        | —         | ns       |            |

| 75*          | TDOR                  | SDO Data Output Rise Time                                              | PIC16 <b>F</b> 818/819<br>PIC16 <b>LF</b> 818/819 |              | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 76*          | TDOF                  | SDO Data Output Fall Time                                              |                                                   | _            | 10       | 25        | ns       |            |

| 77*          | TssH2doZ              | SS ↑ to SDO Output High-Impedance                                      |                                                   | 10           | _        | 50        | ns       |            |

| 78*          | TscR                  | SCK Output Rise Time<br>(Master mode)                                  |                                                   |              | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 79*          | TscF                  | SCK Output Fall Time (Master mode)                                     |                                                   | —            | 10       | 25        | ns       |            |

| 80*          | TSCH2DOV,<br>TSCL2DOV | SDO Data Output Valid after SCK<br>Edge                                | PIC16 <b>F</b> 818/819<br>PIC16 <b>LF</b> 818/819 | _            | _        | 50<br>145 | ns<br>ns |            |

| 81*          | TDOV2scH,<br>TDOV2scL | SDO Data Output Setup to SCK Edge                                      |                                                   | Тсү          | —        | —         | ns       |            |

| 82*          | TssL2doV              | SDO Data Output Valid after $\overline{SS} \downarrow Edge$            |                                                   | —            | —        | 50        | ns       |            |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                                    |                                                   | 1.5 Tcy + 40 | —        | —         | ns       |            |

#### TABLE 15-6: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 15-14: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

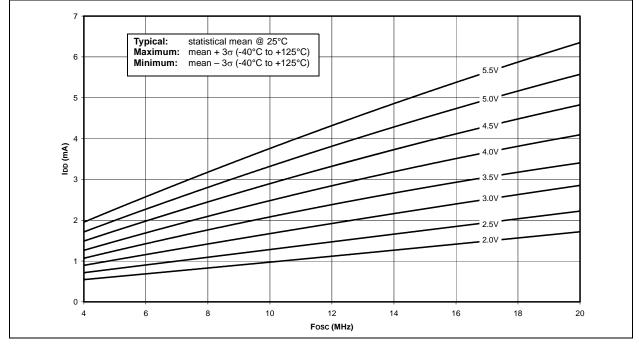

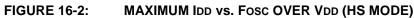

## 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

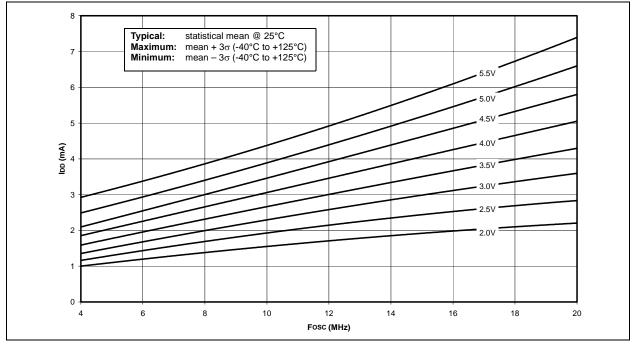

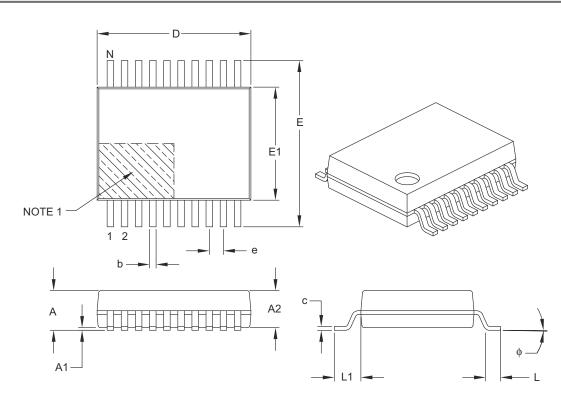

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension Lir            | nits        | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 18        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 11.55 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | $\varphi$   | 0°        | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.20      | -   | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

## 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|------|-------------|--|--|--|

| Dimensio                 | Dimension Limits |          | NOM  | MAX         |  |  |  |

| Number of Pins           | Ν                |          | 20   |             |  |  |  |

| Pitch                    | е                | 0.65 BSC |      |             |  |  |  |

| Overall Height           | А                | -        | -    | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75 | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -    | -           |  |  |  |

| Overall Width            | Е                | 7.40     | 7.80 | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30 | 5.60        |  |  |  |

| Overall Length           | D                | 6.90     | 7.20 | 7.50        |  |  |  |

| Foot Length              | L                | 0.55     | 0.75 | 0.95        |  |  |  |

| Footprint                | L1               | 1.25 REF |      |             |  |  |  |

| Lead Thickness           | С                | 0.09     | _    | 0.25        |  |  |  |

| Foot Angle               | φ                | 0°       | 4°   | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | -    | 0.38        |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

## APPENDIX A: REVISION HISTORY

#### Revision A (May 2002)

Original version of this data sheet.

#### **Revision B (August 2002)**

Added INTRC section. PWRT and BOR are independent of each other. Revised program memory text and code routine. Added QFN package. Modified PORTB diagrams.

#### **Revision C (November 2002)**

Added various new feature descriptions. Added internal RC oscillator specifications. Added low-power Timer1 specifications and RTC application example.

#### **Revision D (November 2003)**

Updated IRCF bit modification information and changed the INTOSC stabilization delay from 1 ms to 4 ms in Section 4.0 "Oscillator Configurations". Updated Section 12.17 "In-Circuit Serial Programming" to clarify LVP programming. In Section 15.0 "Electrical Characteristics", the DC Characteristics (Section 15.2 and Section 15.3) have been updated to include the Typ, Min and Max values and Table 15-1 "External Clock Timing Requirements" has been updated.

#### **Revision E (September 2004)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in Section 16.0 "DC and AC Characteristics Graphs and Tables" have been updated and there have been minor corrections to the data sheet text.

#### **Revision F (November 2011)**

This revision updated **Section 17.0** "Packaging Information".

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

#### TABLE B-1: DIFFERENCES BETWEEN THE PIC16F818 AND PIC16F819

| Features                            | PIC16F818 | PIC16F819 |  |

|-------------------------------------|-----------|-----------|--|

| Flash Program Memory (14-bit words) | 1K        | 2K        |  |

| Data Memory (bytes)                 | 128       | 256       |  |

| EEPROM Data Memory (bytes)          | 128       | 256       |  |