Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819-i-ptsl |

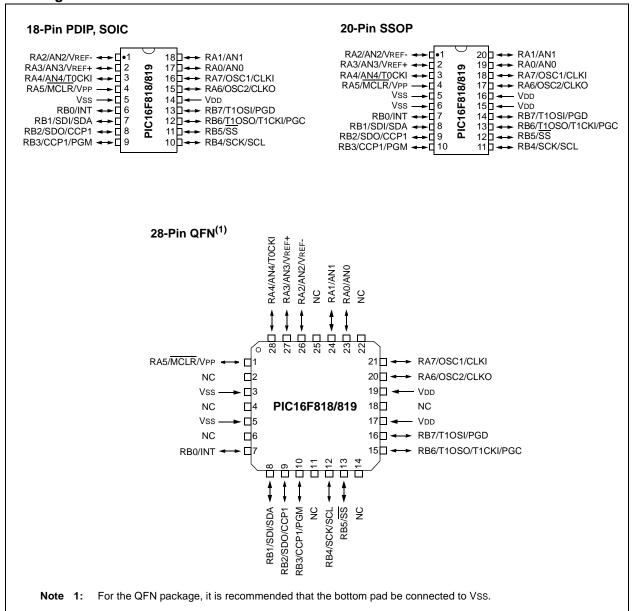

#### **Pin Diagrams**

#### **Table of Contents**

| 1.0   | Device Overview                             |      |

|-------|---------------------------------------------|------|

| 2.0   | Memory Organization                         | 9    |

| 3.0   | Data EEPROM and Flash Program Memory        | . 25 |

| 4.0   | Oscillator Configurations                   | . 33 |

| 5.0   | I/O Ports                                   | . 39 |

| 6.0   | Timer0 Module                               | . 53 |

| 7.0   | Timer1 Module                               | . 57 |

| 8.0   | Timer2 Module                               | . 63 |

| 9.0   | Capture/Compare/PWM (CCP) Module            | . 65 |

| 10.0  | Synchronous Serial Port (SSP) Module        | . 71 |

| 11.0  | Analog-to-Digital Converter (A/D) Module    | . 81 |

| 12.0  | Special Features of the CPU                 | . 89 |

| 13.0  | Instruction Set Summary                     | 103  |

|       | Development Support                         |      |

| 15.0  | Electrical Characteristics                  | 115  |

| 16.0  | DC and AC Characteristics Graphs and Tables | 141  |

| 17.0  | Packaging Information                       | 155  |

| Appe  | ndix A: Revision History                    | 165  |

| Appe  | ndix B: Device Differences                  | 165  |

| INDE  | X                                           | 167  |

| The N | Microchip Web Site                          | 173  |

| Custo | mer Change Notification Service             | 173  |

| Custo | mer Support                                 | 173  |

| Read  | er Response                                 | 174  |

| PIC16 | SF818/819 Product Identification System     | 175  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-x |

|-------|-------|--------|-------|-------|--------|-------|-------|

| GIE   | PEIE  | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF  |

| bit 7 |       |        |       |       |        |       | bit 0 |

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 **PEIE:** Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 TMR0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 TMR0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### PIC16F818/819

#### 2.2.2.8 PCON Register

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### REGISTER 2-8: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 **Unimplemented:** Read as '0'

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | d bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note AN556, "Implementing a Table Read" (DS00556).

#### 2.3.2 STACK

The PIC16F818/819 family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 2.4 Indirect Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### **EXAMPLE 2-1: INDIRECT ADDRESSING**

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- · Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected).

A simple program to clear RAM locations, 20h-2Fh, using indirect addressing is shown in Example 2-2.

# EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | CLRF<br>INCF | 0x20<br>FSR<br>INDF<br>FSR<br>FSR, 4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|----------|--------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CONTINUE | :            |                                              |                                                                                                         |

|          | :            |                                              | ;YES, continue                                                                                          |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6.

#### 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- Clear the EEPGD bit to point to EEPROM data memory.

- Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

#### **EXAMPLE 3-1:** DATA EEPROM READ

```

BANKSEL EEADR

; Select Bank of EEADR

MOVF

ADDR. W

MOVWF

EEADR

: Data Memory Address

; to read

BANKSEL EECON1

; Select Bank of EECON1

BCF

EECON1, EEPGD; Point to Data memory

BSF

EECON1, RD ; EE Read

BANKSEL EEDATA

; Select Bank of EEDATA

; W = EEDATA

MOVF

EEDATA, W

```

#### 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then, the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- Write the 8-bit data value to be programmed in the EEDATA register.

- Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- · Set the WR bit

- 8. Enable interrupts (if using interrupts).

- Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set (EEIF must be cleared by firmware). If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to be clear, to indicate the end of the program cycle.

#### **EXAMPLE 3-2: DATA EEPROM WRITE**

```

BANKSEL EECON1

; Select Bank of

; EECON1

EECON1, WR

; Wait for write

BTFSC

GOTO

$-1

; to complete

BANKSEL EEADR

; Select Bank of

; EEADR

MOVF

ADDR. W

MOVWF

EEADR

; Data Memory

; Address to write

MOVF

VALUE, W

MOVWF

EEDATA

; Data Memory Value

; to write

BANKSEL EECON1

; Select Bank of

; EECON1

BCF

EECON1, EEPGD; Point to DATA

; memory

BSF

EECON1, WREN ; Enable writes

BCF

; Disable INTs.

INTCON, GIE

MOVLW

55h

NOVWF

MOVLW

MOVWF

; Write 55h

EECON2

AAh

EECON2

; Write AAh

BSF

EECON1, WR

; Set WR bit to

; begin write

; Enable INTs.

BSF

INTCON, GIE

BCF

EECON1, WREN ; Disable writes

```

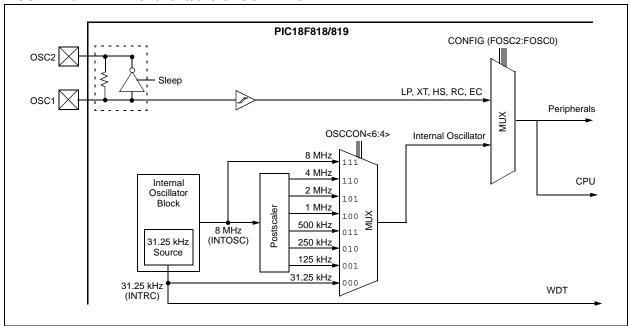

FIGURE 4-6: PIC16F818/819 CLOCK DIAGRAM

#### REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | R-0  | U-0 | U-0   |

|-------|-------|-------|-------|-----|------|-----|-------|

| _     | IRCF2 | IRCF1 | IRCF0 | _   | IOFS |     | _     |

| bit 7 |       |       |       |     |      | •   | hit 0 |

bit 7 Unimplemented: Read as '0'

bit 6-4 IRCF2:IRCF0: Internal Oscillator Frequency Select bits

111 = 8 MHz (8 MHz source drives clock directly)

110 = 4 MHz

101 = 2 MHz

100 = 1 MHz

011 = 500 kHz

010 = 250 kHz

001 = 125 kHz

000 = 31.25 kHz (INTRC source drives clock directly)

bit 3 Unimplemented: Read as '0'

bit 2 IOFS: INTOSC Frequency Stable bit

1 = Frequency is stable

0 = Frequency is not stable

bit 1-0 Unimplemented: Read as '0'

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

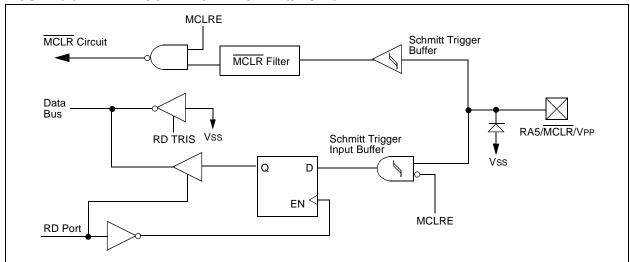

FIGURE 5-5: BLOCK DIAGRAM OF RA5/MCLR/VPP PIN

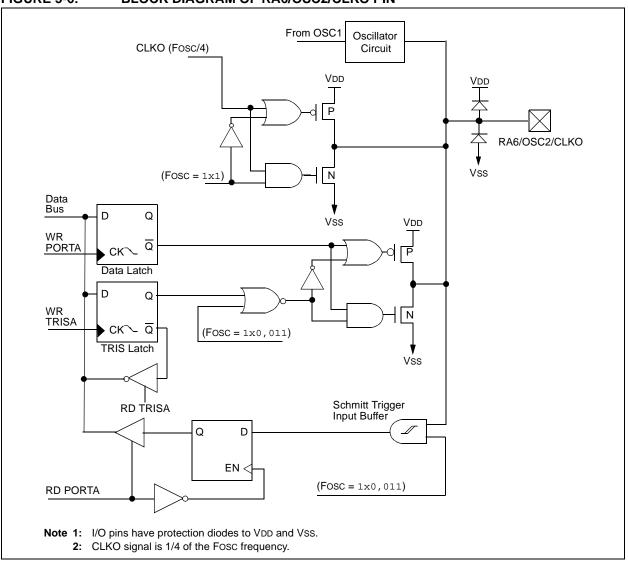

#### FIGURE 5-6: BLOCK DIAGRAM OF RA6/OSC2/CLKO PIN

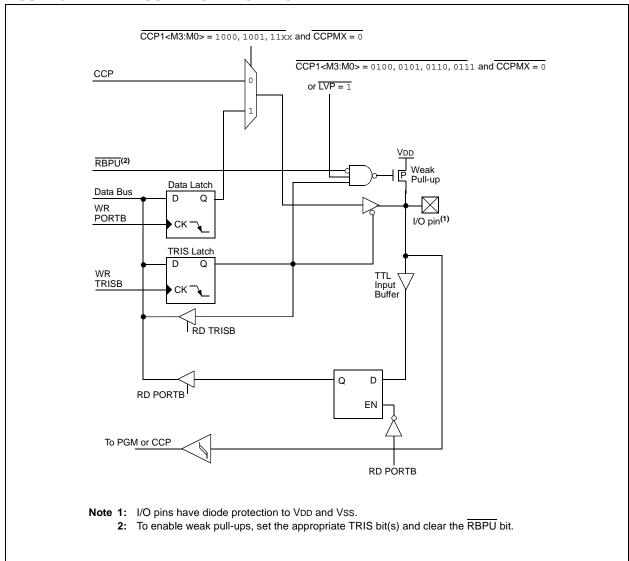

FIGURE 5-11: BLOCK DIAGRAM OF RB3 PIN

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 9-3:**

Resolution =

$$\frac{\log\left(\frac{\text{Fosc}}{\text{FPWM}}\right)}{\log(2)} \text{ bits}$$

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

Note: The TRISB bit (2 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

TABLE 9-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                                | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | Value on<br>POR, BOR |      | e on<br>ther<br>sets |

|----------------------|---------|--------|--------------------------------------|--------------|---------|---------|--------|---------|---------|------|----------------------|------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                 | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x                 | 0000 | 000u                 |

| 0Ch                  | PIR1    | _      | ADIF                                 | _            | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0   | 0000                 | -0   | 0000                 |

| 8Ch                  | PIE1    | _      | ADIE                                 | _            | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0   | 0000                 | -0   | 0000                 |

| 86h                  | TRISB   | PORT   | B Data Dire                          | ection Regis | ter     |         |        |         |         | 1111 | 1111                 | 1111 | 1111                 |

| 11h                  | TMR2    | Timer2 | 2 Module Re                          | gister       |         |         |        |         |         | 0000 | 0000                 | 0000 | 0000                 |

| 92h                  | PR2     | Timer2 | 2 Module Pe                          | riod Registe | er      |         |        |         |         | 1111 | 1111                 | 1111 | 1111                 |

| 12h                  | T2CON   | _      | TOUTPS3                              | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000                 | -000 | 0000                 |

| 15h                  | CCPR1L  | Captu  | Capture/Compare/PWM Register 1 (LSB) |              |         |         |        |         |         |      | xxxx                 | uuuu | uuuu                 |

| 16h                  | CCPR1H  | Captui | Capture/Compare/PWM Register 1 (MSB) |              |         |         |        |         |         |      | xxxx                 | uuuu | uuuu                 |

| 17h                  | CCP1CON | _      | _                                    | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000                 | 00   | 0000                 |

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, \ - = \text{unimplemented}, \ \text{read as `0'}. \ Shaded \ cells \ are \ \text{not used by PWM and Timer2}.$

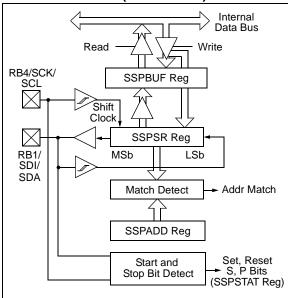

#### 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/SCK/SCL pin, which is the clock (SCL) and the RB1/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits.

To ensure proper communication of the  $I^2C$  Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the  $I^2C$  pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the  $I^2C$  pins (PORTx [SDA, SCL]) are changed in software during  $I^2C$  communication using a Read-Modify-Write instruction (BSF, BCF), then the  $I^2C$  mode may stop functioning properly and  $I^2C$  communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the  $I^2C$  pins) using the instruction BSF or BCF during  $I^2C$  communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

#### **EXAMPLE 10-1:**

```

MOVF TRISC, W ; Example for an 18-pin part such as the PIC16F818/819

IORLW 0x18 ; Ensures <4:3> bits are '11'

ANDLW B'11111001' ; Sets <2:1> as output, but will not alter other bits

; User can use their own logic here, such as IORLW, XORLW and ANDLW

MOVWF TRISC

```

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

### FIGURE 10-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for I<sup>2</sup>C operation:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Firmware Controlled Master mode with Start and Stop bit interrupts enabled, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

Additional information on SSP I<sup>2</sup>C operation may be found in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

#### 10.3.2 MASTER MODE OPERATION

Master mode operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Master mode operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISB<4,1> bit(s). The output level is always low, irrespective of the value(s) in PORTB<4,1>. So when transmitting data, a '1' data bit must have the TRISB<1> bit set (input) and a '0' data bit must have the TRISB<1> bit cleared (output). The same scenario is true for the SCL line with the TRISB<4> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- · Start condition

- · Stop condition

- Data transfer byte transmitted/received

Master mode operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011) or with the Slave mode active. When both Master mode operation and Slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on Master mode operation, see AN554, "Software Implementation of  ${}^{\beta}C^{TM}$  Bus Master" (DS00554).

#### 10.3.3 MULTI-MASTER MODE OPERATION

In Multi-Master mode operation, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISB<4,1>). There are two stages where this arbitration can be lost:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the Slave device continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

For more information on Multi-Master mode operation, see AN578, "Use of the SSP Module in the  $l^2C^{TM}$  Multi-Master Environment" (DS00578).

TABLE 10-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Address                | Name    | Bit 7              | Bit 6              | Bit 5                                 | Bit 4                       | Bit 3     | Bit 2      | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|---------|--------------------|--------------------|---------------------------------------|-----------------------------|-----------|------------|--------|--------|----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                | PEIE               | TMR0IE                                | INTE                        | RBIE      | TMR0IF     | INTF   | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                    | PIR1    | _                  | ADIF               | _                                     | _                           | SSPIF     | CCP1IF     | TMR2IF | TMR1IF | -0 0000              | -0 0000                         |

| 8Ch                    | PIE1    | _                  | ADIE               | _                                     | _                           | SSPIE     | CCP1IE     | TMR2IE | TMR1IE | -0 0000              | -0 0000                         |

| 13h                    | SSPBUF  | Synchron           | ous Seria          | l Port Rece                           | ive Buffe                   | r/Transmi | t Register |        |        | xxxx xxxx            | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchron           | ous Seria          | l Port (l <sup>2</sup> C <sup>⊤</sup> | <sup>™</sup> mode) <i>i</i> | Address F | Register   |        |        | 0000 0000            | 0000 0000                       |

| 14h                    | SSPCON  | WCOL               | SSPOV              | SSPEN                                 | CKP                         | SSPM3     | SSPM2      | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(1)</sup> | CKE <sup>(1)</sup> | D/A                                   | Р                           | S         | R/W        | UA     | BF     | 0000 0000            | 0000 0000                       |

| 86h                    | TRISB   | PORTB D            | ata Direc          |                                       | •                           | 1111 1111 | 1111 1111  |        |        |                      |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in I<sup>2</sup>C mode.

# PIC16F818/819

NOTES:

### 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- · In-Circuit Serial Programming

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

#### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space which can be accessed only during programming.

### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| DC CHARACTERISTICS |                   |                                         |            |      |            |          |                                                                                                 |  |  |  |

|--------------------|-------------------|-----------------------------------------|------------|------|------------|----------|-------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym               | Characteristic                          | Min        | Тур† | Max        | Units    | Conditions                                                                                      |  |  |  |

|                    | Vol               | Output Low Voltage                      |            |      |            |          |                                                                                                 |  |  |  |

| D080               |                   | I/O ports                               | _          | _    | 0.6        | V        | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                    |  |  |  |

| D083               |                   | OSC2/CLKO<br>(RC oscillator config)     | _          | _    | 0.6        | V        | IOL = $1.6 \text{ mA}$ , VDD = $4.5 \text{V}$ , $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ |  |  |  |

|                    | Vон               | Output High Voltage                     |            |      |            |          |                                                                                                 |  |  |  |

| D090               |                   | I/O ports (Note 3)                      | VDD - 0.7  | _    | _          | V        | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+125$ °C                                           |  |  |  |

| D092               |                   | OSC2/CLKO<br>(RC oscillator config)     | VDD - 0.7  | _    | _          | V        | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +125°C                                                   |  |  |  |

|                    |                   | Capacitive Loading Specs on Output Pins |            |      |            |          |                                                                                                 |  |  |  |

| D100               | Cosc <sub>2</sub> | OSC2 pin                                | _          |      | 15         | pF       | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1                          |  |  |  |

| D101               | Сю                | All I/O pins and OSC2<br>(in RC mode)   | _          | _    | 50         | pF       |                                                                                                 |  |  |  |

| D102               | Св                | SCL, SDA in I <sup>2</sup> C™ mode      | _          | -    | 400        | pF       |                                                                                                 |  |  |  |

|                    |                   | Data EEPROM Memory                      |            |      |            |          |                                                                                                 |  |  |  |

| D120               | ED                | Endurance                               | 100K       | 1M   | _          | E/W      | -40°C to +85°C                                                                                  |  |  |  |

|                    |                   |                                         | 10K        | 100K | _          | E/W      | +85°C to +125°C                                                                                 |  |  |  |

| D121               | VDRW              | VDD for read/write                      | VMIN       |      | 5.5        | V        | Using EECON to read/write,<br>VMIN = min. operating<br>voltage                                  |  |  |  |

| D122               | TDEW              | Erase/write cycle time                  | _          | 4    | 8          | ms       |                                                                                                 |  |  |  |

|                    |                   | Program Flash Memory                    |            |      |            |          |                                                                                                 |  |  |  |

| D130               | ЕP                | Endurance                               | 10K        | 100K | _          | E/W      | -40°C to +85°C                                                                                  |  |  |  |

| D131               | Vpr               | VDD for read                            | 1K<br>VMIN | 10K  | —<br>5.5   | E/W<br>V | +85°C to +125°C                                                                                 |  |  |  |

| D131               | VPR               | VDD for read                            | VMIN       |      | 5.5<br>5.5 | V        | Using EECON to read/write,                                                                      |  |  |  |

| D 132A             |                   | VDD IOI GIASE/WIILE                     | VIVIIIV    |      | J.U        | V        | VMIN = min. operating voltage                                                                   |  |  |  |

| D133               | TPE               | Erase cycle time                        | _          | 2    | 4          | ms       |                                                                                                 |  |  |  |

| D134               | Tpw               | Write cycle time                        |            | 2    | 4          | ms       |                                                                                                 |  |  |  |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

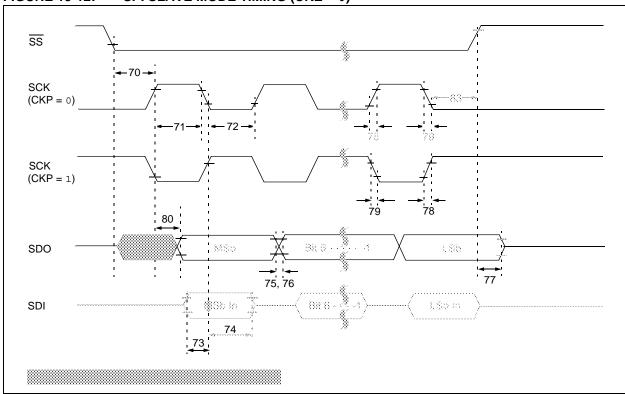

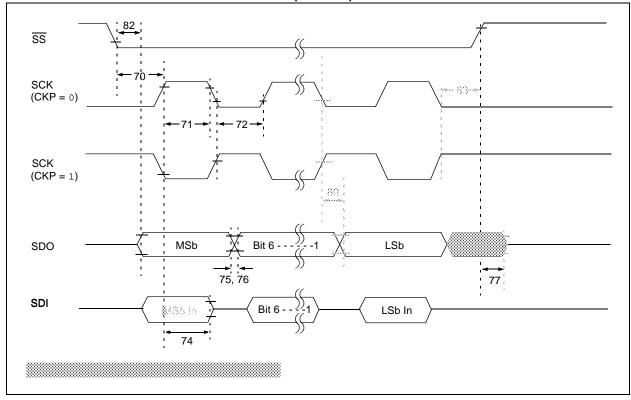

FIGURE 15-12: SPI SLAVE MODE TIMING (CKE = 0)

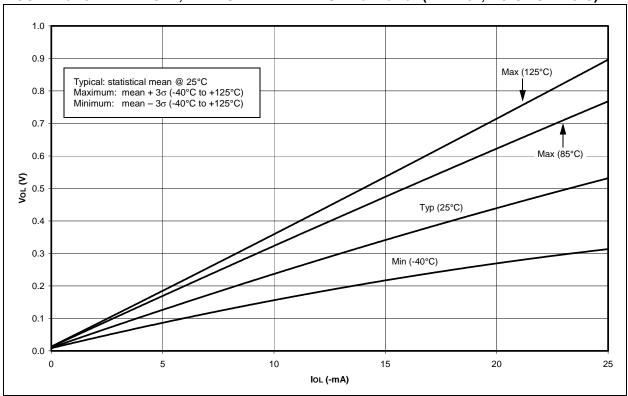

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

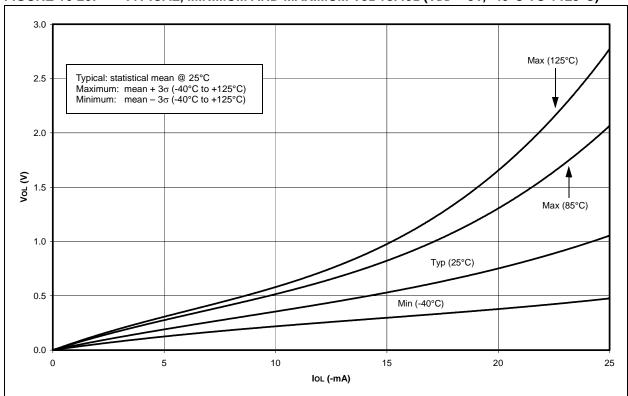

FIGURE 16-20: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 3V, -40°C TO +125°C)

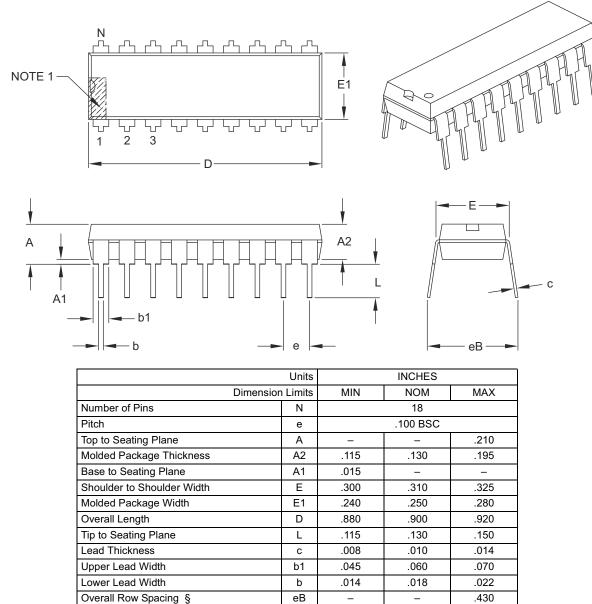

#### 18-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

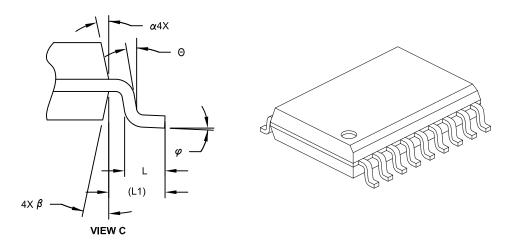

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |     |      |  |  |

|--------------------------|-------|-------------|-----|------|--|--|

| Dimension L              | imits | MIN         | NOM | MAX  |  |  |

| Number of Pins           | N     |             |     |      |  |  |

| Pitch                    | е     | 1.27 BSC    |     |      |  |  |

| Overall Height           | Α     | -           | -   | 2.65 |  |  |

| Molded Package Thickness | A2    | 2.05        | -   | -    |  |  |

| Standoff §               | A1    | 0.10        | -   | 0.30 |  |  |

| Overall Width            | Е     | 10.30 BSC   |     |      |  |  |

| Molded Package Width     | E1    | 7.50 BSC    |     |      |  |  |

| Overall Length           | D     | 11.55 BSC   |     |      |  |  |

| Chamfer (Optional)       | h     | 0.25        | -   | 0.75 |  |  |

| Foot Length              | L     | 0.40 -      |     | 1.27 |  |  |

| Footprint                | L1    | 1.40 REF    |     |      |  |  |

| Lead Angle               | Θ     | 0°          | -   | -    |  |  |

| Foot Angle               | φ     | 0°          | -   | 8°   |  |  |

| Lead Thickness           | С     | 0.20        | -   | 0.33 |  |  |

| Lead Width               | b     | 0.31        | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α     | 5°          | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β     | 5°          | _   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- ${\tt BSC: Basic\ Dimension.\ Theoretically\ exact\ value\ shown\ without\ tolerances.}$

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

### PIC16F818/819

| Writing to Flash Program Memory31                          | 1                                              |    |

|------------------------------------------------------------|------------------------------------------------|----|

| Code Protection 89, 100                                    | I/O Ports                                      | 30 |

| Computed GOTO23                                            | I <sup>2</sup> C                               |    |

| Configuration Bits89                                       | Associated Registers                           | 79 |

| Crystal Oscillator and Ceramic Resonators33                | Master Mode Operation                          |    |

| Customer Change Notification Service173                    | Mode                                           |    |

| Customer Notification Service173                           | Mode Selection                                 |    |

| Customer Support173                                        | Multi-Master Mode Operation                    |    |

| <b>D</b>                                                   | Slave Mode                                     |    |

| D                                                          | Addressing                                     |    |

| Data EEPROM Memory25                                       | Reception                                      |    |

| Associated Registers32                                     | SCL, SDA Pins                                  |    |

| EEADR Register25                                           | Transmission                                   |    |

| EEADRH Register25                                          | ID Locations                                   |    |

| EECON1 Register25                                          | In-Circuit Debugger                            |    |

| EECON2 Register25                                          | In-Circuit Serial Programming                  |    |

| EEDATA Register25                                          | In-Circuit Serial Programming (ICSP)           |    |

| EEDATH Register25                                          | INDF Register                                  |    |

| Operation During Code-Protect32                            | Indirect Addressing                            |    |

| Protection Against Spurious Writes32                       | Instruction Format                             |    |

| Reading27                                                  | Instruction Set                                |    |

| Write Interrupt Enable Flag (EEIF Bit)25                   | Descriptions                                   |    |

| Writing27                                                  | Read-Modify-Write Operations                   |    |

| Data Memory                                                | Summary Table                                  |    |

| Special Function Registers13                               | ADDLW                                          |    |

| DC and AC Characteristics                                  | ADDWF                                          |    |

| Graphs and Tables141                                       |                                                |    |

| DC Characteristics                                         | ANDLW<br>ANDWF                                 |    |

| Internal RC Accuracy125                                    |                                                |    |

| PIC16F818/819, PIC16LF818/819126                           | BCF                                            |    |

| Power-Down and Supply Current118                           | BSF                                            |    |

| Supply Voltage117                                          | BTFSC                                          |    |

| Development Support111                                     | BTFSS                                          |    |

| Device Differences165                                      | CALL                                           |    |

| Device Overview5                                           | CLRF                                           |    |

| Direct Addressing24                                        | CLRW                                           |    |

| -                                                          | CLRWDT<br>COMF                                 |    |

| E                                                          |                                                |    |

| EEADR Register25                                           | DECF                                           | _  |

| EEADRH Register25                                          | DECFSZ<br>GOTO                                 |    |

| EECON1 Register25                                          | INCF                                           |    |

| EECON2 Register25                                          |                                                |    |

| EEDATA Register25                                          | INCFSZ<br>IORLW                                |    |

| EEDATH Register25                                          |                                                |    |

| Electrical Characteristics115                              | IORWF                                          |    |

| Endurance1                                                 | MOVF                                           |    |

| Errata3                                                    | MOVLW                                          |    |

| External Clock Input34                                     | MOVWF<br>NOP                                   |    |

| External Interrupt Input (RB0/INT). See Interrupt Sources. |                                                |    |

| F                                                          | RETFIE                                         |    |

|                                                            | RETURN                                         |    |

| Flash Program Memory25                                     | RETURN                                         |    |

| Associated Registers32                                     | RLF                                            |    |

| EEADR Register25                                           | RRF                                            |    |

| EEADRH Register25                                          | SLEEP                                          |    |

| EECON1 Register25                                          | SUBLW                                          |    |

| EECON2 Register25                                          | SUBWF                                          |    |

| EEDATA Register25                                          | SWAPF                                          |    |

| EEDATH Register25                                          | XORLW                                          |    |

| Erasing28                                                  | XORWF                                          |    |

| Reading28                                                  | INT Interrupt (RB0/INT). See Interrupt Source: |    |

| Writing30                                                  | INTCON Register                                |    |

| FSR Register13, 14, 15, 23                                 | GIE Bit                                        |    |

| G                                                          | INTE Bit                                       | _  |

|                                                            | INTF Bit                                       |    |

| General Purpose Register File10                            | RBIF Bit                                       | 18 |