Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819-i-so |

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

### REGISTER 2-6: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS 8Dh)

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| _     | _   | _   | EEIE  | _   | _   |     | _     |

| bit 7 |     |     |       |     |     |     | bit 0 |

bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIE**: EEPROM Write Operation Interrupt Enable bit

1 = Enable EE write interrupt0 = Disable EE write interrupt

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| _     | _   | _   | EEIF  | _   | _   | _   | _     |

| bit 7 |     |     |       |     |     |     | bit 0 |

bit 7-5 **Unimplemented:** Read as '0'

bit 4 **EEIF**: EEPROM Write Operation Interrupt Enable bit

1 = Enable EE write interrupt 0 = Disable EE write interrupt

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

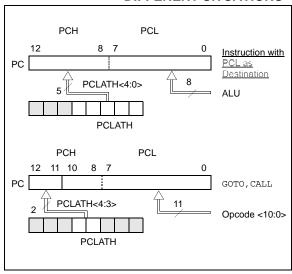

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note AN556, "Implementing a Table Read" (DS00556).

### 2.3.2 STACK

The PIC16F818/819 family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 2.4 Indirect Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### **EXAMPLE 2-1: INDIRECT ADDRESSING**

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- · Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected).

A simple program to clear RAM locations, 20h-2Fh, using indirect addressing is shown in Example 2-2.

## EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | CLRF<br>INCF | 0x20<br>FSR<br>INDF<br>FSR<br>FSR, 4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|----------|--------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CONTINUE | :            |                                              |                                                                                                         |

|          | :            |                                              | ;YES, continue                                                                                          |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (Status<7>) as shown in Figure 2-6.

### **5.0 I/O PORTS**

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

### 5.1 PORTA and the TRISA Register

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On   | а     | Pow    | er-o  | n Reset,   | the | e pins |

|-------|------|-------|--------|-------|------------|-----|--------|

|       | POR  | RTA<  | :4:0>  | are   | configured | as  | analog |

|       | inpu | ts ar | nd rea | ad as | '0'.       |     |        |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input and with an analog input to become the RA4/AN4/T0CKI pin. The RA4/AN4/T0CKI pin is a Schmitt Trigger input and full CMOS output driver.

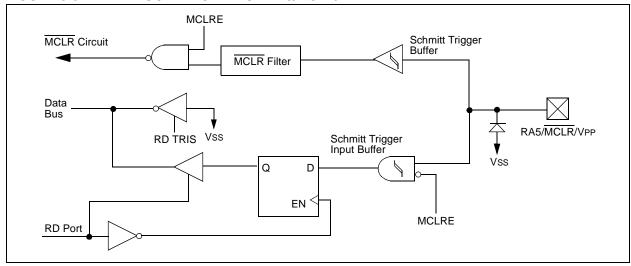

Pin RA5 is multiplexed with the Master Clear module input. The RA5/MCLR/VPP pin is a Schmitt Trigger input.

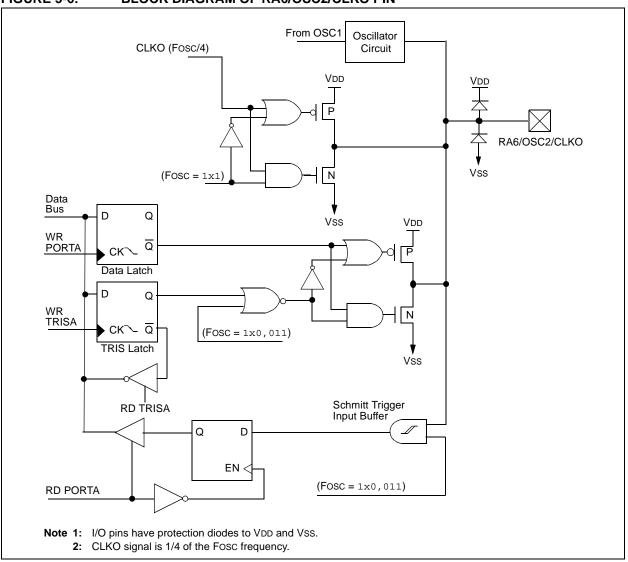

Pin RA6 is multiplexed with the oscillator module input and external oscillator output. Pin RA7 is multiplexed with the oscillator module input and external oscillator input. Pin RA6/OSC2/CLKO and pin RA7/OSC1/CLKI are Schmitt Trigger inputs and full CMOS output drivers.

Pins RA<1:0> are multiplexed with analog inputs. Pins RA<3:2> are multiplexed with analog inputs and VREF inputs. Pins RA<3:0> have TTL inputs and full CMOS output drivers.

**EXAMPLE 5-1: INITIALIZING PORTA**

| BANKSEL | PORTA  | ; | select bank of PORTA  |

|---------|--------|---|-----------------------|

| CLRF    | PORTA  | ; | Initialize PORTA by   |

|         |        | ; | clearing output       |

|         |        | ; | data latches          |

| BANKSEL | ADCON1 | ; | Select Bank of ADCON1 |

| MOVLW   | 0x06   | ; | Configure all pins    |

| MOVWF   | ADCON1 | ; | as digital inputs     |

| MOVLW   | 0xFF   | ; | Value used to         |

|         |        | ; | initialize data       |

|         |        | ; | direction             |

| MOVWF   | TRISA  | ; | Set RA<7:0> as inputs |

TABLE 5-1: PORTA FUNCTIONS

| Name          | Bit#  | Buffer                 | Function                                                                                                                                     |  |  |  |

|---------------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0       | bit 0 | TTL                    | Input/output or analog input.                                                                                                                |  |  |  |

| RA1/AN1       | bit 1 | TTL                    | Input/output or analog input.                                                                                                                |  |  |  |

| RA2/AN2/VREF- | bit 2 | TTL                    | Input/output, analog input or VREF                                                                                                           |  |  |  |

| RA3/AN3/VREF+ | bit 3 | TTL                    | Input/output, analog input or VREF+.                                                                                                         |  |  |  |

| RA4/AN4/T0CKI | bit 4 | ST                     | Input/output, analog input or external clock input for Timer0.                                                                               |  |  |  |

| RA5/MCLR/VPP  | bit 5 | ST                     | Input, Master Clear (Reset) or programming voltage input.                                                                                    |  |  |  |

| RA6/OSC2/CLKO | bit 6 | ST                     | Input/output, connects to crystal or resonator, oscillator output or 1/4 the frequency of OSC1 and denotes the instruction cycle in RC mode. |  |  |  |

| RA7/OSC1/CLKI | bit 7 | ST/CMOS <sup>(1)</sup> | Input/output, connects to crystal or resonator or oscillator input.                                                                          |  |  |  |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7  | Bit 6  | Bit 5                 | Bit 4 | Bit 3                         | Bit 2 | Bit 1 | Bit 0 | Value on POR, BOR | Value on all other Resets |

|---------|--------|--------|--------|-----------------------|-------|-------------------------------|-------|-------|-------|-------------------|---------------------------|

| 05h     | PORTA  | RA7    | RA6    | RA5                   | RA4   | RA3                           | RA2   | RA1   | RA0   | xxx0 0000         | uuu0 0000                 |

| 85h     | TRISA  | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | PORTA | PORTA Data Direction Register |       |       |       | 1111 1111         | 1111 1111                 |

| 9Fh     | ADCON1 | ADFM   | ADCS2  | _                     | _     | PCFG3                         | PCFG2 | PCFG1 | PCFG0 | 00 0000           | 00 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

FIGURE 5-5: BLOCK DIAGRAM OF RA5/MCLR/VPP PIN

### FIGURE 5-6: BLOCK DIAGRAM OF RA6/OSC2/CLKO PIN

### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### 6.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

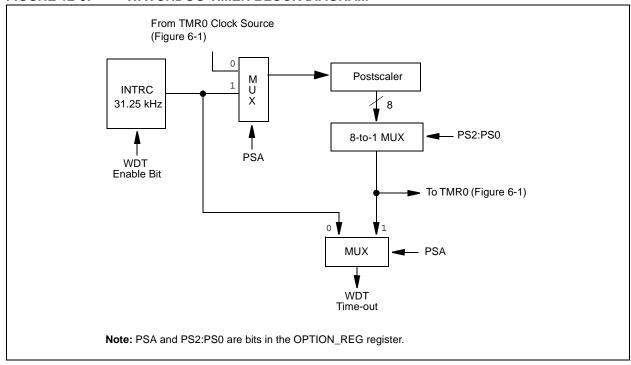

### 6.4 Prescaler

There is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

Timer0 module means that there is no prescaler for the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

### REGISTER 6-1: OPTION\_REG: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 **T0SE**: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

### bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1:256     | 1:128    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** To avoid an unintended device Reset, the instruction sequence shown in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

## PIC16F818/819

**NOTES:**

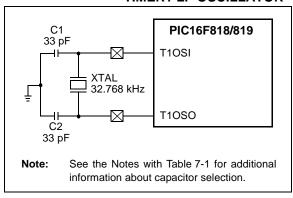

### 7.6 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note:

The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming™ (ICSP™) may not function correctly (high-voltage or low-voltage) or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

FIGURE 7-3: EXTERNAL

COMPONENTS FOR THE

TIMER1 LP OSCILLATOR

TABLE 7-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |

|----------|--------|-------|-------|

| LP       | 32 kHz | 33 pF | 33 pF |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Capacitor values are for design guidance only.

### 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

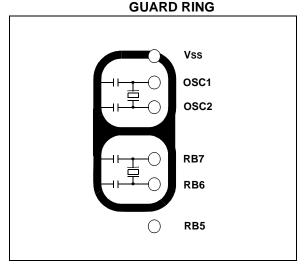

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

FIGURE 7-4: OSCILLATOR CIRCUIT WITH GROUNDED

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

### **EQUATION 9-3:**

Resolution =

$$\frac{\log\left(\frac{\text{Fosc}}{\text{FPWM}}\right)}{\log(2)} \text{ bits}$$

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

Note: The TRISB bit (2 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

TABLE 9-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                                | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | e on<br>BOR | all o | e on<br>ther<br>sets |

|----------------------|---------|--------|--------------------------------------|--------------|---------|---------|--------|---------|---------|------|-------------|-------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                 | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x        | 0000  | 000u                 |

| 0Ch                  | PIR1    | _      | ADIF                                 | _            | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0   | 0000        | -0    | 0000                 |

| 8Ch                  | PIE1    | _      | ADIE                                 | _            | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0   | 0000        | -0    | 0000                 |

| 86h                  | TRISB   | PORT   | B Data Dire                          | ection Regis | ter     |         |        |         |         | 1111 | 1111        | 1111  | 1111                 |

| 11h                  | TMR2    | Timer2 | Timer2 Module Register               |              |         |         |        |         |         | 0000 | 0000        | 0000  | 0000                 |

| 92h                  | PR2     | Timer2 | 2 Module Pe                          | riod Registe | er      |         |        |         |         | 1111 | 1111        | 1111  | 1111                 |

| 12h                  | T2CON   | _      | TOUTPS3                              | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000        | -000  | 0000                 |

| 15h                  | CCPR1L  | Captu  | Capture/Compare/PWM Register 1 (LSB) |              |         |         |        |         |         | xxxx | xxxx        | uuuu  | uuuu                 |

| 16h                  | CCPR1H  | Captui | Capture/Compare/PWM Register 1 (MSB) |              |         |         |        |         |         | xxxx | xxxx        | uuuu  | uuuu                 |

| 17h                  | CCP1CON | _      | _                                    | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000        | 00    | 0000                 |

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, \ - = \text{unimplemented}, \ \text{read as `0'}. \ Shaded \ cells \ are \ \text{not used by PWM and Timer2}.$

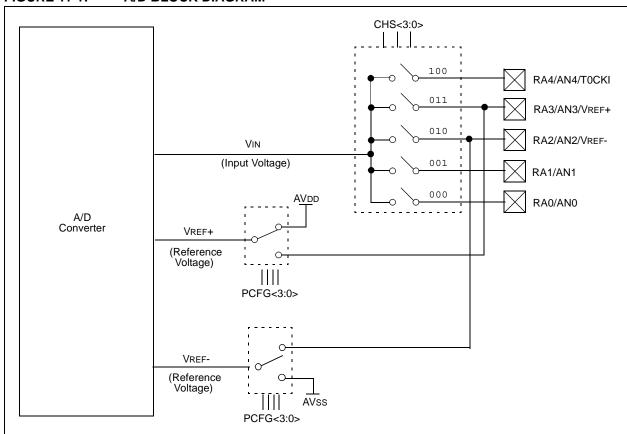

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1 "A/D Acquisition Requirements"**. After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

FIGURE 11-1: A/D BLOCK DIAGRAM

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of Global Interrupt Enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 "Power-Down Mode (Sleep)" for details on Sleep mode.

### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>) (see **Section 6.0 "Timer0 Module"**).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). See Section 3.2 "EECON1 and EECON2 Registers".

### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, Status registers). This will have to be implemented in software as shown in Example 12-1.

For PIC16F818 devices, the upper 64 bytes of each bank are common. Temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed here. These 64 locations do not require banking and therefore, make it easier for context save and restore.

For PIC16F819 devices, the upper 16 bytes of each bank are common.

#### **EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM**

```

MOVWF

W TEMP

;Copy W to TEMP register

SWAPF

STATUS, W

;Swap status to be saved into W

STATUS

CLRF

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

MOVWF

STATUS TEMP

; Save status to bank zero STATUS TEMP register

:(ISR)

; Insert user code here

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

W TEMP, F

; Swap W TEMP

SWAPF

SWAPF

W TEMP, W

;Swap W TEMP into W

```

### 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits"**).

WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | T0SE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

### 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                  | ANDWF           |  |  |

|------------------|------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:          | [label] ADDLW k                                                                    | Syntax:         |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                | Operands:       |  |  |

| Operation:       | $(W) + k \rightarrow (W)$                                                          |                 |  |  |

| Status Affected: | C, DC, Z                                                                           | Operation:      |  |  |

| Description:     | The contents of the W register                                                     | Status Affected |  |  |

| ·                | are added to the eight-bit literal 'k' and the result is placed in the W register. | Description:    |  |  |

|                  |                                                                                    |                 |  |  |

| ANDWF            | AND W with f                                                                                                                                     |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                              |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                               |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                              |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                               |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (destination)$                                                                                                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                         |  |  |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |  |  |  |

| BCF              | Bit Clear f                                                         |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |  |

| Operation:       | $0 \rightarrow (f {<} b {>})$                                       |  |  |  |  |

| Status Affected: | None                                                                |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |  |  |

|                  |                                                                     |  |  |  |  |

|                  |                                                                     |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                           |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDLW k                                                                                              |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |  |

| Operation:       | (W) .AND. $(k) \rightarrow (W)$                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |  |

| Description:     | The contents of W register are ANDed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [ label ] BSF f,b                    |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF<br>(Indu                        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial |     |                                                                                                                                                                                                                                       |       |              |            |                 |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|------------|-----------------|--|--|--|

| PIC16F818/819<br>(Industrial, Extended) |                                                                                                                                                          |     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |       |              |            |                 |  |  |  |

| Param Device                            |                                                                                                                                                          | Тур | Max                                                                                                                                                                                                                                   | Units | c Conditions |            |                 |  |  |  |

|                                         | Supply Current (IDD) <sup>(2,3)</sup>                                                                                                                    |     |                                                                                                                                                                                                                                       |       |              |            |                 |  |  |  |

|                                         | PIC16LF818/819                                                                                                                                           | 9   | 20                                                                                                                                                                                                                                    | μА    | -40°C        |            |                 |  |  |  |

|                                         |                                                                                                                                                          | 7   | 15                                                                                                                                                                                                                                    | μΑ    | +25°C        | VDD = 2.0V |                 |  |  |  |

|                                         |                                                                                                                                                          | 7   | 15                                                                                                                                                                                                                                    | μΑ    | +85°C        |            |                 |  |  |  |

|                                         | PIC16LF818/819                                                                                                                                           | 16  | 30                                                                                                                                                                                                                                    | μΑ    | -40°C        |            |                 |  |  |  |

|                                         |                                                                                                                                                          |     | 25                                                                                                                                                                                                                                    | μА    | +25°C        | VDD = 3.0V | Fosc = 32 kHz   |  |  |  |

|                                         |                                                                                                                                                          | 14  | 25                                                                                                                                                                                                                                    | μΑ    | +85°C        |            | (LP Oscillator) |  |  |  |

|                                         | All devices                                                                                                                                              | 32  | 40                                                                                                                                                                                                                                    | μΑ    | -40°C        |            |                 |  |  |  |

|                                         |                                                                                                                                                          | 26  | 35                                                                                                                                                                                                                                    | μΑ    | +25°C        | VDD = 5.0V |                 |  |  |  |

|                                         |                                                                                                                                                          | 26  | 35                                                                                                                                                                                                                                    | μΑ    | +85°C        | VDD = 5.0V |                 |  |  |  |

|                                         | Extended devices                                                                                                                                         | 35  | 53                                                                                                                                                                                                                                    | μΑ    | +125°C       |            |                 |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF                                 | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                                                                     |     |       |        |             |                         |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|-------------|-------------------------|--|--|--|

| PIC16F818/819<br>(Industrial, Extended) |                                                                                                                                        | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |       |        |             |                         |  |  |  |

| Param<br>No.                            | Device                                                                                                                                 | Тур                                                                                                                                                                                                                                 | Max | Units |        | Conditions  |                         |  |  |  |

|                                         | Supply Current (IDD)(2,3)                                                                                                              |                                                                                                                                                                                                                                     |     |       |        |             |                         |  |  |  |

|                                         | PIC16LF818/819                                                                                                                         | .950                                                                                                                                                                                                                                | 1.3 | mA    | -40°C  |             |                         |  |  |  |

|                                         |                                                                                                                                        |                                                                                                                                                                                                                                     | 1.2 | mA    | +25°C  | VDD = 3.0V  |                         |  |  |  |

|                                         |                                                                                                                                        | .930                                                                                                                                                                                                                                | 1.2 | mA    | +85°C  |             | Fosc = 8 MHz            |  |  |  |

| All devices                             |                                                                                                                                        | 1.8                                                                                                                                                                                                                                 | 3.0 | mA    | -40°C  |             | (RC_RUN mode,           |  |  |  |

|                                         |                                                                                                                                        | 1.7                                                                                                                                                                                                                                 | 2.8 | mA    | +25°C  | VDD = 5.0V  | Internal RC Oscillator) |  |  |  |

|                                         |                                                                                                                                        | 1.7                                                                                                                                                                                                                                 | 2.8 | mA    | +85°C  | 0.00 = 5.00 |                         |  |  |  |

|                                         | Extended devices                                                                                                                       | 2.0                                                                                                                                                                                                                                 | 4.0 | mA    | +125°C |             |                         |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in  $k\Omega$ .

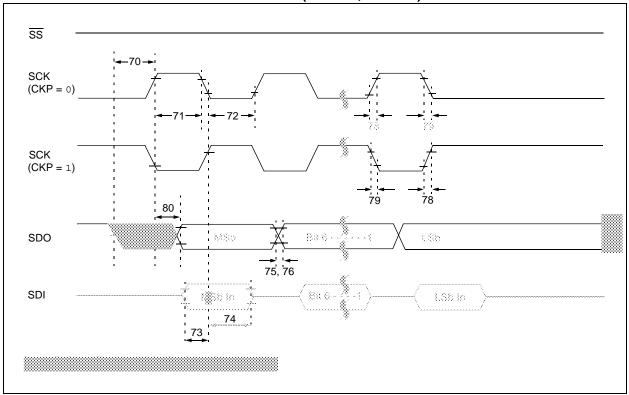

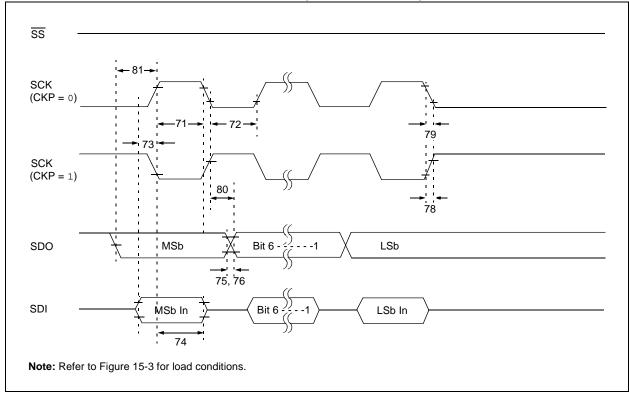

FIGURE 15-10: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

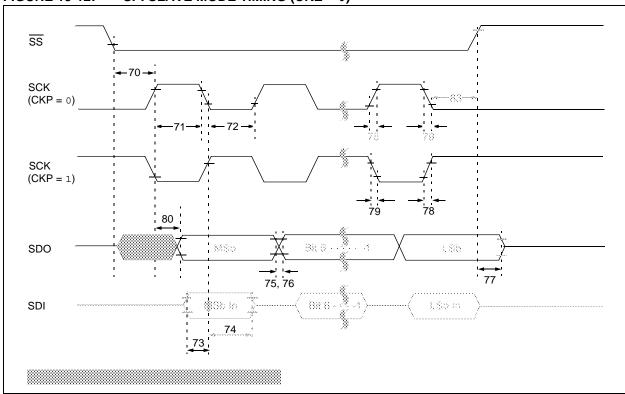

FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

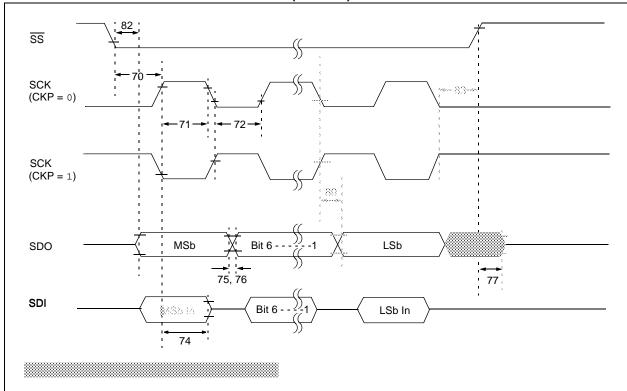

FIGURE 15-12: SPI SLAVE MODE TIMING (CKE = 0)

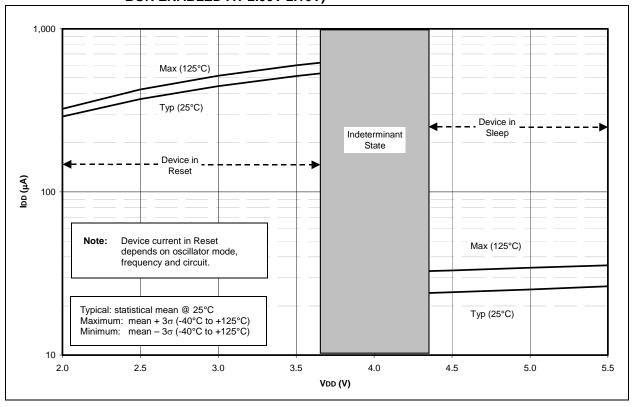

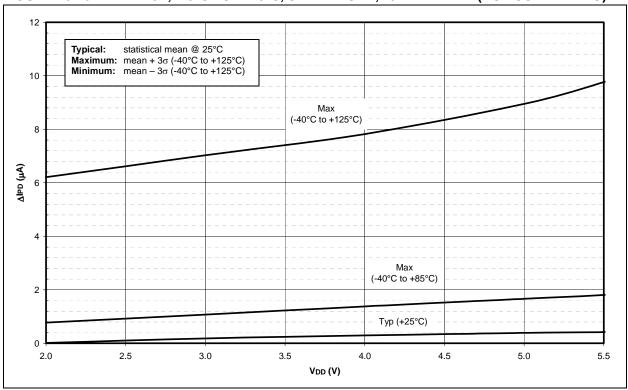

FIGURE 16-15:  $\triangle$ IPD BOR vs. VDD, -40°C TO +125°C (SLEEP MODE, BOR ENABLED AT 2.00V-2.16V)

FIGURE 16-16: IPD A/D, -40°C TO +125°C, SLEEP MODE, A/D ENABLED (NOT CONVERTING)

### PIC16F818/819 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | <u>x</u>                                                                         | <u>xxx</u> | Examples:                                                                                                                                       |

|-------------------|----------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | Temperature Package<br>Range                                                     | Pattern    | a) PIC16LF818-I/P = Industrial temp., PDIP package, Extended VDD limits. b) PIC16F818-I/SO = Industrial temp., SOIC package, normal VDD limits. |

| Device            | PIC16F818: Standard VDD<br>PIC16F818T: (Tape and Ree<br>PIC16LF818: Extended VDD | el)        |                                                                                                                                                 |

| Temperature Range | - = 0°C to +70°C<br>I = -40°C to +85°C (Ind<br>E = -40°C to +125°C (E            |            |                                                                                                                                                 |

| Package           | P = PDIP<br>SO = SOIC<br>SS = SSOP<br>ML = QFN                                   |            | Note 1: F = CMOS Flash  LF = Low-Power CMOS Flash                                                                                               |

| Pattern           | QTP, SQTP, ROM Code (fac<br>Special Requirements. Blank<br>Windowed devices.     |            | 2: T = in tape and reel – SOIC, SSOP packages only.                                                                                             |

|                   |                                                                                  |            |                                                                                                                                                 |

|                   |                                                                                  |            |                                                                                                                                                 |

### PIC16F818/819

NOTES: