Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

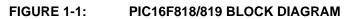

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | I²C, SPI                                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                    |

| Data Converters            | A/D 5x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819t-i-mltsl |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type | Buffer<br>Type | Description                                                                                |

|-------------------|-----------------------|--------------|-------------|---------------|----------------|--------------------------------------------------------------------------------------------|

|                   |                       |              |             |               |                | PORTA is a bidirectional I/O port.                                                         |

| RA0/AN0           | 17                    | 19           | 23          |               |                |                                                                                            |

| RA0               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN0               |                       |              |             | I             | Analog         | Analog input channel 0.                                                                    |

| RA1/AN1           | 18                    | 20           | 24          |               |                |                                                                                            |

| RA1               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN1               |                       |              |             | I             | Analog         | Analog input channel 1.                                                                    |

| RA2/AN2/VREF-     | 1                     | 1            | 26          |               |                |                                                                                            |

| RA2               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN2               |                       |              |             | I             | Analog         | Analog input channel 2.                                                                    |

| VREF-             |                       |              |             | I             | Analog         | A/D reference voltage (low) input.                                                         |

| RA3/AN3/VREF+     | 2                     | 2            | 27          |               |                |                                                                                            |

| RA3               |                       |              |             | I/O           | TTL            | Bidirectional I/O pin.                                                                     |

| AN3               |                       |              |             | I             | Analog         | Analog input channel 3.                                                                    |

| VREF+             |                       |              |             | I             | Analog         | A/D reference voltage (high) input.                                                        |

| RA4/AN4/T0CKI     | 3                     | 3            | 28          |               |                |                                                                                            |

| RA4               |                       |              |             | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| AN4               |                       |              |             | I             | Analog         | Analog input channel 4.                                                                    |

| TOCKI             |                       |              |             | I             | ST             | Clock input to the TMR0 timer/counter.                                                     |

| RA5/MCLR/Vpp      | 4                     | 4            | 1           |               |                |                                                                                            |

| RA5               |                       |              |             | I             | ST             | Input pin.                                                                                 |

| MCLR              |                       |              |             | I             | ST             | Master Clear (Reset). Input/programming                                                    |

|                   |                       |              |             |               |                | voltage input. This pin is an active-low Reset                                             |

| Vpp               |                       |              |             | Р             |                | to the device.                                                                             |

|                   |                       | . –          |             | Р             | _              | Programming threshold voltage.                                                             |

| RA6/OSC2/CLKO     | 15                    | 17           | 20          |               | 07             |                                                                                            |

| RA6               |                       |              |             | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| OSC2              |                       |              |             | 0             | _              | Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode. |

| CLKO              |                       |              |             | 0             |                | In RC mode, this pin outputs CLKO signal                                                   |

| OLINO             |                       |              |             | 0             |                | which has 1/4 the frequency of OSC1 and                                                    |

|                   |                       |              |             |               |                | denotes the instruction cycle rate.                                                        |

| RA7/OSC1/CLKI     | 16                    | 18           | 21          |               |                | ······································                                                     |

| RA7               | 10                    | 10           | 21          | I/O           | ST             | Bidirectional I/O pin.                                                                     |

| OSC1              |                       |              |             | 1/0           | ST/CMOS(3)     | Oscillator crystal input.                                                                  |

| CLKI              |                       |              |             | I             | _              | External clock source input.                                                               |

| Legend: I = Input |                       | 0 =          | = Outp      | but           | I/O =          | Input/Output P = Power                                                                     |

| - = Not us        | sed                   |              | = TTL       |               |                | Schmitt Trigger Input                                                                      |

TABLE 1-2:PIC16F818/819 PINOUT DESCRIPTIONS

$\label{eq:Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.$

**2:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F818/819. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F818 device's 128 bytes of data EEPROM memory have the address range of 00h-7Fh and the PIC16F819 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in Section 3.0 "Data EEPROM and Flash Program Memory".

Additional information on device memory may be found in the *"PIC<sup>®</sup> Mid-Range Reference Manual"* (DS33023).

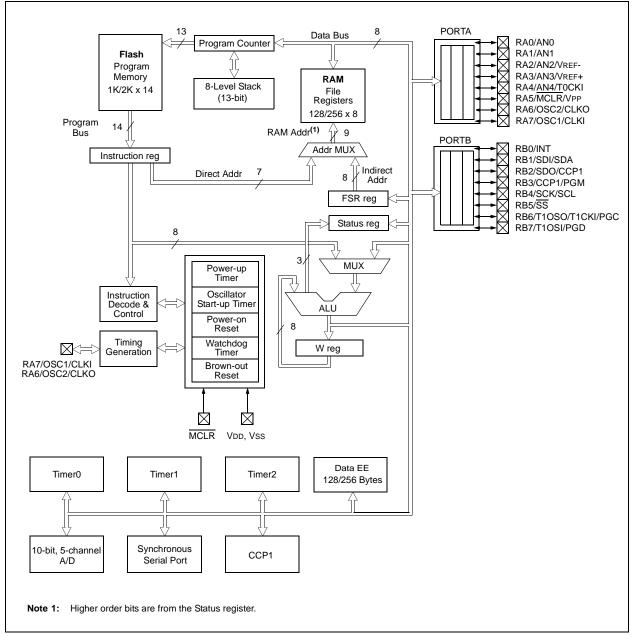

#### 2.1 **Program Memory Organization**

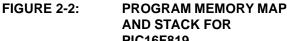

The PIC16F818/819 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F818, the first 1K x 14 (0000h-03FFh) is physically implemented (see Figure 2-1). For the PIC16F819, the first 2K x 14 is located at 0000h-07FFh (see Figure 2-2). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

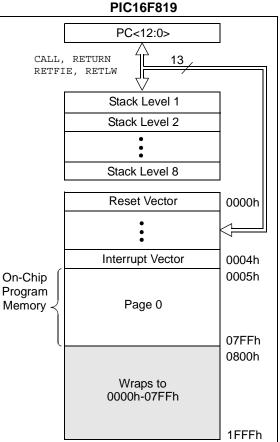

#### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM, with an address range from 00h to 0FFh. Addresses from 80h to FFh are unimplemented on the PIC16F818 device and will read 00h. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. These devices have 1K or 2K words of program Flash, with an address range from 0000h to 03FFh for the PIC16F818 and 0000h to 07FFh for the PIC16F819. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

## 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

#### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when Reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

#### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

| Name                        | Bit#  | Buffer                | Function                                                                                                                                                                       |

|-----------------------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                     | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                                                                                  |

| RB1/SDI/SDA                 | bit 1 | TTL/ST <sup>(5)</sup> | Input/output pin, SPI data input pin or I <sup>2</sup> C™ data I/O pin.<br>Internal software programmable weak pull-up.                                                        |

| RB2/SDO/CCP1                | bit 2 | TTL/ST <sup>(4)</sup> | Input/output pin, SPI data output pin or<br>Capture input/Compare output/PWM output pin.<br>Internal software programmable weak pull-up.                                       |

| RB3/CCP1/PGM <sup>(3)</sup> | bit 3 | TTL/ST <sup>(2)</sup> | Input/output pin, Capture input/Compare output/PWM output pin<br>or programming in LVP mode. Internal software programmable<br>weak pull-up.                                   |

| RB4/SCK/SCL                 | bit 4 | TTL/ST <sup>(5)</sup> | Input/output pin or SPI and I <sup>2</sup> C clock pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                             |

| RB5/SS                      | bit 5 | TTL                   | Input/output pin or SPI slave select pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                           |

| RB6/T1OSO/T1CKI/<br>PGC     | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator output pin, Timer1 clock input pin or serial programming clock (with interrupt-on-change).<br>Internal software programmable weak pull-up. |

| RB7/T1OSI/PGD               | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator input pin or serial programming data<br>(with interrupt-on-change).<br>Internal software programmable weak pull-up.                        |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: Low-Voltage ICSP<sup>™</sup> Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 18-pin mid-range devices.

- 4: This buffer is a Schmitt Trigger input when configured for CCP or SSP mode.

- **5:** This buffer is a Schmitt Trigger input when configured for SPI or I<sup>2</sup>C mode.

| TABLE 5-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address   | Name       | Bit 7 | Bit 6                                                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|------------|-------|-----------------------------------------------------------------|-------|-------|-------|-------|-------|-----------|----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                                                             | RB5   | RB4   | RB3   | RB2   | RB1   | RB0       | xxxx xxxx            | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register                                   |       |       |       |       |       |           | 1111 1111            | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | PU   INTEDG   TOCS   TOSE   PSA   PS2   PS1   PS0   1111   1111 |       |       |       |       |       | 1111 1111 |                      |                                 |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

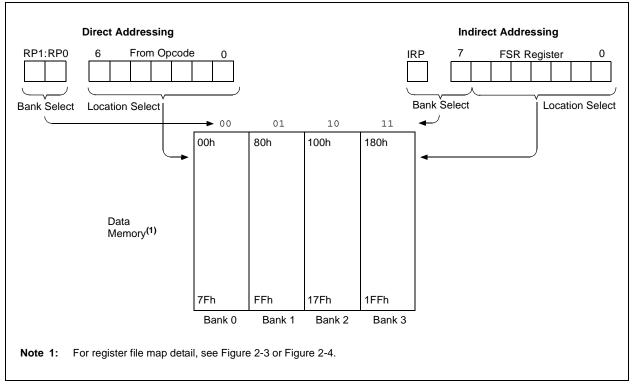

### 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt-on-overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

Figure 6-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

#### 6.1 Timer0 Operation

Timer0 operation is controlled through the OPTION\_REG register (see Register 2-2). Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/AN4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.3 "Using Timer0 with an External Clock".

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. **Section 6.4** "**Prescaler**" details the operation of the prescaler.

#### 6.2 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit, TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit, TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut-off during Sleep.

#### FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

© 2001-2013 Microchip Technology Inc.

#### 7.6 Timer1 Oscillator

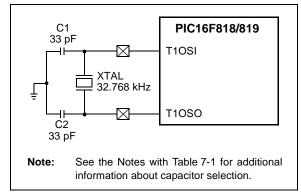

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note: The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) may not function correctly (high-voltage or lowvoltage) or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

#### TABLE 7-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |  |  |

|----------|--------|-------|-------|--|--|

| LP       | 32 kHz | 33 pF | 33 pF |  |  |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- 2: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

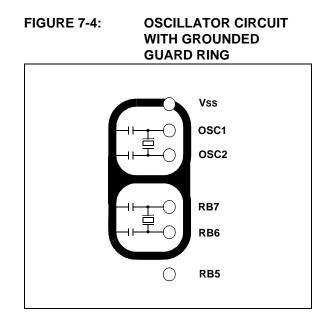

#### 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

### 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                 | U-0        | R/W-0        | R/W-0        | R/W-0         | R/W-0      | R/W-0          | R/W-0       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|---------------|------------|----------------|-------------|--|--|

| —                                                                                                                                                                   | —          | CCP1X        | CCP1Y        | CCP1M3        | CCP1M2     | CCP1M1         | CCP1M0      |  |  |

| bit 7                                                                                                                                                               |            |              |              |               |            |                | bit 0       |  |  |

|                                                                                                                                                                     |            |              |              |               |            |                |             |  |  |

| Unimpleme                                                                                                                                                           |            |              |              |               |            |                |             |  |  |

| CCP1X:CCP1Y: PWM Least Significant bits                                                                                                                             |            |              |              |               |            |                |             |  |  |

| <u>Capture mode:</u><br>Unused.                                                                                                                                     |            |              |              |               |            |                |             |  |  |

| <u>Compare mode:</u><br>Unused.                                                                                                                                     |            |              |              |               |            |                |             |  |  |

| <u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                          |            |              |              |               |            |                |             |  |  |

| CCP1M3:CCP1M0: CCP1 Mode Select bits                                                                                                                                |            |              |              |               |            |                |             |  |  |

| 0000 <b>= Cap</b>                                                                                                                                                   | ture/Compa | are/PWM di   | sabled (res  | ets CCP1 m    | odule)     |                |             |  |  |

| 0100 = Cap                                                                                                                                                          | ture mode, | every fallin | g edge       |               |            |                |             |  |  |

| 0101 <b>= Cap</b>                                                                                                                                                   |            |              |              |               |            |                |             |  |  |

| 0110 = Cap                                                                                                                                                          |            | •            | •••          |               |            |                |             |  |  |

| 0111 = Cap                                                                                                                                                          |            | •            | • •          | (CCP1IF bit   | ic cot)    |                |             |  |  |

|                                                                                                                                                                     |            | · ·          |              | h (CCP1IF b   | ,          |                |             |  |  |

| 1010 <b>= Com</b>                                                                                                                                                   |            |              |              | terrupt on ma |            | F bit is set,  | CCP1 pin is |  |  |

| 1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |            |              |              |               |            |                |             |  |  |

| 11xx = PWM mode                                                                                                                                                     |            |              |              |               |            |                |             |  |  |

|                                                                                                                                                                     |            |              |              |               |            |                |             |  |  |

|                                                                                                                                                                     |            |              |              |               |            |                |             |  |  |

| Legend:                                                                                                                                                             |            |              |              |               |            |                |             |  |  |

| <b>Legend:</b><br>R = Readab                                                                                                                                        | le bit     | W = V        | Vritable bit | U = Uni       | mplemented | l bit, read as | s 'O'       |  |  |

### REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

|            |      |                 | R/P-1     |                             | -        | 101 1    | R/P-1             | R/P-1              | R/P-1           | -                    | R/P-1        | R/P-1 | R/P-1 |

|------------|------|-----------------|-----------|-----------------------------|----------|----------|-------------------|--------------------|-----------------|----------------------|--------------|-------|-------|

| CP CC      | CPMX | DEBUG           | WRT1      | WRT0                        | CPD      | LVP      | BOREN             | MCLRE              | FOSC2           | PWRTEN               | WDTEN        | FOSC1 | FOSC0 |

| oit 13     |      |                 |           |                             |          |          |                   |                    |                 |                      |              |       | bit 0 |

| oit 13     |      |                 | h Droar   | om Mom                      |          | ha Drat  | ection bit        |                    |                 |                      |              |       |       |

| л 15       |      | 1 = Code        |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                 | •         | ocations                    | code-p   | rotecte  | ed                |                    |                 |                      |              |       |       |

| oit 12     |      | ССРМХ           | : CCP1    | Pin Selec                   | tion bit | :        |                   |                    |                 |                      |              |       |       |

|            |      |                 |           | on on RB                    |          |          |                   |                    |                 |                      |              |       |       |

| oit 11     |      |                 |           | on on RB                    |          | odo bit  |                   |                    |                 |                      |              |       |       |

| אנוו       |      |                 |           | uit Debug<br>bugger d       |          |          | and RB7 a         | are gener          | al purpos       | e I/O pins           |              |       |       |

|            |      |                 |           |                             |          |          |                   |                    |                 | e debugger           |              |       |       |

| oit 10-9   |      | WRT1:W          | VRTO: F   | lash Prog                   | gram M   | emory    | Write Ena         | able bits          |                 |                      |              |       |       |

|            |      | For PIC1        |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 11 = Wri        |           |                             |          |          |                   |                    | na a difi a d l |                      | a a vatura l |       |       |

|            |      |                 |           | F write-p                   |          |          | 10 to 03FF        | may be             | moainea i       | by EECON             | CONTROL      |       |       |

|            |      | For PIC1        |           | 1 11110                     |          | Ju       |                   |                    |                 |                      |              |       |       |

|            |      | 11 = Wri        | ite prote |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                 |           |                             |          |          |                   |                    |                 | ified by EE          |              |       |       |

|            |      |                 |           |                             |          |          |                   |                    |                 | ified by EE          |              |       |       |

| oit 8      |      |                 |           | lemory C                    |          |          |                   | ////////           | y 50 moa        |                      |              |       |       |

|            |      | 1 = Code        |           | •                           |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                 |           | mory loca                   |          | -        |                   |                    |                 |                      |              |       |       |

| oit 7      |      |                 |           | e Progra                    |          |          |                   | _                  |                 |                      |              |       |       |

|            |      |                 |           |                             |          |          | ow-Voltag         |                    |                 | abled<br>ed for prog | rammina      |       |       |

| oit 6      |      |                 |           | -out Rese                   |          |          |                   |                    |                 |                      | lanning      |       |       |

|            |      | 1 = BOR         |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = BOR         | t disable | d                           |          |          |                   |                    |                 |                      |              |       |       |

| oit 5      |      |                 |           |                             |          | -        | Select bit        |                    |                 |                      |              |       |       |

|            |      |                 |           | VPP pin fu                  |          |          | LR<br>tal I/O, MC | <u>`I P</u> interr | ally tied t     | ם ער                 |              |       |       |

| oit 3      |      |                 | _         | er-up Tim                   |          | •        |                   |                    | ially lieu l    | 0 000                |              |       |       |

| ло         |      | 1 = PWF         |           | •                           |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = PWF         |           |                             |          |          |                   |                    |                 |                      |              |       |       |

| oit 2      |      |                 |           | dog Time                    | r Enab   | le bit   |                   |                    |                 |                      |              |       |       |

|            |      | 1 = WDT         |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = WDT         |           |                             |          | ntion hi | <b>to</b>         |                    |                 |                      |              |       |       |

| oit 4, 1-0 |      |                 |           | : Oscillato<br>scillator: ( |          |          | n on RA6/         | OSC2/CI            | KO nin          |                      |              |       |       |

|            |      |                 |           |                             |          |          | on on RA6         |                    |                 |                      |              |       |       |

|            |      | 101 = <b>IN</b> | ITRC os   | cillator; C                 | LKO fu   | unction  | on RA6/C          | DSC2/CL            | KO pin ar       | nd port I/O f        | function o   | n     |       |

|            |      |                 |           | 1/CLKI p                    |          | functio  | n on hoth         | DAG/OS             |                 | pin and RA           | 17/0901/     |       |       |

|            |      |                 |           |                             |          |          | 46/OSC2/          |                    |                 | pin anu rv           | 47/0301/     |       |       |

|            |      | 010 = H         | S oscilla | tor                         |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 001 = X         |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 000 = LF        | - oscilla | lor                         |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                 |           |                             |          | ramm     |                   |                    |                 |                      |              |       |       |

#### Legend:

R = Readable bitP = Programmable bitU = Unimplemented bit, read as '1'-n = Value when device is unprogrammedu = Unchanged from programmed state

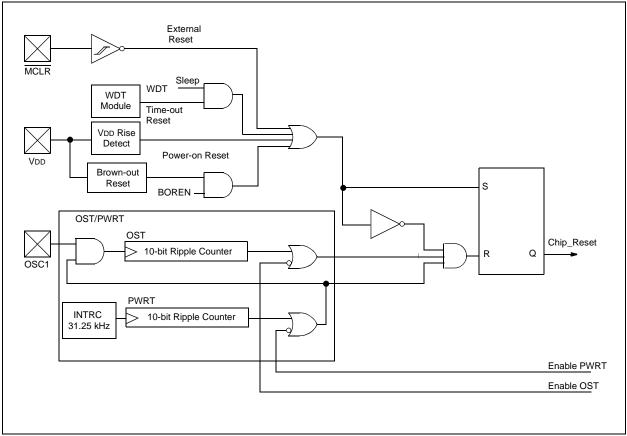

#### 12.2 Reset

The PIC16F818/819 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset during normal operation

- WDT wake-up during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 12-3. These bits are used in software to determine the nature of the Reset. Upon a POR, BOR wake-up from Sleep, the CPU requires or approximately 5-10 µs to become ready for code execution. This delay runs in parallel with any other timers. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 12-1.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### **FIGURE 12-9:** WAKE-UP FROM SLEEP THROUGH INTERRUPT

| OSC1 /<br>CLKO <sup>(4)</sup> //    | 3   Q4 ; Q1   Q2   Q3   Q4 ; Q1<br>/////////_ |                    |              | . Q1  Q2  Q3  Q4<br>          | Q1  Q2  Q3  Q4<br>    | Q1 Q2 Q3 Q4; |

|-------------------------------------|-----------------------------------------------|--------------------|--------------|-------------------------------|-----------------------|--------------|

| INT pin                             | <u> </u>                                      |                    | I            | 1                             | 1                     |              |

| INTF Flag<br>(INTCON<1>)            |                                               | \ <u>+</u>         |              | Interrupt Latency<br>(Note 2) |                       |              |

| GIE bit<br>(INTCON<7>)              | i i i i i i i i i i i i i i i i i i i         | cessor in<br>Sleep |              |                               | ,<br>,<br>,<br>,<br>, | I            |

| INSTRUCTION FLOW                    |                                               | 1                  | l<br>I       | I I                           | 1                     | 1            |

| PC Y PC                             | X PC + 1 X                                    | PC + 2             | X PC + 2     | X PC + 2                      | 0004h                 | X 0005h      |

| Fetched Inst(PC) = S                | Sleep Inst(PC + 1)                            |                    | Inst(PC + 2) | 1<br>1<br>1                   | Inst(0004h)           | Inst(0005h)  |

| Instruction<br>Executed { Inst(PC - | - 1) Sleep                                    |                    | Inst(PC + 1) | Dummy Cycle                   | Dummy Cycle           | Inst(0004h)  |

| Note 1 XT HS or IP                  | Oscillator mode assumed                       |                    |              |                               |                       |              |

2: TOST = 1024 TOSC (drawing not to scale). This delay will not be there for RC Oscillator mode.

GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line. 3:

4: CLKO is not available in these oscillator modes but shown here for timing reference.

#### 12.14 In-Circuit Debugger

When the DEBUG bit in the Configuration Word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-6 shows which features are consumed by the background debugger.

| TABLE 12-6: DEB | JGGER RESOURCES |

|-----------------|-----------------|

|-----------------|-----------------|

| I/O pins       | RB6, RB7                                   |

|----------------|--------------------------------------------|

| Stack          | 1 level                                    |

| Program Memory | Address 0000h must be NOP                  |

|                | Last 100h words                            |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB-0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

#### 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 12.16 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the four Least Significant bits of the ID location are used.

# 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDWF            | AND W with f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                     |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

### 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

|                         | 8 <b>18/819</b><br>strial)            |     | i <b>rd Ope</b> i<br>ing temp | •     | •         | ss otherwise stated $A \leq +85^{\circ}C$ for indust                                      |                                                  |

|-------------------------|---------------------------------------|-----|-------------------------------|-------|-----------|-------------------------------------------------------------------------------------------|--------------------------------------------------|

| <b>PIC16F8</b><br>(Indu | <b>18/819</b><br>strial, Extended)    |     | ird Oper<br>ing temp          | -     | -40°C ≤ T | as otherwise stated<br>$A \le +85^{\circ}C$ for indust<br>$A \le +125^{\circ}C$ for exter | rial                                             |

| Param<br>No.            | Device                                | Тур | Max                           | Units |           | Condit                                                                                    | ions                                             |

|                         | Supply Current (IDD) <sup>(2,3)</sup> |     |                               |       |           |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 8   | 20                            | μA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 7   | 15                            | μA    | +25°C     | VDD = 2.0V                                                                                |                                                  |

|                         |                                       | 7   | 15                            | μA    | +85°C     |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 16  | 30                            | μA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 14  | 25                            | μΑ    | +25°C     | VDD = 3.0V                                                                                | Fosc = 31.25 kHz                                 |

|                         |                                       | 14  | 25                            | μΑ    | +85°C     |                                                                                           | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |

|                         | All devices                           | 32  | 40                            | μΑ    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 29  | 35                            | μΑ    | +25°C     |                                                                                           |                                                  |

|                         |                                       | 29  | 35                            | μA    | +85°C     | VDD = 5.0V                                                                                |                                                  |

|                         | Extended devices                      | 35  | 45                            | μA    | +125°C    |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 132 | 160                           | μA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 126 | 155                           | μA    | +25°C     | VDD = 2.0V                                                                                |                                                  |

|                         |                                       | 126 | 155                           | μA    | +85°C     |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 260 | 310                           | μA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 230 | 300                           | μA    | +25°C     | VDD = 3.0V                                                                                | Fosc = 1 MHz                                     |

|                         |                                       | 230 | 300                           | μA    | +85°C     |                                                                                           | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |

|                         | All devices                           | 560 | 690                           | μA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 500 | 650                           | μΑ    | +25°C     |                                                                                           |                                                  |

|                         |                                       | 500 | 650                           | μΑ    | +85°C     | VDD = 5.0V                                                                                |                                                  |

|                         | Extended devices                      | 570 | 710                           | μΑ    | +125°C    |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 310 | 420                           | μΑ    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 300 | 410                           | μΑ    | +25°C     | VDD = 2.0V                                                                                |                                                  |

|                         |                                       | 300 | 410                           | μA    | +85°C     |                                                                                           |                                                  |

|                         | PIC16LF818/819                        | 550 | 650                           | μΑ    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 530 | 620                           | μΑ    | +25°C     | VDD = 3.0V                                                                                | Fosc = 4 MHz                                     |

|                         |                                       | 530 | 620                           | μΑ    | +85°C     |                                                                                           | ( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |

|                         | All devices                           | 1.2 | 1.5                           | mA    | -40°C     |                                                                                           |                                                  |

|                         |                                       | 1.1 | 1.4                           | mA    | +25°C     | VDD = 5.0V                                                                                |                                                  |

|                         |                                       | 1.1 | 1.4                           | mA    | +85°C     | VDU = 5.0V                                                                                |                                                  |

|                         | Extended devices                      | 1.3 | 1.6                           | mA    | +125°C    |                                                                                           |                                                  |

**Legend:** Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

#### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| DC CHA       | ARACTI | ERISTICS                              | Operating temp | perature    | -40°<br>40°<br>range as | C ≤ TA<br>C ≤ TA<br>descril | ess otherwise stated)<br>≤ +85°C for industrial<br>≤ +125°C for extended<br>bed in Section 15.1 "DC |

|--------------|--------|---------------------------------------|----------------|-------------|-------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                        | Min            | Тур†        | Max                     | Units                       | Conditions                                                                                          |

|              | Vol    | Output Low Voltage                    |                |             |                         |                             |                                                                                                     |

| D080         |        | I/O ports                             | —              | —           | 0.6                     | V                           | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                        |

| D083         |        | OSC2/CLKO<br>(RC oscillator config)   | —              | —           | 0.6                     | V                           | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                                                        |

|              | Vон    | Output High Voltage                   |                |             |                         |                             |                                                                                                     |

| D090         |        | I/O ports <b>(Note 3)</b>             | Vdd - 0.7      | —           | —                       | V                           | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                       |

| D092         |        | OSC2/CLKO<br>(RC oscillator config)   | Vdd - 0.7      | —           | —                       | V                           | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                                                       |

|              |        | Capacitive Loading Specs on           | Output Pins    |             |                         |                             |                                                                                                     |

| D100         | Cosc2  | OSC2 pin                              | _              | —           | 15                      | pF                          | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1                              |

| D101         | Сю     | All I/O pins and OSC2<br>(in RC mode) | —              | —           | 50                      | pF                          |                                                                                                     |

| D102         | Св     | SCL, SDA in I <sup>2</sup> C™ mode    |                | —           | 400                     | pF                          |                                                                                                     |

|              |        | Data EEPROM Memory                    |                |             |                         |                             |                                                                                                     |

| D120         | ED     | Endurance                             | 100K           | 1M          | _                       | E/W                         | -40°C to +85°C                                                                                      |

|              |        |                                       | 10K            | 100K        | _                       | E/W                         | +85°C to +125°C                                                                                     |

| D121         | Vdrw   | VDD for read/write                    | Vmin           | _           | 5.5                     | V                           | Using EECON to read/write,<br>VMIN = min. operating<br>voltage                                      |

| D122         | TDEW   | Erase/write cycle time                |                | 4           | 8                       | ms                          |                                                                                                     |

|              |        | Program Flash Memory                  |                |             |                         |                             |                                                                                                     |

| D130         | Eр     | Endurance                             | 10K<br>1K      | 100K<br>10K | _                       | E/W<br>E/W                  | -40°C to +85°C<br>+85°C to +125°C                                                                   |

| D131         | Vpr    | VDD for read                          | VMIN           | _           | 5.5                     | V                           |                                                                                                     |

| D132A        |        | VDD for erase/write                   | Vmin           | -           | 5.5                     | V                           | Using EECON to read/write,<br>VMIN = min. operating<br>voltage                                      |

| D133         | Тре    | Erase cycle time                      | —              | 2           | 4                       | ms                          |                                                                                                     |

| D134         | TPW    | Write cycle time                      | —              | 2           | 4                       | ms                          |                                                                                                     |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

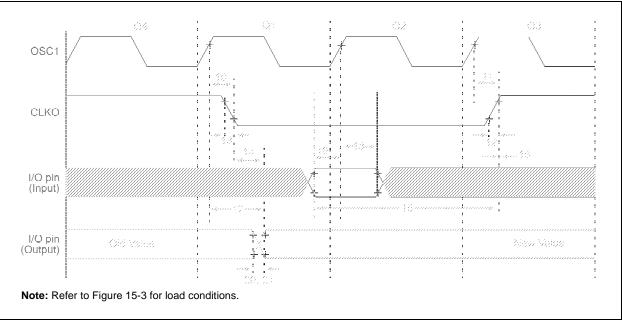

| TABLE 15-2: | CLKO AND I/O TIMING REQUIREMENTS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Param<br>No. | Symbol   | Characterist                         | ic                      | Min        | Тур† | Мах          | Units | Conditions |

|--------------|----------|--------------------------------------|-------------------------|------------|------|--------------|-------|------------|

| 10*          | TosH2ckL | OSC1 $\uparrow$ to CLKO $\downarrow$ |                         | _          | 75   | 200          | ns    | (Note 1)   |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                     |                         | _          | 75   | 200          | ns    | (Note 1)   |

| 12*          | ТскR     | CLKO Rise Time                       |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 13*          | ТскF     | CLKO Fall Time                       |                         | _          | 35   | 100          | ns    | (Note 1)   |

| 14*          | TCKL2IOV | CLKO ↓ to Port Out Valid             |                         |            | _    | 0.5 TCY + 20 | ns    | (Note 1)   |

| 15*          | ТюV2скН  | Port In Valid before CLKO 1          |                         | Tosc + 200 | _    | —            | ns    | (Note 1)   |

| 16*          | TCKH2IOI | Port In Hold after CLKO ↑            |                         | 0          | —    | —            | ns    | (Note 1)   |

| 17*          | TosH2IoV | OSC1 ↑ (Q1 cycle) to Port Out        | Valid                   | _          | 100  | 255          | ns    |            |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to Port            | PIC16F818/819           | 100        | _    | —            | ns    |            |