Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 20MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                    |

| Data Converters            | A/D 5x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f819t-i-sotsl |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                            | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type      | Buffer<br>Type                       | Description                                                                                                                                              |

|-----------------------------------------------------|-----------------------|--------------|-------------|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                       |              |             |                    |                                      | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up or<br>all inputs.                                       |

| RB0/INT<br>RB0<br>INT                               | 6                     | 7            | 7           | I/O<br>I           | TTL<br>ST <sup>(1)</sup>             | Bidirectional I/O pin.<br>External interrupt pin.                                                                                                        |

| RB1/SDI/SDA<br>RB1<br>SDI<br>SDA                    | 7                     | 8            | 8           | I/O<br>I<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>SPI data in.<br>I <sup>2</sup> C™ data.                                                                                        |

| RB2/SDO/CCP1<br>RB2<br>SDO<br>CCP1                  | 8                     | 9            | 9           | I/O<br>O<br>I/O    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>SPI data out.<br>Capture input, Compare output, PWM output.                                                                    |

| RB3/CCP1/PGM<br>RB3<br>CCP1<br>PGM                  | 9                     | 10           | 10          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin.<br>Capture input, Compare output, PWM output.<br>Low-Voltage ICSP™ Programming enable pir                                         |

| RB4/SCK/SCL<br>RB4<br>SCK<br>SCL                    | 10                    | 11           | 12          | I/O<br>I/O<br>I    | TTL<br>ST<br>ST                      | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI<br>Synchronous serial clock input for I <sup>2</sup> C. |

| RB5/SS<br>RB5<br>SS                                 | 11                    | 12           | 13          | I/O<br>I           | TTL<br>TTL                           | Bidirectional I/O pin. Interrupt-on-change pin.<br>Slave select for SPI in Slave mode.                                                                   |

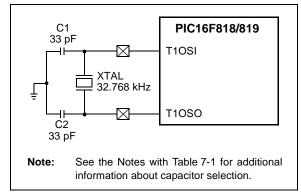

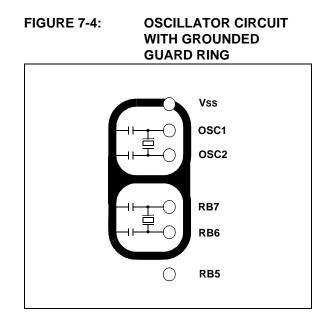

| RB6/T1OSO/T1CKI/PGC<br>RB6<br>T1OSO<br>T1CKI<br>PGC | 12                    | 13           | 15          | I/O<br>O<br>I<br>I | TTL<br>ST<br>ST<br>ST <sup>(2)</sup> | Interrupt-on-change pin.<br>Timer1 Oscillator output.<br>Timer1 clock input.<br>In-circuit debugger and ICSP programming<br>clock pin.                   |

| RB7/T1OSI/PGD<br>RB7<br>T1OSI<br>PGD                | 13                    | 14           | 16          | I/O<br>I<br>I      | TTL<br>ST<br>ST <sup>(2)</sup>       | Interrupt-on-change pin.<br>Timer1 oscillator input.<br>In-circuit debugger and ICSP programming<br>data pin.                                            |

| Vss                                                 | 5                     | 5, 6         | 3, 5        | Р                  | _                                    | Ground reference for logic and I/O pins.                                                                                                                 |

| Vdd                                                 | 14                    | 15, 16       | 17, 19      | Р                  | -                                    | Positive supply for logic and I/O pins.                                                                                                                  |

# TABLE 1-2: PIC16F818/819 PINOUT DESCRIPTIONS (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F818/819. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F818 device's 128 bytes of data EEPROM memory have the address range of 00h-7Fh and the PIC16F819 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in Section 3.0 "Data EEPROM and Flash Program Memory".

Additional information on device memory may be found in the *"PIC<sup>®</sup> Mid-Range Reference Manual"* (DS33023).

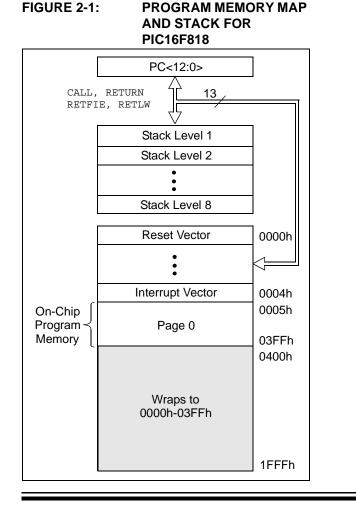

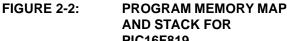

# 2.1 **Program Memory Organization**

The PIC16F818/819 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F818, the first 1K x 14 (0000h-03FFh) is physically implemented (see Figure 2-1). For the PIC16F819, the first 2K x 14 is located at 0000h-07FFh (see Figure 2-2). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

# 2.2 Data Memory Organization

The data memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank for code reduction and quicker access (e.g., the Status register is in Banks 0-3).

| Note: | EEPROM data memory description can be found in Section 3.0 "Data EEPROM and |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

|       | Flash Program Memory" of this data sheet.                                   |  |  |  |  |  |  |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register, FSR.

```

FIGURE 2-3:

```

## PIC16F818 REGISTER FILE MAP

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ddress      |                                | Address     | [                   | Address      |                                   | ddre       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|-------------|---------------------|--------------|-----------------------------------|------------|

| Indirect addr.(*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00h         | Indirect addr.(*)              | 80h         | Indirect addr.(*)   | 100h         | Indirect addr.(*)                 | 180        |

| TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01h         | OPTION_REG                     | 81h         | TMR0                | 101h         | OPTION_REG                        | 181        |

| PCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 02h         | PCL                            | 82h         | PCL                 | 102h         | PCL                               | 182        |

| STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 03h         | STATUS                         | 83h         | STATUS              | 103h         | STATUS                            | 183        |

| FSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 04h         | FSR                            | 84h         | FSR                 | 104h         | FSR                               | 184        |

| PORTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 05h         | TRISA                          | 85h         |                     | 105h         |                                   | 185        |

| PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 06h         | TRISB                          | 86h         | PORTB               | 106h         | TRISB                             | 186        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 07h         |                                | 87h         |                     | 107h         |                                   | 187        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 08h         |                                | 88h         |                     | 108h<br>109h |                                   | 188        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 09h<br>0Ah  |                                | 89h         | PCLATH              | 1091<br>10Ah |                                   | 189        |

| PCLATH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0An<br>0Bh  | PCLATH                         | 8Ah         | INTCON              | 10An<br>10Bh | PCLATH                            | 18/        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0Бh<br>0Ch  |                                | 8Bh         |                     | 10Dh         |                                   | 18E        |

| PIR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | PIE1<br>PIE2                   | 8Ch         | EEDATA<br>EEADR     | 10Ch<br>10Dh | EECON1                            | 180        |

| PIR2<br>TMR1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0Dh<br>0Eh  |                                | 8Dh         |                     | 10Dh<br>10Eh | EECON2<br>Reserved <sup>(1)</sup> | 18[        |

| TMR1L<br>TMR1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0En<br>0Fh  | PCON<br>OSCCON                 | 8Eh<br>8Fh  | EEDATH<br>EEADRH    | 10En<br>10Fh | Reserved <sup>(1)</sup>           | 18E<br>18F |

| TICON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10h         | OSCTUNE                        |             | EEADKI              | 110h         | Reserved                          | 186        |

| TMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1011<br>11h | USCIDINE                       | 90h<br>91h  |                     | 11011        |                                   | 190        |

| T2CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12h         | PR2                            | 91h<br>92h  |                     |              |                                   |            |

| SSPBUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13h         | SSPADD                         | 9211<br>93h |                     |              |                                   |            |

| SSPCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14h         | SSPSTAT                        | 931<br>94h  |                     |              |                                   |            |

| CCPR1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15h         |                                | 9411<br>95h |                     |              |                                   |            |

| CCPR1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16h         |                                | 96h         |                     |              |                                   |            |

| CCP1CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17h         |                                | 97h         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18h         |                                | 98h         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19h         |                                | 99h         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1Ah         |                                | 9Ah         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1Bh         |                                | 9Bh         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1Ch         |                                | 9Ch         |                     |              |                                   |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1Dh         |                                | 9Dh         |                     |              |                                   |            |

| ADRESH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Eh         | ADRESL                         | 9Eh         |                     |              |                                   |            |

| ADCON0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Fh         | ADCON1                         | 9Fh         |                     | 11Fh         |                                   | 19F        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20h         | General<br>Purpose<br>Register | A0h         |                     | 120h         |                                   | 1A)        |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | 32 Bytes                       | BFh         |                     |              |                                   |            |

| Purpose<br>Register<br>96 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | Accesses<br>40h-7Fh            | C0h         | Accesses<br>20h-7Fh |              | Accesses<br>20h-7Fh               |            |

| Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7Fh         | Bank 1                         | FFh         | Bank 2              | 17Fh         | Bank 3                            | 1FF        |

| <ul> <li>Dank 1</li> <li>Dank 2</li> <li>Dank 3</li> <li>Dank 3</li> <li>Dank 4</li> <li>Dank 4</li> <li>Dank 5</li> <li>Dank 5</li></ul> |             |                                |             |                     |              |                                   |            |

### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

|   | U-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---|-------|-------|-----|-----|-------|--------|--------|--------|

|   | —     | ADIF  | —   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| - | bit 7 |       |     |     |       |        |        | bit 0  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                                                                                                                                          |

|         | 1 = An A/D conversion completed                                                                                                                                                                                                                                                                 |