Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf818-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

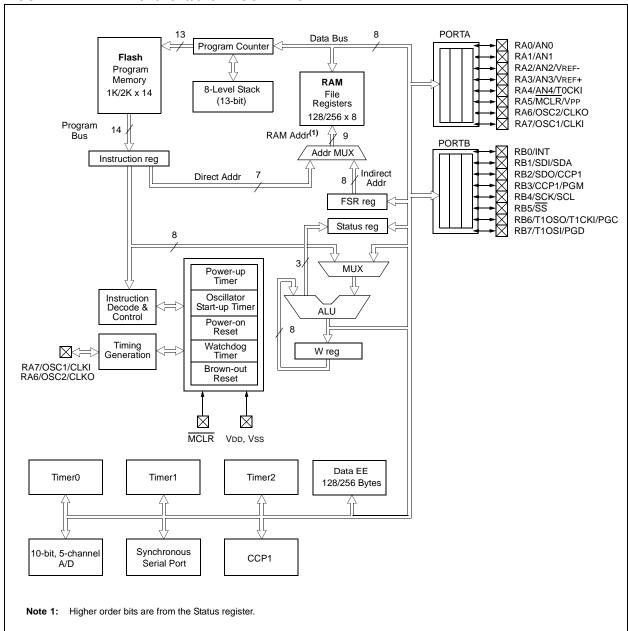

FIGURE 1-1: PIC16F818/819 BLOCK DIAGRAM

#### 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F818/819. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F818 device's 128 bytes of data EEPROM memory have the address range of 00h-7Fh and the PIC16F819 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in **Section 3.0 "Data EEPROM and Flash Program Memory**".

Additional information on device memory may be found in the "PIC® Mid-Range Reference Manual" (DS33023).

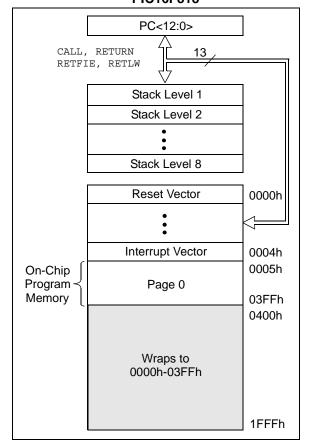

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR

PIC16F818

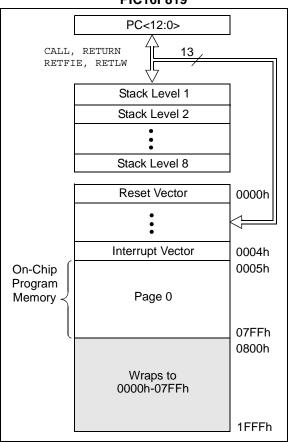

#### 2.1 Program Memory Organization

The PIC16F818/819 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F818, the first 1K x 14 (0000h-03FFh) is physically implemented (see Figure 2-1). For the PIC16F819, the first 2K x 14 is located at 0000h-07FFh (see Figure 2-2). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-2: PROGRAM MEMORY MAP AND STACK FOR PIC16F819

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

**Note:** Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| U-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-----|-----|-------|--------|--------|--------|

| _     | ADIE  | _   | _   | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |     |     |       |        |        | bit 0  |

bit 7 Unimplemented: Read as '0' bit 6 ADIE: A/D Converter Interrupt Enable bit 1 = Enables the A/D converter interrupt 0 = Disables the A/D converter interrupt bit 5-4 Unimplemented: Read as '0' bit 3 SSPIE: Synchronous Serial Port Interrupt Enable bit 1 = Enables the SSP interrupt 0 = Disables the SSP interrupt bit 2 **CCP1IE:** CCP1 Interrupt Enable bit 1 = Enables the CCP1 interrupt 0 = Disables the CCP1 interrupt bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0

TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt0 = Disables the TMR1 overflow interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

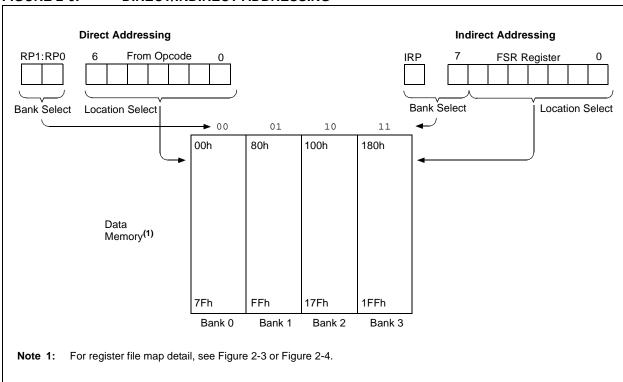

#### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

#### 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

#### **EXAMPLE 3-3: FLASH PROGRAM READ**

```

BANKSEL EEADRH

; Select Bank of EEADRH

MOVF

ADDRH, W

MOVWF

EEADRH

; MS Byte of Program

; Address to read

MOVF

ADDRL, W

; LS Byte of Program

MOVWF

EEADR

; Address to read

; Select Bank of EECON1

BANKSEL EECON1

BSF

EECON1, EEPGD; Point to PROGRAM

; memory

; EE Read

BSF

EECON1, RD

MOP

; Any instructions

; here are ignored as

NOP

; program memory is

; read in second cycle

; after BSF EECON1,RD

; Select Bank of EEDATA

BANKSEL EEDATA

MOVF

EEDATA, W

; DATAL = EEDATA

MOVWF

DATAL

; DATAH = EEDATH

MOVF

EEDATH, W

MOVWF

DATAH

```

#### 3.6 Erasing Flash Program Memory

The minimum erase block is 32 words. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the micro-controller itself, a block of 32 words of program memory is erased. The Most Significant 11 bits of the EEADRH:EEADR point to the block being erased. EEADR< 4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the erase takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

### 3.6.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- Load EEADRH:EEADR with address of row being erased.

- Set EEPGD bit to point to program memory; set WREN bit to enable writes and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- Set the WR bit. This will begin the row erase cycle.

- The CPU will stall for duration of the erase.

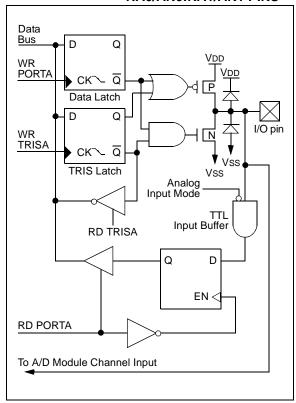

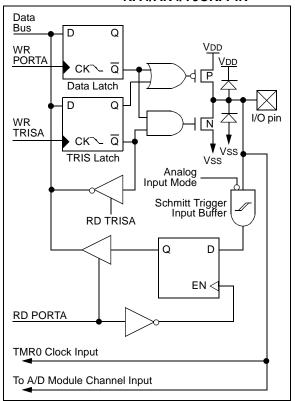

FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

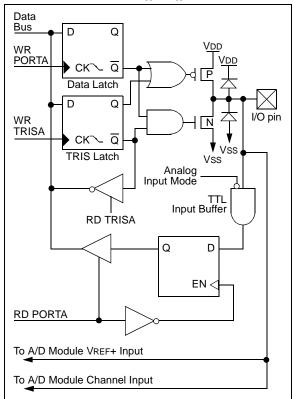

FIGURE 5-2: BLOCK DIAGRAM OF RA3/AN3/VREF+ PIN

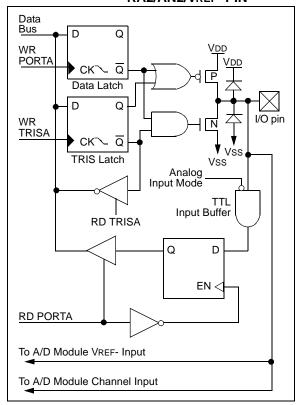

FIGURE 5-3: BLOCK DIAGRAM OF RA2/AN2/VREF- PIN

FIGURE 5-4: BLOCK DIAGRAM OF RA4/AN4/T0CKI PIN

TABLE 5-3: PORTB FUNCTIONS

| Name                        | Bit#  | Buffer                | Function                                                                                                                                                                    |  |

|-----------------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RB0/INT                     | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                                                  |  |

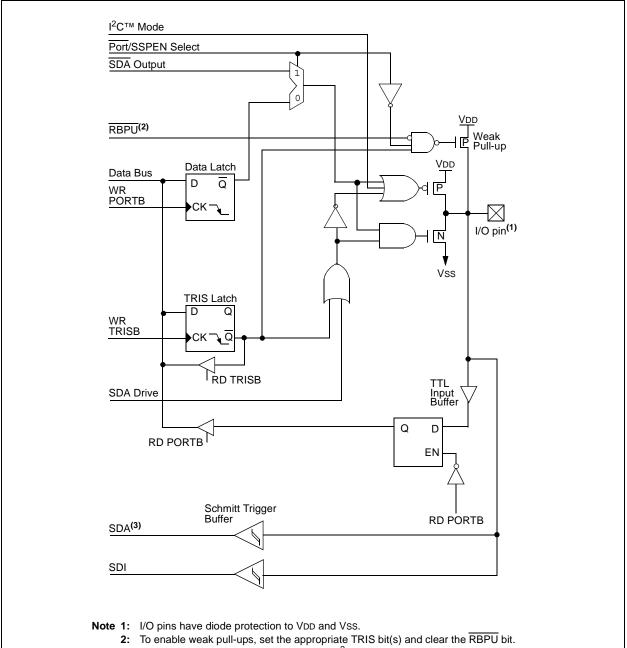

| RB1/SDI/SDA                 | bit 1 | TTL/ST <sup>(5)</sup> | Input/output pin, SPI data input pin or I <sup>2</sup> C™ data I/O pin. Internal software programmable weak pull-up.                                                        |  |

| RB2/SDO/CCP1                | bit 2 | TTL/ST <sup>(4)</sup> | Input/output pin, SPI data output pin or Capture input/Compare output/PWM output pin. Internal software programmable weak pull-up.                                          |  |

| RB3/CCP1/PGM <sup>(3)</sup> | bit 3 | TTL/ST <sup>(2)</sup> | Input/output pin, Capture input/Compare output/PWM output pin or programming in LVP mode. Internal software programmable weak pull-up.                                      |  |

| RB4/SCK/SCL                 | bit 4 | TTL/ST <sup>(5)</sup> | Input/output pin or SPI and I <sup>2</sup> C clock pin (with interrupt-on-change). Internal software programmable weak pull-up.                                             |  |

| RB5/SS                      | bit 5 | TTL                   | Input/output pin or SPI slave select pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                           |  |

| RB6/T1OSO/T1CKI/<br>PGC     | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator output pin, Timer1 clock input pin or serial programming clock (with interrupt-on-change). Internal software programmable weak pull-up. |  |

| RB7/T1OSI/PGD               | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin, Timer1 oscillator input pin or serial programming data (with interrupt-on-change). Internal software programmable weak pull-up.                           |  |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

- Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: Low-Voltage ICSP™ Programming (LVP) is enabled by default which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 18-pin mid-range devices.

- **4:** This buffer is a Schmitt Trigger input when configured for CCP or SSP mode.

- 5: This buffer is a Schmitt Trigger input when configured for SPI or I<sup>2</sup>C mode.

TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7                         | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|------------|-------------------------------|--------|-------|-------|-----------|-----------|-------|-------|----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7                           | RB6    | RB5   | RB4   | RB3       | RB2       | RB1   | RB0   | xxxx xxxx            | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB Data Direction Register |        |       |       | 1111 1111 | 1111 1111 |       |       |                      |                                 |

| 81h, 181h | OPTION_REG | RBPU                          | INTEDG | T0CS  | T0SE  | PSA       | PS2       | PS1   | PS0   | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

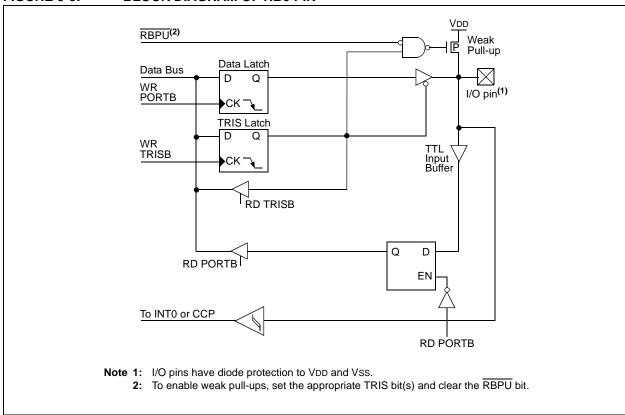

FIGURE 5-8: BLOCK DIAGRAM OF RB0 PIN

FIGURE 5-9: BLOCK DIAGRAM OF RB1 PIN

**3:** The SDA Schmitt Trigger conforms to the I<sup>2</sup>C specification.

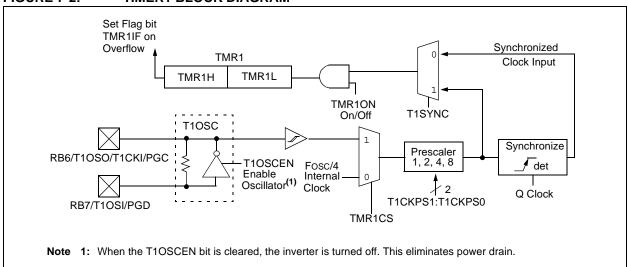

#### 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 Interrupt Enable bit, TMR1IE (PIE1<0>).

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

#### 7.1 Timer1 Operation

Timer1 can operate in one of three modes:

- · as a timer

- · as a synchronous counter

- · as an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP1 module as the special event trigger (see **Section 9.1 "Capture Mode"**). Register 7-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB6/T1OSO/T1CKI/PGC and RB7/T1OSI/PGD pins become inputs. That is, the TRISB<7:6> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

#### REGISTER 7-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| _ | U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|---|-------|-----|---------|---------|---------|--------|--------|--------|

|   | _     | _   | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N |

|   | bit 7 |     |         |         |         |        |        | bit 0  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value

00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled

0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

TMR1CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RB6/T1OSO/T1CKI/PGC (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR10N: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | d bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

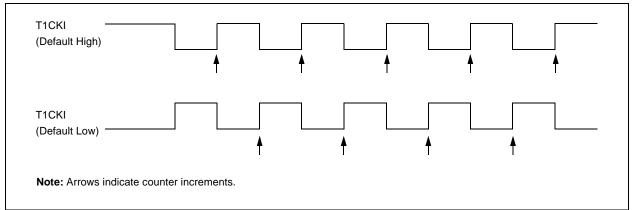

#### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set, or on pin RB6/T1OSO/T1CKI/PGC when bit T1OSCEN is cleared.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 7-1: TIMER1 INCREMENTING EDGE

#### FIGURE 7-2: TIMER1 BLOCK DIAGRAM

#### REGISTER 8-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|-------|---------|---------|---------|---------|--------|---------|---------|

| _     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |         |         |         |         |        |         | bit 0   |

bit 7 Unimplemented: Read as '0'

bit 6-3 TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits

0000 = 1:1 Postscale 0001 = 1:2 Postscale 0010 = 1:3 Postscale

•

.

1111 = 1:16 Postscale

bit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on 0 = Timer2 is off

bit 1-0 T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits

00 =Prescaler is 1 01 =Prescaler is 4 1x =Prescaler is 16

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name                       | Bit 7  | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------|----------------------------|--------|-----------------------|---------|---------|---------|-----------|-----------|---------|----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                     | GIE    | PEIE                  | TMR0IE  | INTE    | RBIE    | TMR0IF    | INTF      | RBIF    | 0000 000x            | 0000 000u                       |

| 0Ch                     | PIR1                       | _      | ADIF                  |         | _       | SSPIF   | CCP1IF    | TMR2IF    | TMR1IF  | -0 0000              | -0 0000                         |

| 8Ch                     | PIE1                       | _      | ADIE                  | -       | _       | SSPIE   | CCP1IE    | TMR2IE    | TMR1IE  | -0 0000              | -0 0000                         |

| 11h                     | TMR2                       | Timer2 | imer2 Module Register |         |         |         |           |           |         | 0000 0000            | 0000 0000                       |

| 12h                     | T2CON                      | _      | TOUTPS3               | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON    | T2CKPS1   | T2CKPS0 | -000 0000            | -000 0000                       |

| 92h                     | PR2 Timer2 Period Register |        |                       |         |         |         | 1111 1111 | 1111 1111 |         |                      |                                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

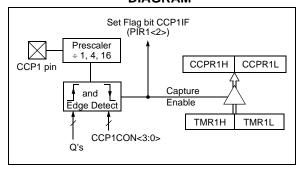

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

**Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

# FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW_CAPT_PS | ;Turn CCP module off ;Load the W reg with                                         |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

#### 12.13 Power-Down Mode (Sleep)

Power-Down mode is entered by executing a  ${\tt SLEEP}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (Status<3>) is cleared, the  $\overline{TO}$  (Status<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- Watchdog Timer wake-up (if WDT was enabled).

- Interrupt from INT pin, RB port change or a peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the Status register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- 3. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 6. A/D conversion (when A/D clock source is RC).

- 7. EEPROM write operation completion.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bit will not be cleared.

- If the interrupt occurs during or after the

execution of a SLEEP instruction, the device will

immediately wake-up from Sleep. The SLEEP

instruction will be completely executed before the

wake-up. Therefore, the WDT and WDT

postscaler will be cleared, the TO bit will be set

and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{\text{PD}}$  bit. If the  $\overline{\text{PD}}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| IORLW            | Inclusive OR Literal with W                                                                                     | MOVLW            | Move Literal to W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                 | Syntax:          | [ label ] MOVLW k                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                                             | Operands:        | $0 \leq k \leq 255$                                                                         |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                    | Operation:       | $k \rightarrow (W)$                                                                         |

| Status Affected: | Z                                                                                                               | Status Affected: | None                                                                                        |

| Description:     | The contents of the W register are ORed with the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as '0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                     | MOVWF            | Move W to f           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                       | Syntax:          | [ label ] MOVWF       |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                       | Operands:        | $0 \leq f \leq 127$   |

|                  | d ∈ [0,1]                                                                                                                                                 | Operation:       | $(W) \rightarrow (f)$ |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                  | Status Affected: | None                  |

| Status Affected: | Z                                                                                                                                                         | Description:     | Move data from W i    |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' = 0, the result is placed in the W register. If 'd' = 1, the result is placed back in register 'f'. | ·                | register 'f'.         |

| MOVF             | Move f                                                                                                                                                                                                                                                         | NOP              | No Operation  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                             | Syntax:          | [ label ] NOP |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                                                            | Operands:        | None          |

|                  | d ∈ [0,1]                                                                                                                                                                                                                                                      | Operation:       | No operation  |

| Operation:       | $(f) \rightarrow (destination)$                                                                                                                                                                                                                                | Status Affected: | None          |

| Status Affected: | Z                                                                                                                                                                                                                                                              | Description:     | No operation. |

| Description:     | The contents of register 'f' are moved to a destination dependant upon the status of 'd'. If 'd' = 0, the destination is W register. If 'd' = 1, the destination is file register 'f' itself. 'd' = 1 is useful to test a file register since status flag Z is | ·                | ·             |

affected.

register to

#### 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C® for Various Device Families

- MPASM™ Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

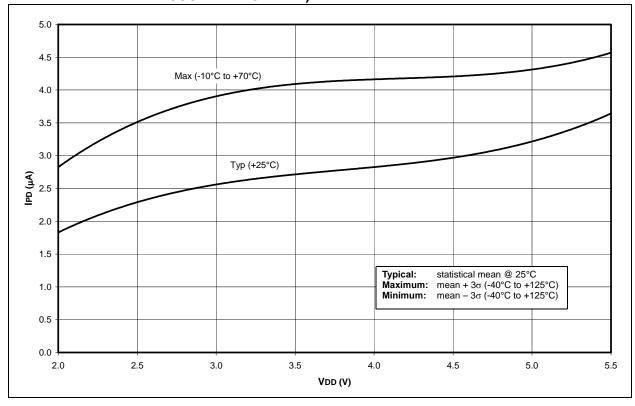

FIGURE 16-13: △IPD TIMER1 OSCILLATOR, -10°C TO +70°C (SLEEP MODE, TMR1 COUNTER DISABLED)

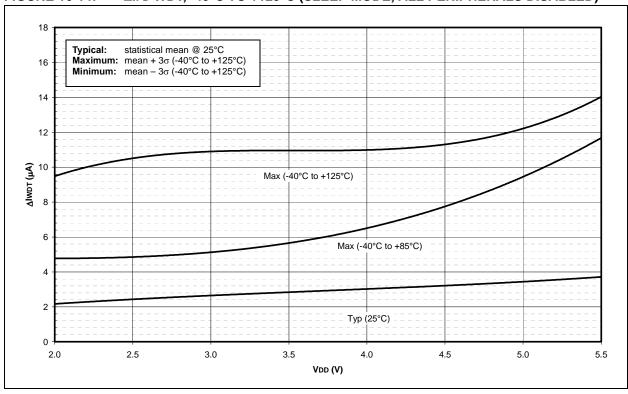

FIGURE 16-14: △IPD WDT, -40°C TO +125°C (SLEEP MODE, ALL PERIPHERALS DISABLED)

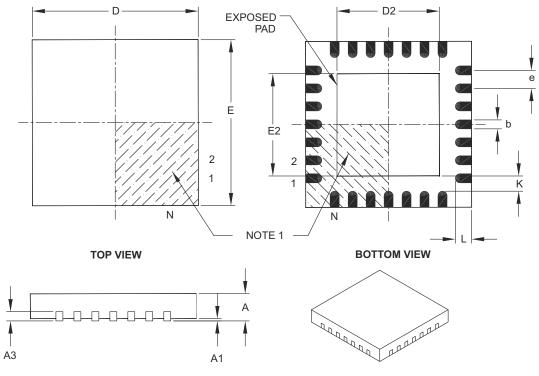

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] with 0.55 mm Contact Length

**lote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     |          | MILLIMETERS |      |  |

|------------------------|-----------|----------|-------------|------|--|

| Dimensi                | on Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N         | 28       |             |      |  |

| Pitch                  | е         | 0.65 BSC |             |      |  |

| Overall Height         | Α         | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1        | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3        | 0.20 REF |             |      |  |

| Overall Width          | E         | 6.00 BSC |             |      |  |

| Exposed Pad Width      | E2        | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D         | 6.00 BSC |             |      |  |

| Exposed Pad Length     | D2        | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b         | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L         | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | K         | 0.20     | _           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

**NOTES:**