Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf818t-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F818/819 devices. Additional information may be found in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) which may be downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F818/819 belongs to the Mid-Range family of the PIC<sup>®</sup> devices. The devices differ from each other in the amount of Flash program memory, data memory and data EEPROM (see Table 1-1). A block diagram of the devices is shown in Figure 1-1. These devices contain features that are new to the PIC16 product line:

- Internal RC oscillator with eight selectable frequencies, including 31.25 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz and 8 MHz. The INTRC can be configured as the system clock via the configuration bits. Refer to Section 4.5 "Internal Oscillator Block" and Section 12.1 "Configuration Bits" for further details.

- The Timer1 module current consumption has been greatly reduced from 20 μA (previous PIC16 devices) to 1.8 μA typical (32 kHz at 2V), which is ideal for real-time clock applications. Refer to Section 6.0 "Timer0 Module" for further details.

- The amount of oscillator selections has increased. The RC and INTRC modes can be selected with an I/O pin configured as an I/O or a clock output (Fosc/4). An external clock can be configured with an I/O pin. Refer to **Section 4.0 "Oscillator Configurations"** for further details.

# TABLE 1-1:AVAILABLE MEMORY INPIC16F818/819 DEVICES

| Device    | Program | Data    | Data    |  |

|-----------|---------|---------|---------|--|

|           | Flash   | Memory  | EEPROM  |  |

| PIC16F818 | 1K x 14 | 128 x 8 | 128 x 8 |  |

| Device    | Device Program<br>Flash |         | Data<br>EEPROM |

|-----------|-------------------------|---------|----------------|

| PIC16F819 | 2K x14                  | 256 x 8 | 256 x 8        |

There are 16 I/O pins that are user configurable on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External Interrupt

- Change on PORTB Interrupt

- Timer0 Clock Input

- Low-Power Timer1 Clock/Oscillator

- Capture/Compare/PWM

- 10-bit, 5-channel Analog-to-Digital Converter

- SPI/I<sup>2</sup>C

- MCLR (RA5) can be configured as an Input

Table 1-2 details the pinout of the devices with descriptions and details for each pin.

#### 2.2.2.1 Status Register

The Status register, shown in Register 2-1, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.

The Status register can be the destination for any instruction, as with any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the Status register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect the Z, C or DC bits from the Status register. For other instructions not affecting any status bits, see Section 13.0 "Instruction Set Summary".

| Note: | The C and DC bits operate as a borrow  |

|-------|----------------------------------------|

|       | and digit borrow bit, respectively, in |

|       | subtraction. See the SUBLW and SUBWF   |

|       | instructions for examples.             |

#### REGISTER 2-1: STATUS: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                | R/W-0                                                                                        | R/W-0                         | R-1            | R-1            | R/W-x         | R/W-x              | R/W-x       |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------|----------------|----------------|---------------|--------------------|-------------|--|

|         | IRP                                                                                                                                  | RP1                                                                                          | RP0                           | TO             | PD             | Z             | DC                 | С           |  |

|         | bit 7                                                                                                                                |                                                                                              |                               |                |                | •             |                    | bit 0       |  |

| bit 7   | 1 = Bank  2                                                                                                                          | ter Bank Sele<br>2, 3 (100h-1F<br>), 1 (00h-FFh                                              | Fh)                           | or indirect a  | ddressing)     |               |                    |             |  |

| bit 6-5 | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank<br>Each bank                                                                        | Register Banł<br>3 (180h-1FFł<br>2 (100h-17Fł<br>1 (80h-FFh)<br>0 (00h-7Fh)<br>is 128 bytes. | ר)                            | (used for dire | ect addressi   | ing)          |                    |             |  |

| bit 4   |                                                                                                                                      | out bit<br>ower-up, CLF<br>I time-out occ                                                    |                               | ion or SLEE    | o instruction  | 1             |                    |             |  |

| bit 3   |                                                                                                                                      | -down bit<br>ower-up or by<br>ecution of the                                                 |                               |                |                |               |                    |             |  |

| bit 2   | <b>Z:</b> Zero bit<br>1 = The re                                                                                                     | sult of an arit<br>sult of an arit                                                           | hmetic or log                 | ic operation   |                |               |                    |             |  |

| bit 1   | <b>DC:</b> Digit c<br>1 = A carry                                                                                                    | arry/borrow b<br>y-out from the<br>ry-out from th                                            | it (ADDWF, AI<br>4th low orde | DLW, SUBLW     | and SUBWI      |               | <sub>IS)</sub> (1) |             |  |

| bit 0   | <b>C:</b> Carry/bo<br>1 = A carry                                                                                                    | prrow bit (ADI<br>y-out from the<br>ry-out from the                                          | WF, ADDLW, S<br>Most Signifi  | SUBLW and S    | UBWF instru    | curred        |                    |             |  |

|         | <b>Note 1:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. |                                                                                              |                               |                |                |               |                    |             |  |

|         | 2:                                                                                                                                   | For rotate (R<br>bit of the sou                                                              |                               | ructions, this | s bit is loade | ed with eithe | er the high c      | r low-order |  |

|         | Legend:                                                                                                                              |                                                                                              |                               |                |                |               |                    |             |  |

|         | R = Reada                                                                                                                            | ahla hit                                                                                     | 14/ 14/                       | itable bit     |                | plemented     |                    | (           |  |

'1' = Bit is set

-n = Value at POR

x = Bit is unknown

'0' = Bit is cleared

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

-n = Value at POR

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| EN <b>2-4</b> . | FIET. PERIFHERAL INTERROFT ENABLE REGISTER T (ADDRESS 6CII)                                                   |                                            |                 |               |          |            |              |        |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|---------------|----------|------------|--------------|--------|--|--|--|

|                 | U-0                                                                                                           | R/W-0                                      | U-0             | U-0           | R/W-0    | R/W-0      | R/W-0        | R/W-0  |  |  |  |

|                 |                                                                                                               | ADIE                                       | _               | _             | SSPIE    | CCP1IE     | TMR2IE       | TMR1IE |  |  |  |

|                 | bit 7                                                                                                         |                                            |                 |               |          |            |              | bit 0  |  |  |  |

| bit 7           | Unimplemer                                                                                                    | nted: Read                                 | <b>d as</b> '0' |               |          |            |              |        |  |  |  |

| bit 6           | ADIE: A/D C                                                                                                   | onverter Ir                                | nterrupt Enab   | ole bit       |          |            |              |        |  |  |  |

|                 | 1 = Enables<br>0 = Disables                                                                                   |                                            |                 |               |          |            |              |        |  |  |  |

| bit 5-4         | 4 Unimplemented: Read as '0'                                                                                  |                                            |                 |               |          |            |              |        |  |  |  |

| bit 3           | SSPIE: Sync                                                                                                   | hronous S                                  | erial Port Int  | errupt Enable | e bit    |            |              |        |  |  |  |

|                 | 1 = Enables the SSP interrupt                                                                                 |                                            |                 |               |          |            |              |        |  |  |  |

|                 | 0 = Disables                                                                                                  | s the SSP i                                | nterrupt        |               |          |            |              |        |  |  |  |

| bit 2           | CCP1IE: CC                                                                                                    | P1 Interru                                 | ot Enable bit   |               |          |            |              |        |  |  |  |

|                 | 1 = Enables the CCP1 interrupt                                                                                |                                            |                 |               |          |            |              |        |  |  |  |

|                 | 0 = Disables the CCP1 interrupt                                                                               |                                            |                 |               |          |            |              |        |  |  |  |

| bit 1           | TMR2IE: TM                                                                                                    |                                            |                 |               | bit      |            |              |        |  |  |  |

|                 | 1 = Enables the TMR2 to PR2 match interrupt                                                                   |                                            |                 |               |          |            |              |        |  |  |  |

| <b>h</b> :+ 0   | 0 = Disables the TMR2 to PR2 match interrupt                                                                  |                                            |                 |               |          |            |              |        |  |  |  |

| bit 0           |                                                                                                               | TMR1IE: TMR1 Overflow Interrupt Enable bit |                 |               |          |            |              |        |  |  |  |

|                 | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |                                            |                 |               |          |            |              |        |  |  |  |

|                 |                                                                                                               |                                            |                 |               |          |            |              |        |  |  |  |

|                 | Legend:                                                                                                       |                                            |                 |               |          |            |              |        |  |  |  |

|                 | R = Readab                                                                                                    | ole bit                                    | W = W           | Vritable bit  | U = Unin | nplemented | bit, read as | ʻ0'    |  |  |  |

|                 |                                                                                                               |                                            |                 |               |          |            |              |        |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

# PIC16F818/819

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

|   | U-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---|-------|-------|-----|-----|-------|--------|--------|--------|

|   | —     | ADIF  | —   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| - | bit 7 |       |     |     |       |        |        | bit 0  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                                                                                                                                          |

|         | 1 = An A/D conversion completed                                                                                                                                                                                                                                                                 |

|         | <ul> <li>The A/D conversion is not complete</li> </ul>                                                                                                                                                                                                                                          |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

| bit 3   | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are a transmission/ reception has taken place.</li> <li>0 = No SSP interrupt condition has occurred</li> </ul> |

| bit 2   | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                                                                                                                                                                 |

|         | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                                                                                                                                                             |

|         | <u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred                                                                                                                                                 |

|         | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                                                                                                                                                        |

| bit 1   | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                                                                                                                                                                     |

| bit 0   | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                                                                                                                                                        |

|         | 1 = TMR1 register overflowed (must be cleared in software)                                                                                                                                                                                                                                      |

|         | 0 = TMR1 register did not overflow                                                                                                                                                                                                                                                              |

|         |                                                                                                                                                                                                                                                                                                 |

|         | Legend:                                                                                                                                                                                                                                                                                         |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.8 **PCON Register**

| Note: | Interrupt fleg bits get eet when an interrupt |

|-------|-----------------------------------------------|

| note: | Interrupt flag bits get set when an interrupt |

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the Global    |

|       | Interrupt Enable bit, GIE (INTCON<7>).        |

|       | User software should ensure the appropri-     |

|       | ate interrupt flag bits are clear prior to    |

|       | enabling an interrupt.                        |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

-n = Value at POR

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### **REGISTER 2-8:** PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         | U-0                                                                                                                                                  | U-0          | U-0             | U-0          | U-0      | U-0         | R/W-0        | R/W-x |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|----------|-------------|--------------|-------|--|--|

|         | _                                                                                                                                                    | _            |                 | —            | _        | _           | POR          | BOR   |  |  |

|         | bit 7                                                                                                                                                |              |                 |              |          |             |              | bit 0 |  |  |

| bit 7-2 | Unimplem                                                                                                                                             | ented: Read  | <b>l as</b> '0' |              |          |             |              |       |  |  |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                       |              |                 |              |          |             |              |       |  |  |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>    |              |                 |              |          |             |              |       |  |  |

| bit 0   | BOR: Brow                                                                                                                                            | /n-out Reset | Status bit      |              |          |             |              |       |  |  |

|         | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |              |                 |              |          |             |              |       |  |  |

|         | Legend:                                                                                                                                              |              |                 |              |          |             |              |       |  |  |

|         | R = Reada                                                                                                                                            | able bit     | W = W           | /ritable bit | U = Unim | plemented I | bit, read as | '0'   |  |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

# 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 128 or 256 bytes of data EEPROM, with an address range from 00h to 0FFh. Addresses from 80h to FFh are unimplemented on the PIC16F818 device and will read 00h. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EEDATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. These devices have 1K or 2K words of program Flash, with an address range from 0000h to 03FFh for the PIC16F818 and 0000h to 07FFh for the PIC16F819. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

# 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

#### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit, EEPGD, determines if the access will be a program or data memory access. When clear, as it is when Reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

#### 4.5.3 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

#### 4.5.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF<2:0> = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.5.5 CLOCK TRANSITION SEQUENCE WHEN THE IRCF BITS ARE MODIFIED

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

# PIC16F818/819

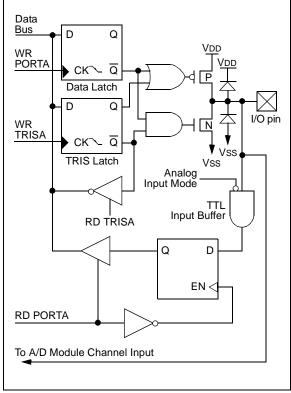

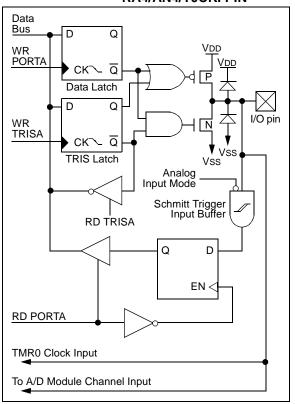

FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

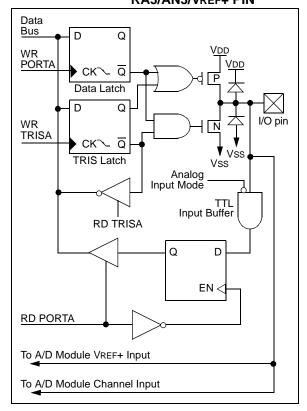

FIGURE 5-2:

#### BLOCK DIAGRAM OF RA3/AN3/VREF+ PIN

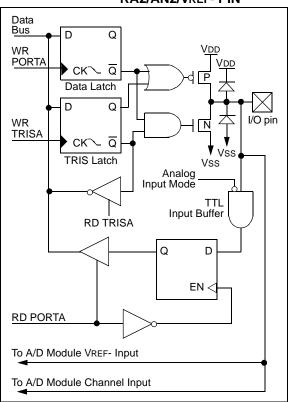

#### FIGURE 5-3: BLOCK DIAGRAM OF RA2/AN2/VREF- PIN

FIGURE 5-4:

#### BLOCK DIAGRAM OF RA4/AN4/T0CKI PIN

#### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

## 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                                                                                                                                                                                                                   | U-0        | R/W-0       | R/W-0        | R/W-0         | R/W-0        | R/W-0          | R/W-0       |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|--------------|---------------|--------------|----------------|-------------|--|--|--|

| _                                                                                                                                                                                                                     | —          | CCP1X       | CCP1Y        | CCP1M3        | CCP1M2       | CCP1M1         | CCP1M0      |  |  |  |

| bit 7                                                                                                                                                                                                                 |            |             |              |               |              |                | bit 0       |  |  |  |

|                                                                                                                                                                                                                       |            |             |              |               |              |                |             |  |  |  |

| Unimplemented: Read as '0'                                                                                                                                                                                            |            |             |              |               |              |                |             |  |  |  |

| CCP1X:CCP1Y: PWM Least Significant bits                                                                                                                                                                               |            |             |              |               |              |                |             |  |  |  |

| <u>Capture moo</u><br>Unused.                                                                                                                                                                                         | <u>de:</u> |             |              |               |              |                |             |  |  |  |

| <u>Compare mo</u><br>Unused.                                                                                                                                                                                          | ode:       |             |              |               |              |                |             |  |  |  |

| <u>PWM mode:</u><br>These bits a                                                                                                                                                                                      |            | LSbs of the | PWM duty     | cycle. The e  | eight MSbs a | re found in (  | CCPRxL.     |  |  |  |

| CCP1M3:CO                                                                                                                                                                                                             | CP1M0: CC  | P1 Mode S   | elect bits   |               |              |                |             |  |  |  |

| 0000 = Cap                                                                                                                                                                                                            | ture/Compa | are/PWM di  | sabled (res  | ets CCP1 m    | odule)       |                |             |  |  |  |

| 0100 = Cap                                                                                                                                                                                                            |            |             |              |               | ,            |                |             |  |  |  |

| 0101 <b>= Cap</b>                                                                                                                                                                                                     |            |             |              |               |              |                |             |  |  |  |

| 0110 = Cap                                                                                                                                                                                                            |            | •           | • •          |               |              |                |             |  |  |  |

| 0111 = Cap<br>1000 = Com                                                                                                                                                                                              |            | •           | • •          |               | ic cot)      |                |             |  |  |  |

|                                                                                                                                                                                                                       | •          | · ·         |              | h (CCP1IF b   | ,            |                |             |  |  |  |

| 1010 <b>= Cor</b>                                                                                                                                                                                                     |            |             |              | terrupt on ma |              | F bit is set,  | CCP1 pin is |  |  |  |

| <ul> <li>1011 = Compare mode, trigger special event (CCP1IF bit is set, CCP1 pin is unaffected)</li> <li>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled)</li> <li>11xx = PWM mode</li> </ul> |            |             |              |               |              |                |             |  |  |  |

|                                                                                                                                                                                                                       |            |             |              |               |              |                | ,           |  |  |  |

|                                                                                                                                                                                                                       |            |             |              |               |              |                |             |  |  |  |

|                                                                                                                                                                                                                       |            |             |              |               |              |                |             |  |  |  |

| Legend:                                                                                                                                                                                                               |            |             |              |               |              |                |             |  |  |  |

| <b>Legend:</b><br>R = Readab                                                                                                                                                                                          | le bit     | W = V       | Vritable bit | U = Uni       | mplemented   | l bit, read as | s 'O'       |  |  |  |

# PIC16F818/819

NOTES:

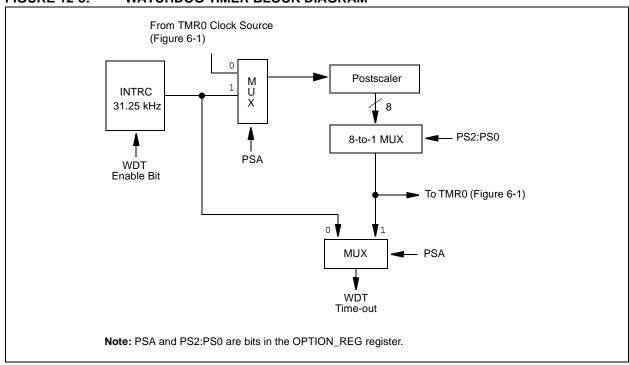

### 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits**"). WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

#### FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | TOSE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

#### 14.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 14.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 14.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 14.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 14.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 14.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 14.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 14.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| PIC16LF<br>(Indus | <b>818/819</b><br>strial) | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |       |            |            |  |  |  |

|-------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------|--|--|--|

| PIC16F8<br>(Indu  | 18/819                    |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |            |            |  |  |  |

| Param<br>No.      | Device                    | Тур                                                                                                                                | Max                                                                                                                                                                                     | Units | Conditions |            |  |  |  |

|                   | Power-Down Current (IPD)  | (1)                                                                                                                                |                                                                                                                                                                                         |       |            |            |  |  |  |

|                   | PIC16LF818/819            | 0.1                                                                                                                                | 0.4                                                                                                                                                                                     | μΑ    | -40°C      |            |  |  |  |

|                   |                           | 0.1                                                                                                                                | 0.4                                                                                                                                                                                     | μΑ    | +25°C      | VDD = 2.0V |  |  |  |

|                   |                           | 0.4                                                                                                                                | 1.5                                                                                                                                                                                     | μΑ    | +85°C      |            |  |  |  |

|                   | PIC16LF818/819            | 0.3                                                                                                                                | 0.5                                                                                                                                                                                     | μΑ    | -40°C      |            |  |  |  |

|                   |                           | 0.3                                                                                                                                | 0.5                                                                                                                                                                                     | μΑ    | +25°C      | VDD = 3.0V |  |  |  |

|                   |                           | 0.7                                                                                                                                | 1.7                                                                                                                                                                                     | μΑ    | +85°C      |            |  |  |  |

|                   | All devices               | 0.6                                                                                                                                | 1.0                                                                                                                                                                                     | μΑ    | -40°C      |            |  |  |  |

|                   |                           | 0.6                                                                                                                                | 1.0                                                                                                                                                                                     | μΑ    | +25°C      | VDD = 5.0V |  |  |  |

|                   |                           | 1.2                                                                                                                                | 5.0                                                                                                                                                                                     | μΑ    | +85°C      | VDD = 3.0V |  |  |  |

|                   | Extended devices          | 6.0                                                                                                                                | 28                                                                                                                                                                                      | μΑ    | +125°C     |            |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

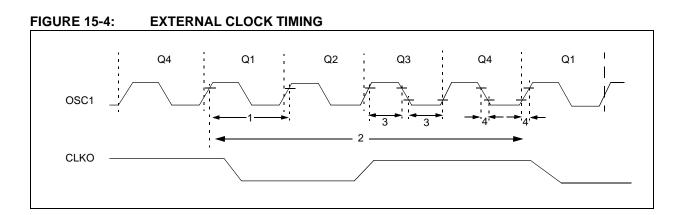

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                |

|--------------|-------|----------------------------------|------|------|--------|-------|---------------------------|

|              | Fosc  | External CLKI Frequency (Note 1) | DC   | _    | 1      | MHz   | XT and RC Oscillator mode |

|              |       |                                  | DC   | _    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | DC   | _    | 32     | kHz   | LP Oscillator mode        |

|              |       | Oscillator Frequency (Note 1)    | DC   |      | 4      | MHz   | RC Oscillator mode        |

|              |       |                                  | 0.1  | _    | 4      | MHz   | XT Oscillator mode        |

|              |       |                                  | 4    | —    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | 5    | _    | 200    | kHz   | LP Oscillator mode        |

| 1            | Tosc  | External CLKI Period (Note 1)    | 1000 | —    | —      | ns    | XT and RC Oscillator mode |

|              |       |                                  | 50   | —    | —      | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | —    | —      | ms    | LP Oscillator mode        |

|              |       | Oscillator Period (Note 1)       | 250  | _    | —      | ns    | RC Oscillator mode        |

|              |       |                                  | 250  |      | 10,000 | ns    | XT Oscillator mode        |

|              |       |                                  | 50   |      | 250    | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | _    | _      | ms    | LP Oscillator mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200  | TCY  | DC     | ns    | TCY = 4/FOSC              |

| 3            | TosL, | External Clock in (OSC1) High    | 500  |      | _      | ns    | XT Oscillator             |

|              | TosH  | or Low Time                      | 2.5  | _    | _      | ms    | LP Oscillator             |

|              |       |                                  | 15   | _    | _      | ns    | HS Oscillator             |

| 4            | TosR, | External Clock in (OSC1) Rise or | —    |      | 25     | ns    | XT Oscillator             |

|              | TosF  | Fall Time                        | —    | _    | 50     | ns    | LP Oscillator             |

|              |       |                                  | —    | _    | 15     | ns    | HS Oscillator             |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

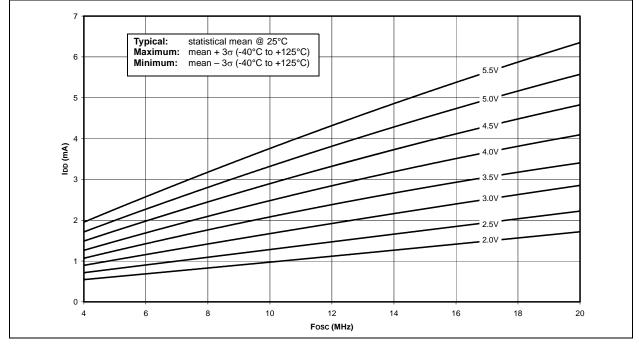

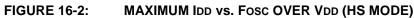

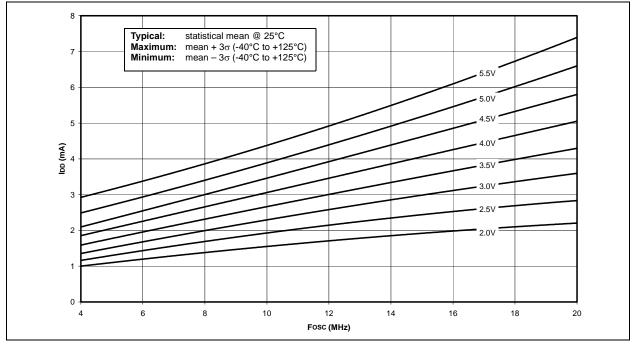

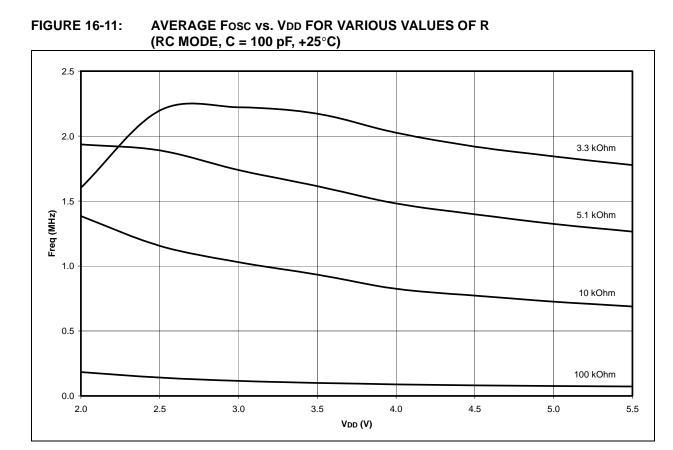

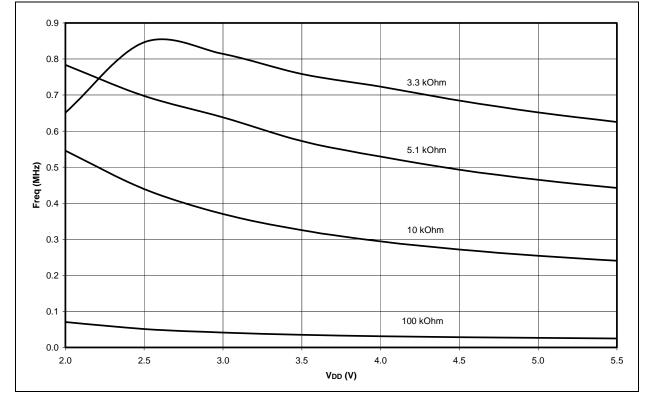

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

# PIC16F818/819

FIGURE 16-12: AVERAGE Fosc vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 300 pF, +25°C)

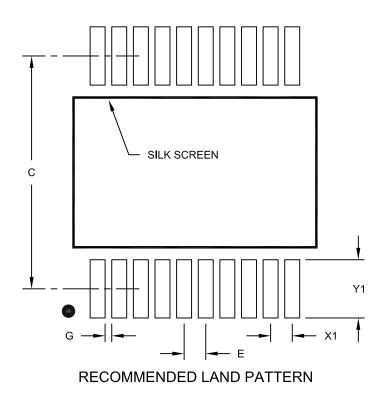

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |  |      |  |

|--------------------------|------------------|----------|--|------|--|

| Dimension                | Dimension Limits |          |  | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |  |      |  |

| Contact Pad Spacing      | С                | 7.20     |  |      |  |

| Contact Pad Width (X20)  | X1               |          |  | 0.45 |  |

| Contact Pad Length (X20) | Y1               |          |  | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |  |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

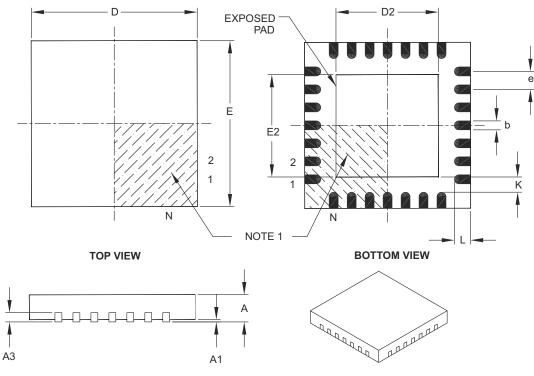

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     | MILLIMETERS    |          |      |  |

|------------------------|-----------|----------------|----------|------|--|

| Dimensio               | on Limits | MIN            | NOM      | MAX  |  |

| Number of Pins         | Ν         |                | 28       |      |  |

| Pitch                  | е         |                | 0.65 BSC |      |  |

| Overall Height         | Α         | 0.80 0.90 1.0  |          |      |  |

| Standoff               | A1        | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3        | 0.20 REF       |          |      |  |

| Overall Width          | Е         | 6.00 BSC       |          |      |  |

| Exposed Pad Width      | E2        | 3.65 3.70 4.20 |          |      |  |

| Overall Length         | D         | 6.00 BSC       |          |      |  |

| Exposed Pad Length     | D2        | 3.65           | 3.70     | 4.20 |  |

| Contact Width          | b         | 0.23           | 0.30     | 0.35 |  |

| Contact Length         | L         | 0.50           | 0.55     | 0.70 |  |

| Contact-to-Exposed Pad | К         | 0.20           | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B