Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf818t-i-ml |

### **Table of Contents**

| 1.0   | Device Overview                             |      |

|-------|---------------------------------------------|------|

| 2.0   | Memory Organization                         | 9    |

| 3.0   | Data EEPROM and Flash Program Memory        | . 25 |

| 4.0   | Oscillator Configurations                   | . 33 |

| 5.0   | I/O Ports                                   | . 39 |

| 6.0   | Timer0 Module                               | . 53 |

| 7.0   | Timer1 Module                               | . 57 |

| 8.0   | Timer2 Module                               | . 63 |

| 9.0   | Capture/Compare/PWM (CCP) Module            | . 65 |

| 10.0  | Synchronous Serial Port (SSP) Module        | . 71 |

| 11.0  | Analog-to-Digital Converter (A/D) Module    | . 81 |

| 12.0  | Special Features of the CPU                 | . 89 |

| 13.0  | Instruction Set Summary                     | 103  |

|       | Development Support                         |      |

| 15.0  | Electrical Characteristics                  | 115  |

| 16.0  | DC and AC Characteristics Graphs and Tables | 141  |

| 17.0  | Packaging Information                       | 155  |

| Appe  | ndix A: Revision History                    | 165  |

| Appe  | ndix B: Device Differences                  | 165  |

| INDE  | X                                           | 167  |

| The N | Microchip Web Site                          | 173  |

| Custo | mer Change Notification Service             | 173  |

| Custo | mer Support                                 | 173  |

| Read  | er Response                                 | 174  |

| PIC16 | SF818/819 Product Identification System     | 175  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F818/819. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F818 device's 128 bytes of data EEPROM memory have the address range of 00h-7Fh and the PIC16F819 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in **Section 3.0 "Data EEPROM and Flash Program Memory**".

Additional information on device memory may be found in the "PIC® Mid-Range Reference Manual" (DS33023).

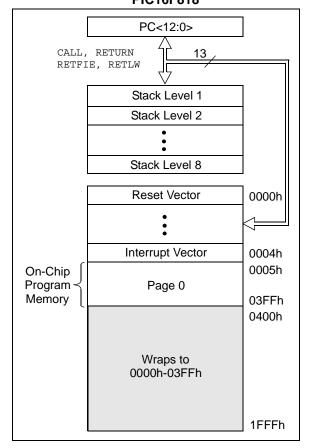

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR

PIC16F818

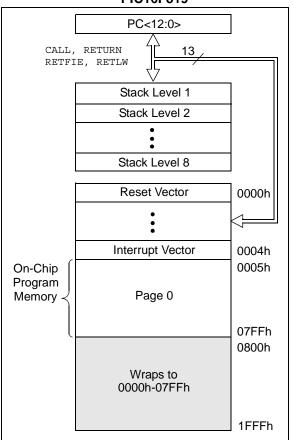

# 2.1 Program Memory Organization

The PIC16F818/819 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F818, the first 1K x 14 (0000h-03FFh) is physically implemented (see Figure 2-1). For the PIC16F819, the first 2K x 14 is located at 0000h-07FFh (see Figure 2-2). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK FOR

PIC16F819

# PIC16F818/819

# 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

| U-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-----|-----|-------|--------|--------|--------|

| _     | ADIF  | _   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7 |       |     |     |       |        |        | hit 0  |

Note:

bit 7 Unimplemented: Read as '0'

bit 6 ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed

0 = The A/D conversion is not complete

bit 5-4 Unimplemented: Read as '0'

bit 3 SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit

1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are a transmission/ reception has taken place.

0 = No SSP interrupt condition has occurred

bit 2 CCP1IF: CCP1 Interrupt Flag bit

### Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

# Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

#### PWM mode:

Unused in this mode.

bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 4.5.2 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the application. This is done by writing to the OSCTUNE register (Register 4-1). The tuning sensitivity is constant throughout the tuning range. The OSCTUNE register has a tuning range of ±12.5%.

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately 8 \* 32  $\mu s = 256~\mu s$ ); the INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the 31.25 kHz INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

# REGISTER 4-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** Frequency Tuning bits

011111 = Maximum frequency

011110 =

•

•

000001 =

000000 = Center frequency. Oscillator module is running at the calibrated frequency.

111111 =

•

•

100000 = Minimum frequency

# Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared X = Bit is unknown

# 6.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

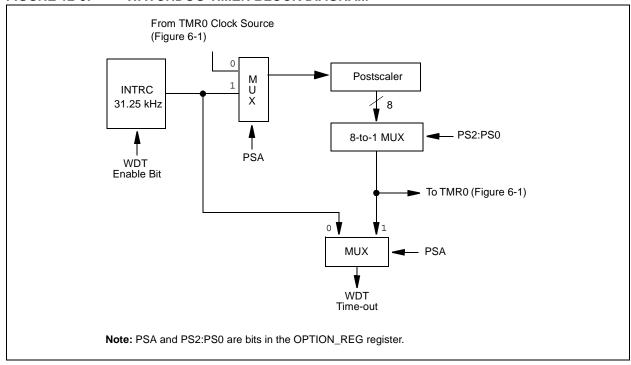

#### 6.4 Prescaler

There is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

Timer0 module means that there is no prescaler for the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

# REGISTER 6-1: OPTION\_REG: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 **T0SE**: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin

0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

#### bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1:256     | 1:128    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** To avoid an unintended device Reset, the instruction sequence shown in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

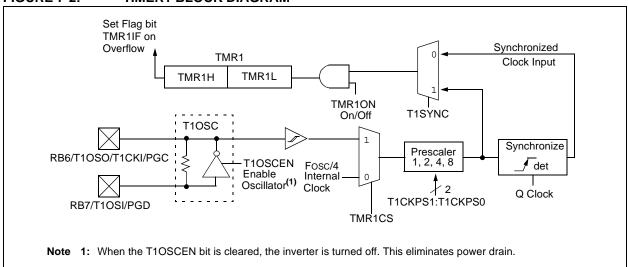

# 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

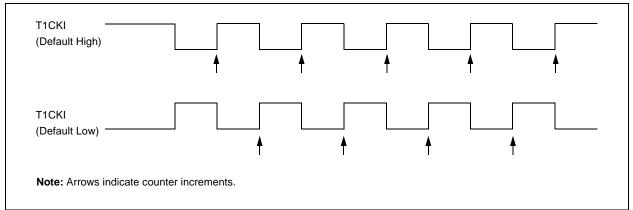

# 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set, or on pin RB6/T1OSO/T1CKI/PGC when bit T1OSCEN is cleared.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

### FIGURE 7-1: TIMER1 INCREMENTING EDGE

### FIGURE 7-2: TIMER1 BLOCK DIAGRAM

# 7.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

# 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

### 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

# 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6** "Timer1 Oscillator"), gives users the option to include RTC functionality in their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

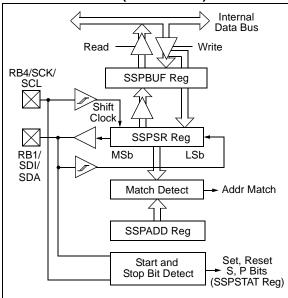

# 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/SCK/SCL pin, which is the clock (SCL) and the RB1/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits.

To ensure proper communication of the  $I^2C$  Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the  $I^2C$  pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the  $I^2C$  pins (PORTx [SDA, SCL]) are changed in software during  $I^2C$  communication using a Read-Modify-Write instruction (BSF, BCF), then the  $I^2C$  mode may stop functioning properly and  $I^2C$  communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the  $I^2C$  pins) using the instruction BSF or BCF during  $I^2C$  communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

### **EXAMPLE 10-1:**

```

MOVF TRISC, W ; Example for an 18-pin part such as the PIC16F818/819

IORLW 0x18 ; Ensures <4:3> bits are '11'

ANDLW B'11111001' ; Sets <2:1> as output, but will not alter other bits

; User can use their own logic here, such as IORLW, XORLW and ANDLW

MOVWF TRISC

```

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

# FIGURE 10-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for I<sup>2</sup>C operation:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Firmware Controlled Master mode with Start and Stop bit interrupts enabled, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

Additional information on SSP I<sup>2</sup>C operation may be found in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

# 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. The seven possible options for TAD are:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu s$  and not greater than 6.4  $\mu s$ .

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# 11.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current out of the device specification.

TABLE 11-1: TAD vs. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (F))

|                       | Maximum Davice Erequency |           |                          |

|-----------------------|--------------------------|-----------|--------------------------|

| Operation             | ADCS<2>                  | ADCS<1:0> | Maximum Device Frequency |

| 2 Tosc                | 0                        | 00        | 1.25 MHz                 |

| 4 Tosc                | 1                        | 00        | 2.5 MHz                  |

| 8 Tosc                | 0                        | 01        | 5 MHz                    |

| 16 Tosc               | 1                        | 01        | 10 MHz                   |

| 32 Tosc               | 0                        | 10        | 20 MHz                   |

| 64 Tosc               | 1                        | 10        | 20 MHz                   |

| RC <sup>(1,2,3)</sup> | Х                        | 11        | (Note 1)                 |

- **Note 1:** The RC source has a typical TAD time of 4  $\mu$ s but can vary between 2-6  $\mu$ s.

- 2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for Sleep operation.

- 3: For extended voltage devices (LF), please refer to Section 15.0 "Electrical Characteristics".

# 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits"**).

WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | T0SE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

# 15.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                               | -40°C to +125°C                     |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Storage temperature                                                                                          | -65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                 | 0.3V to (VDD + 0.3V)                |

| Voltage on VDD with respect to Vss                                                                           | -0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                 | 0.3 to +14V                         |

| Total power dissipation (Note 1)                                                                             | 1W                                  |

| Maximum current out of Vss pin                                                                               | 200 mA                              |

| Maximum current into VDD pin                                                                                 |                                     |

| Input clamp current, IIK (VI < 0 or VI > VDD)                                                                | ±20 mA                              |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                               | ±20 mA                              |

| Maximum output current sunk by any I/O pin                                                                   | 25 mA                               |

| Maximum output current sourced by any I/O pin                                                                | 25 mA                               |

| Maximum current sunk by PORTA                                                                                | 100 mA                              |

| Maximum current sourced by PORTA                                                                             | 100 mA                              |

| Maximum current sunk by PORTB                                                                                | 100 mA                              |

| Maximum current sourced by PORTB                                                                             | 100 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VI | $D = VOH(x IOH) + \Sigma(VO(x IO))$ |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD  $x \{IDD - \sum IOH\} + \sum \{(VDD - VOH) \times IOH\} + \sum \{(VDL \times IOL) \times IOH\} + \sum \{(VDL \times IOH) \times$

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>2:</sup> Voltage spikes at the MCLR pin may cause latch-up. A series resistor of greater than 1 kΩ should be used to pull MCLR to VDD, rather than tying the pin directly to VDD.

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF<br>(Indu                        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial |                                                                                                                                                                                                                                     |     |       |            |            |                 |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|-----------------|--|--|

| PIC16F818/819<br>(Industrial, Extended) |                                                                                                                                                          | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |       |            |            |                 |  |  |

| Param<br>No.                            | Device                                                                                                                                                   | Тур                                                                                                                                                                                                                                 | Max | Units | Conditions |            |                 |  |  |

|                                         | Supply Current (IDD) <sup>(2,3)</sup>                                                                                                                    |                                                                                                                                                                                                                                     |     |       |            |            |                 |  |  |

|                                         | PIC16LF818/819                                                                                                                                           | 9                                                                                                                                                                                                                                   | 20  | μА    | -40°C      | VDD = 2.0V |                 |  |  |

|                                         |                                                                                                                                                          | 7                                                                                                                                                                                                                                   | 15  | μΑ    | +25°C      |            |                 |  |  |

|                                         |                                                                                                                                                          | 7                                                                                                                                                                                                                                   | 15  | μΑ    | +85°C      |            |                 |  |  |

|                                         | PIC16LF818/819                                                                                                                                           | 16                                                                                                                                                                                                                                  | 30  | μΑ    | -40°C      |            |                 |  |  |

|                                         |                                                                                                                                                          | 14                                                                                                                                                                                                                                  | 25  | μΑ    | +25°C      | VDD = 3.0V | Fosc = 32 kHz   |  |  |

|                                         |                                                                                                                                                          | 14                                                                                                                                                                                                                                  | 25  | μΑ    | +85°C      |            | (LP Oscillator) |  |  |

|                                         | All devices                                                                                                                                              | 32                                                                                                                                                                                                                                  | 40  | μΑ    | -40°C      |            |                 |  |  |

|                                         |                                                                                                                                                          | 26                                                                                                                                                                                                                                  | 35  | μΑ    | +25°C      | VDD = 5.0V |                 |  |  |

|                                         |                                                                                                                                                          | 26                                                                                                                                                                                                                                  | 35  | μΑ    | +85°C      | טטע = 5.00 |                 |  |  |

|                                         | Extended devices                                                                                                                                         | 35                                                                                                                                                                                                                                  | 53  | μΑ    | +125°C     |            |                 |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

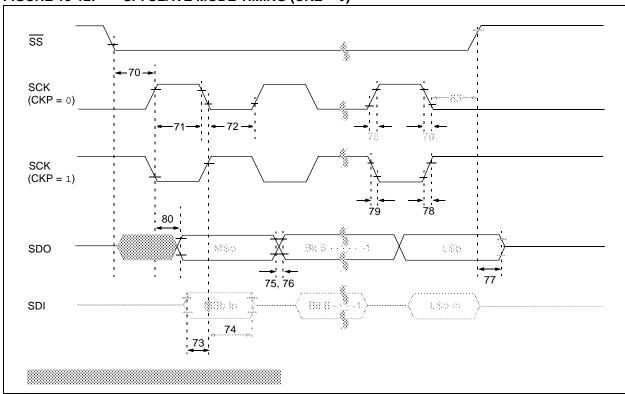

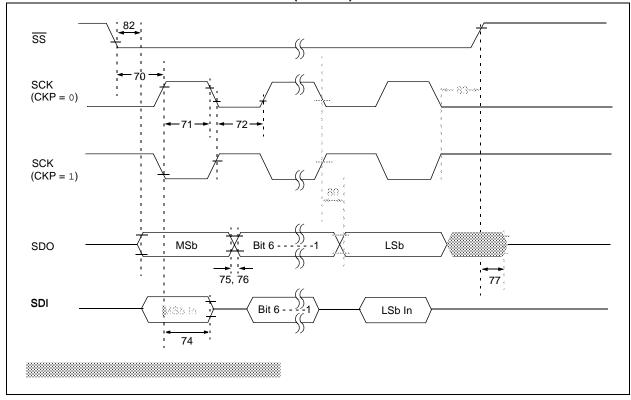

FIGURE 15-12: SPI SLAVE MODE TIMING (CKE = 0)

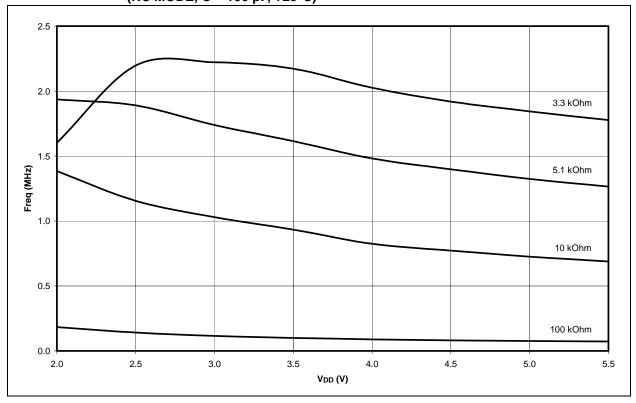

FIGURE 16-11: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, +25°C)

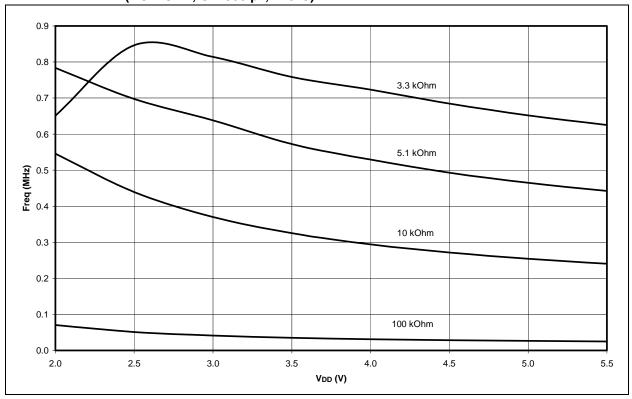

FIGURE 16-12: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 300 pF, +25°C)

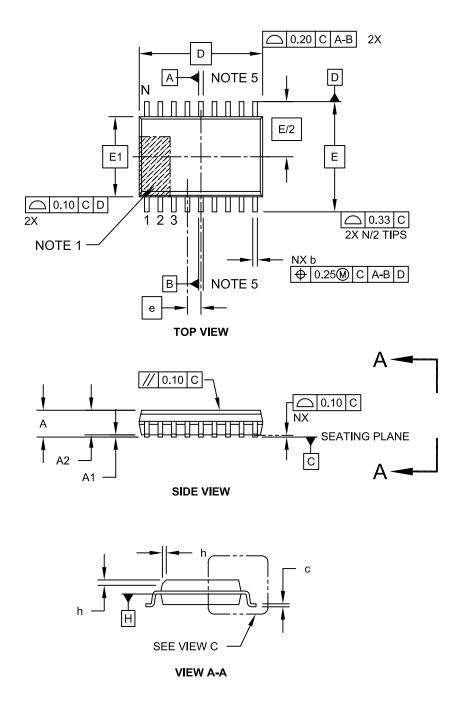

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-051C Sheet 1 of 2

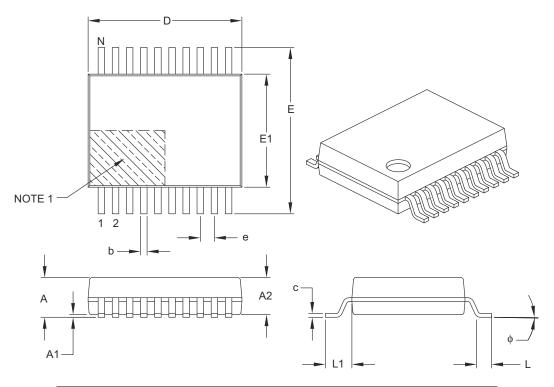

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      |      |          | MILLIMETERS |  |  |  |

|--------------------------|------------|------|----------|-------------|--|--|--|

| Dimens                   | ion Limits | MIN  | NOM      | MAX         |  |  |  |

| Number of Pins           | N          |      | 20       |             |  |  |  |

| Pitch                    | е          |      | 0.65 BSC |             |  |  |  |

| Overall Height           | Α          | _    | _        | 2.00        |  |  |  |

| Molded Package Thickness | A2         | 1.65 | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1         | 0.05 | _        | _           |  |  |  |

| Overall Width            | Е          | 7.40 | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1         | 5.00 | 5.30     | 5.60        |  |  |  |

| Overall Length           | D          | 6.90 | 7.20     | 7.50        |  |  |  |

| Foot Length              | L          | 0.55 | 0.75     | 0.95        |  |  |  |

| Footprint                | L1         |      | 1.25 REF |             |  |  |  |

| Lead Thickness           | С          | 0.09 | _        | 0.25        |  |  |  |

| Foot Angle               | ф          | 0°   | 4°       | 8°          |  |  |  |

| Lead Width               | b          | 0.22 | _        | 0.38        |  |  |  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

# PIC16F818/819

| TMR0IE Bit                                  | 18       | RCIO                               | 3                              |

|---------------------------------------------|----------|------------------------------------|--------------------------------|

| Internal Oscillator Block                   | 35       | XT                                 |                                |

| INTRC Modes                                 |          | Oscillator Control Register        |                                |

| Internet Address                            |          | Modifying IRCF Bits                |                                |

| Interrupt Sources                           |          | Clock Transition Sequence          |                                |

| RB0/INT Pin, External                       |          | Oscillator Start-up Timer (OST)    |                                |

| TMR0 Overflow                               |          | Oscillator, WDT                    |                                |

| Interrupts                                  |          | ·                                  |                                |

| RB7:RB4 Port Change                         | 43       | Р                                  |                                |

| Synchronous Serial Port Interrupt           |          | Packaging Information              | 15                             |

| Interrupts, Context Saving During           |          | Marking                            | 15                             |

| Interrupts, Enable Bits                     |          | PCFG0 Bit                          |                                |

| Global Interrupt Enable (GIE Bit)           | 96       | PCFG1 Bit                          | 82                             |

| Interrupt-on-Change (RB7:RB4) Enable        |          | PCFG2 Bit                          | 82                             |

| (RBIE Bit)                                  | 97       | PCFG3 Bit                          | 8:                             |

| RB0/INT Enable (INTE Bit)                   |          | PCL Register                       |                                |

| TMR0 Overflow Enable (TMR0IE Bit)           |          | PCLATH Register                    |                                |

| Interrupts, Enable bits                     |          | PCON Register                      |                                |

| Global Interrupt Enable (GIE Bit)           | 18       | POR Bit                            |                                |

| Interrupts, Flag Bits                       |          | Pinout Descriptions                |                                |

| Interrupt-on-Change (RB7:RB4) Flag          |          | PIC16F818/819                      |                                |

| (RBIF Bit)                                  | 18 97    | Pointer, FSR                       |                                |

| RB0/INT Flag (INTF Bit)                     |          | POP                                |                                |

| TMR0 Overflow Flag (TMR0IF Bit)             |          | POR. See Power-on Reset.           |                                |

| INTRC Modes                                 |          | PORTA                              | ·                              |

| Adjustment                                  | 36       | Associated Register Summary        |                                |

|                                             |          | Functions                          |                                |

| L                                           |          | PORTA Register                     |                                |

| Loading of PC                               | 23       | TRISA Register                     |                                |

| Low-Voltage ICSP Programming                |          | PORTA Register                     |                                |

|                                             |          | PORTB                              |                                |

| M                                           |          | Associated Register Summary        |                                |

| Master Clear (MCLR)                         |          | Functions                          |                                |

| MCLR Reset, Normal Operation91,             | 93, 94   | PORTB Register                     |                                |

| MCLR Reset, Sleep91,                        |          | Pull-up Enable (RBPU Bit)          |                                |

| Operation and ESD Protection                |          | RB0/INT Edge Select (INTEDG Bit)   |                                |

| Memory Organization                         |          | RB0/INT Pin, External              |                                |

| Data Memory                                 |          | RB7:RB4 Interrupt-on-Change        |                                |

| Program Memory                              |          | RB7:RB4 Interrupt-on-Change Enable | •                              |

| Microchip Internet Web Site                 |          | (RBIE Bit)                         | 9 <sup>-</sup>                 |

| MPLAB ASM30 Assembler, Linker, Librarian    | 112      | RB7:RB4 Interrupt-on-Change Flag   | •                              |

| MPLAB Integrated Development                |          | (RBIF Bit)                         | 18. 9 <sup>-</sup>             |

| Environment Software                        | 111      | TRISB Register                     |                                |

| MPLAB PM3 Device Programmer                 |          | PORTB Register                     |                                |

| MPLAB REAL ICE In-Circuit Emulator System   |          | Postscaler, WDT                    |                                |

| MPLINK Object Linker/MPLIB Object Librarian | 112      | Assignment (PSA Bit)               | 1                              |

| •                                           |          | Rate Select (PS2:PS0 Bits)         |                                |

| 0                                           |          | Power-Down Mode. See Sleep.        |                                |

| Opcode Field Descriptions                   | 103      | Power-on Reset (POR)               | 39. 91. 92. 93. 9 <sup>4</sup> |

| OPTION_REG Register                         | 15       | POR Status (POR Bit)               |                                |

| INTEDG Bit                                  | . 17, 54 | Power Control (PCON) Register      |                                |

| PS2:PS0 Bits                                | 17       | Power-Down (PD Bit)                |                                |

| PSA Bit                                     | 17       | Time-out (TO Bit)                  |                                |

| RBPU Bit                                    | . 17, 54 | Power-up Timer (PWRT)              |                                |

| T0CS Bit                                    | 17       | PR2 Register                       |                                |

| T0SE Bit                                    | 17       | Prescaler, Timer0                  | •                              |

| Oscillator Configuration                    | 33       | Assignment (PSA Bit)               | 1                              |

| ECIO                                        | 33       | Rate Select (PS2:PS0 Bits)         |                                |

| EXTCLK                                      | 93       | Program Counter                    |                                |

| EXTRC                                       | 93       | Reset Conditions                   | 9:                             |

| HS                                          | . 33, 93 |                                    |                                |

| INTIO1                                      | 33       |                                    |                                |

| INTIO2                                      | 33       |                                    |                                |

| INTRC                                       | 93       |                                    |                                |

| LP                                          | . 33, 93 |                                    |                                |

| RC                                          | . 33, 35 |                                    |                                |

# PIC16F818/819

**NOTES:**

# PIC16F818/819 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | <u>x</u>                                                                         | <u>xxx</u> | Examples:                                                                                                                                       |

|-------------------|----------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | Temperature Package<br>Range                                                     | Pattern    | a) PIC16LF818-I/P = Industrial temp., PDIP package, Extended VDD limits. b) PIC16F818-I/SO = Industrial temp., SOIC package, normal VDD limits. |

| Device            | PIC16F818: Standard VDD<br>PIC16F818T: (Tape and Ree<br>PIC16LF818: Extended VDD | el)        |                                                                                                                                                 |

| Temperature Range | - = 0°C to +70°C<br>I = -40°C to +85°C (Ind<br>E = -40°C to +125°C (E            |            |                                                                                                                                                 |

| Package           | P = PDIP<br>SO = SOIC<br>SS = SSOP<br>ML = QFN                                   |            | Note 1: F = CMOS Flash  LF = Low-Power CMOS Flash                                                                                               |

| Pattern           | QTP, SQTP, ROM Code (fac<br>Special Requirements. Blank<br>Windowed devices.     |            | 2: T = in tape and reel – SOIC, SSOP packages only.                                                                                             |

|                   |                                                                                  |            |                                                                                                                                                 |

|                   |                                                                                  |            |                                                                                                                                                 |

# Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Vieio, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

**Toronto**

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000

Fax: 86-10-8528-2104 China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongging Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300

Fax: 86-27-5980-5118 China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859 Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

## **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340 Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

UK - Wokingham Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12