# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 10MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 16                                                                            |

| Program Memory Size        | 1.75KB (1K x 14)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 128 x 8                                                                       |

| RAM Size                   | 128 × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 5x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf818t-i-sstsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F818/819. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F818 device's 128 bytes of data EEPROM memory have the address range of 00h-7Fh and the PIC16F819 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in Section 3.0 "Data EEPROM and Flash Program Memory".

Additional information on device memory may be found in the *"PIC<sup>®</sup> Mid-Range Reference Manual"* (DS33023).

#### 2.1 **Program Memory Organization**

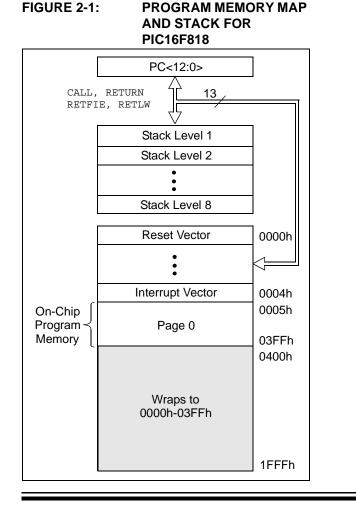

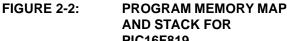

The PIC16F818/819 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F818, the first 1K x 14 (0000h-03FFh) is physically implemented (see Figure 2-1). For the PIC16F819, the first 2K x 14 is located at 0000h-07FFh (see Figure 2-2). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

#### 2.2 Data Memory Organization

The data memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank for code reduction and quicker access (e.g., the Status register is in Banks 0-3).

| Note: | EEPROM data memory description can be<br>found in Section 3.0 "Data EEPROM and |  |  |  |

|-------|--------------------------------------------------------------------------------|--|--|--|

|       | Flash Program Memory" of this data sheet.                                      |  |  |  |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register, FSR.

### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F818/819 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

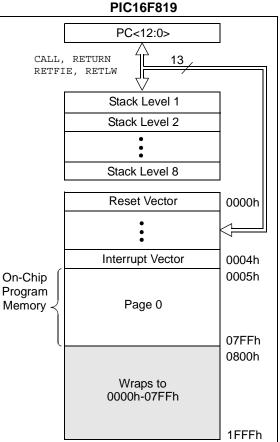

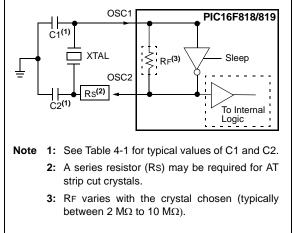

#### 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F818/819 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

#### TABLE 4-1: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|---------|-------------------------------------|-------|--|--|

|          | Freq    | C1                                  | C2    |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |

|          | 200 kHz | 15 pF                               | 15 pF |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |

|          | 8 MHz   |                                     | 15 pF |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111' | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock, |

|---------|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

|         | MOVWF                                      | TICON                                          | ; Asynchronous operation, external oscillator                                              |

|         | CLRF<br>CLRF                               | secs<br>mins                                   | ; Initialize timekeeping registers                                                         |

|         | MOVLW                                      | mins<br>.12                                    |                                                                                            |

|         | MOVLW                                      | .12<br>hours                                   |                                                                                            |

|         | BANKSEL                                    | PIE1                                           |                                                                                            |

|         | BSF                                        |                                                | ; Enable Timer1 interrupt                                                                  |

|         | RETURN                                     | ,                                              | ,                                                                                          |

| RTCisr  | BANKSEL                                    | TMR1H                                          |                                                                                            |

|         | BSF                                        | TMR1H, 7                                       | ; Preload for 1 sec overflow                                                               |

|         | BCF                                        | PIR1, TMR1IF                                   | ; Clear interrupt flag                                                                     |

|         | INCF                                       | secs, F                                        | ; Increment seconds                                                                        |

|         | MOVF                                       | secs, w                                        |                                                                                            |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | seconds                                        | ; Clear seconds                                                                            |

|         | INCF<br>MOVF                               | mins, f<br>mins, w                             | ; Increment minutes                                                                        |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     | 511105, 2                                      | ; No, done                                                                                 |

|         | CLRF                                       | mins                                           | ; Clear minutes                                                                            |

|         | INCF                                       | hours, f                                       | ; Increment hours                                                                          |

|         | MOVF                                       | hours, w                                       |                                                                                            |

|         | SUBLW                                      | .24                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 24 hours elapsed?                                                                        |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | hours                                          | ; Clear hours                                                                              |

|         | RETURN                                     |                                                | ; Done                                                                                     |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7   | Bit 6                                                                                          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Valu<br>POR, |      | all c | e on<br>other<br>sets |

|-----------------------|--------|---------|------------------------------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|--------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                                                                                           | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000         | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1   | _       | ADIF                                                                                           | _       | _       | SSPIF   | CCP1IF | TMR2IF | TMR1IF | - 0          | 0000 | - 0   | 0000                  |

| 8Ch                   | PIE1   | _       | ADIE                                                                                           | _       | _       | SSPIE   | CCP1IE | TMR2IE | TMR1IE | - 0          | 0000 | - 0   | 0000                  |

| 0Eh                   | TMR1L  | Holding | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register                    |         |         |         |        |        |        |              |      |       |                       |

| 0Fh                   | TMR1H  | Holding | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |         |         |         |        |        |        |              |      |       |                       |

| 10h                   | T1CON  |         | _                                                                                              | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00           | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

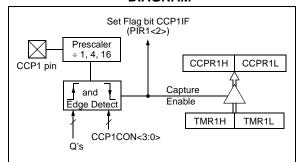

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW CAPT PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

NOTES:

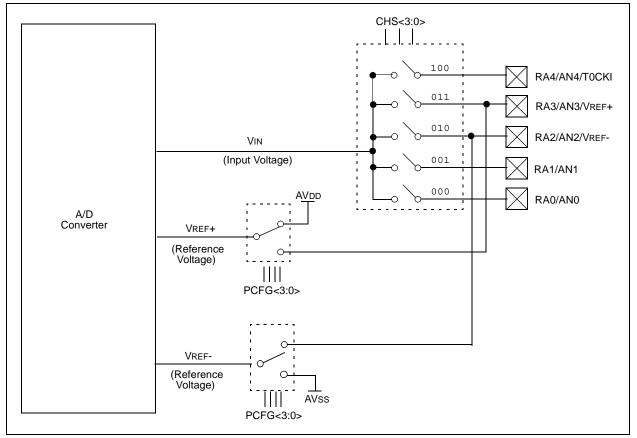

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1** "**A/D Acquisition Requirements**". After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

**FIGURE 11-1:**

#### A/D BLOCK DIAGRAM

© 2001-2013 Microchip Technology Inc.

#### **FIGURE 12-9:** WAKE-UP FROM SLEEP THROUGH INTERRUPT

| OSC1 /<br>CLKO <sup>(4)</sup> //    | 3   Q4 ; Q1   Q2   Q3   Q4 ; Q1<br>/////////_ |                    |              | . Q1  Q2  Q3  Q4<br>          | Q1  Q2  Q3  Q4<br>    | Q1 Q2 Q3 Q4; |

|-------------------------------------|-----------------------------------------------|--------------------|--------------|-------------------------------|-----------------------|--------------|

| INT pin                             | <u> </u>                                      |                    | I            | 1                             | 1                     |              |

| INTF Flag<br>(INTCON<1>)            |                                               | \ <u>+</u>         |              | Interrupt Latency<br>(Note 2) |                       |              |

| GIE bit<br>(INTCON<7>)              | i i i i i i i i i i i i i i i i i i i         | cessor in<br>Sleep |              |                               | ,<br>,<br>,<br>,<br>, |              |

| INSTRUCTION FLOW                    |                                               | 1                  | l<br>I       | I I                           | 1                     | 1            |

| PC Y PC                             | X PC + 1 X                                    | PC + 2             | X PC + 2     | X PC + 2                      | 0004h                 | X 0005h      |

| Fetched Inst(PC) = S                | Sleep Inst(PC + 1)                            |                    | Inst(PC + 2) | 1<br>1<br>1                   | Inst(0004h)           | Inst(0005h)  |

| Instruction<br>Executed { Inst(PC - | - 1) Sleep                                    |                    | Inst(PC + 1) | Dummy Cycle                   | Dummy Cycle           | Inst(0004h)  |

| Note 1: XT HS or IP (               | Oscillator mode assumed                       |                    |              |                               |                       |              |

2: TOST = 1024 TOSC (drawing not to scale). This delay will not be there for RC Oscillator mode.

GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line. 3:

4: CLKO is not available in these oscillator modes but shown here for timing reference.

#### 12.14 In-Circuit Debugger

When the DEBUG bit in the Configuration Word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-6 shows which features are consumed by the background debugger.

| TABLE 12-6: DEB | JGGER RESOURCES |

|-----------------|-----------------|

|-----------------|-----------------|

| I/O pins       | RB6, RB7                                   |

|----------------|--------------------------------------------|

| Stack          | 1 level                                    |

| Program Memory | Address 0000h must be NOP                  |

|                | Last 100h words                            |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB-0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

#### 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 12.16 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the four Least Significant bits of the ID location are used.

#### 12.18 Low-Voltage ICSP Programming

The LVP bit of the Configuration Word register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when Programming mode is entered with VIHH on MCLR. The LVP bit can only be changed when using high voltage on MCLR.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only this mode can be used to program the device.

When using Low-Voltage ICSP, the part must be supplied at 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code-protect bits from an ON state to an OFF state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs or user code can be reprogrammed or added.

The following LVP steps assume the LVP bit is set in the Configuration Word register.

- 1. Apply VDD to the VDD pin.

- 2. Drive MCLR low.

- 3. Apply VDD to the RB3/PGM pin.

- 4. Apply VDD to the  $\overline{\text{MCLR}}$  pin.

- 5. Follow with the associated programming steps.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode (LVP = 1), the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F818/819 device will enter Programming mode.

- 5: LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the Configuration Word register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

## 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                     |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \le k \le 255$                                                                                                     |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

## 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| DC CHARACTERISTICS     |       | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \\ \mbox{Operating voltage VDD range as described in Section 15.1 "DC Characteristics: Supply Voltage".} \end{array}$ |                 |      |          |       |                                                                    |

|------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------|-------|--------------------------------------------------------------------|

| Param<br>No.           | Sym   | Characteristic                                                                                                                                                                                                                                                                                                                                                     | Min             | Тур† | Max      | Units | Conditions                                                         |

| VIL Input Low Voltage  |       |                                                                                                                                                                                                                                                                                                                                                                    | •               |      |          |       |                                                                    |

|                        |       | I/O ports:                                                                                                                                                                                                                                                                                                                                                         |                 |      |          |       |                                                                    |

| D030                   |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                    | Vss             | _    | 0.15 Vdd | V     | For entire VDD range                                               |

| D030A                  |       |                                                                                                                                                                                                                                                                                                                                                                    | Vss             | _    | 0.8V     | V     | $4.5V \le V\text{DD} \le 5.5V$                                     |

| D031                   |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                        | Vss             | _    | 0.2 Vdd  | V     |                                                                    |

| D032                   |       | MCLR, OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                            | Vss             | _    | 0.2 Vdd  | V     | (Note 1)                                                           |

| D033                   |       | OSC1 (in XT and LP mode)                                                                                                                                                                                                                                                                                                                                           | Vss             | _    | 0.3V     | V     |                                                                    |

|                        |       | OSC1 (in HS mode)                                                                                                                                                                                                                                                                                                                                                  | Vss             | _    | 0.3 Vdd  | V     |                                                                    |

|                        |       | Ports RB1 and RB4:                                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                    |

| D034                   |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                        | Vss             | _    | 0.3 Vdd  | V     | For entire VDD range                                               |

| VIH Input High Voltage |       |                                                                                                                                                                                                                                                                                                                                                                    |                 |      |          |       |                                                                    |

|                        |       | I/O ports:                                                                                                                                                                                                                                                                                                                                                         |                 |      |          |       |                                                                    |

| D040                   |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                    | 2.0             | _    | Vdd      | V     | $4.5V \le V\text{DD} \le 5.5V$                                     |

| D040A                  |       |                                                                                                                                                                                                                                                                                                                                                                    | 0.25 VDD + 0.8V | _    | Vdd      | V     | For entire VDD range                                               |

| D041                   |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                        | 0.8 Vdd         | _    | Vdd      | V     | For entire VDD range                                               |

| D042                   |       | MCLR                                                                                                                                                                                                                                                                                                                                                               | 0.8 Vdd         | —    | Vdd      | V     |                                                                    |

| D042A                  |       | OSC1 (in XT and LP mode)                                                                                                                                                                                                                                                                                                                                           | 1.6V            | _    | Vdd      | V     |                                                                    |

|                        |       | OSC1 (in HS mode)                                                                                                                                                                                                                                                                                                                                                  | 0.7 Vdd         | _    | Vdd      | V     |                                                                    |

| D043                   |       | OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                  | 0.9 Vdd         | _    | Vdd      | V     | (Note 1)                                                           |

|                        |       | Ports RB1 and RB4:                                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                    |

| D044                   |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                        | 0.7 Vdd         | _    | Vdd      | V     | For entire VDD range                                               |

| D070                   | IPURB | PORTB Weak Pull-up Current                                                                                                                                                                                                                                                                                                                                         | 50              | 250  | 400      | μΑ    | VDD = 5V, VPIN = VSS                                               |

|                        | lı∟   | Input Leakage Current (Notes 2, 3)                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                    |

| D060                   |       | I/O ports                                                                                                                                                                                                                                                                                                                                                          | —               | —    | ±1       | μA    | Vss $\leq$ VPIN $\leq$ VDD, pin at high-impedance                  |

| D061                   |       | MCLR                                                                                                                                                                                                                                                                                                                                                               | —               | _    | ±5       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                           |

| D063                   |       | OSC1                                                                                                                                                                                                                                                                                                                                                               | _               | —    | ±5       | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F818/819 be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

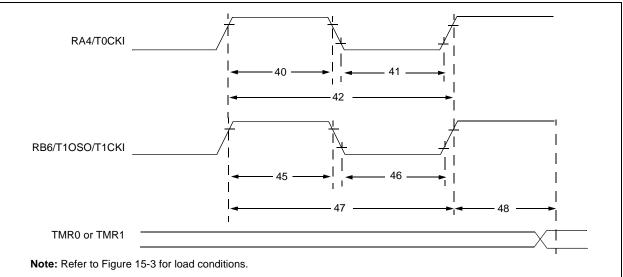

#### FIGURE 15-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Symbol                                                    |                   | Characteristic                        |                         | Min                                       | Тур† | Max    | Units | Conditions                         |

|--------------|-----------------------------------------------------------|-------------------|---------------------------------------|-------------------------|-------------------------------------------|------|--------|-------|------------------------------------|

| 40*          | T⊤0H                                                      | T0CKI High Pulse  | T0CKI High Pulse Width                |                         | 0.5 TCY + 20                              | —    | —      | ns    | Must also meet<br>parameter 42     |

|              |                                                           |                   |                                       |                         | 10                                        | _    | _      | ns    |                                    |

| 41*          | TT0L                                                      | T0CKI Low Pulse   | Width No Prescaler                    |                         | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet                     |

|              |                                                           |                   |                                       | With Prescaler          | 10                                        | _    | _      | ns    | parameter 42                       |

| 42*          | TT0P                                                      | T0CKI Period      |                                       | No Prescaler            | Tcy + 40                                  | _    | _      | ns    |                                    |

|              |                                                           |                   |                                       | With Prescaler          | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —    | —      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H                                                      | T1CKI High        | Synchronous, Pre                      | scaler = 1              | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet                     |

|              |                                                           | Time              | Synchronous,<br>Prescaler = 2,4,8     | PIC16F818/819           | 15                                        | _    | _      | ns    | parameter 47                       |

|              |                                                           |                   |                                       | PIC16LF818/819          | 25                                        | _    | _      | ns    | -                                  |

|              |                                                           |                   | Asynchronous                          | PIC16F818/819           | 30                                        |      | _      | ns    |                                    |

|              |                                                           |                   |                                       | PIC16LF818/819          | 50                                        | _    | _      | ns    |                                    |

| 46*          | T⊤1L                                                      | T1CKI Low Time    | Synchronous, Prescaler = 1            |                         | 0.5 Tcy + 20                              |      | —      | ns    | Must also meet                     |

|              |                                                           |                   | Synchronous,<br>Prescaler = 2,4,8     | PIC16 <b>F</b> 818/819  | 15                                        | —    | —      | ns    | parameter 47                       |

|              |                                                           |                   |                                       | PIC16LF818/819          | 25                                        | _    | —      | ns    |                                    |

|              |                                                           |                   | Asynchronous                          | PIC16 <b>F</b> 818/819  | 30                                        | _    | —      | ns    |                                    |

|              |                                                           |                   |                                       | PIC16LF818/819          | 50                                        | —    | _      | ns    |                                    |

| 47*          | Ττ1Ρ                                                      | Period            | Synchronous                           | PIC16 <b>F</b> 818/819  | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale<br>value (1, 2, 4, 8) |

|              |                                                           |                   |                                       | PIC16 <b>LF</b> 818/819 | Greater of:<br>50 or <u>Tcy + 40</u><br>N |      |        |       | N = prescale value $(1, 2, 4, 8)$  |

|              |                                                           |                   | Asynchronous                          | PIC16 <b>F</b> 818/819  | 60                                        | —    | —      | ns    |                                    |

|              |                                                           |                   |                                       | PIC16 <b>LF</b> 818/819 | 100                                       | _    | _      | ns    |                                    |

|              | FT1 Timer1 Oscillator Input I<br>(Oscillator enabled by s |                   |                                       |                         |                                           | —    | 32.768 | kHz   |                                    |

| 48           | TCKEZTMR1                                                 | Delay from Extern | xternal Clock Edge to Timer Increment |                         | 2 Tosc                                    | _    | 7 Tosc | _     |                                    |

| TABLE 15-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

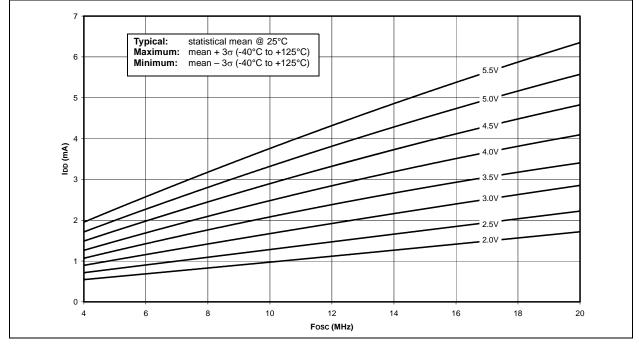

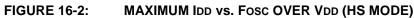

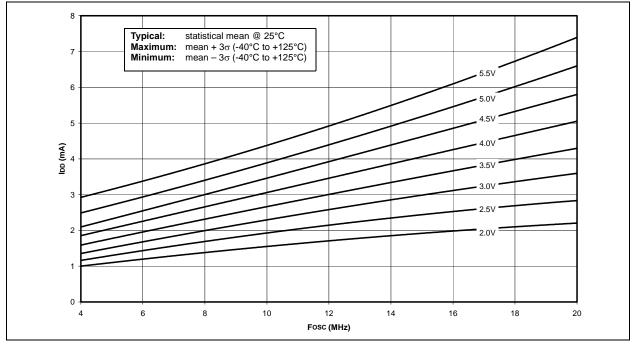

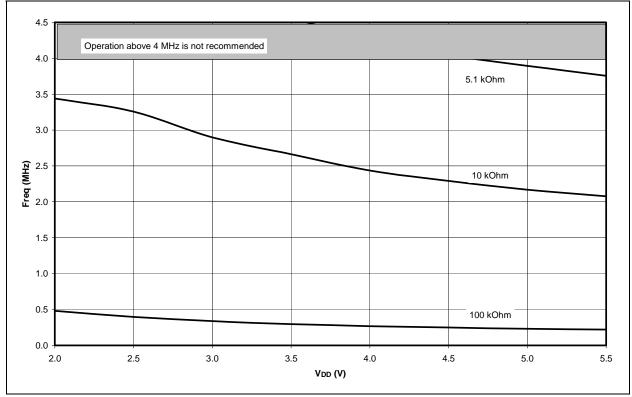

### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

### APPENDIX A: REVISION HISTORY

#### Revision A (May 2002)

Original version of this data sheet.

#### **Revision B (August 2002)**

Added INTRC section. PWRT and BOR are independent of each other. Revised program memory text and code routine. Added QFN package. Modified PORTB diagrams.

#### **Revision C (November 2002)**

Added various new feature descriptions. Added internal RC oscillator specifications. Added low-power Timer1 specifications and RTC application example.

#### **Revision D (November 2003)**

Updated IRCF bit modification information and changed the INTOSC stabilization delay from 1 ms to 4 ms in Section 4.0 "Oscillator Configurations". Updated Section 12.17 "In-Circuit Serial Programming" to clarify LVP programming. In Section 15.0 "Electrical Characteristics", the DC Characteristics (Section 15.2 and Section 15.3) have been updated to include the Typ, Min and Max values and Table 15-1 "External Clock Timing Requirements" has been updated.

#### **Revision E (September 2004)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in Section 16.0 "DC and AC Characteristics Graphs and Tables" have been updated and there have been minor corrections to the data sheet text.

#### **Revision F (November 2011)**

This revision updated **Section 17.0** "Packaging Information".

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

#### TABLE B-1: DIFFERENCES BETWEEN THE PIC16F818 AND PIC16F819

| Features                            | PIC16F818 | PIC16F819 |  |  |

|-------------------------------------|-----------|-----------|--|--|

| Flash Program Memory (14-bit words) | 1K        | 2K        |  |  |

| Data Memory (bytes)                 | 128       | 256       |  |  |

| EEPROM Data Memory (bytes)          | 128       | 256       |  |  |

NOTES:

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response  | Total Pages Sent                          |

|------------|----------------------------------------------------|-------------------------------------------|

| From       | Name                                               |                                           |

|            | Company                                            |                                           |

|            | Address                                            |                                           |

|            | City / State / ZIP / Country                       |                                           |

|            | Telephone: ()                                      | FAX: ()                                   |

|            | cation (optional):                                 |                                           |

| Would      | d you like a reply?YN                              |                                           |

| Devic      | e: PIC16F818/819                                   | Literature Number: DS39598F               |

| Ques       | tions:                                             |                                           |

| 1. V       | /hat are the best features of this document?       |                                           |

|            |                                                    |                                           |

| _          |                                                    |                                           |

| 2. H       | ow does this document meet your hardware and s     | oftware development needs?                |

| _          |                                                    |                                           |

|            |                                                    |                                           |

| 3. D       | o you find the organization of this document easy  | to follow? If not, why?                   |

|            |                                                    |                                           |

| 4. W       | /hat additions to the document do you think would  | enhance the structure and subject?        |

|            |                                                    |                                           |

|            |                                                    |                                           |

| 5. V       | /hat deletions from the document could be made v   | vithout affecting the overall usefulness? |

|            |                                                    |                                           |

| _          |                                                    |                                           |

| 6. Is      | there any incorrect or misleading information (whe | at and where)?                            |

|            |                                                    |                                           |

|            |                                                    |                                           |

| 7. H       | ow would you improve this document?                |                                           |

| _          |                                                    |                                           |

| _          |                                                    |                                           |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2001-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769393

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.