Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf819-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7      | Bit 6                                                                       | Bit 5          | Bit 4           | Bit 3           | Bit 2         | Bit 1         | Bit 0     | Value on<br>POR, BOR | Details on page: |

|----------------------|---------|------------|-----------------------------------------------------------------------------|----------------|-----------------|-----------------|---------------|---------------|-----------|----------------------|------------------|

| Bank 0               |         |            |                                                                             |                |                 |                 |               |               |           |                      |                  |

| 00h <sup>(1)</sup>   | INDF    | Addressir  | ng this locati                                                              | on uses cont   | ents of FSR to  | o address dat   | a memory (n   | ot a physical | register) | 0000 0000            | 23               |

| 01h                  | TMR0    | Timer0 M   | odule Regis                                                                 | ter            |                 |                 |               |               |           | XXXX XXXX            | 53, 17           |

| 02h <sup>(1)</sup>   | PCL     | Program    | Counter's (F                                                                | PC) Least Sig  | nificant Byte   |                 |               |               |           | 0000 0000            | 23               |

| 03h <sup>(1)</sup>   | STATUS  | IRP        | RP1                                                                         | RP0            | то              | PD              | Z             | DC            | С         | 0001 1xxx            | 16               |

| 04h <sup>(1)</sup>   | FSR     | Indirect D | ata Memory                                                                  | Address Poi    | nter            |                 |               |               |           | xxxx xxxx            | 23               |

| 05h                  | PORTA   | PORTA D    | Data Latch w                                                                | hen written; F | PORTA pins w    | hen read        |               |               |           | xxx0 0000            | 39               |

| 06h                  | PORTB   | PORTB D    | Data Latch w                                                                | hen written; I | PORTB pins v    | when read       |               |               |           | xxxx xxxx            | 43               |

| 07h                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | _                    | _                |

| 08h                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | —                    | —                |

| 09h                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | —                    | —                |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _          | _                                                                           |                | Write Buffer    | for the upper   | 5 bits of the | Program Cou   | unter     | 0 0000               | 23               |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE        | PEIE                                                                        | TMR0IE         | INTE            | RBIE            | TMR0IF        | INTF          | RBIF      | 0000 000x            | 18               |

| 0Ch                  | PIR1    | _          | ADIF                                                                        |                | _               | SSPIF           | CCP1IF        | TMR2IF        | TMR1IF    | -0 0000              | 20               |

| 0Dh                  | PIR2    | _          | _                                                                           | _              | EEIF            | _               | _             | _             | _         | 0                    | 21               |

| 0Eh                  | TMR1L   | Holding R  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |                 |                 |               |               |           |                      | 57               |

| 0Fh                  | TMR1H   | Holding R  | Register for tl                                                             | he Most Sign   | ificant Byte of | f the 16-bit TM | /IR1 Register | r             |           | xxxx xxxx            | 57               |

| 10h                  | T1CON   | _          | _                                                                           | T1CKPS1        | T1CKPS0         | T1OSCEN         | T1SYNC        | TMR1CS        | TMR10N    | 00 0000              | 57               |

| 11h                  | TMR2    | Timer2 M   | odule Regis                                                                 | ter            |                 |                 |               |               |           | 0000 0000            | 63               |

| 12h                  | T2CON   | _          | TOUTPS3                                                                     | TOUTPS2        | TOUTPS1         | TOUTPS0         | TMR2ON        | T2CKPS1       | T2CKPS0   | -000 0000            | 64               |

| 13h                  | SSPBUF  | Synchron   | ous Serial P                                                                | ort Receive I  | Buffer/Transm   | it Register     |               |               |           | XXXX XXXX            | 71, 76           |

| 14h                  | SSPCON  | WCOL       | SSPOV                                                                       | SSPEN          | CKP             | SSPM3           | SSPM2         | SSPM1         | SSPM0     | 0000 0000            | 73               |

| 15h                  | CCPR1L  | Capture/0  | Compare/PW                                                                  | /M Register (  | LSB)            |                 |               |               |           | XXXX XXXX            | 66, 67, 68       |

| 16h                  | CCPR1H  | Capture/0  | Compare/PW                                                                  | /M Register (  | MSB)            |                 |               |               |           | XXXX XXXX            | 66, 67, 68       |

| 17h                  | CCP1CON | _          | _                                                                           | CCP1X          | CCP1Y           | CCP1M3          | CCP1M2        | CCP1M1        | CCP1M0    | 00 0000              | 65               |

| 18h                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | _                    | _                |

| 19h                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | _                    | _                |

| 1Ah                  | —       | Unimplen   | Unimplemented —                                                             |                |                 |                 |               |               | _         |                      |                  |

| 1Bh                  | _       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | —                    | _                |

| 1Ch                  | —       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | —                    | _                |

| 1Dh                  | _       | Unimplen   | nented                                                                      |                |                 |                 |               |               |           | —                    | _                |

| 1Eh                  | ADRESH  | A/D Resu   | ılt Register ⊦                                                              | ligh Byte      |                 |                 |               |               |           | XXXX XXXX            | 81               |

| 1Fh                  | ADCON0  | ADCS1      | ADCS0                                                                       | CHS2           | CHS1            | CHS0            | GO/DONE       | _             | ADON      | 0000 00-0            | 81               |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register that contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the external INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### **REGISTER 2-2: OPTION\_REG: OPTION REGISTER (ADDRESS 81h, 181h)**

|       | R/W-1                                                                      | R/W-1                              | R/W-1                                          | R/W-1         | R/W-1          | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|-------|----------------------------------------------------------------------------|------------------------------------|------------------------------------------------|---------------|----------------|-------|-------|-------|--|--|--|--|

|       | RBPU                                                                       | INTEDG                             | TOCS                                           | TOSE          | PSA            | PS2   | PS1   | PS0   |  |  |  |  |

|       | bit 7                                                                      |                                    |                                                |               |                |       |       | bit ( |  |  |  |  |

| 7     | RBPU: PO                                                                   | RTB Pull-up                        | Enable bit                                     |               |                |       |       |       |  |  |  |  |

|       |                                                                            | B pull-ups are<br>B pull-ups are   |                                                | individual po | ort latch valu | ues   |       |       |  |  |  |  |

| t 6   | INTEDG: I                                                                  | nterrupt Edge                      | e Select bit                                   |               |                |       |       |       |  |  |  |  |

|       |                                                                            | pt on rising e<br>pt on falling e  |                                                |               |                |       |       |       |  |  |  |  |

| t 5   | TOCS: TMI                                                                  | R0 Clock Sou                       | irce Select bi                                 | it            |                |       |       |       |  |  |  |  |

|       |                                                                            | tion on T0CK<br>al instruction (   | •                                              | CLKO)         |                |       |       |       |  |  |  |  |

| t 4   | TOSE: TM                                                                   | R0 Source Ec                       | lge Select bit                                 | t             |                |       |       |       |  |  |  |  |

|       |                                                                            | nent on high-t<br>nent on low-to   |                                                |               | •              |       |       |       |  |  |  |  |

| t 3   | PSA: Pres                                                                  | caler Assignn                      | nent bit                                       |               |                |       |       |       |  |  |  |  |

|       |                                                                            | aler is assigne<br>aler is assigne |                                                |               |                |       |       |       |  |  |  |  |

| t 2-0 | PS2:PS0: Prescaler Rate Select bits                                        |                                    |                                                |               |                |       |       |       |  |  |  |  |

|       | Bit Value                                                                  | TMR0 Rate<br>1 : 2                 | WDT Rate                                       |               |                |       |       |       |  |  |  |  |

|       | 001                                                                        | 1:4                                | 1:2                                            |               |                |       |       |       |  |  |  |  |

|       | 010<br>011                                                                 | 1 : 8<br>1 : 16                    | 1:4<br>1:8                                     |               |                |       |       |       |  |  |  |  |

|       | 100                                                                        | 1:32                               | 1:16                                           |               |                |       |       |       |  |  |  |  |

|       | 101                                                                        | 1:64                               | 1:32                                           |               |                |       |       |       |  |  |  |  |

|       | 110<br>111                                                                 | 1 : 128<br>1 : 256                 | 1 : 64<br>1 : 128                              |               |                |       |       |       |  |  |  |  |

|       |                                                                            |                                    |                                                |               |                |       |       |       |  |  |  |  |

|       | Legend:                                                                    |                                    |                                                |               |                |       |       |       |  |  |  |  |

|       | R = Reada                                                                  | able bit                           | W = Writable bit U = Unimplemented bit, read a |               |                |       |       | '0'   |  |  |  |  |

|       | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                    |                                                |               |                |       |       |       |  |  |  |  |

## 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| BANKSEL | EEADRH   |       | ; | Select Bank of EEADRH |

|---------|----------|-------|---|-----------------------|

| MOVF    | ADDRH, W | 1     | ; |                       |

| MOVWF   | EEADRH   |       | ; | MS Byte of Program    |

|         |          |       | ; | Address to read       |

| MOVF    | ADDRL, W | T     | ; |                       |

| MOVWF   | EEADR    |       | ; | LS Byte of Program    |

|         |          |       | ; | Address to read       |

| BANKSEL | EECON1   |       | ; | Select Bank of EECON1 |

| BSF     | EECON1,  | EEPGD | ; | Point to PROGRAM      |

|         |          |       | ; | memory                |

| BSF     | EECON1,  | RD    | ; | EE Read               |

|         |          |       | ; |                       |

| NOP     |          |       | ; | Any instructions      |

|         |          |       | ; | here are ignored as   |

| NOP     |          |       | ; | program memory is     |

|         |          |       | ; | read in second cycle  |

|         |          |       | ; | after BSF EECON1,RD   |

| BANKSEL | EEDATA   |       | ; | Select Bank of EEDATA |

| MOVF    | EEDATA,  | W     | ; | DATAL = EEDATA        |

| MOVWF   | DATAL    |       | ; |                       |

| MOVF    | EEDATH,  | W     | ; | DATAH = EEDATH        |

| MOVWF   | DATAH    |       | ; |                       |

| 1       |          |       |   |                       |

### 3.6 Erasing Flash Program Memory

The minimum erase block is 32 words. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 32 words of program memory is erased. The Most Significant 11 bits of the EEADRH:EEADR point to the block being erased. EEADR< 4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the erase takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

#### 3.6.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load EEADRH:EEADR with address of row being erased.

- Set EEPGD bit to point to program memory; set WREN bit to enable writes and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase.

| EXAMPLE 3-4: | ERASING A FLASH PROGRAM MEMORY ROW |

|--------------|------------------------------------|

|--------------|------------------------------------|

|           | BANKSEL | EEADRH      | ;        | Select Bank of EEADRH                                |

|-----------|---------|-------------|----------|------------------------------------------------------|

|           | MOVF    | ADDRH, W    | ;        |                                                      |

|           | MOVWF   | EEADRH      | ;        | MS Byte of Program Address to Erase                  |

|           | MOVF    | ADDRL, W    | ;        |                                                      |

|           | MOVWF   | EEADR       | ;        | LS Byte of Program Address to Erase                  |

| ERASE ROW |         |             |          |                                                      |

| _         | BANKSEL | EECON1      | ;        | Select Bank of EECON1                                |

|           | BSF     | EECON1, EEE | GD ;     | Point to PROGRAM memory                              |

|           | BSF     | EECON1, WRE | EN ;     | Enable Write to memory                               |

|           | BSF     | EECON1, FRE | EE ;     | Enable Row Erase operation                           |

| ;         |         |             |          |                                                      |

|           | BCF     | INTCON, GIE | s;       | Disable interrupts (if using)                        |

|           | MOVLW   | 55h         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write 55h                                            |

|           | MOVLW   | AAh         | ;        |                                                      |

|           | MOVWF   | EECON2      | ;        | Write AAh                                            |

|           | BSF     | EECON1, WR  | ;        | Start Erase (CPU stall)                              |

|           | NOP     |             | ;        | Any instructions here are ignored as processor       |

|           |         |             | ;        | halts to begin Erase sequence                        |

|           | NOP     |             | ;        | processor will stop here and wait for Erase complete |

|           |         |             | ;        | after Erase processor continues with 3rd instruction |

|           | BCF     | EECON1, FRE | EE ;     | Disable Row Erase operation                          |

|           | BCF     | EECON1, WRE | EN ;     | Disable writes                                       |

|           | BSF     | INTCON, GIE | ·<br>; 2 | Enable interrupts (if using)                         |

|           |         |             |          |                                                      |

#### EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM TIMER0 TO WDT

| BANKSEL | OPTION_REG  | ; | Select Bank of OPTION_REG                 |

|---------|-------------|---|-------------------------------------------|

| MOVLW   | b'xx0x0xxx' | ; | Select clock source and prescale value of |

| MOVWF   | OPTION_REG  | ; | other than 1:1                            |

| BANKSEL | TMR0        | ; | Select Bank of TMR0                       |

| CLRF    | TMR0        | ; | Clear TMR0 and prescaler                  |

| BANKSEL | OPTION_REG  | ; | Select Bank of OPTION_REG                 |

| MOVLW   | b'xxxx1xxx' | ; | Select WDT, do not change prescale value  |

| MOVWF   | OPTION_REG  |   |                                           |

| CLRWDT  |             | ; | Clears WDT and prescaler                  |

| MOVLW   | b'xxxx1xxx' | ; | Select new prescale value and WDT         |

| MOVWF   | OPTION_REG  |   |                                           |

|         |             |   |                                           |

#### EXAMPLE 6-2: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0

| CLRWDT  |             | ; | Clear WDT and prescaler   |

|---------|-------------|---|---------------------------|

| BANKSEL | OPTION_REG  | ; | Select Bank of OPTION_REG |

| MOVLW   | b'xxxx0xxx' | ; | Select TMR0, new prescale |

| MOVWF   | OPTION_REG  | ; | value and clock source    |

|         |             |   |                           |

### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7     | Bit 6       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|-----------|-------------|--------|-------|-------|--------|-------|-------|----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 Mo | odule Regis | ster   |       |       |        |       |       | xxxx xxxx            | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE       | PEIE        | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF  | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU      | INTEDG      | TOCS   | T0SE  | PSA   | PS2    | PS1   | PS0   | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

# 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 Interrupt Enable bit, TMR1IE (PIE1<0>).

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

# 7.1 Timer1 Operation

Timer1 can operate in one of three modes:

- as a timer

- as a synchronous counter

- · as an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP1 module as the special event trigger (see **Section 9.1** "**Capture Mode**"). Register 7-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB6/T1OSO/T1CKI/PGC and RB7/T1OSI/ PGD pins become inputs. That is, the TRISB<7:6> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### REGISTER 7-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON |

| bit 7 |     |         |         |         |        |        | bit 0  |

| bit 7-6 | Unimplemented: Read                                                                   | <b>as</b> '0'              |                                        |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|----------------------------|----------------------------------------|--|--|--|--|--|--|--|

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                              |                            |                                        |  |  |  |  |  |  |  |

|         | 11 = 1:8 Prescale value                                                               | ł                          |                                        |  |  |  |  |  |  |  |

|         | 10 = 1:4 Prescale value                                                               |                            |                                        |  |  |  |  |  |  |  |

|         | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                    |                            |                                        |  |  |  |  |  |  |  |

| bit 3   |                                                                                       |                            |                                        |  |  |  |  |  |  |  |

| DIT 3   | T1OSCEN: Timer1 Osc                                                                   |                            |                                        |  |  |  |  |  |  |  |

|         | 1 = Oscillator is enabled<br>0 = Oscillator is shut-off                               | -                          | s turned off to eliminate power drain) |  |  |  |  |  |  |  |

| bit 2   |                                                                                       |                            |                                        |  |  |  |  |  |  |  |

|         | <b>T1SYNC:</b> Timer1 External Clock Input Synchronization Control bit<br>TMR1CS = 1: |                            |                                        |  |  |  |  |  |  |  |

|         | 1 = Do not synchronize external clock input                                           |                            |                                        |  |  |  |  |  |  |  |

|         | 0 = Synchronize externa                                                               | al clock input             |                                        |  |  |  |  |  |  |  |

|         | <u>TMR1CS = 0:</u>                                                                    |                            |                                        |  |  |  |  |  |  |  |

|         | This bit is ignored. Time                                                             | er1 uses the internal cloc | k when TMR1CS = 0.                     |  |  |  |  |  |  |  |

| bit 1   | TMR1CS: Timer1 Clock Source Select bit                                                |                            |                                        |  |  |  |  |  |  |  |

|         | <ul> <li>1 = External clock from</li> <li>0 = Internal clock (Fost</li> </ul>         | •                          | /PGC (on the rising edge)              |  |  |  |  |  |  |  |

| bit 0   | TMR1ON: Timer1 On bi                                                                  |                            |                                        |  |  |  |  |  |  |  |

|         | 1 = Enables Timer1                                                                    |                            |                                        |  |  |  |  |  |  |  |

|         | 0 = Stops Timer1                                                                      |                            |                                        |  |  |  |  |  |  |  |

|         | Legend:                                                                               |                            |                                        |  |  |  |  |  |  |  |

|         | R = Readable bit                                                                      | W = Writable bit           | U = Unimplemented bit, read as '0'     |  |  |  |  |  |  |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 7.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

## 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

# 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

# 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6 "Timer1 Oscillator**"), gives users the option to include RTC functionality in their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

| REGISTER 8-1: | T2CON: TIM                                         | ER2 CONTROL     | REGISTER (      | ADDRESS       | 12h)      |              |         |

|---------------|----------------------------------------------------|-----------------|-----------------|---------------|-----------|--------------|---------|

|               | U-0 R/                                             | /W-0 R/W-0      | R/W-0           | R/W-0         | R/W-0     | R/W-0        | R/W-0   |

|               | — TOL                                              | JTPS3 TOUTPS    | 2 TOUTPS1       | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |

|               | bit 7                                              |                 |                 |               |           |              | bit 0   |

| bit 7         | Unimplement                                        | ed: Read as '0' |                 |               |           |              |         |

| bit 6-3       | TOUTPS3:TO                                         | UTPS0: Timer2 O | utput Postscale | e Select bits |           |              |         |

|               | 0000 = 1:1 Pos<br>0001 = 1:2 Pos<br>0010 = 1:3 Pos | stscale         |                 |               |           |              |         |

|               | •                                                  |                 |                 |               |           |              |         |

|               | •                                                  |                 |                 |               |           |              |         |

|               | 1111 = 1:16 P                                      | ostscale        |                 |               |           |              |         |

| bit 2         | TMR2ON: Tim                                        | er2 On bit      |                 |               |           |              |         |

|               | 1 = Timer2 is<br>0 = Timer2 is                     |                 |                 |               |           |              |         |

| bit 1-0       | T2CKPS1:T2C                                        | KPS0: Timer2 Cl | ock Prescale S  | elect bits    |           |              |         |

|               | 00 = Prescaler<br>01 = Prescaler<br>1x = Prescaler | is 4            |                 |               |           |              |         |

|               | Legend:                                            |                 |                 |               |           |              | ]       |

|               | R = Readable                                       | bit W :         | = Writable bit  | U = Unim      | plemented | bit. read as | '0'     |

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7  | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      |      | e on<br>other<br>sets |

|-------------------------|--------|--------|-----------|---------|---------|---------|--------|---------|---------|---------------|------|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE      | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000 | 000u                  |

| 0Ch                     | PIR1   | —      | ADIF      | _       | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0           | 0000 | - 0  | 0000                  |

| 8Ch                     | PIE1   | _      | ADIE      | _       | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0           | 0000 | - 0  | 0000                  |

| 11h                     | TMR2   | Timer2 | Module Re | egister |         |         |        |         |         | 0000          | 0000 | 0000 | 0000                  |

| 12h                     | T2CON  | —      | TOUTPS3   | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000 | 0000                  |

| 92h                     | PR2    | Timer2 | Period Re | gister  |         |         |        |         |         | 1111          | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

# 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB2 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word register.

Additional information on the CCP module is available in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023) and in Application Note AN594, "Using the CCP Module(s)" (DS00594).

### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### **REGISTER 9-1:** CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0                              | U-0        | R/W-0        | R/W-0        | R/W-0                     | R/W-0        | R/W-0          | R/W-0       |

|----------------------------------|------------|--------------|--------------|---------------------------|--------------|----------------|-------------|

| —                                | —          | CCP1X        | CCP1Y        | CCP1M3                    | CCP1M2       | CCP1M1         | CCP1M0      |

| bit 7                            |            |              |              |                           |              |                | bit 0       |

|                                  |            |              |              |                           |              |                |             |

| Unimpleme                        |            |              |              |                           |              |                |             |

| CCP1X:CCI                        | P1Y: PWM   | Least Signi  | ficant bits  |                           |              |                |             |

| <u>Capture mo</u><br>Unused.     | <u>de:</u> |              |              |                           |              |                |             |

| <u>Compare mo</u><br>Unused.     | ode:       |              |              |                           |              |                |             |

| <u>PWM mode:</u><br>These bits a | -          | LSbs of the  | PWM duty     | cycle. The e              | eight MSbs a | re found in (  | CCPRxL.     |

| CCP1M3:CO                        | CP1M0: CC  | P1 Mode S    | elect bits   |                           |              |                |             |

| 0000 <b>= Cap</b>                | ture/Compa | are/PWM di   | sabled (res  | ets CCP1 m                | odule)       |                |             |

| 0100 = Cap                       | ture mode, | every fallin | g edge       |                           |              |                |             |

| 0101 <b>= Cap</b>                |            |              |              |                           |              |                |             |

| 0110 = Cap                       |            | •            | • •          |                           |              |                |             |

| 0111 = Cap                       |            | •            | • •          | (CCP1IF bit               | ic cot)      |                |             |

|                                  |            | · ·          |              | h (CCP1IF b               | ,            |                |             |

| 1010 <b>= Com</b>                |            |              |              | terrupt on ma             |              | F bit is set,  | CCP1 pin is |

| 1011 <b>= Com</b>                | npare mode |              |              | t (CCP1IF b<br>conversion |              |                |             |

| 11xx = PWI                       |            |              |              |                           | ,            |                | ,           |

|                                  |            |              |              |                           |              |                |             |

|                                  |            |              |              |                           |              |                |             |

| Legend:                          |            |              |              |                           |              |                |             |

| <b>Legend:</b><br>R = Readab     | le bit     | W = V        | Vritable bit | U = Uni                   | mplemented   | l bit, read as | s 'O'       |

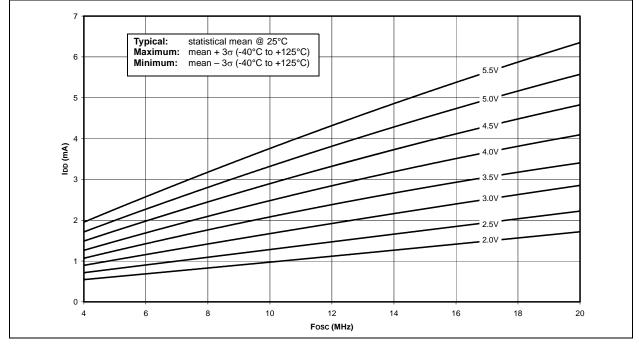

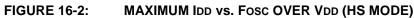

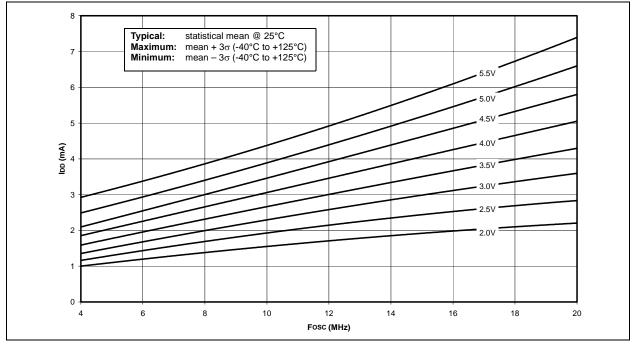

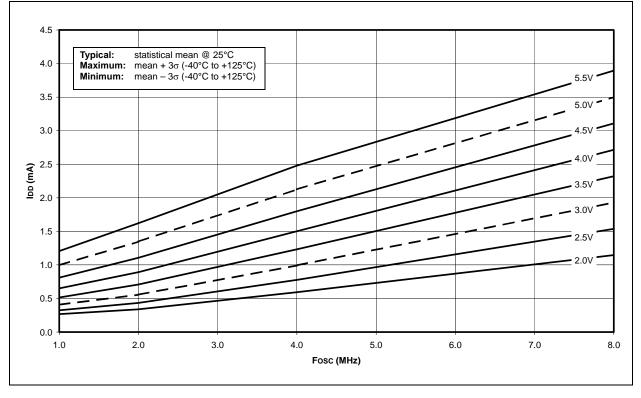

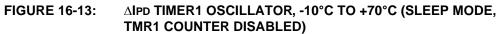

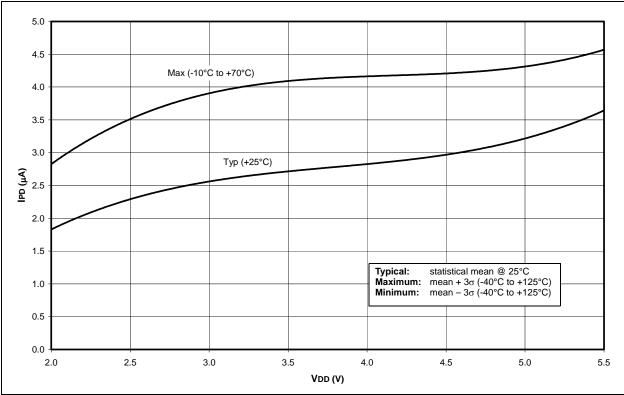

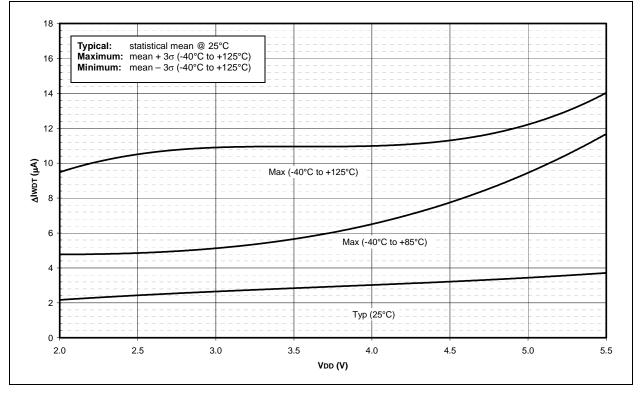

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

FIGURE 16-7: TYPICAL IDD vs. VDD, -40°C TO +125°C, 1 MHz TO 8 MHz (RC\_RUN MODE, ALL PERIPHERALS DISABLED)

FIGURE 16-8: MAXIMUM IDD vs. VDD, -40°C TO +125°C, 1 MHz TO 8 MHz (RC\_RUN MODE, ALL PERIPHERALS DISABLED)

# INDEX

|   | L |

|---|---|

| - | ٩ |

| A/D                                                  |       |

|------------------------------------------------------|-------|

| Acquisition Requirements                             | 84    |

| ADIF Bit                                             |       |

| Analog-to-Digital Converter                          | 81    |

| Associated Registers                                 |       |

| Calculating Acquisition Time                         |       |

| Configuring Analog Port Pins                         | 85    |

| Configuring the Interrupt                            |       |

| Configuring the Module                               | 83    |

| Conversion Clock                                     | 85    |

| Conversion Requirements                              | . 140 |

| Conversions                                          | 86    |

| Converter Characteristics                            | . 139 |

| Delays                                               | 84    |

| Effects of a Reset                                   |       |

| GO/DONE Bit                                          | 83    |

| Internal Sampling Switch (Rss) Impedance             | 84    |

| Operation During Sleep                               |       |

| Result Registers                                     | 86    |

| Source Impedance                                     | 84    |

| Time Delays                                          | 84    |

| Use of the CCP Trigger                               | 87    |

| Absolute Maximum Ratings                             | . 115 |

| ACK                                                  | 77    |

| ADCON0 Register                                      | 81    |

| ADCON1 Register                                      | 81    |

| ADRESH Register 1                                    | 3, 81 |

| ADRESH, ADRESL Register Pair                         | 83    |

| ADRESL Register1                                     | 4, 81 |

| Application Notes                                    |       |

| AN556 (Implementing a Table Read)                    | 23    |

| AN578 (Use of the SSP Module in the I <sup>2</sup> C |       |

| Multi-Master Environment)                            | 71    |

| AN607 (Power-up Trouble Shooting)                    |       |

| Assembler                                            |       |

| MPASM Assembler                                      | . 112 |

| в                                                    |       |

| В                                            |

|----------------------------------------------|

| BF Bit                                       |

| Block Diagrams                               |

| A/D83                                        |

| Analog Input Model84                         |

| Capture Mode Operation66                     |

| Compare Mode Operation67                     |

| In-Circuit Serial Programming Connections101 |

| Interrupt Logic96                            |

| On-Chip Reset Circuit91                      |

| PIC16F818/8196                               |

| PWM68                                        |

| RA0/AN0:RA1/AN1 Pins40                       |

| RA2/AN2/Vref- Pin40                          |

| RA3/AN3/Vref+ Pin40                          |

| RA4/ <u>AN4/T</u> 0CKI Pin40                 |

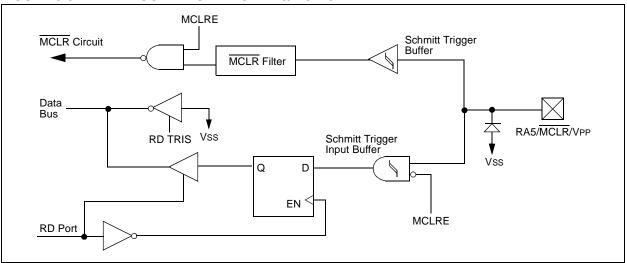

| RA5/MCLR/Vpp Pin41                           |

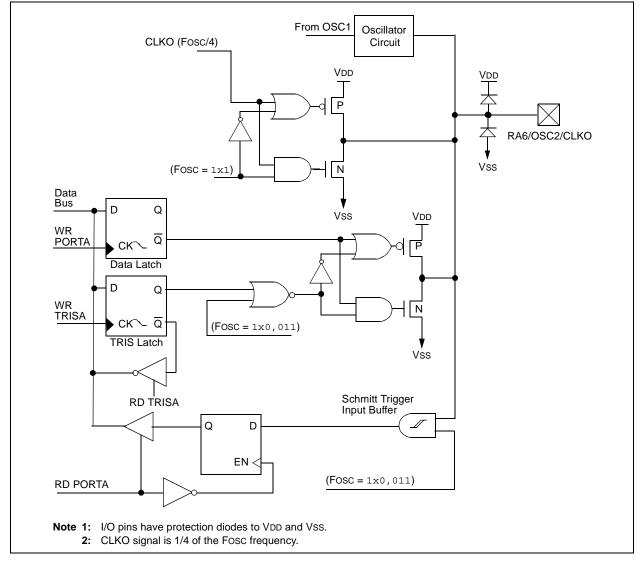

| RA6/OSC2/CLKO Pin41                          |

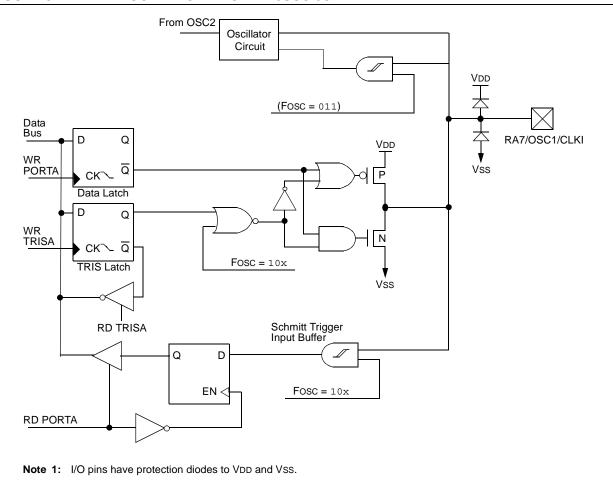

| RA7/OSC1/CLKI Pin42                          |

| RB0 Pin45                                    |

| RB1 Pin46                                    |

| RB2 Pin47                                    |

| RB3 Pin48                                    |

| RB4 Pin                                      |

| RB5 Pin50                                    |

| RB6 Pin51                                |

|------------------------------------------|

| RB7 Pin52                                |

| Recommended MCLR Circuit                 |

| SSP in I <sup>2</sup> C Mode76           |

| SSP in SPI Mode74                        |

| System Clock 38                          |

| Timer0/WDT Prescaler                     |

| Timer1                                   |

| Timer2                                   |

| Watchdog Timer (WDT) 98                  |

| BOR. See Brown-out Reset.                |

| Brown-out Reset (BOR) 89, 91, 92, 93, 94 |

# С

| C Compilers                               |     |

|-------------------------------------------|-----|

| MPLAB C18 1                               | 12  |

| Capture/Compare/PWM (CCP)                 | 65  |

| Capture Mode                              |     |

| CCP Prescaler                             |     |

| Pin Configuration                         |     |

| Software Interrupt                        |     |

| Timer1 Mode Selection                     |     |

| Capture, Compare and Timer1               |     |

| Associated Registers                      | 67  |

| CCP1IF                                    |     |

| CCPR1                                     |     |

| CCPR1H:CCPR1L                             |     |

| Compare Mode                              |     |

| Pin Configuration                         |     |

| Software Interrupt Mode                   |     |

| Special Event Trigger                     |     |

| Special Event Trigger Output of CCP1      |     |

| Timer1 Mode Selection                     |     |

| PWM and Timer2                            | •.  |

| Associated Registers                      | 69  |

| PWM Mode                                  |     |

| Duty Cycle                                |     |

| Example Frequencies/Resolutions           | 69  |

| Period                                    |     |

| Setup for Operation                       |     |

| Timer Resources                           |     |

| CCP1M0 Bit                                |     |

| CCP1M1 Bit                                |     |

| CCP1M2 Bit                                |     |

| CCP1M3 Bit                                |     |

| CCP1X Bit                                 |     |

| CCP1Y Bit                                 |     |

| CCPR1H Register                           |     |

| CCPR1L Register                           |     |

| Code Examples                             | 00  |

| Changing Between Capture Prescalers       | 66  |

| Changing Prescaler Assignment from Timer0 | 00  |

| to WDT                                    | 55  |

| Changing Prescaler Assignment from WDT    |     |

| to Timer0                                 | 55  |

| Clearing RAM Using Indirect Addressing    |     |

| Erasing a Flash Program Memory Row        |     |

| Implementing a Real-Time Clock Using a    | 20  |

| Timer1 Interrupt Service                  | 62  |

| Initializing PORTA                        |     |

| Reading a 16-Bit Free Running Timer       |     |

| Reading Data EEPROM                       |     |

| Reading Flash Program Memory              | 28  |

| Saving Status and W Registers in RAM      |     |

| Writing a 16-Bit Free Running Timer       |     |

| Writing to Data EEPROM                    |     |

|                                           | ~ ' |

| Timer157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Associated Registers62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Capacitor Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Counter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operation in Asynchronous Counter Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operation in Synchronized Counter Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operation in Timer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Oscillator Layout Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Resetting Register Pair (TMR1H, TMR1L)61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Resetting Using a CCP Trigger Output61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TMR1H59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMR1L59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |