Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 10MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 5x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf819-i-sstsl |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

```

FIGURE 2-3:

```

# PIC16F818 REGISTER FILE MAP

|                                 | ddress      |                                | Address     | [                   | Address      |                                   | ddre       |

|---------------------------------|-------------|--------------------------------|-------------|---------------------|--------------|-----------------------------------|------------|

| Indirect addr.(*)               | 00h         | Indirect addr.(*)              | 80h         | Indirect addr.(*)   | 100h         | Indirect addr.(*)                 | 180        |

| TMR0                            | 01h         | OPTION_REG                     | 81h         | TMR0                | 101h         | OPTION_REG                        | 181        |

| PCL                             | 02h         | PCL                            | 82h         | PCL                 | 102h         | PCL                               | 182        |

| STATUS                          | 03h         | STATUS                         | 83h         | STATUS              | 103h         | STATUS                            | 183        |

| FSR                             | 04h         | FSR                            | 84h         | FSR                 | 104h         | FSR                               | 184        |

| PORTA                           | 05h         | TRISA                          | 85h         |                     | 105h         |                                   | 185        |

| PORTB                           | 06h         | TRISB                          | 86h         | PORTB               | 106h         | TRISB                             | 186        |

|                                 | 07h         |                                | 87h         |                     | 107h         |                                   | 187        |

|                                 | 08h         |                                | 88h         |                     | 108h<br>109h |                                   | 188        |

|                                 | 09h<br>0Ah  |                                | 89h         | PCLATH              | 1091<br>10Ah |                                   | 189        |

| PCLATH                          | 0An<br>0Bh  | PCLATH                         | 8Ah         | INTCON              | 10An<br>10Bh | PCLATH                            | 18/        |

|                                 | 0Бh<br>0Ch  |                                | 8Bh         |                     | 10Dh         |                                   | 18E        |

| PIR1                            |             | PIE1<br>PIE2                   | 8Ch         | EEDATA<br>EEADR     | 10Ch<br>10Dh | EECON1                            | 180        |

| PIR2<br>TMR1L                   | 0Dh<br>0Eh  |                                | 8Dh         |                     | 10Dh<br>10Eh | EECON2<br>Reserved <sup>(1)</sup> | 18[        |

| TMR1L<br>TMR1H                  | 0En<br>0Fh  | PCON<br>OSCCON                 | 8Eh<br>8Fh  | EEDATH<br>EEADRH    | 10En<br>10Fh | Reserved <sup>(1)</sup>           | 18E<br>18F |

| TICON                           | 10h         | OSCTUNE                        |             | EEADKI              | 110h         | Reserved                          | 186        |

| TMR2                            | 1011<br>11h | USCIDINE                       | 90h<br>91h  |                     | 11011        |                                   | 190        |

| T2CON                           | 12h         | PR2                            | 91h<br>92h  |                     |              |                                   |            |

| SSPBUF                          | 13h         | SSPADD                         | 9211<br>93h |                     |              |                                   |            |

| SSPCON                          | 14h         | SSPSTAT                        | 931<br>94h  |                     |              |                                   |            |

| CCPR1L                          | 15h         |                                | 9411<br>95h |                     |              |                                   |            |

| CCPR1H                          | 16h         |                                | 96h         |                     |              |                                   |            |

| CCP1CON                         | 17h         |                                | 97h         |                     |              |                                   |            |

|                                 | 18h         |                                | 98h         |                     |              |                                   |            |

|                                 | 19h         |                                | 99h         |                     |              |                                   |            |

|                                 | 1Ah         |                                | 9Ah         |                     |              |                                   |            |

|                                 | 1Bh         |                                | 9Bh         |                     |              |                                   |            |

|                                 | 1Ch         |                                | 9Ch         |                     |              |                                   |            |

|                                 | 1Dh         |                                | 9Dh         |                     |              |                                   |            |

| ADRESH                          | 1Eh         | ADRESL                         | 9Eh         |                     |              |                                   |            |

| ADCON0                          | 1Fh         | ADCON1                         | 9Fh         |                     | 11Fh         |                                   | 19F        |

|                                 | 20h         | General<br>Purpose<br>Register | A0h         |                     | 120h         |                                   | 1A)        |

| General                         |             | 32 Bytes                       | BFh         |                     |              |                                   |            |

| Purpose<br>Register<br>96 Bytes |             | Accesses<br>40h-7Fh            | C0h         | Accesses<br>20h-7Fh |              | Accesses<br>20h-7Fh               |            |

| Bank 0                          | 7Fh         | Bank 1                         | FFh         | Bank 2              | 17Fh         | Bank 3                            | 1FF        |

| Unimple<br>* Not a ph           | nysical reg | ata memory locati              |             | as '0'.             |              |                                   |            |

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7      | Bit 6           | Bit 5          | Bit 4           | Bit 3           | Bit 2         | Bit 1         | Bit 0     | Value on<br>POR, BOR | Details on page: |

|----------------------|---------|------------|-----------------|----------------|-----------------|-----------------|---------------|---------------|-----------|----------------------|------------------|

| Bank 0               |         |            |                 |                |                 |                 |               |               |           |                      |                  |

| 00h <sup>(1)</sup>   | INDF    | Addressir  | ng this locati  | on uses cont   | ents of FSR to  | o address dat   | a memory (n   | ot a physical | register) | 0000 0000            | 23               |

| 01h                  | TMR0    | Timer0 M   | odule Regis     | ter            |                 |                 |               |               |           | XXXX XXXX            | 53, 17           |

| 02h <sup>(1)</sup>   | PCL     | Program    | Counter's (F    | PC) Least Sig  | nificant Byte   |                 |               |               |           | 0000 0000            | 23               |

| 03h <sup>(1)</sup>   | STATUS  | IRP        | RP1             | RP0            | то              | PD              | Z             | DC            | С         | 0001 1xxx            | 16               |

| 04h <sup>(1)</sup>   | FSR     | Indirect D | ata Memory      | Address Poi    | nter            |                 |               |               |           | xxxx xxxx            | 23               |

| 05h                  | PORTA   | PORTA D    | Data Latch w    | hen written; F | PORTA pins w    | hen read        |               |               |           | xxx0 0000            | 39               |

| 06h                  | PORTB   | PORTB D    | Data Latch w    | hen written; I | PORTB pins v    | when read       |               |               |           | xxxx xxxx            | 43               |

| 07h                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | _                    | _                |

| 08h                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | —                    | —                |

| 09h                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | —                    | —                |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _          | _               |                | Write Buffer    | for the upper   | 5 bits of the | Program Cou   | unter     | 0 0000               | 23               |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE        | PEIE            | TMR0IE         | INTE            | RBIE            | TMR0IF        | INTF          | RBIF      | 0000 000x            | 18               |

| 0Ch                  | PIR1    | _          | ADIF            |                | _               | SSPIF           | CCP1IF        | TMR2IF        | TMR1IF    | -0 0000              | 20               |

| 0Dh                  | PIR2    | _          | _               | _              | EEIF            | _               | _             | _             | _         | 0                    | 21               |

| 0Eh                  | TMR1L   | Holding R  | Register for tl | he Least Sigr  | nificant Byte c | of the 16-bit T | MR1 Registe   | r             |           | xxxx xxxx            | 57               |

| 0Fh                  | TMR1H   | Holding R  | Register for tl | he Most Sign   | ificant Byte of | f the 16-bit TM | /IR1 Register | r             |           | xxxx xxxx            | 57               |

| 10h                  | T1CON   | _          | _               | T1CKPS1        | T1CKPS0         | T1OSCEN         | T1SYNC        | TMR1CS        | TMR10N    | 00 0000              | 57               |

| 11h                  | TMR2    | Timer2 M   | odule Regis     | ter            |                 |                 |               |               |           | 0000 0000            | 63               |

| 12h                  | T2CON   | _          | TOUTPS3         | TOUTPS2        | TOUTPS1         | TOUTPS0         | TMR2ON        | T2CKPS1       | T2CKPS0   | -000 0000            | 64               |

| 13h                  | SSPBUF  | Synchron   | ous Serial P    | ort Receive I  | Buffer/Transm   | it Register     |               |               |           | XXXX XXXX            | 71, 76           |

| 14h                  | SSPCON  | WCOL       | SSPOV           | SSPEN          | CKP             | SSPM3           | SSPM2         | SSPM1         | SSPM0     | 0000 0000            | 73               |

| 15h                  | CCPR1L  | Capture/0  | Compare/PW      | /M Register (  | LSB)            |                 |               |               |           | XXXX XXXX            | 66, 67, 68       |

| 16h                  | CCPR1H  | Capture/0  | Compare/PW      | /M Register (  | MSB)            |                 |               |               |           | XXXX XXXX            | 66, 67, 68       |

| 17h                  | CCP1CON | _          | _               | CCP1X          | CCP1Y           | CCP1M3          | CCP1M2        | CCP1M1        | CCP1M0    | 00 0000              | 65               |

| 18h                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | _                    | _                |

| 19h                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | _                    | _                |

| 1Ah                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | _                    | _                |

| 1Bh                  | _       | Unimplen   | nented          |                |                 |                 |               |               |           | —                    | _                |

| 1Ch                  | —       | Unimplen   | nented          |                |                 |                 |               |               |           | —                    | _                |

| 1Dh                  | _       | Unimplen   | nented          |                |                 |                 |               |               |           | —                    | _                |

| 1Eh                  | ADRESH  | A/D Resu   | ılt Register ⊦  | ligh Byte      |                 |                 |               |               |           | XXXX XXXX            | 81               |

| 1Fh                  | ADCON0  | ADCS1      | ADCS0           | CHS2           | CHS1            | CHS0            | GO/DONE       | _             | ADON      | 0000 00-0            | 81               |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ADDRESS 0Ch)

|   | U-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|---|-------|-------|-----|-----|-------|--------|--------|--------|

|   | —     | ADIF  | —   | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| - | bit 7 |       |     |     |       |        |        | bit 0  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                                                                                                                                          |

|         | 1 = An A/D conversion completed                                                                                                                                                                                                                                                                 |

|         | <ul> <li>The A/D conversion is not complete</li> </ul>                                                                                                                                                                                                                                          |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                      |

| bit 3   | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = The SSP interrupt condition has occurred and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are a transmission/ reception has taken place.</li> <li>0 = No SSP interrupt condition has occurred</li> </ul> |

| bit 2   | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                                                                                                                                                                 |

|         | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                                                                                                                                                             |

|         | <u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred                                                                                                                                                 |

|         | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                                                                                                                                                        |

| bit 1   | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                                                                                                                                                                     |

| bit 0   | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                                                                                                                                                        |

|         | 1 = TMR1 register overflowed (must be cleared in software)                                                                                                                                                                                                                                      |

|         | 0 = TMR1 register did not overflow                                                                                                                                                                                                                                                              |

|         |                                                                                                                                                                                                                                                                                                 |

|         | Legend:                                                                                                                                                                                                                                                                                         |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.6 **PIE2** Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

#### **REGISTER 2-6:** PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS 8Dh)

|         |             |              |                 |              |          | •         |                 |       |

|---------|-------------|--------------|-----------------|--------------|----------|-----------|-----------------|-------|

|         | U-0         | U-0          | U-0             | R/W-0        | U-0      | U-0       | U-0             | U-0   |

|         | —           | —            | —               | EEIE         | —        | —         | —               |       |

|         | bit 7       |              |                 |              |          |           |                 | bit 0 |

|         |             |              |                 |              |          |           |                 |       |

| bit 7-5 | Unimpleme   | ented: Rea   | <b>d as</b> '0' |              |          |           |                 |       |

| bit 4   | EEIE: EEPF  | ROM Write    | Operation Ir    | terrupt Enal | ole bit  |           |                 |       |

|         | 1 = Enable  | EE write int | terrupt         |              |          |           |                 |       |

|         | 0 = Disable | EE write in  | terrupt         |              |          |           |                 |       |

| bit 3-0 | Unimpleme   | ented: Rea   | <b>d as</b> '0' |              |          |           |                 |       |

|         |             |              |                 |              |          |           |                 |       |

|         | Legend:     |              |                 |              |          |           |                 |       |

|         | R = Readab  | ole bit      | W = W           | ritable bit  | U = Unim | plemented | bit, read as '0 | ,     |

#### 2.2.2.7 **PIR2** Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

-n = Value at POR

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs regardless of the state of<br>its corresponding enable bit or the Global<br>Interrupt Enable bit, GIE (INTCON<7>).<br>User software should ensure the appropri-<br>ate interrupt flag bits are clear prior to<br>enabling an interrupt. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

x = Bit is unknown

'0' = Bit is cleared

#### **REGISTER 2-7:** PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

'1' = Bit is set

| $\Box X Z^{-1}$ . |           |                                 |                 | INLGUL        |         | ILCIOID LIV |     |       |

|-------------------|-----------|---------------------------------|-----------------|---------------|---------|-------------|-----|-------|

|                   | U-0       | U-0                             | U-0             | R/W-0         | U-0     | U-0         | U-0 | U-0   |

|                   |           | —                               | —               | EEIF          | _       | _           | _   |       |

|                   | bit 7     |                                 |                 |               |         |             |     | bit 0 |

|                   |           |                                 |                 |               |         |             |     |       |

| bit 7-5           | Unimplem  | ented: Rea                      | <b>d as</b> '0' |               |         |             |     |       |

| bit 4             | EEIF: EEP | ROM Write                       | Operation Ir    | nterrupt Enal | ole bit |             |     |       |

|                   |           | e EE write int<br>e EE write in |                 |               |         |             |     |       |

| bit 3-0           | Unimplem  | ented: Rea                      | <b>d as</b> '0' |               |         |             |     |       |

|                   |           |                                 |                 |               |         |             |     |       |

|                   | Legend:   |                                 |                 |               |         |             |     |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

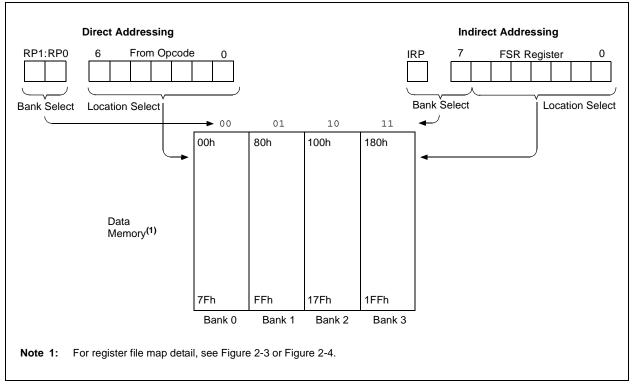

# FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

| REGISTER 3-1: | EECON1:                     | EEPROM                                   | ACCESS C                                    | ONTROL       | REGISTER      | 1 (ADDRI      | ESS 18Ch)     |             |

|---------------|-----------------------------|------------------------------------------|---------------------------------------------|--------------|---------------|---------------|---------------|-------------|

|               | R/W-x                       | U-0                                      | U-0                                         | R/W-x        | R/W-x         | R/W-0         | R/S-0         | R/S-0       |

|               | EEPGD                       |                                          | _                                           | FREE         | WRERR         | WREN          | WR            | RD          |

|               | bit 7                       |                                          |                                             |              |               |               |               | bit 0       |

| bit 7         | EEPGD: Pr                   | ogram/Data                               | EEPROM                                      | Select bit   |               |               |               |             |

|               | 0 = Access                  | es program<br>es data mei<br>fter a POR; | mory                                        | not be chang | ged while a v | write operati | on is in prog | jress.      |

| bit 6-5       | Unimplem                    | ented: Read                              | <b>d as</b> '0'                             |              |               |               |               |             |

| bit 4         | FREE: EEF                   | PROM Force                               | ed Row Eras                                 | se bit       |               |               |               |             |

|               | 1 = Erase tl<br>0 = Perforn |                                          | memory row                                  | addressed    | by EEADRH     | I:EEADR on    | the next WF   | R command   |

| bit 3         | WRERR: E                    | EPROM Er                                 | ror Flag bit                                |              |               |               |               |             |

|               | operat                      | ion)                                     | s premature<br>n completed                  | -            | d (any MCLI   | R or any WI   | OT Reset du   | ring normal |

| bit 2         | WREN: EE                    | PROM Writ                                | e Enable bit                                |              |               |               |               |             |

|               |                             | write cycles<br>write to the             |                                             |              |               |               |               |             |

| bit 1         | WR: Write                   | Control bit                              |                                             |              |               |               |               |             |

|               | can on                      | ly be set (no                            | cle. The bit<br>ot cleared) ir<br>EEPROM is | n software.  | y hardware o  | once write is | s complete.   | The WR bit  |

| bit 0         | RD: Read                    | Control bit                              |                                             |              |               |               |               |             |

|               |                             | s an EEPR<br>d) in softwar               |                                             | D is cleared | l in hardwar  | e. The RD I   | bit can only  | be set (not |

|               | 0 = Does r                  | not initiate a                           | n EEPROM                                    | read         |               |               |               |             |

|               | Legend:                     |                                          |                                             |              |               |               |               | ]           |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Set only         | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

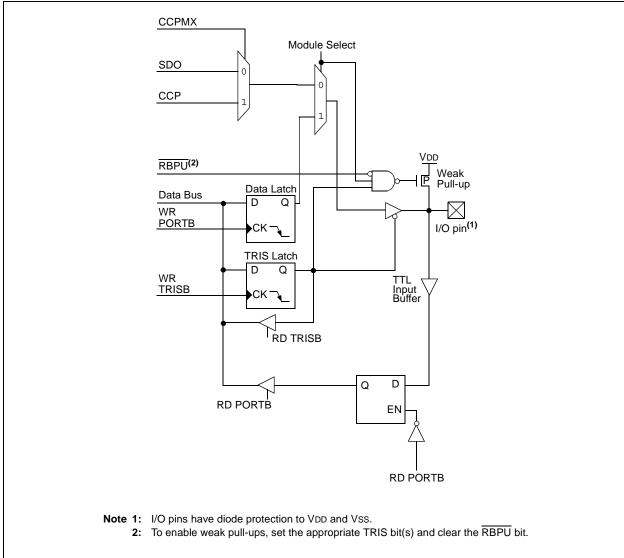

# 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

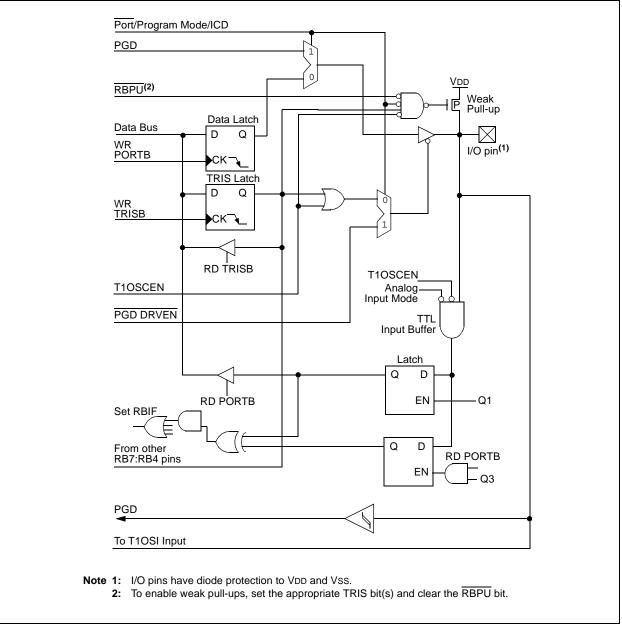

# FIGURE 5-15: BLOCK DIAGRAM OF RB7 PIN

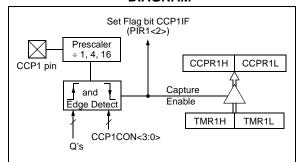

# 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | CCP1CON<br>NEW CAPT PS | ;Turn CCP module off<br>;Load the W reg with                                      |

|-------|------------------------|-----------------------------------------------------------------------------------|

| MOVWF | CCP1CON                | ;the new prescaler<br>;move value and CCP ON<br>;Load CCP1CON with this<br>;value |

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

### **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

- Note: The TRISB bit (2 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

# TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                              | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value o<br>POR, B |     | all o | e on<br>other<br>sets |

|----------------------|---------|--------|------------------------------------|--------------|---------|---------|--------|---------|---------|-------------------|-----|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                               | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 0            | 00x | 0000  | 000u                  |

| 0Ch                  | PIR1    | _      | ADIF                               | _            | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0 0              | 000 | - 0   | 0000                  |

| 8Ch                  | PIE1    | _      | ADIE                               | _            | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0              | 000 | - 0   | 0000                  |

| 86h                  | TRISB   | PORT   | B Data Dire                        | ection Regis | ter     |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 11h                  | TMR2    | Timer2 | 2 Module Re                        | gister       |         |         |        |         |         | 0000 0            | 000 | 0000  | 0000                  |

| 92h                  | PR2     | Timer2 | 2 Module Pe                        | riod Registe | er      |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 12h                  | T2CON   | _      | TOUTPS3                            | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0            | 000 | -000  | 0000                  |

| 15h                  | CCPR1L  | Captu  | pture/Compare/PWM Register 1 (LSB) |              |         |         |        |         |         | XXXX X            | xxx | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Captur | pture/Compare/PWM Register 1 (MSB) |              |         |         |        |         |         | XXXX X            | xxx | uuuu  | uuuu                  |

| 17h                  | CCP1CON |        |                                    | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0              | 000 | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

#### 10.3.2 MASTER MODE OPERATION

Master mode operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is Idle and both the S and P bits are clear.

In Master mode operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISB<4,1> bit(s). The output level is always low, irrespective of the value(s) in PORTB<4,1>. So when transmitting data, a '1' data bit must have the TRISB<1> bit set (input) and a '0' data bit must have the TRISB<1> bit cleared (output). The same scenario is true for the SCL line with the TRISB<4> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011) or with the Slave mode active. When both Master mode operation and Slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on Master mode operation, see AN554, "Software Implementation of  $f^2C^{TM}$  Bus Master" (DS00554).

### 10.3.3 MULTI-MASTER MODE OPERATION

In Multi-Master mode operation, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISB<4,1>). There are two stages where this arbitration can be lost:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the Slave device continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

For more information on Multi-Master mode operation, see AN578, "Use of the SSP Module in the  $l^2C^{TM}$  Multi-Master Environment" (DS00578).

| Address                | Name                                   | Bit 7              | Bit 6              | Bit 5                     | Bit 4                | Bit 3     | Bit 2      | Bit 1  | Bit 0  | Valu<br>POR, |      | Valu<br>all o<br>Res |      |

|------------------------|----------------------------------------|--------------------|--------------------|---------------------------|----------------------|-----------|------------|--------|--------|--------------|------|----------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                | PEIE               | TMR0IE                    | INTE                 | RBIE      | TMR0IF     | INTF   | RBIF   | 0000         | 000x | 0000                 | 000u |

| 0Ch                    | PIR1                                   | _                  | ADIF               | _                         | _                    | SSPIF     | CCP1IF     | TMR2IF | TMR1IF | - 0          | 0000 | - 0                  | 0000 |

| 8Ch                    | PIE1                                   | _                  | ADIE               | _                         | _                    | SSPIE     | CCP1IE     | TMR2IE | TMR1IE | - 0          | 0000 | - 0                  | 0000 |

| 13h                    | SSPBUF                                 | Synchron           | ous Seria          | Port Rece                 | ive Buffe            | r/Transmi | t Register |        |        | xxxx         | xxxx | uuuu                 | uuuu |

| 93h                    | SSPADD                                 | Synchron           | ous Seria          | l Port (l <sup>2</sup> C⊺ | <sup>™</sup> mode) / | Address F | Register   |        |        | 0000         | 0000 | 0000                 | 0000 |

| 14h                    | SSPCON                                 | WCOL               | SSPOV              | SSPEN                     | CKP                  | SSPM3     | SSPM2      | SSPM1  | SSPM0  | 0000         | 0000 | 0000                 | 0000 |

| 94h                    | SSPSTAT                                | SMP <sup>(1)</sup> | CKE <sup>(1)</sup> | D/A                       | Р                    | S         | R/W        | UA     | BF     | 0000         | 0000 | 0000                 | 0000 |

| 86h                    | 6h TRISB PORTB Data Direction Register |                    |                    |                           |                      |           |            |        |        | 1111         | 1111 | 1111                 | 1111 |

TABLE 10-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

© 2001-2013 Microchip Technology Inc.

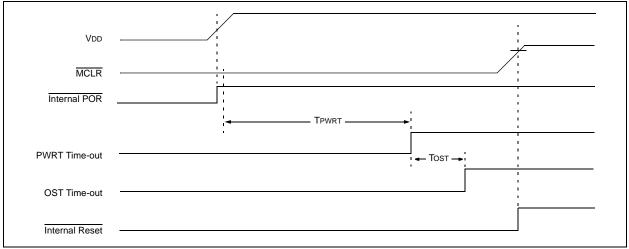

# 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits**"). WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

## FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | TOSE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

# 12.13 Power-Down Mode (Sleep)

Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (Status<3>) is cleared, the  $\overline{TO}$  (Status<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the Status register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- 3. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 6. A/D conversion (when A/D clock source is RC).

- 7. EEPROM write operation completion.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| RETFIE           | Return from Interrupt  | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE         | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | None                   | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $TOS \rightarrow PC$ , |                  | d ∈ [0,1]                                                                                                                                                                                                      |

|                  | $1 \rightarrow GIE$    | Operation:       | See description below                                                                                                                                                                                          |

| Status Affected: | None                   | Status Affected: | С                                                                                                                                                                                                              |

|                  |                        | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| RETLW                   | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [label] RRF f,d                                                                                                                                                                                                 |

| Operands:<br>Operation: | $0 \le k \le 255$<br>k $\rightarrow$ (W);                                                                                                                                           | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                 |

| oporation               | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                           |

| Status Affected:        | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                               |

| Description:            | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |

| <b>─→</b> C <b>→</b> | Register f |  |

|----------------------|------------|--|

|                      |            |  |

| RETURN           | Return from Subroutine                                             | SLEEP            | Enter Sleep mode                                                                                                                                                                                           |  |  |  |

|------------------|--------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETURN                                                     | Syntax:          | [label] SLEEP                                                                                                                                                                                              |  |  |  |

| Operands:        | None                                                               | Operands:        | None                                                                                                                                                                                                       |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                               | Operation:       | $00h \rightarrow WDT$ ,                                                                                                                                                                                    |  |  |  |

| Status Affected: | None                                                               |                  | $0 \rightarrow WDT$ prescaler,<br>1 $\rightarrow TO$ ,                                                                                                                                                     |  |  |  |

| Description:     | Return from subroutine. The stack                                  |                  | $0 \rightarrow \overline{PD}$                                                                                                                                                                              |  |  |  |

|                  | is POPed and the top of the stack (TOS) is loaded into the program | Status Affected: | TO, PD                                                                                                                                                                                                     |  |  |  |

|                  | counter. This is a two-cycle instruction.                          | Description:     | The Power-Down status bit, PD,<br>is cleared. Time-out status bit,<br>TO, is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |  |

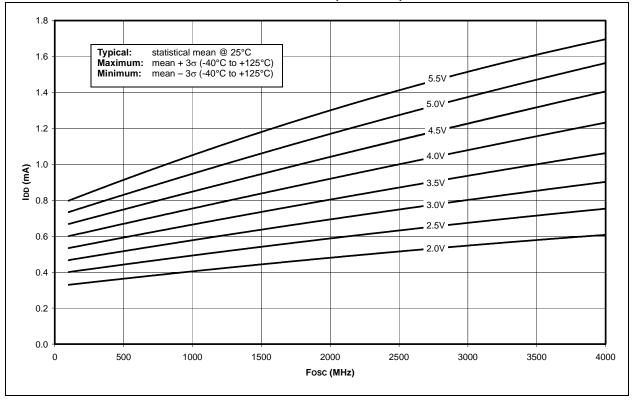

# 15.2 DC Characteristics: Power-Down and Supply Current PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial) (Continued)

| PIC16LF<br>(Indu | <b>818/819</b><br>strial)          |          | <b>rd Oper</b><br>ng temp |                   | onditions (unless -40°C $\leq$ TA | otherwise stated<br>≤ +85°C for indus |                               |  |  |  |  |  |

|------------------|------------------------------------|----------|---------------------------|-------------------|-----------------------------------|---------------------------------------|-------------------------------|--|--|--|--|--|

| PIC16F8<br>(Indu | <b>18/819</b><br>strial, Extended) |          |                           |                   |                                   |                                       |                               |  |  |  |  |  |

| Param<br>No.     | Device                             | Тур      | Max                       | Units             | Conditions                        |                                       |                               |  |  |  |  |  |

| D022             | Module Differential Curre          | nts (∆lw | от, ∆Іво                  | R, ∆ <b>i</b> lvd | , $\Delta$ IOSCB, $\Delta$ IAD)   |                                       |                               |  |  |  |  |  |

| (∆IWDT)          | Watchdog Timer                     | 1.5      | 3.8                       | μA                | -40°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 2.2      | 3.8                       | μA                | +25°C                             | VDD = 2.0V                            |                               |  |  |  |  |  |

|                  |                                    | 2.7      | 4.0                       | μΑ                | +85°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 2.3      | 4.6                       | μΑ                | -40°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 2.7      | 4.6                       | μΑ                | +25°C                             | VDD = 3.0V                            |                               |  |  |  |  |  |

|                  |                                    | 3.1      | 4.8                       | μΑ                | +85°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 3.0      | 10.0                      | μA                | -40°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 3.3      | 10.0                      | μΑ                | +25°C                             | VDD = 5.0V                            |                               |  |  |  |  |  |

|                  |                                    | 3.9      | 13.0                      | μΑ                | +85°C                             | VDD = 5.0V                            |                               |  |  |  |  |  |

|                  | Extended Devices                   | 5.0      | 21.0                      | μΑ                | +125°C                            |                                       |                               |  |  |  |  |  |

| D022A<br>(∆IBOR) | Brown-out Reset                    | 40       | 60                        | μΑ                | -40°C to +85°C                    | VDD = 5.0V                            |                               |  |  |  |  |  |

| D025             | Timer1 Oscillator                  | 1.7      | 2.3                       | μΑ                | -40°C                             |                                       |                               |  |  |  |  |  |

| (∆IOSCB)         |                                    | 1.8      | 2.3                       | μΑ                | +25°C                             | VDD = 2.0V                            |                               |  |  |  |  |  |

|                  |                                    | 2.0      | 2.3                       | μΑ                | +85°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 2.2      | 3.8                       | μΑ                | -40°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 2.6      | 3.8                       | μΑ                | +25°C                             | VDD = 3.0V                            | 32 kHz on Timer1              |  |  |  |  |  |

|                  |                                    | 2.9      | 3.8                       | μA                | +85°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 3.0      | 6.0                       | μΑ                | -40°C                             |                                       |                               |  |  |  |  |  |

|                  |                                    | 3.2      | 6.0                       | μΑ                | +25°C                             | VDD = 5.0V                            |                               |  |  |  |  |  |

|                  |                                    | 3.4      | 7.0                       | μA                | +85°C                             |                                       |                               |  |  |  |  |  |

| D026             | A/D Converter                      | 0.001    | 2.0                       | μA                | -40°C to +85°C                    | VDD = 2.0V                            |                               |  |  |  |  |  |

| $(\Delta IAD)$   |                                    | 0.001    | 2.0                       | μΑ                | -40°C to +85°C                    | VDD = 3.0V                            | A/D on, Sleep, not converting |  |  |  |  |  |

|                  |                                    | 0.003    | 2.0                       | μΑ                | -40°C to +85°C                    | VDD = 5.0V                            |                               |  |  |  |  |  |

|                  | Extended Devices                   | 4.0      | 8.0                       | μA                | -40°C to +125°C                   |                                       |                               |  |  |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 15.4 DC Characteristics: PIC16F818/819 (Industrial, Extended) PIC16LF818/819 (Industrial)

| DC CHA       | ARACTI | ERISTICS                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |          |       |                                                                    |  |  |  |  |

|--------------|--------|------------------------------|------------------------------------------------------|------|----------|-------|--------------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Sym    | Characteristic               | Min                                                  | Тур† | Max      | Units | Conditions                                                         |  |  |  |  |

|              | VIL    | Input Low Voltage            | •                                                    |      |          |       |                                                                    |  |  |  |  |

|              |        | I/O ports:                   |                                                      |      |          |       |                                                                    |  |  |  |  |

| D030         |        | with TTL buffer              | Vss                                                  | _    | 0.15 Vdd | V     | For entire VDD range                                               |  |  |  |  |

| D030A        |        |                              | Vss                                                  | _    | 0.8V     | V     | $4.5V \le V\text{DD} \le 5.5V$                                     |  |  |  |  |

| D031         |        | with Schmitt Trigger buffer  | Vss                                                  | _    | 0.2 Vdd  | V     |                                                                    |  |  |  |  |

| D032         |        | MCLR, OSC1 (in RC mode)      | Vss                                                  | _    | 0.2 Vdd  | V     | (Note 1)                                                           |  |  |  |  |

| D033         |        | OSC1 (in XT and LP mode)     | Vss                                                  | _    | 0.3V     | V     |                                                                    |  |  |  |  |

|              |        | OSC1 (in HS mode)            | Vss                                                  | _    | 0.3 Vdd  | V     |                                                                    |  |  |  |  |

|              |        | Ports RB1 and RB4:           |                                                      |      |          |       |                                                                    |  |  |  |  |

| D034         |        | with Schmitt Trigger buffer  | Vss                                                  | _    | 0.3 Vdd  | V     | For entire VDD range                                               |  |  |  |  |

|              | Viн    | Input High Voltage           |                                                      |      |          |       |                                                                    |  |  |  |  |

|              |        | I/O ports:                   |                                                      |      |          |       |                                                                    |  |  |  |  |

| D040         |        | with TTL buffer              | 2.0                                                  | _    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |  |  |  |

| D040A        |        |                              | 0.25 VDD + 0.8V                                      | _    | Vdd      | V     | For entire VDD range                                               |  |  |  |  |

| D041         |        | with Schmitt Trigger buffer  | 0.8 Vdd                                              | _    | Vdd      | V     | For entire VDD range                                               |  |  |  |  |

| D042         |        | MCLR                         | 0.8 Vdd                                              | —    | Vdd      | V     |                                                                    |  |  |  |  |

| D042A        |        | OSC1 (in XT and LP mode)     | 1.6V                                                 | _    | Vdd      | V     |                                                                    |  |  |  |  |

|              |        | OSC1 (in HS mode)            | 0.7 Vdd                                              | _    | Vdd      | V     |                                                                    |  |  |  |  |

| D043         |        | OSC1 (in RC mode)            | 0.9 Vdd                                              | _    | Vdd      | V     | (Note 1)                                                           |  |  |  |  |