Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 10MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 16                                                                            |

| Program Memory Size        | 3.5KB (2K x 14)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 256 x 8                                                                       |

| RAM Size                   | 256 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 5x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf819t-i-mltsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address               | Name       | Bit 7                                               | Bit 6                                                              | Bit 5          | Bit 4          | Bit 3          | Bit 2                 | Bit 1           | Bit 0    | Value on<br>POR, BOR | Details on<br>page: |

|-----------------------|------------|-----------------------------------------------------|--------------------------------------------------------------------|----------------|----------------|----------------|-----------------------|-----------------|----------|----------------------|---------------------|

| Bank 2                |            |                                                     |                                                                    |                |                |                |                       |                 |          |                      |                     |

| 100h <sup>(1)</sup>   | INDF       | Addressin                                           | ng this locatio                                                    | on uses conte  | ents of FSR to | address data   | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 101h                  | TMR0       | Timer0 M                                            | lodule Regist                                                      | ter            |                |                |                       |                 |          | xxxx xxxx            | 53                  |

| 102h <sup>(1</sup>    | PCL        | Program                                             | Counter's (P                                                       | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 103h <sup>(1)</sup>   | STATUS     | IRP                                                 | RP1                                                                | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 104h <sup>(1)</sup>   | FSR        | Indirect D                                          | ata Memory                                                         | Address Poir   | nter           |                |                       |                 |          | xxxx xxxx            | 23                  |

| 105h                  | —          | Unimpler                                            | nented                                                             |                |                |                |                       |                 |          | _                    | —                   |

| 106h                  | PORTB      | PORTB [                                             | Data Latch w                                                       | hen written; P | ORTB pins w    | hen read       |                       |                 |          | XXXX XXXX            | 43                  |

| 107h                  | —          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          | —                    | _                   |

| 108h                  | —          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          | —                    | —                   |

| 109h                  | —          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          | —                    | —                   |

| 10Ah <sup>(1,2)</sup> | PCLATH     | _                                                   | —                                                                  | _              | Write Buffer   | for the upper  | 5 bits of the F       | Program Cour    | nter     | 0 0000               | 23                  |

| 10Bh <sup>(1)</sup>   | INTCON     | GIE                                                 | PEIE                                                               | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 10Ch                  | EEDATA     | EEPROM                                              | I/Flash Data                                                       | Register Low   | Byte           |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Dh                  | EEADR      | EEPROM                                              | 1/Flash Addre                                                      | ess Register L | ow Byte        |                |                       |                 |          | xxxx xxxx            | 25                  |

| 10Eh                  | EEDATH     | _                                                   | —                                                                  | EEPROM/Fla     | ash Data Reg   | ister High Byt | е                     |                 |          | xx xxxx              | 25                  |

| 10Fh                  | EEADRH     | —                                                   | —                                                                  | —              | —              | —              | EEPROM/F<br>High Byte | lash Address    | Register | xxx                  | 25                  |

| Bank 3                |            |                                                     |                                                                    |                |                |                |                       |                 |          |                      |                     |

| 180h <sup>(1)</sup>   | INDF       | Addressin                                           | ng this locatio                                                    | on uses conte  | ents of FSR to | address data   | memory (not           | t a physical re | egister) | 0000 0000            | 23                  |

| 181h                  | OPTION_REG | RBPU                                                | INTEDG                                                             | TOCS           | TOSE           | PSA            | PS2                   | PS1             | PS0      | 1111 1111            | 17, 54              |

| 182h <sup>(1)</sup>   | PCL        | Program                                             | Counter's (P                                                       | C) Least Sigr  | ificant Byte   |                |                       |                 |          | 0000 0000            | 23                  |

| 183h <sup>(1)</sup>   | STATUS     | IRP                                                 | RP1                                                                | RP0            | TO             | PD             | Z                     | DC              | С        | 0001 1xxx            | 16                  |

| 184h <sup>(1)</sup>   | FSR        | Indirect D                                          | ata Memory                                                         | Address Poir   | nter           |                |                       |                 |          | xxxx xxxx            | 23                  |

| 185h                  | —          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          | —                    | _                   |

| 186h                  | TRISB      | PORTB [                                             | Data Direction                                                     | n Register     |                |                |                       |                 |          | 1111 1111            | 43                  |

| 187h                  | _          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          | _                    | —                   |

| 188h                  | _          | Unimplen                                            | nented                                                             |                |                |                |                       |                 |          |                      | —                   |

| 189h                  | _          | Unimplen                                            | Unimplemented —                                                    |                |                |                |                       |                 |          | —                    |                     |

| 18Ah <sup>(1,2)</sup> | PCLATH     |                                                     | Write Buffer for the upper 5 bits of the Program Counter    0 0000 |                |                |                |                       |                 |          | 23                   |                     |

| 18Bh <sup>(1)</sup>   | INTCON     | GIE                                                 | PEIE                                                               | TMR0IE         | INTE           | RBIE           | TMR0IF                | INTF            | RBIF     | 0000 000x            | 18                  |

| 18Ch                  | EECON1     | EEPGD                                               |                                                                    |                |                |                |                       |                 |          |                      | 26                  |

|                       | 1          | EEPROM Control Register 2 (not a physical register) |                                                                    |                |                |                |                       |                 |          | 25                   |                     |

| 18Dh                  | EECON2     | LEFRON                                              | Reserved; maintain clear 0000 0000                                 |                |                |                |                       |                 |          |                      |                     |

| 18Dh<br>18Eh          | EECON2     |                                                     |                                                                    |                | p, e.e         | ,              |                       |                 |          | 0000 0000            | —                   |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'. Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0      | R/W-0                             | R/W-0           | R/W-0        | R/W-0         | R/W-0         | R/W-0        | R/W-x      |

|------------|-----------------------------------|-----------------|--------------|---------------|---------------|--------------|------------|

| GIE        | PEIE                              | TMR0IE          | INTE         | RBIE          | TMR0IF        | INTF         | RBIF       |

| bit 7      |                                   |                 |              |               |               |              | bit (      |

| GIE: Globa | al Interrupt Er                   | nable bit       |              |               |               |              |            |

|            | es all unmask<br>les all interrup |                 | ;            |               |               |              |            |

| PEIE: Peri | pheral Interru                    | ipt Enable bit  | :            |               |               |              |            |

|            | es all unmask<br>les all periphe  |                 |              |               |               |              |            |

| TMR0IE: T  | MR0 Overflo                       | w Interrupt E   | nable bit    |               |               |              |            |

|            | es the TMR0<br>les the TMR0       |                 |              |               |               |              |            |

| INTE: RB0  | /INT Externa                      | I Interrupt En  | able bit     |               |               |              |            |

|            | es the RB0/IN<br>les the RB0/II   |                 |              |               |               |              |            |

| RBIE: RB   | Port Change                       | Interrupt Ena   | able bit     |               |               |              |            |

|            | es the RB po<br>les the RB po     | •               | •            |               |               |              |            |

| TMR0IF: T  | MR0 Overflo                       | w Interrupt F   | lag bit      |               |               |              |            |

|            | register has<br>register did r    |                 | must be clea | ared in softv | vare)         |              |            |

| INTF: RB0  | /INT Externa                      | I Interrupt Fla | ng bit       |               |               |              |            |

|            | B0/INT exter<br>B0/INT exter      |                 | · ·          |               | ed in softwa  | ire)         |            |

| RBIF: RB   | Port Change                       | Interrupt Flag  | g bit        |               |               |              |            |

|            | h condition w<br>Ind allow flag   |                 | •            | RBIF. Read    | ing PORTB     | will end the | e mismatcl |

|            | st one of the of the RB7:R        | •               | •            | •             | be cleared in | n software)  |            |

| Legend:    |                                   |                 |              |               |               |              |            |

| R = Reada  | able bit                          | W = Wr          | ritable bit  | U = Unim      | plemented     | bit, read as | '0'        |

|            |                                   |                 |              |               |               |              |            |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| REGISTER 3-1: | EECON1:                     | EEPROM                                   | ACCESS C                                    | ONTROL       | REGISTER      | 1 (ADDRI      | ESS 18Ch)     |             |

|---------------|-----------------------------|------------------------------------------|---------------------------------------------|--------------|---------------|---------------|---------------|-------------|

|               | R/W-x                       | U-0                                      | U-0                                         | R/W-x        | R/W-x         | R/W-0         | R/S-0         | R/S-0       |

|               | EEPGD                       |                                          | _                                           | FREE         | WRERR         | WREN          | WR            | RD          |

|               | bit 7                       |                                          |                                             |              |               |               |               | bit 0       |

| bit 7         | EEPGD: Pr                   | ogram/Data                               | EEPROM                                      | Select bit   |               |               |               |             |

|               | 0 = Access                  | es program<br>es data mei<br>fter a POR; | mory                                        | not be chang | ged while a v | write operati | on is in prog | jress.      |

| bit 6-5       | Unimplem                    | ented: Read                              | <b>d as</b> '0'                             |              |               |               |               |             |

| bit 4         | FREE: EEF                   | PROM Force                               | ed Row Eras                                 | se bit       |               |               |               |             |

|               | 1 = Erase tl<br>0 = Perforn |                                          | memory row                                  | addressed    | by EEADRH     | I:EEADR on    | the next WF   | R command   |

| bit 3         | WRERR: E                    | EPROM Er                                 | ror Flag bit                                |              |               |               |               |             |

|               | operat                      | ion)                                     | s premature<br>n completed                  | -            | d (any MCLI   | R or any WI   | OT Reset du   | ring normal |

| bit 2         | WREN: EE                    | PROM Writ                                | e Enable bit                                |              |               |               |               |             |

|               |                             | write cycles<br>write to the             |                                             |              |               |               |               |             |

| bit 1         | WR: Write                   | Control bit                              |                                             |              |               |               |               |             |

|               | can on                      | ly be set (no                            | cle. The bit<br>ot cleared) ir<br>EEPROM is | n software.  | y hardware o  | once write is | s complete.   | The WR bit  |

| bit 0         | RD: Read                    | Control bit                              |                                             |              |               |               |               |             |

|               |                             | s an EEPR<br>d) in softwar               |                                             | D is cleared | l in hardwar  | e. The RD I   | bit can only  | be set (not |

|               | 0 = Does r                  | not initiate a                           | n EEPROM                                    | read         |               |               |               |             |

|               | Legend:                     |                                          |                                             |              |               |               |               | ]           |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Set only         | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

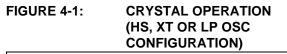

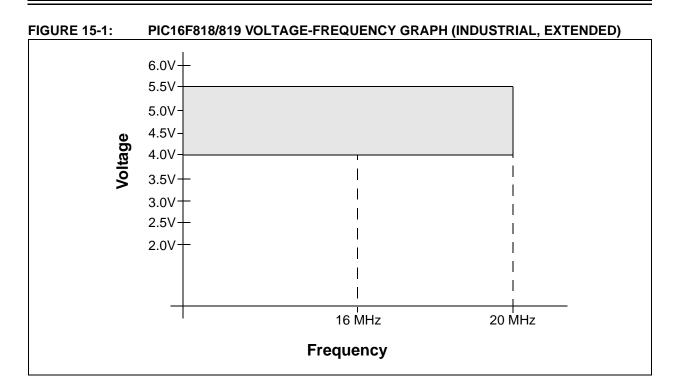

### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F818/819 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

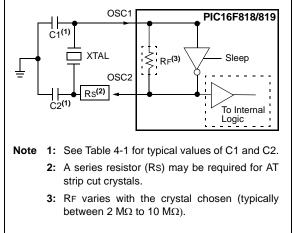

#### 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F818/819 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

#### TABLE 4-1: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|---------|-------------------------------------|-------|--|--|--|

|          | Freq    | C1                                  | C2    |  |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz   | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### 4.5.3 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

#### 4.5.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF<2:0> = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

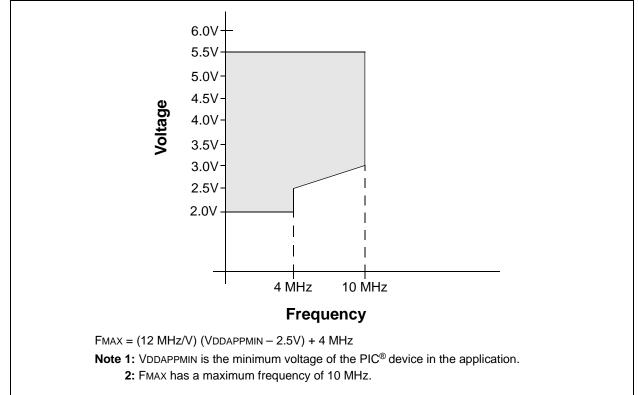

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.5.5 CLOCK TRANSITION SEQUENCE WHEN THE IRCF BITS ARE MODIFIED

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

- Note: The TRISB bit (2 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

#### TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                                | Bit 5        | Bit 4        | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value o<br>POR, B |     | all o | e on<br>other<br>sets |

|----------------------|---------|--------|--------------------------------------|--------------|--------------|---------|--------|---------|---------|-------------------|-----|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                 | TMR0IE       | INTE         | RBIE    | TMR0IF | INTF    | RBIF    | 0000 00           | 20x | 0000  | 000u                  |

| 0Ch                  | PIR1    | _      | ADIF                                 | _            | —            | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0 00             | 000 | - 0   | 0000                  |

| 8Ch                  | PIE1    | _      | ADIE                                 | _            | —            | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 00             | 000 | - 0   | 0000                  |

| 86h                  | TRISB   | PORT   | B Data Dire                          | ection Regis | ter          |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 11h                  | TMR2    | Timer2 | 2 Module Re                          | gister       |              |         |        |         |         | 0000 00           | 000 | 0000  | 0000                  |

| 92h                  | PR2     | Timer2 | 2 Module Pe                          | riod Registe | er           |         |        |         |         | 1111 1:           | 111 | 1111  | 1111                  |

| 12h                  | T2CON   | _      | TOUTPS3                              | TOUTPS2      | TOUTPS1      | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 00           | 000 | -000  | 0000                  |

| 15h                  | CCPR1L  | Captu  | re/Compare                           | PWM Regis    | ster 1 (LSB) |         |        |         |         | XXXX XX           | xx  | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Captur | Capture/Compare/PWM Register 1 (MSB) |              |              |         |        |         | uuuu    |                   |     |       |                       |

| 17h                  | CCP1CON |        | _                                    | CCP1X        | CCP1Y        | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 00             | 000 | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

|         | R/W-0                     | R/W-0                                                                                                                                   | R/W-0                                                                             | R/W-0                       | R/W-0                             | R/W-0                      | R/W-0                      | R/W-0                       |  |  |  |

|---------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------|-----------------------------------|----------------------------|----------------------------|-----------------------------|--|--|--|

|         | WCOL                      | SSPOV                                                                                                                                   | SSPEN                                                                             | CKP                         | SSPM3                             | SSPM2                      | SSPM1                      | SSPM0                       |  |  |  |

|         | bit 7                     |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            | bit 0                       |  |  |  |

| bit 7   | WCOL: W                   | rite Collision                                                                                                                          | Detect bit                                                                        |                             |                                   |                            |                            |                             |  |  |  |

|         |                           | <ul> <li>1 = An attempt to write the SSPBUF register failed because the SSP module is busy<br/>(must be cleared in software)</li> </ul> |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         | 0 = No col                |                                                                                                                                         | ,                                                                                 |                             |                                   |                            |                            |                             |  |  |  |

| bit 6   | SSPOV: R                  | eceive Over                                                                                                                             | flow Indicator                                                                    | <sup>·</sup> bit            |                                   |                            |                            |                             |  |  |  |

|         | In SPI mod                |                                                                                                                                         |                                                                                   | 00000115                    |                                   |                            |                            |                             |  |  |  |

|         | of ove<br>must r<br>mode, | erflow, the da<br>read the SSF<br>, the overflow<br>g to the SSPI                                                                       | ived while the<br>ta in SSPSR<br>PBUF, even if<br>bit is not set<br>BUF register. | is lost. Ove<br>only transm | erflow can on<br>nitting data, to | ily occur in<br>avoid sett | Slave mode<br>ing overflow | e. The user<br>/. In Master |  |  |  |

|         | In I <sup>2</sup> C mod   | le:                                                                                                                                     |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         |                           | care" in Trar                                                                                                                           | while the SSI<br>nsmit mode. \$                                                   |                             |                                   |                            |                            |                             |  |  |  |

| bit 5   | SSPEN: S                  | ynchronous                                                                                                                              | Serial Port E                                                                     | nable bit <sup>(1)</sup>    |                                   |                            |                            |                             |  |  |  |

|         | In SPI mod                | -                                                                                                                                       |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | and configur                                                                      |                             |                                   |                            | t pins                     |                             |  |  |  |

|         | In I <sup>2</sup> C mod   |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | port and conf<br>and configu                                                      |                             |                                   |                            | rial port pins             | ;                           |  |  |  |

|         | Note 1:                   | In both mo<br>output.                                                                                                                   | des, when er                                                                      | abled, these                | e pins must l                     | be properly                | configured                 | as input or                 |  |  |  |

| bit 4   | CKP: Cloc                 | k Polarity Se                                                                                                                           | elect bit                                                                         |                             |                                   |                            |                            |                             |  |  |  |

|         |                           | nit happens o                                                                                                                           | on falling edg<br>on rising edg                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         | In I <sup>2</sup> C Slav  |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         | SCK release               |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         | 1 = Enable<br>0 = Holds ( |                                                                                                                                         | ock stretch).                                                                     | Used to ens                 | sure data set                     | up time.)                  |                            |                             |  |  |  |

| bit 3-0 |                           | -                                                                                                                                       | ous Serial P                                                                      | -                           |                                   |                            |                            |                             |  |  |  |

|         |                           | -                                                                                                                                       | de, clock = C                                                                     |                             |                                   |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | de, clock = C                                                                     |                             |                                   |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | de, clock = C<br>de, clock = T                                                    |                             | 12                                |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | e, clock = SC                                                                     |                             |                                   | abled.                     |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | e, clock = SC                                                                     |                             | in control dis                    | abled. SS c                | an be used                 | as I/O pin                  |  |  |  |

|         |                           |                                                                                                                                         | e, 7-bit addre<br>e, 10-bit addr                                                  |                             |                                   |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | Controlled Ma                                                                     |                             | Slave Idle)                       |                            |                            |                             |  |  |  |

|         | $1110 = I^2C$             | Slave mode                                                                                                                              | e, 7-bit addre                                                                    | ss with Starl               | t and Stop bit                    |                            |                            |                             |  |  |  |

|         |                           |                                                                                                                                         | e, 10-bit addr                                                                    |                             |                                   | oit interrupts             | enabled                    |                             |  |  |  |

|         | 1000, 10                  | UUI, 1010,                                                                                                                              | 1100, 11                                                                          | JI = Keserv                 | ea                                |                            |                            |                             |  |  |  |

|         | Legend:                   |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            |                             |  |  |  |

|         | R = Reada                 | ble bit                                                                                                                                 | W = W                                                                             | itable bit                  | U = Unim                          | lemented h                 | oit, read as '             | 0'                          |  |  |  |

|         |                           |                                                                                                                                         |                                                                                   |                             |                                   |                            |                            | -                           |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 10.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<4,1> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

Either or both of the following conditions will cause the SSP module not to give this ACK pulse:

- a) The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- b) The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF but bit, SSPIF (PIR1<3>), is set. Table 10-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, are shown in timing parameter #100 and parameter #101.

#### 10.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF, is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

#### 10.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit, BF (SSPSTAT<0>), is set or bit, SSPOV (SSPCON<6>), is set.

An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 10.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RB4/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RB4/SCK/SCL should be enabled by setting bit, CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 10-7).

NOTES:

### 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has five inputs for 18/20 pin devices.

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has a high and low-voltage reference input that is software selectable to some combination of VDD, VSS, RA2 or RA3.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/Os.

Additional information on using the A/D module can be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

|         | R/W-0                  | R/W-0                        | R/W-0           | R/W-0          | R/W-0        | R/W-0           | U-0          | R/W-0  |

|---------|------------------------|------------------------------|-----------------|----------------|--------------|-----------------|--------------|--------|

|         | ADCS1                  | ADCS0                        | CHS2            | CHS1           | CHS0         | GO/DONE         | _            | ADON   |

|         | bit 7                  |                              |                 |                |              |                 |              | bit 0  |

|         |                        |                              |                 |                |              |                 |              |        |

| bit 7-6 | ADCS1:AD               | DCS0: A/D C                  | onversion C     | lock Select b  | oits         |                 |              |        |

|         | If ADCS2 =             |                              |                 |                |              |                 |              |        |

|         | 00 = Fosc<br>01 = Fosc |                              |                 |                |              |                 |              |        |

|         | 10 = FOSC              | -                            |                 |                |              |                 |              |        |

|         |                        | clock derived                | from the in     | ternal A/D m   | odule RC o   | scillator)      |              |        |

|         | If ADCS2 =             | <u>= 1:</u>                  |                 |                |              |                 |              |        |

|         | 00 = FOSC              | -                            |                 |                |              |                 |              |        |

|         | 01 = FOSC<br>10 = FOSC | -                            |                 |                |              |                 |              |        |

|         |                        | clock derived                | from the in     | ternal A/D m   | odule RC o   | scillator)      |              |        |

| bit 5-3 | •                      | 50: Analog C                 |                 |                |              |                 |              |        |

|         |                        | nnel 0 (RA0/                 |                 | 01 0110        |              |                 |              |        |

|         |                        | nnel 1 (RA1/                 | ,               |                |              |                 |              |        |

|         |                        | nnel 2 (RA2/                 | ,               |                |              |                 |              |        |

|         |                        | nnel 3 (RA3/<br>nnel 4 (RA4/ |                 |                |              |                 |              |        |

| bit 2   |                        | : A/D Conve                  | •               | hit            |              |                 |              |        |

|         | If ADON =              |                              | SION Status     | DIL            |              |                 |              |        |

|         |                        |                              | progress (se    | tting this bit | starts the A | D conversion)   |              |        |

|         |                        |                              |                 |                |              | cleared by ha   | rdware wh    | en the |

|         | A/D co                 | onversion is o               | complete)       |                |              |                 |              |        |

| bit 1   | Unimplem               | ented: Read                  | <b>l as</b> '0' |                |              |                 |              |        |

| bit 0   | ADON: A/I              |                              |                 |                |              |                 |              |        |

|         |                        | onverter mod                 |                 |                |              |                 |              |        |

|         | 0 = A/D cc             | onverter mod                 | ule is snut-o   | m and consu    | mes no ope   | erating current |              |        |

|         | Legend:                |                              |                 |                |              |                 |              |        |

|         | R = Reada              | able bit                     | W = W           | /ritable bit   | U = Unir     | nplemented bit  | , read as '( | )'     |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 11-1: ADCON0: A/D CONTROL REGISTER 0 (ADDRESS 1Fh)

-n = Value at POR

x = Bit is unknown

### 11.5 A/D Operation During Sleep

The A/D module can operate during Sleep mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in Sleep, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in Sleep, ensure the SLEEP instruction immediately <u>follows</u> the instruction that sets the GO/DONE bit.

#### 11.6 Effects of a Reset

A device Reset forces all registers to their Reset state. The A/D module is disabled and any conversion in progress is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

### 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRESH:ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module but will still reset the Timer1 counter.

| Address              | Name   | Bit 7   | Bit 6      | Bit 5      | Bit 4 | Bit 3   | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|--------|---------|------------|------------|-------|---------|---------------|--------|--------|----------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON | GIE     | PEIE       | TMR0IE     | INTE  | RBIE    | TMR0IF        | INTF   | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                  | PIR1   | —       | ADIF       |            | —     | SSPIF   | CCP1IF        | TMR2IF | TMR1IF | -0 0000              | -0 0000                         |

| 8Ch                  | PIE1   | —       | ADIE       |            | —     | SSPIE   | CCP1IE        | TMR2IE | TMR1IE | -0 0000              | -0 0000                         |

| 1Eh                  | ADRESH | A/D Res | ult Regist | er High By | /te   |         |               |        |        | xxxx xxxx            | uuuu uuuu                       |

| 9Eh                  | ADRESL | A/D Res | ult Regist | er Low By  | te    |         |               |        |        | xxxx xxxx            | uuuu uuuu                       |

| 1Fh                  | ADCON0 | ADCS1   | ADCS0      | CHS2       | CHS1  | CHS0    | GO/DONE       | _      | ADON   | 0000 00-0            | 0000 00-0                       |

| 9Fh                  | ADCON1 | ADFM    | ADCS2      | _          | _     | PCFG3   | PCFG2         | PCFG1  | PCFG0  | 00 0000              | 00 0000                         |

| 05h                  | PORTA  | RA7     | RA6        | RA5        | RA4   | RA3     | RA2           | RA1    | RA0    | xxx0 0000            | uuu0 0000                       |

| 85h                  | TRISA  | TRISA7  | TRISA6     | TRISA5     | PORTA | Data Di | rection Regis | ster   |        | 1111 1111            | 1111 1111                       |

#### TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

### 12.18 Low-Voltage ICSP Programming

The LVP bit of the Configuration Word register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when Programming mode is entered with VIHH on MCLR. The LVP bit can only be changed when using high voltage on MCLR.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only this mode can be used to program the device.

When using Low-Voltage ICSP, the part must be supplied at 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code-protect bits from an ON state to an OFF state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs or user code can be reprogrammed or added.

The following LVP steps assume the LVP bit is set in the Configuration Word register.

- 1. Apply VDD to the VDD pin.

- 2. Drive MCLR low.

- 3. Apply VDD to the RB3/PGM pin.

- 4. Apply VDD to the  $\overline{\text{MCLR}}$  pin.

- 5. Follow with the associated programming steps.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode (LVP = 1), the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F818/819 device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the Configuration Word register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' = 0, the next<br>instruction is executed.<br>If bit 'b' = 1, then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| CLRF             | Clear f                                                               |  |

|------------------|-----------------------------------------------------------------------|--|

| Syntax:          | [label] CLRF f                                                        |  |

| Operands:        | $0 \le f \le 127$                                                     |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |

| Status Affected: | Z                                                                     |  |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                               |

| Description:     | If bit 'b' in register 'f' = 1, the next<br>instruction is executed.<br>If bit 'b' in register 'f' = 0, the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                            | CLRWDT           | Clear Watchdog Timer                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                    | Syntax:          | [label] CLRWDT                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                         | Operands:        | None                                                                                                                           |

| Operation:       | (PC) + 1 → TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                              | Operation:       | $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$                               |

| Status Affected: | None                                                                                                                                                                                                       |                  | $1 \rightarrow PD$                                                                                                             |

| Description:     | Call subroutine. First, return                                                                                                                                                                             | Status Affected: | TO, PD                                                                                                                         |

|                  | address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits<10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. | Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set. |

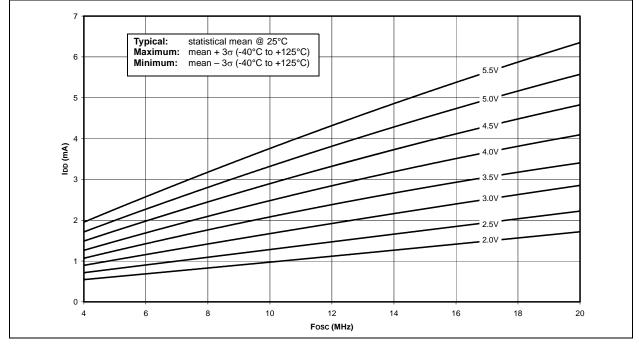

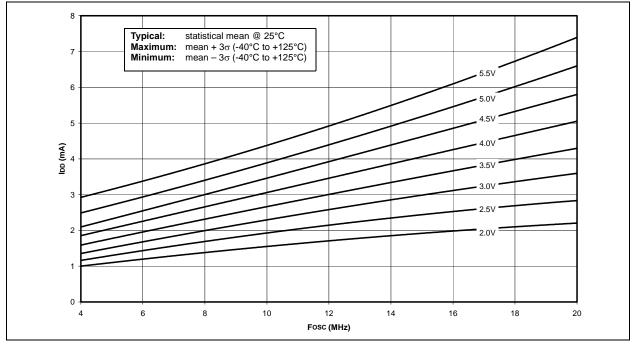

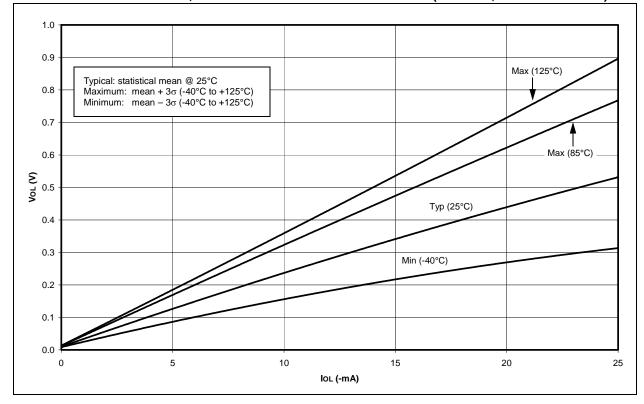

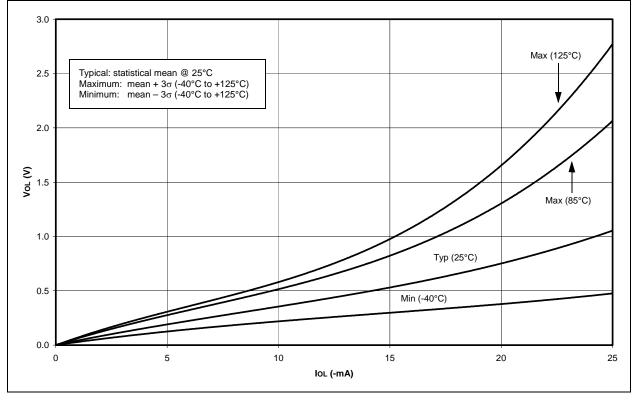

### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 2001-2013 Microchip Technology Inc.

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

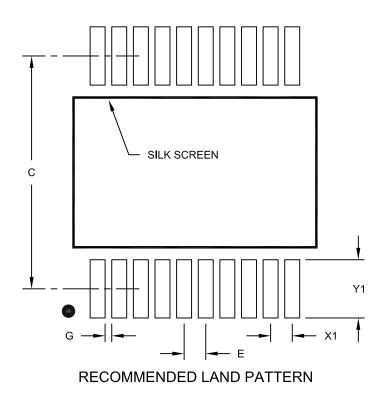

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | E  |             | 0.65 BSC |      |

| Contact Pad Spacing      | С  |             | 7.20     |      |

| Contact Pad Width (X20)  | X1 |             |          | 0.45 |

| Contact Pad Length (X20) | Y1 |             |          | 1.75 |

| Distance Between Pads    | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

| Writing to Flash Program Memory           | 31        |

|-------------------------------------------|-----------|