Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf819t-i-sog |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F818/819

NOTES:

# PIC16F818/819

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB port change and external RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|                                           | R/W-0                                    | R/W-0                             | R/W-0          | R/W-0        | R/W-0         | R/W-0         | R/W-0        | R/W-x      |

|-------------------------------------------|------------------------------------------|-----------------------------------|----------------|--------------|---------------|---------------|--------------|------------|

|                                           | GIE                                      | PEIE                              | TMR0IE         | INTE         | RBIE          | TMR0IF        | INTF         | RBIF       |

|                                           | bit 7                                    |                                   |                |              |               |               |              | bit (      |

|                                           | GIE: Globa                               | al Interrupt Er                   | nable bit      |              |               |               |              |            |

|                                           |                                          | es all unmask<br>les all interrup |                | ;            |               |               |              |            |

|                                           | PEIE: Peri                               | pheral Interru                    | ipt Enable bit | :            |               |               |              |            |

|                                           |                                          | es all unmask<br>les all periphe  |                |              |               |               |              |            |

|                                           | TMR0IE: T                                | MR0 Overflo                       | w Interrupt E  | nable bit    |               |               |              |            |

|                                           |                                          | es the TMR0<br>les the TMR0       |                |              |               |               |              |            |

|                                           | INTE: RB0                                | /INT Externa                      | I Interrupt En | able bit     |               |               |              |            |

|                                           |                                          | es the RB0/IN<br>les the RB0/II   |                |              |               |               |              |            |

|                                           | RBIE: RB                                 | Port Change                       | Interrupt Ena  | able bit     |               |               |              |            |

|                                           |                                          | es the RB po<br>les the RB po     | •              | •            |               |               |              |            |

|                                           | TMR0IF: TMR0 Overflow Interrupt Flag bit |                                   |                |              |               |               |              |            |

|                                           |                                          | register has<br>register did r    |                | must be clea | ared in softv | vare)         |              |            |

| INTF: RB0/INT External Interrupt Flag bit |                                          |                                   |                |              |               |               |              |            |

|                                           |                                          | B0/INT exter<br>B0/INT exter      |                | · ·          |               | ed in softwa  | ire)         |            |

|                                           | RBIF: RB Port Change Interrupt Flag bit  |                                   |                |              |               |               |              |            |

|                                           |                                          | h condition w<br>Ind allow flag   |                | •            | RBIF. Read    | ing PORTB     | will end the | e mismatcl |

|                                           |                                          | st one of the of the RB7:R        | •              | •            | •             | be cleared in | n software)  |            |

|                                           | Legend:                                  |                                   |                |              |               |               |              |            |

|                                           | R = Reada                                | able bit                          | W = Wr         | ritable bit  | U = Unim      | plemented     | bit, read as | '0'        |

|                                           |                                          |                                   |                |              |               |               |              |            |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

### 4.5.3 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

#### 4.5.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF<2:0> = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.5.5 CLOCK TRANSITION SEQUENCE WHEN THE IRCF BITS ARE MODIFIED

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

## 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

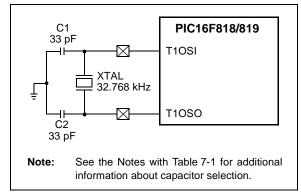

# 7.6 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note: The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) may not function correctly (high-voltage or lowvoltage) or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

#### TABLE 7-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type Freq |        | C1    | C2    |  |

|---------------|--------|-------|-------|--|

| LP            | 32 kHz | 33 pF | 33 pF |  |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- 2: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

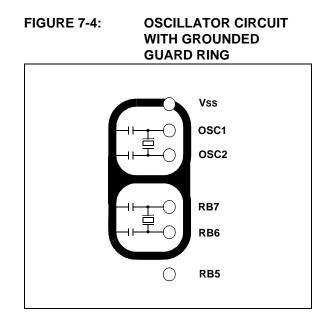

## 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

| RTCinit | BANKSEL<br>MOVLW<br>MOVWF<br>CLRF<br>MOVLW | TMR1H<br>0x80<br>TMR1H<br>TMR1L<br>b'00001111' | ; Preload TMR1 register pair<br>; for 1 second overflow<br>; Configure for external clock, |

|---------|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

|         | MOVWF                                      | TICON                                          | ; Asynchronous operation, external oscillator                                              |

|         | CLRF<br>CLRF                               | secs<br>mins                                   | ; Initialize timekeeping registers                                                         |

|         | MOVLW                                      | mins<br>.12                                    |                                                                                            |

|         | MOVLW                                      | .12<br>hours                                   |                                                                                            |

|         | BANKSEL                                    | PIE1                                           |                                                                                            |

|         | BSF                                        |                                                | ; Enable Timer1 interrupt                                                                  |

|         | RETURN                                     | ,                                              | ,                                                                                          |

| RTCisr  | BANKSEL                                    | TMR1H                                          |                                                                                            |

|         | BSF                                        | TMR1H, 7                                       | ; Preload for 1 sec overflow                                                               |

|         | BCF                                        | PIR1, TMR1IF                                   | ; Clear interrupt flag                                                                     |

|         | INCF                                       | secs, F                                        | ; Increment seconds                                                                        |

|         | MOVF                                       | secs, w                                        |                                                                                            |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | seconds                                        | ; Clear seconds                                                                            |

|         | INCF<br>MOVF                               | mins, f<br>mins, w                             | ; Increment minutes                                                                        |

|         | SUBLW                                      | .60                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 60 seconds elapsed?                                                                      |

|         | RETURN                                     | 511105, 2                                      | ; No, done                                                                                 |

|         | CLRF                                       | mins                                           | ; Clear minutes                                                                            |

|         | INCF                                       | hours, f                                       | ; Increment hours                                                                          |

|         | MOVF                                       | hours, w                                       |                                                                                            |

|         | SUBLW                                      | .24                                            |                                                                                            |

|         | BTFSS                                      | STATUS, Z                                      | ; 24 hours elapsed?                                                                        |

|         | RETURN                                     |                                                | ; No, done                                                                                 |

|         | CLRF                                       | hours                                          | ; Clear hours                                                                              |

|         | RETURN                                     |                                                | ; Done                                                                                     |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7   | Bit 6                                                                                          | Bit 5         | Bit 4        | Bit 3         | Bit 2       | Bit 1    | Bit 0  | Valu<br>POR, |      | all c | e on<br>other<br>sets |

|-----------------------|--------|---------|------------------------------------------------------------------------------------------------|---------------|--------------|---------------|-------------|----------|--------|--------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                                                                                           | TMR0IE        | INTE         | RBIE          | TMR0IF      | INTF     | RBIF   | 0000         | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1   | _       | ADIF                                                                                           | _             | _            | SSPIF         | CCP1IF      | TMR2IF   | TMR1IF | - 0          | 0000 | - 0   | 0000                  |

| 8Ch                   | PIE1   | _       | ADIE                                                                                           | _             | _            | SSPIE         | CCP1IE      | TMR2IE   | TMR1IE | - 0          | 0000 | - 0   | 0000                  |

| 0Eh                   | TMR1L  | Holding | g Registe                                                                                      | er for the Le | ast Signific | ant Byte of t | he 16-bit T | MR1 Regi | ster   | xxxx         | xxxx | uuuu  | uuuu                  |

| 0Fh                   | TMR1H  | Holding | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |               |              |               |             |          | uuuu   |              |      |       |                       |

| 10h                   | T1CON  |         | _                                                                                              | T1CKPS1       | T1CKPS0      | T1OSCEN       | T1SYNC      | TMR1CS   | TMR10N | 00           | 0000 | uu    | uuuu                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

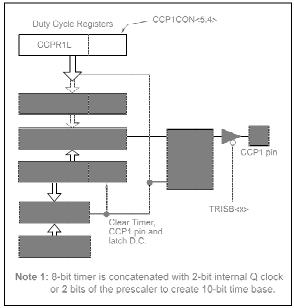

### 9.3 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<x> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTB I/O data |

|       | latch.                                    |

Figure 9-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 9.3.3 "Setup for PWM Operation"**.

#### FIGURE 9-3: SIMPLIFIED PWM BLOCK DIAGRAM

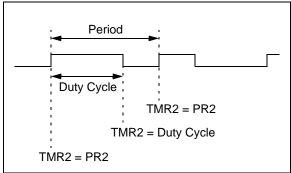

A PWM output (Figure 9-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 9-4: PWM OUTPUT

#### 9.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula.

#### **EQUATION 9-1:**

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

#### 9.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

#### **EQUATION 9-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

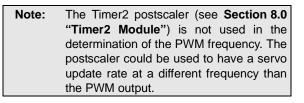

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 11.1** "**A/D Acquisition Requirements**". After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

**FIGURE 11-1:**

#### A/D BLOCK DIAGRAM

© 2001-2013 Microchip Technology Inc.

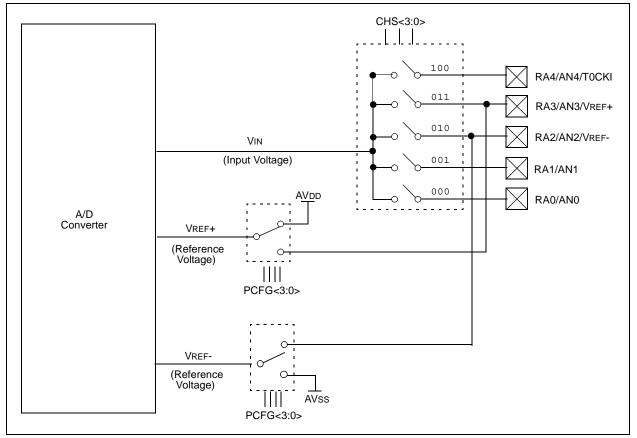

### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 2.5 k\Omega. As the impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### EQUATION 11-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient= TAMP + TC + TCOFF = 2  $\mu$ s + TC + [(Temperature - 25°C)(0.05  $\mu$ s/°C)] TC = CHOLD (RIC + Rss + Rs) In(1/2047) = -120 pF (1 k $\Omega$  + 7 k $\Omega$  + 10 k $\Omega$ ) In(0.0004885) = 16.47  $\mu$ s TACQ = 2  $\mu$ s + 16.47  $\mu$ s + [(50°C - 25°C)(0.05  $\mu$ s/°C) = 19.72  $\mu$ s

Note 1: The reference voltage (VREF) has no effect on the equation since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

| TABLE 12-4: INITIALIZATION CONDITIONS FOR ALL REGISTE |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Register   | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|------------------------------------|--------------------------|---------------------------------|

| W          | xxxx xxxx                          | นนนน นนนน                | นนนน นนนน                       |

| INDF       | N/A                                | N/A                      | N/A                             |

| TMR0       | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL        | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS     | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <sup>(3)</sup>        |

| FSR        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA      | xxx0 0000                          | uuu0 0000                | uuuu uuuu                       |

| PORTB      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH     | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON     | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1       | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| PIR2       | 0                                  |                          | u(1)                            |

| TMR1L      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H      | xxxx xxxx                          | uuuu uuuu                | <u>uuuu</u> uuuu                |

| T1CON      | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2       | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| T2CON      | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON     | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| CCPR1L     | xxxx xxxx                          | <u>uuuu</u> uuuu         | <u>uuuu</u> uuuu                |

| CCPR1H     | xxxx xxxx                          | uuuu uuuu                | <u> </u>                        |

| CCP1CON    | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRESH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA      | 1111 1111                          | 1111 1111                | <u>uuuu</u> uuuu                |

| TRISB      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1       | -0 0000                            | -0 0000                  | -u uuuu                         |

| PIE2       | 0                                  | 0                        | u                               |

| PCON       | dd                                 | uu                       |                                 |

| OSCCON     | -000 -0                            | -000 -0                  | -uuu -u                         |

| OSCTUNE    | 00 0000                            | 00 0000                  | uu uuuu                         |

| PR2        | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD     | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| SSPSTAT    | 0000 0000                          | 0000 0000                | <u>uuuu</u> uuuu                |

| ADRESL     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON1     | 00 0000                            | 00 0000                  | uu uuuu                         |

| EEDATA     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEADR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEDATH     | xx xxxx                            | uu uuuu                  | uu uuuu                         |

| EEADRH     | xxx                                | uuu                      | uuu                             |

| EECON1     | xx x000                            | ux u000                  | uu uuuu                         |

| EECON2     |                                    |                          |                                 |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and PR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-3 for Reset value for specific conditions.

# 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDWF            | AND W with f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                     |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                              |

| Operands:        | $0 \le k \le 255$                                                                                                     |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of W register are<br>ANDed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| Param.<br>No. | Symbol  | Characte                            | eristic                | Min          | Max  | Units | Conditions                                            |          |

|---------------|---------|-------------------------------------|------------------------|--------------|------|-------|-------------------------------------------------------|----------|

| 100*          | Тнідн   | Clock High Time                     | 100 kHz mode           | 4.0          |      | μS    |                                                       |          |

|               |         |                                     | 400 kHz mode           | 0.6          |      | μs    |                                                       |          |

|               |         |                                     | SSP Module             | 1.5 TCY      |      |       |                                                       |          |

| 101*          | TLOW    | Clock Low Time                      | 100 kHz mode           | 4.7          |      | μs    |                                                       |          |

|               |         |                                     | 400 kHz mode           | 1.3          | _    | μs    |                                                       |          |

|               |         |                                     | SSP Module             | 1.5 TCY      | _    |       |                                                       |          |

| 102*          | Tr      | SDA and SCL Rise                    | 100 kHz mode           | —            | 1000 | ns    |                                                       |          |

|               |         | Time                                | 400 kHz mode           | 20 + 0.1 Св  | 300  | ns    | CB is specified to be from 10-400 pF                  |          |

| 103*          | TF      | SDA and SCL Fall<br>Time            | 100 kHz mode           | —            | 300  | ns    |                                                       |          |

|               |         |                                     | 400 kHz mode           | 20 + 0.1 Св  | 300  | ns    | CB is specified to be from 10-400 pF                  |          |

| 90*           | TSU:STA | Start Condition<br>Setup Time       | 100 kHz mode           | 4.7          |      | μs    | Only relevant for Repeate<br>Start condition          |          |

|               |         |                                     | 400 kHz mode           | 0.6          |      | μs    |                                                       |          |

| 91*           | THD:STA | Start Condition Hold<br>Time        | 100 kHz mode           | 4.0          | _    | μs    | After this period, the first clock pulse is generated |          |

|               |         |                                     | 400 kHz mode           | 0.6          |      | μs    |                                                       |          |

| 106*          | THD:DAT | D:DAT Data Input Hold<br>Time       | 100 kHz mode           | 0            | _    | ns    |                                                       |          |

|               |         |                                     | 400 kHz mode           | 0            | 0.9  | μs    |                                                       |          |

| 107*          | TSU:DAT | 7* TSU:DAT Data Input Setup<br>Time | U:DAT Data Input Setup | 100 kHz mode | 250  | _     | ns                                                    | (Note 2) |

|               |         |                                     | 400 kHz mode           | 100          |      | ns    |                                                       |          |

| 92*           | Tsu:sto | SU:STO Stop Condition<br>Setup Time | 100 kHz mode           | 4.7          | _    | μs    |                                                       |          |

|               |         |                                     | 400 kHz mode           | 0.6          | _    | μs    |                                                       |          |

| 109*          | ΤΑΑ     | Output Valid from<br>Clock          | 100 kHz mode           | —            | 3500 | ns    | (Note 1)                                              |          |

|               |         |                                     | 400 kHz mode           | —            |      | ns    |                                                       |          |

| 110*          | TBUF    | Bus Free Time                       | 100 kHz mode           | 4.7          |      | μS    | Time the bus must be free                             |          |

|               |         |                                     | 400 kHz mode           | 1.3          |      | μS    | before a new transmission can start                   |          |

|               | Св      | Bus Capacitive Load                 | ling                   | —            | 400  | pF    |                                                       |          |

### TABLE 15-8: I<sup>2</sup>C™ BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>TM</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system but the requirement, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

# TABLE 15-9:A/D CONVERTER CHARACTERISTICS: PIC16F818/819 (INDUSTRIAL, EXTENDED)PIC16LF818/819 (INDUSTRIAL)

| Param<br>No. | Sym   | Charac                             | teristic                | Min         | Тур†                      | Мах          | Units | Conditions                                                                                                                                    |

|--------------|-------|------------------------------------|-------------------------|-------------|---------------------------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| A01          | Nr    | Resolution                         |                         | _           | —                         | 10-bits      | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A03          | Eı∟   | Integral Linearity Error           |                         | _           | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A04          | Edl   | Differential Linearity Error       |                         |             | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A06          | EOFF  | Offset Error                       |                         | —           | —                         | <±2          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A07          | Egn   | Gain Error                         |                         | _           | —                         | <±1          | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A10          | _     | Monotonicity                       |                         | _           | guaranteed <sup>(3)</sup> | —            | _     | $VSS \leq VAIN \leq VREF$                                                                                                                     |

| A20          | Vref  | Reference Voltage (VREF+ - VREF-)  |                         | 2.0         | —                         | VDD + 0.3    | V     |                                                                                                                                               |

| A21          | Vref+ | Reference Voltage High             |                         | AVdd - 2.5V |                           | AVDD + 0.3V  | V     |                                                                                                                                               |

| A22          | Vref- | Reference Voltage Low              |                         | AVss-0.3V   |                           | VREF+ - 2.0V | V     |                                                                                                                                               |

| A25          | VAIN  | Analog Input Voltage               |                         | Vss - 0.3V  | —                         | VREF + 0.3V  | V     |                                                                                                                                               |

| A30          | ZAIN  | Recommended Ir<br>Analog Voltage S |                         | _           | —                         | 2.5          | kΩ    | (Note 4)                                                                                                                                      |

| A40          | IAD   | A/D Conversion                     | PIC16 <b>F</b> 818/819  | _           | 220                       | —            | μΑ    | Average current                                                                                                                               |

|              |       | Current (VDD)                      | PIC16 <b>LF</b> 818/819 |             | 90                        | —            | μA    | consumption when A/D is on (Note 1)                                                                                                           |

| A50          | IREF  | VREF Input Currei                  | nt <b>(Note 2)</b>      | _           |                           | 5            | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD,<br>see Section 11.1 "A/D<br>Acquisition Requirements". |

|              |       |                                    |                         |             | —                         | 150          | μΑ    | During A/D conversion cycle                                                                                                                   |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

- 3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 4: Maximum allowed impedance for analog voltage source is 10 kΩ. This requires higher acquisition time.

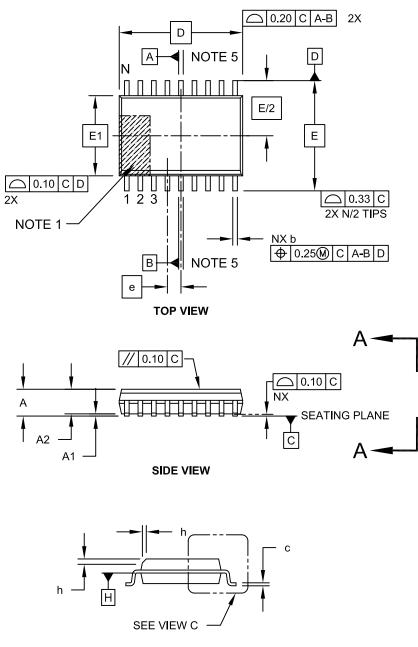

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-051C Sheet 1 of 2

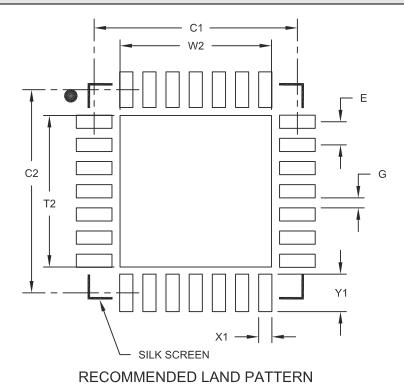

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimensior                  | MIN         | NOM  | MAX      |      |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.25 |

| Optional Center Pad Length | T2          |      |          | 4.25 |

| Contact Pad Spacing        | C1          |      | 5.70     |      |

| Contact Pad Spacing        | C2          |      | 5.70     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1          |      |          | 1.00 |

| Distance Between Pads      | G           | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

# PIC16F818/819

NOTES:

# PIC16F818/819

| TMR0IE Bit 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Oscillator Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INTRC Modes35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Internet Address 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Interrupt Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RB0/INT Pin, External97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMR0 Overflow97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RB7:RB4 Port Change43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synchronous Serial Port Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupts, Context Saving During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupts, Enable Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global Interrupt Enable (GIE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt-on-Change (RB7:RB4) Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (RBIE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RB0/INT Enable (INTE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TMR0 Overflow Enable (TMR0IE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupts, Enable bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global Interrupt Enable (GIE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupts, Flag Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Interrupt-on-Change (RB7:RB4) Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (RBIF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RB0/INT Flag (INTF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMR0 Overflow Flag (TMR0IF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTRC Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INTRC Modes<br>Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |