Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 10MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 16                                                                            |

| Program Memory Size        | 3.5KB (2K x 14)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 256 x 8                                                                       |

| RAM Size                   | 256 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 5x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 18-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf819t-i-sotsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 1.0   | Device Overview                             | 5    |

|-------|---------------------------------------------|------|

| 2.0   | Memory Organization                         | 9    |

| 3.0   | Data EEPROM and Flash Program Memory        | . 25 |

| 4.0   | Oscillator Configurations                   | . 33 |

| 5.0   | I/O Ports                                   | 39   |

| 6.0   | Timer0 Module                               | . 53 |

| 7.0   | Timer1 Module                               | . 57 |

| 8.0   | Timer2 Module                               | . 63 |

| 9.0   | Capture/Compare/PWM (CCP) Module            | . 65 |

| 10.0  | Synchronous Serial Port (SSP) Module        | . 71 |

| 11.0  | Analog-to-Digital Converter (A/D) Module    | . 81 |

| 12.0  | Special Features of the CPU                 | . 89 |

| 13.0  | Instruction Set Summary                     | 103  |

| 14.0  | Development Support                         | 111  |

| 15.0  | Electrical Characteristics                  | 115  |

| 16.0  | DC and AC Characteristics Graphs and Tables | 141  |

| 17.0  | Packaging Information                       | 155  |

| Appe  | ndix A: Revision History                    | 165  |

| Appe  | ndix B: Device Differences                  | 165  |

| INDE  | X                                           | 167  |

| The I | /icrochip Web Site                          | 173  |

| Custo | mer Change Notification Service             | 173  |

| Custo | mer Support                                 | 173  |

| Read  | er Response                                 | 174  |

| PIC1  | 6F818/819 Product Identification System     | 175  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

· Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 2.2.2.8 **PCON Register**

| Note: | Interrupt fleg bits get eet when an interrupt |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

| note: | Interrupt flag bits get set when an interrupt |  |  |  |  |  |  |  |  |

|       | condition occurs regardless of the state of   |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |  |

|       | Interrupt Enable bit, GIE (INTCON<7>).        |  |  |  |  |  |  |  |  |

|       | User software should ensure the appropri-     |  |  |  |  |  |  |  |  |

|       | ate interrupt flag bits are clear prior to    |  |  |  |  |  |  |  |  |

|       | enabling an interrupt.                        |  |  |  |  |  |  |  |  |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

-n = Value at POR

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### **REGISTER 2-8:** PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         | U-0                                                                                                                                                  | U-0          | U-0             | U-0          | U-0      | U-0         | R/W-0        | R/W-x |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|----------|-------------|--------------|-------|--|--|--|--|

|         | _                                                                                                                                                    | _            |                 | —            | _        | _           | POR          | BOR   |  |  |  |  |

|         | bit 7                                                                                                                                                |              |                 |              |          |             |              | bit 0 |  |  |  |  |

| bit 7-2 | Unimplem                                                                                                                                             | ented: Read  | <b>l as</b> '0' |              |          |             |              |       |  |  |  |  |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                       |              |                 |              |          |             |              |       |  |  |  |  |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>    |              |                 |              |          |             |              |       |  |  |  |  |

| bit 0   | BOR: Brow                                                                                                                                            | /n-out Reset | Status bit      |              |          |             |              |       |  |  |  |  |

|         | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |              |                 |              |          |             |              |       |  |  |  |  |

|         | Legend:                                                                                                                                              |              |                 |              |          |             |              |       |  |  |  |  |

|         | R = Reada                                                                                                                                            | able bit     | W = W           | /ritable bit | U = Unim | plemented I | bit, read as | '0'   |  |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

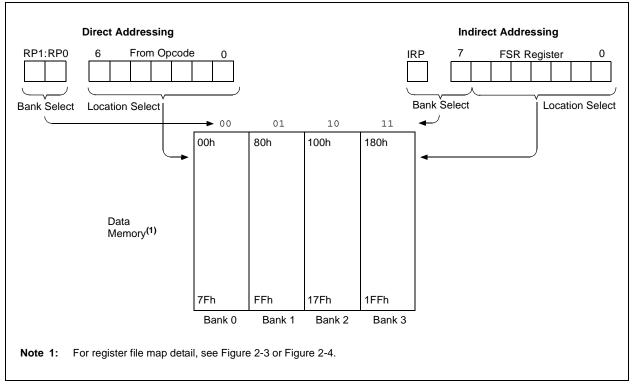

#### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING

| REGISTER 3-1: | EECON1:                                                                                                                                                                                                          | EEPROM                                   | ACCESS C                   | ONTROL       | REGISTER      | 1 (ADDRI      | ESS 18Ch)     |             |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|--------------|---------------|---------------|---------------|-------------|--|--|--|

|               | R/W-x                                                                                                                                                                                                            | U-0                                      | U-0                        | R/W-x        | R/W-x         | R/W-0         | R/S-0         | R/S-0       |  |  |  |

|               | EEPGD                                                                                                                                                                                                            |                                          | _                          | FREE         | WRERR         | WREN          | WR            | RD          |  |  |  |

|               | bit 7                                                                                                                                                                                                            |                                          |                            |              |               |               |               | bit 0       |  |  |  |

| bit 7         | EEPGD: Pr                                                                                                                                                                                                        | ogram/Data                               | EEPROM                     | Select bit   |               |               |               |             |  |  |  |

|               | 0 = Access                                                                                                                                                                                                       | es program<br>es data mei<br>fter a POR; | mory                       | not be chang | ged while a v | write operati | on is in prog | jress.      |  |  |  |

| bit 6-5       | Unimplem                                                                                                                                                                                                         | ented: Read                              | <b>d as</b> '0'            |              |               |               |               |             |  |  |  |

| bit 4         | FREE: EEF                                                                                                                                                                                                        | PROM Force                               | ed Row Eras                | se bit       |               |               |               |             |  |  |  |

|               | 1 = Erase tl<br>0 = Perforn                                                                                                                                                                                      |                                          | memory row                 | addressed    | by EEADRH     | I:EEADR on    | the next WF   | R command   |  |  |  |

| bit 3         | WRERR: E                                                                                                                                                                                                         | EPROM Er                                 | ror Flag bit               |              |               |               |               |             |  |  |  |

|               | operat                                                                                                                                                                                                           | ion)                                     | s premature<br>n completed | -            | d (any MCLI   | R or any WI   | OT Reset du   | ring normal |  |  |  |

| bit 2         | WREN: EE                                                                                                                                                                                                         | PROM Writ                                | e Enable bit               |              |               |               |               |             |  |  |  |

|               | <ul><li>1 = Allows write cycles</li><li>0 = Inhibits write to the EEPROM</li></ul>                                                                                                                               |                                          |                            |              |               |               |               |             |  |  |  |

| bit 1         | WR: Write Control bit                                                                                                                                                                                            |                                          |                            |              |               |               |               |             |  |  |  |

|               | <ul> <li>1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                          |                            |              |               |               |               |             |  |  |  |

| bit 0         | RD: Read                                                                                                                                                                                                         | Control bit                              |                            |              |               |               |               |             |  |  |  |

|               |                                                                                                                                                                                                                  | s an EEPR<br>d) in softwar               |                            | D is cleared | l in hardwar  | e. The RD I   | bit can only  | be set (not |  |  |  |

|               | 0 = Does r                                                                                                                                                                                                       | not initiate a                           | n EEPROM                   | read         |               |               |               |             |  |  |  |

|               | Legend:                                                                                                                                                                                                          |                                          |                            |              |               |               |               | ]           |  |  |  |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Set only         | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

#### 7.5 Timer1 Operation in Asynchronous Counter Mode

If control bit,  $\overline{\text{T1SYNC}}$  (T1CON<2>), is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow that will wake-up the processor. However, special precautions in software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

#### 7.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example codes provided in Example 7-1 and Example 7-2 demonstrate how to write to and read Timer1 while it is running in Asynchronous mode.

| EXAMPLE 7-1:   | WRITING A 16-BIT FREE RUNNING TIMER |

|----------------|-------------------------------------|

| EAAIVIFLE /-I. | WRITING A 10-DIT FREE RUNNING TIMER |

| ; All  | interrupts are | e disabled                                       |  |

|--------|----------------|--------------------------------------------------|--|

| CLRF   | TMR1L          | ; Clear Low byte, Ensures no rollover into TMR1H |  |

| MOVLW  | HI_BYTE        | ; Value to load into TMR1H                       |  |

| MOVWF  | TMR1H, F       | ; Write High byte                                |  |

| MOVLW  | LO_BYTE        | ; Value to load into TMR1L                       |  |

| MOVWF  | TMR1H, F       | ; Write Low byte                                 |  |

| ; Re-e | nable the Inte | errupt (if required)                             |  |

| CONTIN | IUE            | ; Continue with your code                        |  |

|        |                |                                                  |  |

#### EXAMPLE 7-2: READING A 16-BIT FREE RUNNING TIMER

| ; All interrupts are disabled                                            |

|--------------------------------------------------------------------------|

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL                                                               |

| MOVF TMR1H, W ; Read high byte                                           |

| SUBWF TMPH, W ; Sub 1st read with 2nd read                               |

| BTFSC STATUS, Z ; Is result = 0                                          |

| GOTO CONTINUE ; Good 16-bit read                                         |

| ; TMR1L may have rolled over between the read of the high and low bytes. |

| ; Reading the high and low bytes now will read a good value.             |

| MOVF TMR1H, W ; Read high byte                                           |

| MOVWF TMPH                                                               |

| MOVF TMR1L, W ; Read low byte                                            |

| MOVWF TMPL ; Re-enable the Interrupt (if required)                       |

| CONTINUE ; Continue with your code                                       |

|                                                                          |

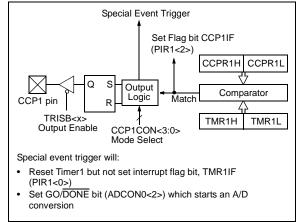

#### 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 9-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 9.2.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the TRISB<x> bit.

- Note 1: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the data latch.

- 2: The TRISB bit (2 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### 9.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 9.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 9.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated that may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

**Note:** The special event trigger from the CCP1 module will not set interrupt flag bit, TMR1IF (PIR1<0>).

#### TABLE 9-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Address              | Name    | Bit 7   | Bit 6                                | Bit 5         | Bit 4         | Bit 3         | Bit 2       | Bit 1     | Bit 1 Bit 0 |      | Value on<br>POR, BOR |      | all off |  | other |

|----------------------|---------|---------|--------------------------------------|---------------|---------------|---------------|-------------|-----------|-------------|------|----------------------|------|---------|--|-------|

| 0Bh,8Bh<br>10BH,18Bh | INTCON  | GIE     | PEIE                                 | TMR0IE        | INTE          | RBIE          | TMR0IF      | INTF      | RBIF        | 0000 | 000x                 | 0000 | 000u    |  |       |

| 0Ch                  | PIR1    | —       | ADIF                                 | _             | —             | SSPIF         | CCP1IF      | TMR2IF    | TMR1IF      | - 0  | 0000                 | - 0  | 0000    |  |       |

| 8Ch                  | PIE1    | —       | ADIE                                 | _             | _             | SSPIE         | CCP1IE      | TMR2IE    | TMR1IE      | - 0  | 0000                 | - 0  | 0000    |  |       |

| 86h                  | TRISB   | PORTE   | 3 Data Dir                           | ection Reg    | ister         |               |             |           |             | 1111 | 1111                 | 1111 | 1111    |  |       |

| 0Eh                  | TMR1L   | Holding | g Register                           | r for the Lea | ast Significa | ant Byte of t | he 16-bit T | MR1 Regi  | ster        | xxxx | xxxx                 | uuuu | uuuu    |  |       |

| 0Fh                  | TMR1H   | Holding | g Register                           | r for the Mo  | st Significa  | nt Byte of th | ne 16-bit T | MR1 Regis | ster        | xxxx | xxxx                 | uuuu | uuuu    |  |       |

| 10h                  | T1CON   | -       |                                      | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC      | TMR1CS    | TMR1ON      | 00   | 0000                 | uu   | uuuu    |  |       |

| 15h                  | CCPR1L  | Capture | Capture/Compare/PWM Register 1 (LSB) |               |               |               |             |           |             |      |                      | uuuu | uuuu    |  |       |

| 16h                  | CCPR1H  | Capture | e/Compar                             | re/PWM Re     | gister 1 (M   | SB)           |             |           |             | xxxx | xxxx                 | uuuu | uuuu    |  |       |

| 17h                  | CCP1CON | _       | _                                    | CCP1X         | CCP1Y         | CCP1M3        | CCP1M2      | CCP1M1    | CCP1M0      | 00   | 0000                 | 00   | 0000    |  |       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

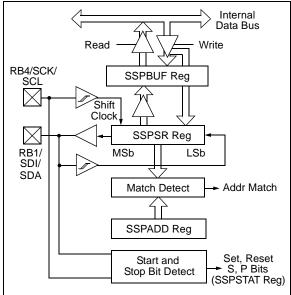

### 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/SCK/SCL pin, which is the clock (SCL) and the RB1/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits.

To ensure proper communication of the I<sup>2</sup>C Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the I<sup>2</sup>C pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the I<sup>2</sup>C pins (PORTx [SDA, SCL]) are changed in software during I<sup>2</sup>C communication using a Read-Modify-Write instruction (BSF, BCF), then the I<sup>2</sup>C mode may stop functioning properly and I<sup>2</sup>C communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the I<sup>2</sup>C pins) using the instruction BSF or BCF during I<sup>2</sup>C communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

#### EXAMPLE 10-1:

| MOVF  | TRISC, W    | ; Example for an 18-pin part such as the PIC16F818/819              |

|-------|-------------|---------------------------------------------------------------------|

| IORLW | 0x18        | ; Ensures <4:3> bits are `11'                                       |

| ANDLW | B'11111001' | ; Sets <2:1> as output, but will not alter other bits               |

|       |             | ; User can use their own logic here, such as IORLW, XORLW and ANDLW |

| MOVWF | TRISC       |                                                                     |

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

FIGURE 10-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for  $I^2C$  operation:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Firmware Controlled Master mode with Start and Stop bit interrupts enabled, slave is Idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation may be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

NOTES:

#### REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

|            |      |                                                     | R/P-1     |                             | -        | 101 1    | R/P-1             | R/P-1              | R/P-1           | -                    | R/P-1        | R/P-1 | R/P-1 |

|------------|------|-----------------------------------------------------|-----------|-----------------------------|----------|----------|-------------------|--------------------|-----------------|----------------------|--------------|-------|-------|

| CP CC      | CPMX | DEBUG                                               | WRT1      | WRT0                        | CPD      | LVP      | BOREN             | MCLRE              | FOSC2           | PWRTEN               | WDTEN        | FOSC1 | FOSC0 |

| oit 13     |      |                                                     |           |                             |          |          |                   |                    |                 |                      |              |       | bit 0 |

| oit 13     |      |                                                     | h Droar   | om Mom                      |          | ha Drat  | ection bit        |                    |                 |                      |              |       |       |

| л 15       |      | 1 = Code                                            |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                                                     | •         | ocations                    | code-p   | rotecte  | ed                |                    |                 |                      |              |       |       |

| oit 12     |      | ССРМХ                                               | : CCP1    | Pin Selec                   | tion bit | :        |                   |                    |                 |                      |              |       |       |

|            |      |                                                     |           | on on RB                    |          |          |                   |                    |                 |                      |              |       |       |

| oit 11     |      |                                                     |           | on on RB                    |          | odo bit  |                   |                    |                 |                      |              |       |       |

| אנוו       |      |                                                     |           | uit Debug<br>bugger d       |          |          | and RB7 a         | are gener          | al purpos       | e I/O pins           |              |       |       |

|            |      |                                                     |           |                             |          |          |                   |                    |                 | e debugger           |              |       |       |

| oit 10-9   |      | WRT1:W                                              | VRTO: F   | lash Prog                   | gram M   | emory    | Write Ena         | able bits          |                 |                      |              |       |       |

|            |      | For PIC1                                            |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 11 = Wri                                            |           |                             |          |          |                   |                    | na a difi a d l |                      | a a vatura l |       |       |

|            |      |                                                     |           |                             |          |          | 10 to 03FF        | may be             | moainea i       | by EECON             | CONTROL      |       |       |

|            |      | 01 = 000h to 03FF write-protected<br>For PIC16F819: |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 11 = Wri                                            | ite prote |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                                                     |           |                             |          |          |                   |                    |                 | ified by EE          |              |       |       |

|            |      |                                                     |           |                             |          |          |                   |                    |                 | ified by EE          |              |       |       |

| oit 8      |      |                                                     |           | lemory C                    |          |          |                   | ////////           | y 50 moa        |                      |              |       |       |

|            |      | 1 = Code                                            |           | •                           |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                                                     |           | mory loca                   |          | -        |                   |                    |                 |                      |              |       |       |

| oit 7      |      |                                                     |           | e Progra                    |          |          |                   | -                  |                 |                      |              |       |       |

|            |      |                                                     |           |                             |          |          | ow-Voltag         |                    |                 | abled<br>ed for prog | rammina      |       |       |

| oit 6      |      |                                                     |           | -out Rese                   |          |          |                   |                    |                 |                      | lanning      |       |       |

|            |      | 1 = BOR                                             |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = BOR                                             | t disable | d                           |          |          |                   |                    |                 |                      |              |       |       |

| oit 5      |      |                                                     |           |                             |          | -        | Select bit        |                    |                 |                      |              |       |       |

|            |      |                                                     |           | VPP pin fu                  |          |          | LR<br>tal I/O, MC | <u>`I P</u> interr | ally tied t     | ם ער                 |              |       |       |

| oit 3      |      |                                                     | _         | er-up Tim                   |          | •        |                   |                    | ially lieu l    | 0 000                |              |       |       |

| ло         |      | 1 = PWF                                             |           | •                           |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = PWF                                             |           |                             |          |          |                   |                    |                 |                      |              |       |       |

| oit 2      |      |                                                     |           | dog Time                    | r Enab   | le bit   |                   |                    |                 |                      |              |       |       |

|            |      | 1 = WDT                                             |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 0 = WDT                                             |           |                             |          | ntion hi | <b>to</b>         |                    |                 |                      |              |       |       |

| oit 4, 1-0 |      |                                                     |           | : Oscillato<br>scillator: ( |          |          | n on RA6/         | OSC2/CI            | KO nin          |                      |              |       |       |

|            |      |                                                     |           |                             |          |          | on on RA6         |                    |                 |                      |              |       |       |

|            |      | 101 = <b>IN</b>                                     | ITRC os   | cillator; C                 | LKO fu   | unction  | on RA6/C          | DSC2/CL            | KO pin ar       | nd port I/O f        | function o   | n     |       |

|            |      |                                                     |           | 1/CLKI p                    |          | functio  | n on hoth         | DAG/OS             |                 | pin and RA           | 17/0901/     |       |       |

|            |      |                                                     |           |                             |          |          | 46/OSC2/          |                    |                 | pin anu rv           | 47/0301/     |       |       |

|            |      | 010 = H                                             | S oscilla | tor                         |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 001 = X                                             |           |                             |          |          |                   |                    |                 |                      |              |       |       |

|            |      | 000 = LF                                            | - oscilla | lor                         |          |          |                   |                    |                 |                      |              |       |       |

|            |      |                                                     |           |                             |          | ramm     |                   |                    |                 |                      |              |       |       |

#### Legend:

R = Readable bitP = Programmable bitU = Unimplemented bit, read as '1'-n = Value when device is unprogrammedu = Unchanged from programmed state

#### 12.2 Reset

The PIC16F818/819 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset during normal operation

- WDT wake-up during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 12-3. These bits are used in software to determine the nature of the Reset. Upon a POR, BOR wake-up from Sleep, the CPU requires or approximately 5-10 µs to become ready for code execution. This delay runs in parallel with any other timers. See Table 12-4 for a full description of Reset states of all registers.

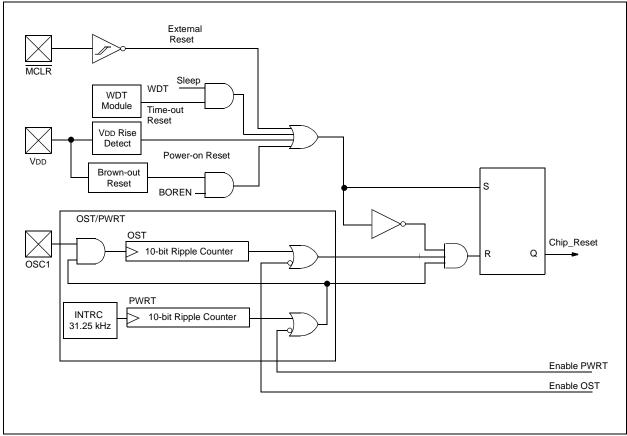

A simplified block diagram of the on-chip Reset circuit is shown in Figure 12-1.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 12.9 Power Control/Status Register (PCON)

The Power Control/Status register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if

# bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is Power-on Reset Status bit,  $\overline{\text{POR}}$ . It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 12-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator           | Power-u             | p                      | Brown-out R         | Wake-up                |                               |

|----------------------|---------------------|------------------------|---------------------|------------------------|-------------------------------|

| Configuration        | PWRTE = 0           | PWRTE = 1              | PWRTE = 0           | PWRTE = 1              | from Sleep                    |

| XT, HS, LP           | TPWRT + 1024 • TOSC | 1024 • Tosc            | TPWRT + 1024 • Tosc | 1024 • Tosc            | 1024 • Tosc                   |

| EXTRC, EXTCLK, INTRC | Tpwrt               | 5-10 μs <sup>(1)</sup> | TPWRT               | 5-10 μs <sup>(1)</sup> | 5-10 μs <b><sup>(1)</sup></b> |

**Note 1:** CPU start-up is always invoked on POR, BOR and wake-up from Sleep.

#### TABLE 12-2: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

**Legend:** u = unchanged, x = unknown

#### TABLE 12-3: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INTF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit, INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep if bit INTE was set prior to going into Sleep. The status of Global Interrupt Enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 "Power-Down Mode (Sleep)" for details on Sleep mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit, TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>) (see **Section 6.0 "Timer0 Module"**).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). See Section 3.2 "EECON1 and EECON2 Registers".

#### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, Status registers). This will have to be implemented in software as shown in Example 12-1.

For PIC16F818 devices, the upper 64 bytes of each bank are common. Temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed here. These 64 locations do not require banking and therefore, make it easier for context save and restore.

For PIC16F819 devices, the upper 16 bytes of each bank are common.

EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS, W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| :      |                |                                                         |

| :(ISR) |                | ;Insert user code here                                  |

| :      |                |                                                         |

| SWAPF  | STATUS_TEMP, W | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP, F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP, W      | ;Swap W_TEMP into W                                     |

|        |                |                                                         |

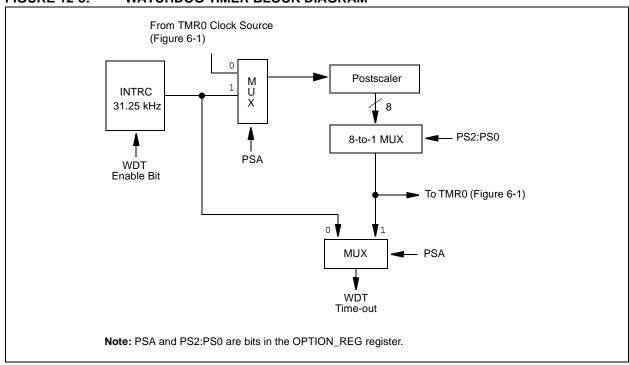

#### 12.12 Watchdog Timer (WDT)

For PIC16F818/819 devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the INTRC (31.25 kHz) oscillator is enabled. The nominal WDT period is 16 ms and has the same accuracy as the INTRC oscillator.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The TO bit in the Status register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit, WDTEN (see **Section 12.1 "Configuration Bits**"). WDT time-out period values may be found in **Section 15.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT prescaler (actually a postscaler but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared but the prescaler assignment is not changed.

#### FIGURE 12-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-5: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                              | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------------|-------|--------|-------|-------|--------|-------|-------|-------|

| 81h,181h | OPTION_REG                        | RBPU  | INTEDG | T0CS  | TOSE  | PSA    | PS2   | PS1   | PS0   |

| 2007h    | Configuration bits <sup>(1)</sup> | LVP   | BOREN  | MCLRE | FOSC2 | PWRTEN | WDTEN | FOSC1 | FOSC0 |

**Legend:** Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

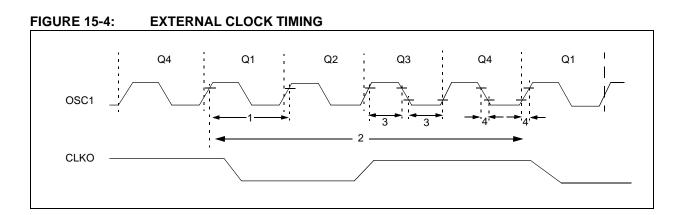

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                |

|--------------|-------|----------------------------------|------|------|--------|-------|---------------------------|

|              | Fosc  | External CLKI Frequency (Note 1) | DC   | _    | 1      | MHz   | XT and RC Oscillator mode |

|              |       |                                  | DC   | _    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | DC   | _    | 32     | kHz   | LP Oscillator mode        |

|              |       | Oscillator Frequency (Note 1)    | DC   |      | 4      | MHz   | RC Oscillator mode        |

|              |       |                                  | 0.1  | _    | 4      | MHz   | XT Oscillator mode        |

|              |       |                                  | 4    | —    | 20     | MHz   | HS Oscillator mode        |

|              |       |                                  | 5    | _    | 200    | kHz   | LP Oscillator mode        |

| 1            | Tosc  | External CLKI Period (Note 1)    | 1000 | —    | —      | ns    | XT and RC Oscillator mode |

|              |       |                                  | 50   | —    | —      | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | —    | —      | ms    | LP Oscillator mode        |

|              |       | Oscillator Period (Note 1)       | 250  | _    | —      | ns    | RC Oscillator mode        |

|              |       |                                  | 250  |      | 10,000 | ns    | XT Oscillator mode        |

|              |       |                                  | 50   |      | 250    | ns    | HS Oscillator mode        |

|              |       |                                  | 5    | _    | _      | ms    | LP Oscillator mode        |

| 2            | Тсү   | Instruction Cycle Time (Note 1)  | 200  | TCY  | DC     | ns    | TCY = 4/FOSC              |

| 3            | TosL, | External Clock in (OSC1) High    | 500  |      | _      | ns    | XT Oscillator             |

|              | TosH  | or Low Time                      | 2.5  | _    | _      | ms    | LP Oscillator             |

|              |       |                                  | 15   | _    | _      | ns    | HS Oscillator             |

| 4            | TosR, | External Clock in (OSC1) Rise or | —    |      | 25     | ns    | XT Oscillator             |

|              | TosF  | Fall Time                        | —    | _    | 50     | ns    | LP Oscillator             |

|              |       |                                  | —    | _    | 15     | ns    | HS Oscillator             |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

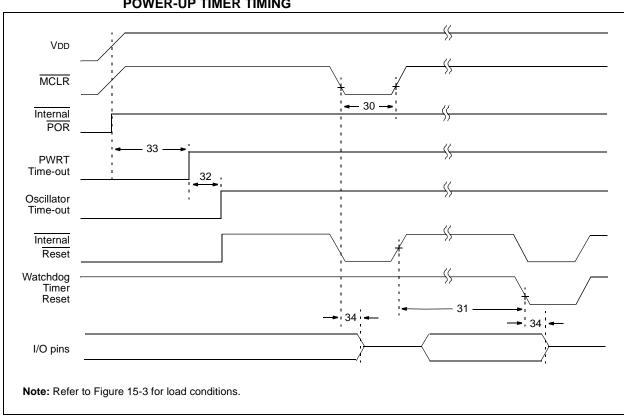

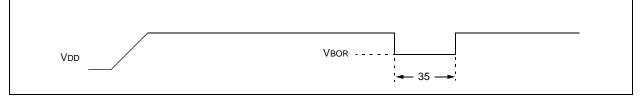

### FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### FIGURE 15-7: BROWN-OUT RESET TIMING

### TABLE 15-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Symbol | Characteristic                                              | Min                                                                                                                                                                                                                                                                           | Тур†                                                                                                                                                                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                     | Units                                                                                                                                                                                                                                              | Conditions                                                                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMCL   | MCLR Pulse Width (Low)                                      | 2                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                         | μS                                                                                                                                                                                                                                                 | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                   |

| Twdt   | Watchdog Timer Time-out Period<br>(no prescaler)            | 13.6                                                                                                                                                                                                                                                                          | 16                                                                                                                                                                                                                                                                                                    | 18.4                                                                                                                                                                                                                                                                                                                                    | ms                                                                                                                                                                                                                                                 | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                   |

| Tost   | Oscillation Start-up Timer Period                           |                                                                                                                                                                                                                                                                               | 1024 Tosc                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                    | Tosc = OSC1 period                                                                                                                                                                                                                                         |

| TPWRT  | Power-up Timer Period                                       | 61.2                                                                                                                                                                                                                                                                          | 72                                                                                                                                                                                                                                                                                                    | 82.8                                                                                                                                                                                                                                                                                                                                    | ms                                                                                                                                                                                                                                                 | VDD = 5V, -40°C to +85°C                                                                                                                                                                                                                                   |

| Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset | —                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                     | 2.1                                                                                                                                                                                                                                                                                                                                     | μS                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                            |

| TBOR   | Brown-out Reset Pulse Width                                 | 100                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                       | μS                                                                                                                                                                                                                                                 | $VDD \leq VBOR (D005)$                                                                                                                                                                                                                                     |

|        | TMCL<br>TWDT<br>TOST<br>TPWRT<br>TIOZ                       | TMCL       MCLR Pulse Width (Low)         TWDT       Watchdog Timer Time-out Period (no prescaler)         TOST       Oscillation Start-up Timer Period         TPWRT       Power-up Timer Period         TIOZ       I/O High-Impedance from MCLR Low or Watchdog Timer Reset | TMCL     MCLR Pulse Width (Low)     2       TWDT     Watchdog Timer Time-out Period<br>(no prescaler)     13.6       TOST     Oscillation Start-up Timer Period     —       TPWRT     Power-up Timer Period     61.2       TIOZ     I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset     — | TMCL     MCLR Pulse Width (Low)     2       TWDT     Watchdog Timer Time-out Period<br>(no prescaler)     13.6     16       TOST     Oscillation Start-up Timer Period     —     1024 Tosc       TPWRT     Power-up Timer Period     61.2     72       TIOZ     I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset     —     — | TMCLMCLR Pulse Width (Low)2—TWDTWatchdog Timer Time-out Period<br>(no prescaler)13.61618.4TOSTOscillation Start-up Timer Period—1024 Tosc—TPWRTPower-up Timer Period61.27282.8TIOZI/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset——2.1 | TMCLMCLR Pulse Width (Low)2—μsTWDTWatchdog Timer Time-out Period<br>(no prescaler)13.61618.4msTOSTOscillation Start-up Timer Period—1024 Tosc——TPWRTPower-up Timer Period61.27282.8msTIOZI/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset—2.1μs |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

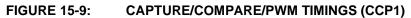

TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Symbol        |                    | Characteristic   |                         |                        | Тур† | Max | Units | Conditions                        |

|--------------|---------------|--------------------|------------------|-------------------------|------------------------|------|-----|-------|-----------------------------------|

| 50*          | TCCL          | CCP1               | No Prescaler     |                         | 0.5 Tcy + 20           | —    | —   | ns    |                                   |

|              |               | Input Low Time     |                  | PIC16F818/819           | 10                     | —    | —   | ns    |                                   |

|              |               |                    | With Prescaler   | PIC16 <b>LF</b> 818/819 | 20                     | —    | —   | ns    |                                   |

| 51*          | 51* TccH CCP1 |                    |                  |                         | 0.5 TCY + 20           |      | _   | ns    |                                   |

|              |               | Input High<br>Time |                  | PIC16F818/819           | 10                     |      | _   | ns    |                                   |

|              |               |                    | With Prescaler   | PIC16 <b>LF</b> 818/819 | 20                     |      | —   | ns    |                                   |

| 52*          | TCCP          | CCP1 Input Per     | CP1 Input Period |                         | <u>3 Tcy + 40</u><br>N | —    | —   | ns    | N = prescale<br>value (1,4 or 16) |

| 53*          | TCCR          | CCP1 Output R      | ise Time         | PIC16F818/819           | —                      | 10   | 25  | ns    |                                   |

|              |               |                    |                  | PIC16 <b>LF</b> 818/819 | —                      | 25   | 50  | ns    |                                   |

| 54*          | TccF          | CCP1 Output Fa     | all Time         | PIC16F818/819           | —                      | 10   | 25  | ns    |                                   |

|              |               |                    |                  | PIC16 <b>LF</b> 818/819 | —                      | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

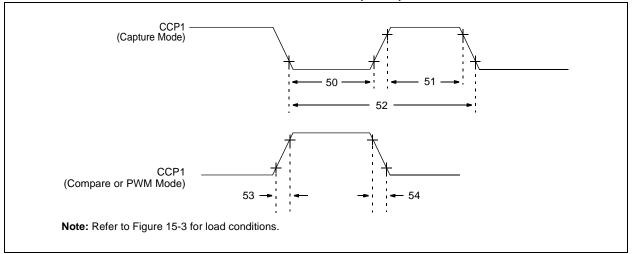

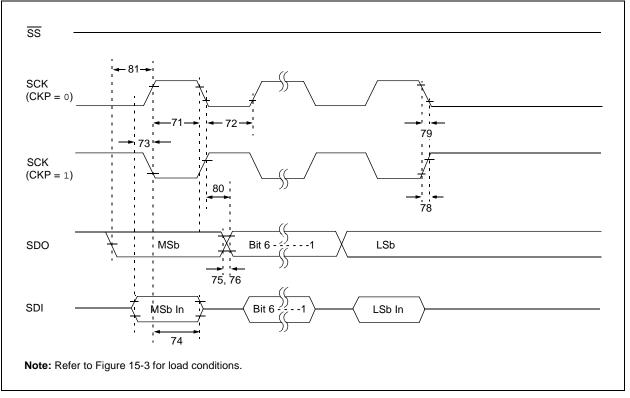

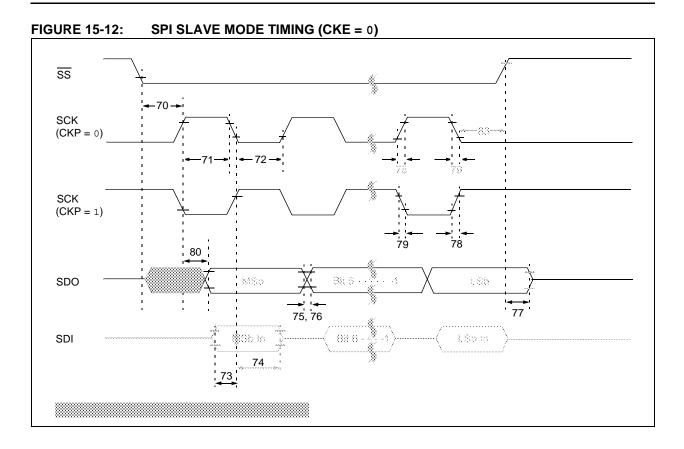

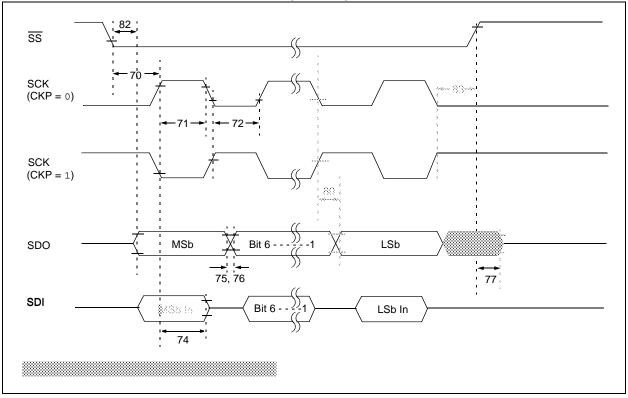

#### FIGURE 15-10: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

#### FIGURE 15-11: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

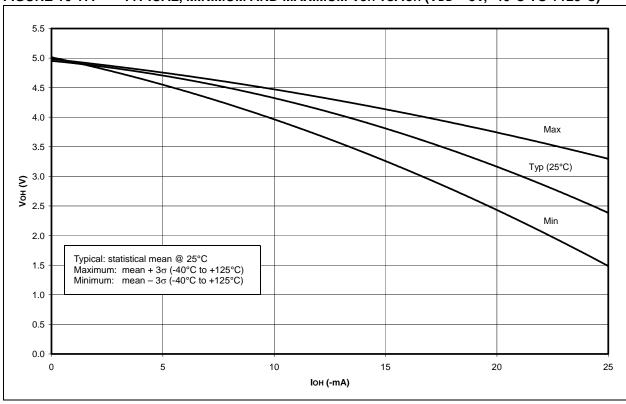

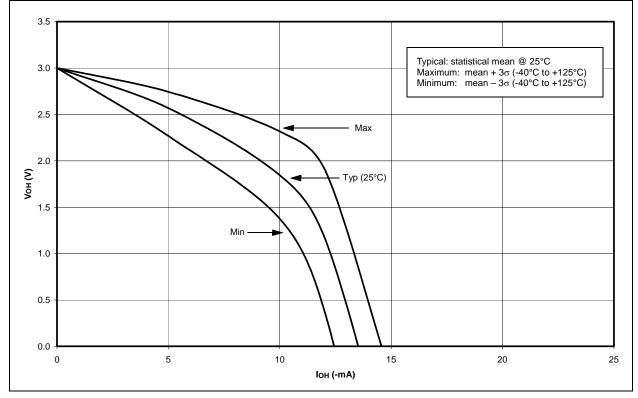

FIGURE 16-17: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

NOTES: