Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                           |

| Core Processor                  | MIPS-I                                                                             |

| Number of Cores/Bus Width       | 1 Core, 64-Bit                                                                     |

| Speed                           | 200MHz                                                                             |

| Co-Processors/DSP               | System Control; CP0                                                                |

| RAM Controllers                 | -                                                                                  |

| Graphics Acceleration           | No                                                                                 |

| Display & Interface Controllers | -                                                                                  |

| Ethernet                        | -                                                                                  |

| SATA                            | -                                                                                  |

| USB                             | -                                                                                  |

| Voltage - I/O                   | 3.3V                                                                               |

| Operating Temperature           | 0°C ~ 85°C (TC)                                                                    |

| Security Features               | -                                                                                  |

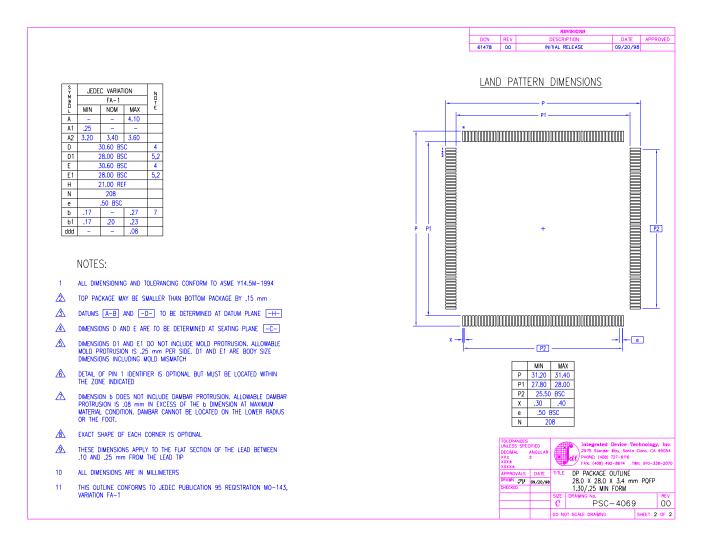

| Package / Case                  | 208-BFQFP Exposed Pad                                                              |

| Supplier Device Package         | 208-PQFP (28x28)                                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/idt79rv4700-200dp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### IDT79R4700

This data sheet provides an overview of the R4700's CPU features and architecture. A more detailed description of this processor is provided in the *IDT79R4700 RISC Processor Hardware User's Manual*, available from Integrated Device Technology (IDT). Information on development support, applications notes and complementary products is available on the IDT Web site **www.idt.com** or through your local IDT sales representative.

**Note**: Throughout this data sheet and any other IDT materials for this device, the R4700 indicates a 5V part; RV4700 designates a reduced voltage (3V) part; and the RC4700 reflects either.

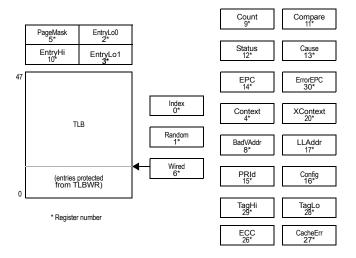

Figure 1 The RC4700 CPO Registers

#### **Hardware Overview**

The RC4700 processor family brings a high-level of integration designed for high-performance computing. The R4700's key elements are briefly described below. A more detailed explanation of each subsystem is available in the user's manual.

#### **Pipeline**

The RC4700 uses a simple 5-stage pipeline, similar to the pipeline structure implemented in the IDT79R32364. This pipeline's simplicity allows the RC4700 to be lower cost and lower power than super-scalar or super-pipelined processors. The pipeline stages are shown in Figure 3 on page 3.

#### **Integer Execution Engine**

The R4700 implements the MIPS-III Instruction Set architecture and is upwardly compatible with applications that run on earlier generation parts.

Implementation of the MIPS-III architecture results in 64-bit operations, better code density, greater multi-processing support, improved performance for commonly used code sequences in operating system kernels and faster execution of floating-point intensive applications. All resource dependencies are made transparent to the programmer, insuring transportability among implementations of the MIPS instruction set architecture.

The MIPS integer unit implements a load/store architecture with single cycle ALU operations (logical, shift, add, sub) and an autonomous multiply/divide unit. Register resources include:

- 32 general-purpose orthogonal integer registers

- HI/LO result registers, for the integer multiply/divide unit

- Program counter

Also, the on-chip floating-point co-processor adds 32 floating-point registers and a floating-point control/status register.

#### **Register File**

The R4700 has 32 general-purpose registers (shown in Figure 2). These registers are used for scalar integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

| General I | General Purpose Registers |    | Multiply/Divide Registers |  |  |

|-----------|---------------------------|----|---------------------------|--|--|

| 63        | 0                         |    |                           |  |  |

|           | 0                         | 63 | 0                         |  |  |

|           | r1                        |    | HI                        |  |  |

|           | r2                        | 63 | 0                         |  |  |

|           | •                         |    | LO                        |  |  |

|           | •                         | -  |                           |  |  |

|           | •                         |    | Program Counter           |  |  |

|           | •                         | 63 | 0                         |  |  |

|           | r29                       |    | PC                        |  |  |

|           | r30                       | ,  | <u>'</u>                  |  |  |

|           | r31                       |    |                           |  |  |

Figure 2 R4700 CPU Registers

#### **ALU**

The RC4700 ALU consists of the integer adder and logic unit. The adder performs address calculations in addition to arithmetic operations, and the logic unit performs all logical and shift operations. Each of these units is highly optimized and can perform an operation in a single pipeline cycle.

### **Integer Multiply/Divide**

To perform integer multiply and divide operations, the RC4700 uses the floating-point unit. The results of the operation are placed in the HI and LO registers. The values can then be transferred to the general purpose register file using the MFHI/MFLO instructions. To prevent the

The RC4700 processor also supports a supervisor mode in which the virtual address space is 256.5GB (2.5GB in 32-bit address mode), divided into three regions that are based on the high-order bits of the virtual address. If the RC4700 is configured for 64-bit virtual addressing, the virtual address space layout is an upwardly compatible extension of the 32-bit virtual address space layout. Figure 4 on page 5 shows the address space layout for the 32-bit virtual address operation.

### **Memory Management Unit (MMU)**

The Memory management unit controls the virtual memory system page mapping. It consists of an instruction address translation buffer (the ITLB), a data address translation buffer (the DTLB), a Joint TLB (the JTLB), and co-processor registers used for the virtual memory mapping sub-system.

#### Instruction TLB (ITLB)

The RC4700 also incorporates a two-entry instruction TLB. Each entry maps a 4KB page. The instruction TLB improves performance by allowing instruction address translation to occur in parallel with data address translation. When a miss occurs on an instruction address translation, the least-recently used ITLB entry is filled from the JTLB. The operation of the ITLB is invisible to the user.

#### **Data TLB (DTLB)**

The RC4700 also incorporates a four-entry data TLB. Each entry maps a 4KB page. The data TLB improves performance by allowing data address translation to occur in parallel with instruction address translation. When a miss occurs on a data address translation, the DTLB is filled from the JTLB. The DTLB refill is pseudo-LRU: the least recently used entry of the least recently used half is filled. The operation of the DTLB is invisible to the user.

#### Joint TLB (JTLB)

For fast virtual-to-physical address decoding, the RC4700 uses a large, fully associative TLB that maps 96 virtual pages to their corresponding physical addresses. The TLB is organized as 48 pairs of even-odd entries and maps a virtual address and address space identifier into the large, 64GB physical address space.

Two mechanisms are provided to assist in controlling the amount of mapped space and the replacement characteristics of various memory regions. First, the page size can be configured, on a per-entry basis, to map a page size of 4KB to 16MB (in multiples of 4). A CP0 register is loaded with the page size of a mapping, and that size is entered into the TLB when a new entry is written. Thus, operating systems can provide special purpose maps; for example, a typical frame buffer can be memory mapped using only one TLB entry.

The second mechanism controls the replacement algorithm, when a TLB miss occurs. The RC4700 provides a random replacement algorithm to select a TLB entry to be written with a new mapping; however, the processor provides a mechanism whereby a system specific number

of mappings can be locked into the TLB and avoid being randomly replaced. This facilitates the design of real-time systems, by allowing deterministic access to critical software.

The joint TLB also contains information to control the cache coherency protocol for each page. Specifically, each page has attribute bits to determine whether the coherency algorithm is uncached, non-coherent write-back, non-coherent write-through write-allocate or non-coherent write-through no write-allocate. Non-coherent write-back is typically used for both code and data on the RC4700; however, hardware-based cache coherency is not supported.

| 0xFFFFFFF  | Kernel virtual address space (kseg3)                  |

|------------|-------------------------------------------------------|

| 0xE0000000 | Mapped, 0.5GB                                         |

| 0xDFFFFFF  | Supervisor virtual address space                      |

|            | (sseg)<br>Mapped, 0.5GB                               |

| 0xC0000000 |                                                       |

| 0xBFFFFFF  | Uncached kernel physical address space                |

| 0xA0000000 | (kseg1)<br>Unmapped, 0.5GB                            |

| 0x9FFFFFF  |                                                       |

|            | Cached kernel physical address space (kseg0)          |

|            | Unmapped, 0.5GB                                       |

| 0x80000000 |                                                       |

| 0x7FFFFFF  |                                                       |

|            | User virtual address space<br>(useg)<br>Mapped, 2.0GB |

| 0x00000000 |                                                       |

Figure 4 Kernel Mode Virtual Addressing (32-bit Mode)

## **Cache Memory**

To keep the RC4700's high-performance pipeline full and operating efficiently, the RC4700 incorporates on-chip instruction and data caches that can be accessed in a single processor cycle. Each cache has its own 64-bit data path and can be accessed in parallel.

#### **Instruction Cache**

The RC4700 incorporates a two-way set associative on-chip instruction cache. This virtually indexed, physically tagged cache is 16KB in size and is protected with word parity.

#### IDT79R4700

Because the cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access, further increasing performance by allowing these two operations to occur simultaneously. The tag holds a 24-bit physical address and valid bit and is parity protected.

The instruction cache is 64-bits wide and can be refilled or accessed in a single processor cycle. For a peak instruction bandwidth of 800MB/sec at 200MHz, instruction fetches require only 32 bits per cycle. To reduce power dissipation, sequential accesses take advantage of the 64-bit fetch. To minimize the cache miss penalty, cache miss refill writes use 64 bits-per-cycle, and to maximize cache performance, the line size is eight instructions (32 bytes).

#### **Data Cache**

For fast, single cycle data access, the RC4700 includes a 16KB onchip data cache that is two-way set associative with a fixed 32-byte (eight words) line size.

The data cache is protected with byte parity and its tag is protected with a single parity bit. It is virtually indexed and physically tagged to allow simultaneous address translation and data cache access

The normal write policy is writeback, which means that a store to a cache line does not immediately cause memory to be updated. This increases system performance by reducing bus traffic and eliminating the bottleneck of waiting for each store operation to finish before issuing a subsequent memory operation. Software can however select write-through on a per-page basis when it is appropriate, such as for frame buffers.

Associated with the data cache is the store buffer. When the RC4700 executes a Store instruction, this single-entry buffer gets written with the store data while the tag comparison is performed. If the tag matches, then the data is written into the data cache in the next cycle that the data cache is not accessed (the next non-load cycle). The store buffer allows the R4700 to execute a store instruction every processor cycle and to perform back-to-back stores without penalty.

The data cache can provide 8 bytes each clock cycle, for a peak bandwidth of 1.6 GB/sec.

#### Write Buffer

Writes to external memory—whether they are cache miss write-backs, stores to uncached or write-through addresses—use the on-chip write buffer. The write buffer holds a maximum of four 64-bit address and 64-bit data pairs. The entire buffer is used for a data cache writeback and allows the processor to proceed in parallel with memory updates.

## **System Interface**

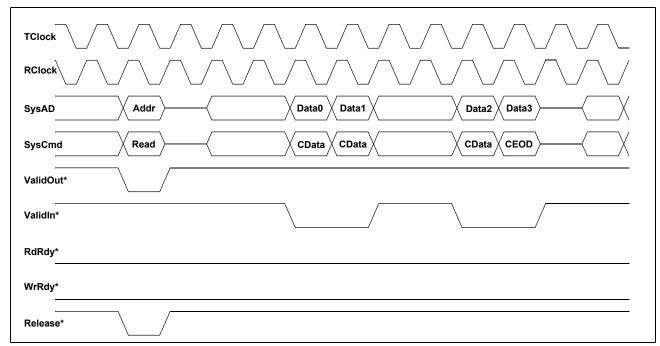

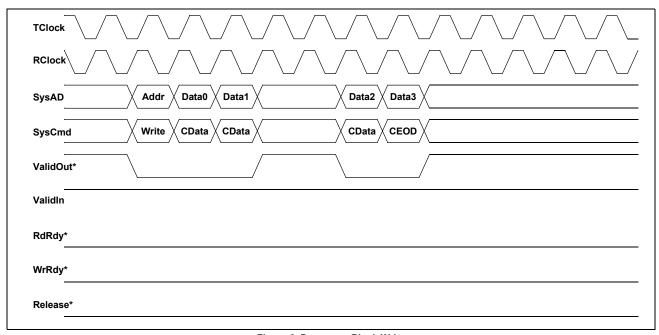

The RC4700 supports a 64-bit system interface. This interface operates from two clocks—TClock[1:0] and RClock[1:0]—provided by the RC4700, at some division of the internal clock.

The system interface consists of a 64-bit Address/Data bus with eight check bits and a 9-bit command bus protected with parity. In addition, there are eight handshake signals and six interrupt inputs. The interface has a simple timing specification and is capable of transferring data between the processor and memory at a peak rate of 500MB/sec with a 67MHz bus.

#### System Address/Data Bus

The 64-bit System Address Data (SysAD) bus is used to transfer addresses and data between the RC4700 and the rest of the system. It is protected with an 8-bit parity check bus, SysADC.

The system interface is configurable to allow easier interfacing to memory and I/O systems of varying frequencies. The data rate and the bus frequency at which the RC4700 transmits data to the system interface are programmable via boot time mode control bits. Also, the rate at which the processor receives data is fully controlled by the external device. Therefore, either a low cost interface requiring no read or write buffering or a faster, high performance interface can be designed to communicate with the RC4700. Again, the system designer has the flexibility to make these price/performance trade-offs.

#### **System Command Bus**

The RC4700 interface has a 9-bit System Command (SysCmd) bus. The command bus indicates whether the SysAD bus carries an address or data. If the SysAD carries an address, then the SysCmd bus also indicates what type of transaction is to take place (for example, a read or write). If the SysAD carries data, then the SysCmd bus also gives information about the data (for example, this is the last data word transmitted, or the cache state of this data line is clean exclusive). The SysCmd bus is bidirectional to support both processor requests and external requests to the RC4700. Processor requests are initiated by the RC4700 and responded to by an external device. External requests are issued by an external device and require the RC4700 to respond.

The RC4700 supports one to eight byte and block transfers on the SysAD bus. In the case of a sub-doubleword transfer, the low-order three address bits give the byte address of the transfer, and the SysCmd bus indicates the number of bytes being transferred.

#### **Handshake Signals**

There are six handshake signals on the system interface. Two of these, RdRdy\* and WrRdy\* are used by an external device to indicate to the RC4700 whether it can accept a new read or write transaction. The RC4700 samples these signals before deasserting the address on read and write requests.

ExtRqst\* and Release\* are used to transfer control of the SysAD and SysCmd buses between the processor and an external device. When an external device needs to control the interface, it asserts ExtRqst\*. The RC4700 responds by asserting Release\* to release the system interface to slave state.

ValidOut\* and ValidIn\* are used by the RC4700 and the external device respectively to indicate that there is a valid command or data on the SysAD and SysCmd buses. The RC4700 asserts ValidOut\* when it is driving these buses with a valid command or data, and the external device drives ValidIn\* when it has control of the buses and is driving a valid command or data.

## **Non-overlapping System Interface**

The RC4700 bus uses a non-overlapping system interface. This means that only one processor request may be outstanding at a time and that the request must be serviced by an external device before the RC4700 issues another request. The RC4700 can issue read and write requests to an external device, and an external device can issue read and write requests to the RC4700.

For processor read transaction the RC4700 asserts ValidOut\* and simultaneously drives the address and read command on the SysAD and SysCmd buses. If the system interface has RdRdy\* asserted, then the processor tristates its drivers and releases the system interface to slave state by asserting Release\*. The external device can then begin sending the data.

Figure 5 on page 10 shows a processor block read request and the external agent read response. The read latency is four cycles (ValidOut\* to ValidIn\*), and the response data pattern is DDxxDD. Figure 6 on page 10 shows a processor block write.

### **Write Reissue and Pipeline Write**

The RC4700 implements additional write protocols that have been designed to improve performance. This implementation doubles the effective write bandwidth. The write re-issue has a high repeat rate of two cycles per write. A write issues if WrRdy\* is asserted two cycles earlier and is still asserted at the issue cycle. If it is not still asserted, the last write re-issues again. Pipelined writes have the same two cycle per write repeat rate but can issue one additional write after WrRdy\* deasserts. They still follow the issue rule as R4x00 mode for other writes.

#### **External Requests**

The RC4700 responds to requests issued by an external device. The requests can take several forms. An external device may need to supply data in response to an RC4700 read request or it may need to gain control over the system interface bus to access other resources which may be on that bus. It also may issue requests to the processor, such as a request for the RC4700 to write to the RC4700 interrupt register. The RC4700 supports Write, Null, and Read Response external requests.

## **Boot-Time Options**

Fundamental operational modes for the processor are initialized by the boot-time mode control interface. The boot-time mode control interface is a serial interface operating at a very low frequency (MasterClock divided by 256). The low-frequency operation allows the initialization information to be kept in a low-cost serial EEPROM; alternatively, the 20-or-so bits could be generated by the system interface ASIC or a simple PAL.

Immediately after the VCCOK signal is asserted, the processor reads a bit stream of 256 bits to initialize all fundamental operational modes. After initialization is complete, the processor continues to drive the serial clock output, but no further initialization bits are read.

#### JTAG Interface

The RC4700 supports the JTAG interface pins, with the serial input connected to serial output. Boundary scan is not supported.

#### **Boot-Time Modes**

The boot-time serial mode stream is defined in Table 3. Bit 0 is the first bit presented to the processor when VCCOK is asserted; bit 255 is the last.

# **Power Management<sup>1</sup>**

CP0 is also used to control the power management for the RC4700. This is the standby mode and can be used to reduce the power consumption of the internal core of the CPU. Standby mode is entered by executing the WAIT instruction with the SysAD bus idle and is exited by an interrupt.

### **Standby Mode Operations**

The RC4700 provides a means to reduce the amount of power consumed by the internal core when the CPU would otherwise not be performing any useful operations. This is known as "Standby Mode."

#### **Entering Standby Mode**

Executing the WAIT instruction enables interrupts and enters Standby mode. When the WAIT instruction finishes the W pipe-stage, if the SysAd bus is currently idle, the internal clocks will shut down, thus freezing the pipeline. The PLL, internal timer, some of the input pin clocks (Int[5:0]\*, NMI\*, ExtReq\*, Reset\*, and ColdReset\*), and the output clocks—TClock[1:0], RClock[1:0] SyncOut, Modeclock and MasterOut—will continue to run. If the conditions are not correct when the WAIT instruction finishes the W pipe-stage (such as the SysAd bus is not idle), the WAIT is treated as a NOP.

Once the CPU is in Standby Mode, any interrupt— including the internally generated timer interrupt—will cause the CPU to exit Standby Mode.

<sup>1.</sup> The R4700 implements advanced power management, to substantially reduce the average power dissipation of the device. This operation is described in the R4700 Microprocessor Hardware User's Manual.

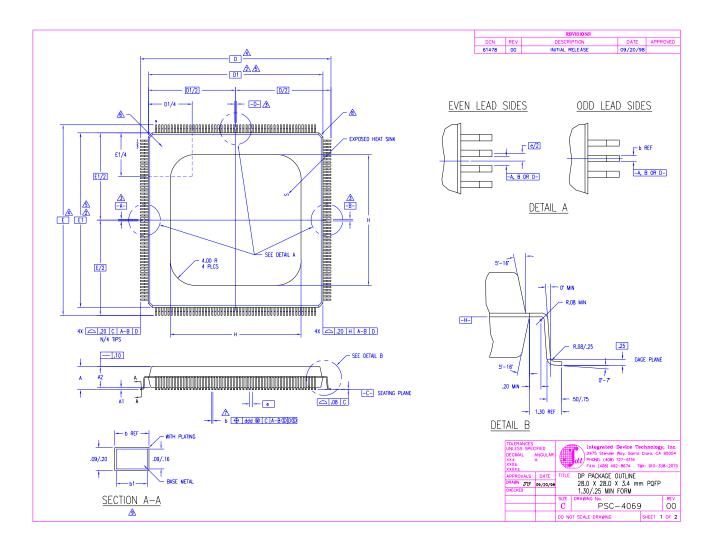

#### **Thermal Considerations**

The RC4700 uses special packaging techniques to improve the thermal properties of high-speed processors. The RC4700 is packaged using cavity down packaging in a 179-pin PGA package, and a 208-lead QFP package. These packages effectively dissipate the power of the CPU, increasing device reliability.

The R4700 is guaranteed in a case temperature range of  $0^{\circ}$  to  $+85^{\circ}$  C. The type of package, speed (power) of the device, and airflow conditions affect the equivalent ambient temperature conditions that will meet this specification.

The equivalent allowable ambient temperature, TA, can be calculated using the thermal resistance from case to ambient ( $\varnothing$ CA) of the given package. The following equation relates ambient and case temperatures:

where P is the maximum power consumption at hot temperature, calculated by using the maximum ICC specification for the device.

Typical values for  $\varnothing$ CA at various airflows are shown in Table 2:.

|                  | Ø <b>c</b> A |     |     |     |     |      |

|------------------|--------------|-----|-----|-----|-----|------|

| Airflow (ft/min) | 0            | 200 | 400 | 600 | 800 | 1000 |

| PGA              | 16           | 7   | 5   | 3   | 2.5 | 2    |

| QFP              | 21           | 13  | 10  | 9   | 8   | 7    |

Table 2: Thermal Resistance (ØCA) at Various Airflows

## **Revision History**

January 1996: Initial draft.

March 1997: Deleted data on 150MHz speed for 5V part only.

**August 1997:** Upgraded 80 to 175 MHz speed specs from "Preliminary" to "Final."

**June 1999:** Upgraded speed to 200MHz on 3V part specs. Package change to DP.

June 29, 2000: Added back 175 and 200 MHz speeds.

**April 10, 2001**: In the Data Output category of the System Interface Parameters tables, changed values in the Min column for all speeds from 1.0 to 0.

**December 5, 2008**: Removed IDT from ordering codes on Ordering Information page.

| Mode bit | Description                                                                                                                                                                                                                                                            | Mode bit | Description                                                                                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | reserved (must be zero)                                                                                                                                                                                                                                                | 14:13    | Output driver strength $10 \rightarrow 100\%$ strength (fastest), $11 \rightarrow 83\%$ strength, $00 \rightarrow 67\%$ strength, $01 \rightarrow 50\%$ strength (slowest) |

| 4:1      | Writeback data rate $0 \rightarrow \Delta$ , $1 \rightarrow DDx$ , $2 \rightarrow DDxx$ , $3 \rightarrow DxDx$ , $4 \rightarrow DDxxx$ , $5 \rightarrow DDxxxx$ , $6 \rightarrow DxxDxx$ , $7 \rightarrow DDxxxxx$ , $8 \rightarrow DxxDxx$ , $9 \rightarrow reserved$ | bit 15   | 0 → TClock[0] enabled 1 → TClock[0] disabled                                                                                                                               |

| 7:5      | Clock divisor $0 \rightarrow 2$ , $1 \rightarrow 3$ , $2 \rightarrow 4$ , $3 \rightarrow 5$ , $4 \rightarrow 6$ , $5 \rightarrow 7$ , $6 \rightarrow 8$ , $7$ reserved                                                                                                 | bit 16   | 0 → TClock[1] enabled<br>1 → TClock[1] disabled                                                                                                                            |

| 8        | 0 → Little endian,<br>1 → Big endian                                                                                                                                                                                                                                   | bit 17   | $0 \rightarrow RClock[0]$ enabled $1 \rightarrow RClock[0]$ disabled                                                                                                       |

| 10:9     | 00 → R4000 compatible,<br>01 → reserved,<br>10 → pipelined writes,<br>11 → write re-issue                                                                                                                                                                              | bit 18   | 0 → RClock[1] enabled<br>1 →RClock[1] disabled                                                                                                                             |

| 11       | Disable the timer interrupt on Int[5].  0 → Enabled  1 → Disabled                                                                                                                                                                                                      | 255:19   | Reserved (must be zero)                                                                                                                                                    |

| 12       | reserved (must be zero)                                                                                                                                                                                                                                                |          |                                                                                                                                                                            |

Table 3 Boot-time Serial Mode Stream

Figure 5 Processor Block Read

Figure 6 Processor Block Write

# **Pin Description**

The table below provides a list of interface, interrupt and miscellaneous pins that are available on the RC4700. Note that signals marked with an asterisk are active when low. Boundary scan is not supported.

| Pin Name                                                                                                                                                         | Туре                                                                                        | Description                                                                                                                                                  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System Interface                                                                                                                                                 |                                                                                             |                                                                                                                                                              |  |  |  |

| ExtRqst*                                                                                                                                                         | * I External request Signals that the system interface needs to submit an external request. |                                                                                                                                                              |  |  |  |

| Release*                                                                                                                                                         | 0                                                                                           | Release interface Signals that the processor is releasing the system interface to slave state.                                                               |  |  |  |

| RdRdy*                                                                                                                                                           | I                                                                                           | Read Ready Signals that an external agent can now accept a processor read.                                                                                   |  |  |  |

| WrRdy*                                                                                                                                                           | I                                                                                           | Write Ready Signals that an external agent can now accept a processor write request.                                                                         |  |  |  |

| ValidIn*                                                                                                                                                         | I                                                                                           | Valid Input Signals that an external agent is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus. |  |  |  |

| ValidOut* O Valid output Signals that the processor is now driving a valid address or data on the SysAD bus and a valid comma data identifier on the SysCmd bus. |                                                                                             |                                                                                                                                                              |  |  |  |

| SysAD(63:0)  I/O  System address/data bus A 64-bit address and data bus for communication between the processor and an external agent.                           |                                                                                             |                                                                                                                                                              |  |  |  |

| SysADC(7:0)                                                                                                                                                      | I/O                                                                                         | System address/data check bus An 8-bit bus containing parity check bits for the SysAD bus during data bus cycles.                                            |  |  |  |

| SysCmd(8:0)  I/O  System command/data identifier bus A 9-bit bus for command and data identifier transmission between the processor and an external agent        |                                                                                             | System command/data identifier bus A 9-bit bus for command and data identifier transmission between the processor and an external agent.                     |  |  |  |

| SysCmdP                                                                                                                                                          | I/O                                                                                         | Reserved system command/data identifier bus parity for the R4700 unused on input and zero on output.                                                         |  |  |  |

| Clock/Control                                                                                                                                                    | Interface                                                                                   |                                                                                                                                                              |  |  |  |

#### Clock/Control Interface

| MasterClock | I | Master clock Master clock input at one half the processor operating frequency.                                                                                         |

|-------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MasterOut   | 0 | Master clock out Master clock output aligned with MasterClock.                                                                                                         |

| RClock(1:0) | 0 | Receive clocks Two identical receive clocks at the system interface frequency.                                                                                         |

| TClock(1:0) | 0 | Transmit clocks Two identical transmit clocks at the system interface frequency.                                                                                       |

| IOOut       | 0 | Reserved for future output Always HIGH.                                                                                                                                |

| IOIn        | I | Reserved for future input Should be driven HIGH.                                                                                                                       |

| SyncOut     | 0 | Synchronization clock out  Must be connected to SyncIn through an interconnect that models the interconnect between MasterOut, TClock, RClock, and the external agent. |

| SyncIn      | I | Synchronization clock in Synchronization clock input. See SyncOut.                                                                                                     |

| Fault*      | 0 | Fault Always HIGH.                                                                                                                                                     |

| Pin Name | Туре | Description                                                     |  |

|----------|------|-----------------------------------------------------------------|--|

| VccP     | I    | Quiet Vcc for PLL Quiet Vcc for the internal phase locked loop. |  |

| VssP     | I    | Quiet Vss for PLL Quiet Vss for the internal phase locked loop. |  |

#### Interrupt Interface

| Int*(5:0) | I | Interrupt Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt register. |

|-----------|---|----------------------------------------------------------------------------------------------------|

| NMI*      | I | Non-maskable interrupt Non-maskable interrupt, ORed with bit 6 of the interrupt register.          |

#### Initialization Interface

| Vccok     | l | Vcc is OK When asserted, this signal indicates to the R4700 that the power supply has been above the Vcc minimum for more than 100 milliseconds and will remain stable. The assertion of Vccok initiates the reading of the boot-time-mode-control serial stream. |

|-----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |   | This signal must be asserted for a power on reset or a cold reset. The clocks SClock, TClock, and RClock begin to cycle and are synchronized with the de-assertion edge of ColdReset. ColdReset must be de-                                                       |

| Reset*    | I | Reset This signal must be asserted for any reset sequence. It may be asserted synchronously or asynchronously for a cold reset, or synchronously to initiate a warm reset. Reset must be de-asserted synchronously with MasterOut.                                |

| ModeClock | 0 | Boot-mode clock Serial boot-mode data clock output at the system clock frequency divided by two hundred fifty-six.                                                                                                                                                |

| Modeln    | ı | Boot-mode data in<br>Serial boot-mode data input.                                                                                                                                                                                                                 |

## **Absolute Maximum Ratings**

**Note:** Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Symbol            | Rating                               | RV4700<br>3.3V±5%         | R4700<br>5.0V±5%          | Unit |

|-------------------|--------------------------------------|---------------------------|---------------------------|------|

|                   |                                      | Commercial                | Commercial                |      |

| V <sub>TERM</sub> | Terminal Voltage with respect to GND | -0.5 <sup>1</sup> to +4.6 | -0.5 <sup>1</sup> to +7.0 | V    |

| T <sub>C</sub>    | Operating Temperature (case)         | 0 to +85                  | 0 to +85                  | °C   |

| T <sub>BIAS</sub> | Case Temperature Under Bias          | -55 to +125               | -55 to +125               | °C   |

| T <sub>STG</sub>  | Storage Temperature                  | -55 to +125               | -55 to +125               | °C   |

| I <sub>IN</sub>   | DC Input Current                     | 20 <sup>2</sup>           | 20 <sup>2</sup>           | mA   |

| I <sub>OUT</sub>  | DC Output Current                    | 50                        | 50 <sup>3</sup>           | mA   |

$<sup>^{1.}</sup>$  V<sub>IN</sub> minimum = -2.0V for pulse width less than 15ns. V<sub>IN</sub> should not exceed V<sub>CC</sub> +0.5V.

$<sup>^{2.}</sup>$  When  $V_{IN}$  < 0.0V or  $V_{IN}$  > $V_{CC}$ .

$<sup>^{3\</sup>cdot}$  Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

## **Recommended Operation Temperature and Supply Voltage**

| Grade      | Temperature GND     |    | RV4700          | R4700    |

|------------|---------------------|----|-----------------|----------|

| Orace      | remperature         |    | V <sub>CC</sub> | $v_{cc}$ |

| Commercial | 0°C to +85°C (Case) | 0V | 3.3V±5%         | 5.0V±5%  |

### **DC Electrical Characteristics—R4700**

$(V_{cc} = 5.0 \pm 5\%, T_{CASE} = 0^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter           | R4700                  | BO MHz                 | R4700 1                | 100MHz                 | R4700 1                | 133MHz                 | Conditions                |

|---------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|

|                     | Min                    | Мах                    | Min                    | Max                    | Min                    | Max                    |                           |

| V <sub>OL</sub>     | _                      | 0.1V                   | _                      | 0.1V                   | _                      | 0.1V                   | I <sub>OUT</sub>  = 20uA  |

| V <sub>OH</sub>     | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      |                           |

| V <sub>OL</sub>     |                        | 0.4V                   | _                      | 0.4V                   | _                      | 0.4V                   | I <sub>OUT</sub>  = 4mA   |

| V <sub>OH</sub>     | 3.5V                   | _                      | 3.5V                   | _                      | 3.5V                   | _                      |                           |

| V <sub>IL</sub>     | -0.5V                  | 0.8V                   | -0.5V                  | 0.8V                   | -0.5V                  | 0.8V                   | _                         |

| V <sub>IH</sub>     | 2.0V                   | V <sub>CC</sub> + 0.5V | 2.0V                   | V <sub>CC</sub> + 0.5V | 2.0V                   | V <sub>CC</sub> + 0.5V | _                         |

| I <sub>IN</sub>     |                        | ±10uA                  | _                      | ±10uA                  | _                      | ±10uA                  | $0 \le V_{IN} \le V_{CC}$ |

| C <sub>IN</sub>     |                        | 15pF                   | _                      | 15pF                   | _                      | 15pF                   | _                         |

| C <sub>OUT</sub>    | _                      | 15pF                   | _                      | 15pF                   | _                      | 15pF                   | _                         |

| I/O <sub>LEAK</sub> | _                      | 20uA                   | _                      | 20uA                   | _                      | 20uA                   | Input/Output<br>Leakage   |

# **Power Consumption—R4700**

|                 |                   | R4700              | 80 MHz              | R4700                | 100MHz              | R4700                | 133MHz              |                                                                                         |

|-----------------|-------------------|--------------------|---------------------|----------------------|---------------------|----------------------|---------------------|-----------------------------------------------------------------------------------------|

| Par             | ameter            | Typical            | Max                 | Typical <sup>1</sup> | Мах                 | Typical <sup>1</sup> | Max                 | - Conditions                                                                            |

|                 | ystem<br>ndition: | 80/20              | MHz                 | 100/2                | 5MHz                | 133/3                | ЗМН                 | _                                                                                       |

|                 |                   | _                  | 150mA <sup>2</sup>  | _                    | 175mA <sup>2</sup>  | _                    | 225mA <sup>2</sup>  | $C_L = 0pF^3$                                                                           |

|                 | standby           | _                  | 215mA <sup>2</sup>  | _                    | 250mA <sup>2</sup>  | _                    | 325mA <sup>2</sup>  | C <sub>L</sub> = 50pF                                                                   |

|                 |                   | 750mA <sup>2</sup> | 850 mA <sup>2</sup> | 875mA <sup>2</sup>   | 1000mA <sup>2</sup> | 1175mA <sup>2</sup>  | 1300mA <sup>2</sup> | C <sub>L</sub> = 0pF<br>No SysAd activity <sup>3</sup>                                  |

| I <sub>CC</sub> | active            | 850mA <sup>2</sup> | 1050mA <sup>2</sup> | 975mA <sup>2</sup>   | 1200mA <sup>2</sup> | 1275mA <sup>2</sup>  | 1500mA <sup>2</sup> | $C_L = 50 pF$<br>R4x00 compatible writes<br>$T_C = 25^{\circ}C$                         |

| 1-              |                   | 850mA <sup>2</sup> | 1250mA <sup>a</sup> | 975mA <sup>2</sup>   | 1400mA <sup>4</sup> | 1275mA <sup>2</sup>  | 1675mA <sup>4</sup> | C <sub>L</sub> = 50pF<br>Pipelined writes or write<br>re-issue<br>T <sub>C</sub> = 25°C |

<sup>&</sup>lt;sup>1.</sup> Typical integer instruction mix and cache miss rates.

<sup>&</sup>lt;sup>2.</sup> These are not tested. They are the result of engineering analysis and are provided for reference only.

<sup>&</sup>lt;sup>3.</sup> Guaranteed by design.

<sup>&</sup>lt;sup>4.</sup> These are the specifications IDT tests to insure compliance.

### **AC Electrical Characteristics—R4700**

(V<sub>CC</sub>=5.0V  $\pm$  5%; T<sub>CASE</sub> = 0°C to +85°C)

#### **Clock Parameters—R4700**

| Parameter                                              | Symbol                              | Test<br>Conditions           | _   | R4700<br>BOMHz       | _   | R4700<br>DOMHz       | R4700<br>133MHz |                      | Units |

|--------------------------------------------------------|-------------------------------------|------------------------------|-----|----------------------|-----|----------------------|-----------------|----------------------|-------|

|                                                        |                                     | Conditions                   | Min | Max                  | Min | Мах                  | Min             | Max                  |       |

| MasterClock HIGH                                       | t <sub>MCHIGH</sub>                 | $Transition \leq t_{MCRise}$ | 4   | _                    | 4   | _                    | 3               | _                    | ns    |

| MasterClock LOW                                        | t <sub>MCLOW</sub>                  | $Transition \leq t_{MCFall}$ | 4   | _                    | 4   | _                    | 3               | _                    | ns    |

| MasterClock Frequency <sup>1</sup>                     | _                                   | _                            | 25  | 40                   | 25  | 50                   | 25              | 67                   | MHz   |

| MasterClock Period                                     | t <sub>MCP</sub>                    | _                            | 25  | 40                   | 20  | 40                   | 15              | 40                   | ns    |

| Clock Jitter for MasterClock                           | t <sub>JitterIn</sub> <sup>2</sup>  | _                            | _   | ±250                 | -   | ±250                 | _               | ±250                 | ps    |

| Clock Jitter for<br>MasterOut, SyncOut, TClock, RClock | t <sub>JitterOut</sub> <sup>2</sup> | _                            | _   | ±500                 | -   | ±500                 | _               | ±500                 | ps    |

| MasterClock Rise Time                                  | t <sub>MCRise</sub> <sup>2</sup>    | _                            | _   | 5.5                  | _   | 5                    | _               | 4                    | ns    |

| MasterClock Fall Time                                  | t <sub>MCFall</sub> <sup>2</sup>    | _                            | _   | 5.5                  | _   | 5                    | _               | 4                    | ns    |

| ModeClock Period                                       | t <sub>ModeCKP</sub> <sup>2</sup>   | _                            | _   | 256*t <sub>MCP</sub> | _   | 256*t <sub>MCP</sub> | _               | 256*t <sub>MCP</sub> | ns    |

| JTAG Clock Period                                      | t <sub>JTAGCKP</sub> <sup>2</sup>   | _                            | _   | 4*t <sub>MCP</sub>   | _   | 4*t <sub>MCP</sub>   | _               | 4*t <sub>MCP</sub>   | ns    |

| SyncOut to SyncIn Delay                                | t <sub>Sync</sub> <sup>2,3</sup>    | _                            | _   | 2*t <sub>MCP</sub>   | _   | 2*t <sub>MCP</sub>   | _               | 2*t <sub>MCP</sub>   | ns    |

<sup>1.</sup> Operation of the R4700 is only guaranteed with the Phase Lock Loop enabled.

### **System Interface Parameters—R4700**

**Note:** Timings are measured from 1.5V of the clock to 1.5V of the signal.

| Parameter        | Symbol          | Test Conditions                     |     | 700<br>MHz |     |     | R4700 R4700<br>100MHz 133MHz |     | Units |

|------------------|-----------------|-------------------------------------|-----|------------|-----|-----|------------------------------|-----|-------|

|                  |                 |                                     | Min | Max        | Min | Max | Min                          | Max |       |

| Data Output      | t <sub>DO</sub> | mode <sub>1413</sub> = 10 (fastest) | 01  | 9          | 01  | 9   | 01                           | 9   | ns    |

|                  |                 | mode <sub>1413</sub> = 01 (slowest) | 01  | 15         | 01  | 15  | 0 <sup>1</sup>               | 12  | ns    |

| Input Data Setup | t <sub>DS</sub> | t <sub>rise</sub> = 5ns             | 3.5 | _          | 3.5 | _   | 3.5                          | _   | ns    |

| Input Data Hold  | t <sub>DH</sub> | t <sub>fall</sub> = 5ns             | 1.5 | _          | 1.5 | _   | 1.5                          | _   | ns    |

<sup>1.</sup> Guaranteed by design.

#### **Boot-Time Interface Parameters—R4700**

| Parameter       | Symbol          | Test<br>Conditions | R4700<br>80MHz |     |     | R4700<br>100MHz |     | 700<br>MHz | Units             |

|-----------------|-----------------|--------------------|----------------|-----|-----|-----------------|-----|------------|-------------------|

|                 |                 | Conditions         | Min            | Max | Min | Max             | Min | Max        |                   |

| Mode Data Setup | t <sub>DS</sub> | _                  | 3              | _   | 3   | _               | 3   | _          | Master ClockCycle |

| Mode Data Hold  | t <sub>DH</sub> | _                  | 0              | _   | 0   | _               | 0   | _          | Master ClockCycle |

<sup>&</sup>lt;sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Rise and fall times of the SyncIn signal must match those of MasterClock to avoid the introduction of additional clock skew.

### **Capacitive Load Deration—R4700**

| Parameter   | Symbol          | R4700 | 80MHz | R4700 | R4700 100MHz R4700 133MHz |     | R4700 133MHz |         |

|-------------|-----------------|-------|-------|-------|---------------------------|-----|--------------|---------|

| raiametei   | - Cyllibol      | Min   | Max   | Min   | Max                       | Min | Max          | Units   |

| Load Derate | C <sub>LD</sub> | _     | 2     | _     | 2                         | _   | 2            | ns/25pF |

## **AC Electrical Characteristics — RV4700**

$(V_{CC}$ =3.3V  $\pm$  5%;  $T_{CASE}$  = 0°C to +85°C)

#### **Clock Parameters**

| Parameter                                              | Symbol                              | Test<br>Conditions                |     | /4700<br>00MHz       | RV4700<br>133MHz |                      | R\<br>15 | Units                |     |

|--------------------------------------------------------|-------------------------------------|-----------------------------------|-----|----------------------|------------------|----------------------|----------|----------------------|-----|

|                                                        |                                     | Conditions                        | Min | Max                  | Min              | Max                  | Min      | Max                  |     |

| MasterClock HIGH                                       | t <sub>MCHIGH</sub>                 | $Transition \leq t_{MCRise/Fall}$ | 4   | _                    | 3                | _                    | 3        | _                    | ns  |

| MasterClock LOW                                        | t <sub>MCLOW</sub>                  | $Transition \leq t_{MCRise/Fall}$ | 4   | _                    | 3                | _                    | 3        | _                    | ns  |

| MasterClock Frequency <sup>1</sup>                     | _                                   | _                                 | 25  | 50                   | 25               | 67                   | 25       | 75                   | MHz |

| MasterClock Period                                     | t <sub>MCP</sub>                    | _                                 | 20  | 40                   | 15               | 40                   | 13.3     | 40                   | ns  |

| Clock Jitter for MasterClock                           | t <sub>JitterIn</sub> <sup>2</sup>  | _                                 | _   | ±250                 | _                | ±250                 | _        | ±250                 | ps  |

| Clock Jitter for MasterOut,<br>SyncOut, TClock, RClock | t <sub>JitterOut</sub> <sup>2</sup> | _                                 | _   | ±500                 | _                | ±500                 | _        | ±500                 | ps  |

| MasterClock Rise Time                                  | t <sub>MCRise</sub> <sup>2</sup>    | _                                 | _   | 5                    | _                | 4                    | _        | 3.5                  | ns  |

| MasterClock Fall Time                                  | t <sub>MCFall</sub> <sup>2</sup>    | _                                 | _   | 5                    | _                | 4                    | _        | 3.5                  | ns  |

| ModeClock Period                                       | t <sub>ModeCKP</sub>                | _                                 | _   | 256*t <sub>MCP</sub> | _                | 256*t <sub>MCP</sub> | _        | 256*t <sub>MCP</sub> | ns  |

| SyncOut to SyncIn Delay                                | t <sub>Sync</sub> <sup>2, 3</sup>   | _                                 | _   | 2*t <sub>MCP</sub>   | _                | 2*t <sub>MCP</sub>   | _        | 2*t <sub>MCP</sub>   | ns  |

<sup>1.</sup> Typical integer instruction mix and cache miss rates.

<sup>3.</sup> Rise and fall times of the SyncIn signal must match those of MasterClock to avoid the introduction of additional clock skew.

| Parameter                                              | Symbol                            | Test Conditions                   |      | RV4700<br>175MHz <sup>1</sup> |     | RV4700<br>200MHz <sup>1</sup> |     |  |

|--------------------------------------------------------|-----------------------------------|-----------------------------------|------|-------------------------------|-----|-------------------------------|-----|--|

|                                                        |                                   |                                   | Min  | Max                           | Min | Max                           |     |  |

| MasterClock HIGH                                       | t <sub>MCHIGH</sub>               | $Transition \leq t_{MCRise/Fall}$ | 3    | _                             | 3   | _                             | ns  |  |

| MasterClock LOW                                        | t <sub>MCLOW</sub>                | $Transition \leq t_{MCRise/Fall}$ | 3    | _                             | 3   | _                             | ns  |  |

| MasterClock Frequency <sup>2</sup>                     | _                                 | _                                 | 25   | 87.5                          | 25  | 100                           | MHz |  |

| MasterClock Period                                     | t <sub>MCP</sub>                  | _                                 | 11.4 | 40                            | 10  | 40                            | ns  |  |

| Clock Jitter for MasterClock                           | t <sub>JitterIn</sub> 3           | _                                 | 1-   | ±250                          | _   | ±250                          | ps  |  |

| Clock Jitter for MasterOut,<br>SyncOut, TClock, RClock | t <sub>JitterOu</sub> 3           | _                                 | _    | ±500                          | _   | ±500                          | ps  |  |

| MasterClock Rise Time                                  | t <sub>MCRise</sub> <sup>3</sup>  | _                                 | _    | 3.5                           | _   | 3.5                           | ns  |  |

| MasterClock Fall Time                                  | t <sub>MCFall</sub> <sup>3</sup>  | _                                 | _    | 3.5                           | _   | 3.5                           | ns  |  |

| ModeClock Period                                       | t <sub>ModeCKP</sub>              | _                                 | -    | 256*t <sub>MCP</sub>          | _   | 256*t <sub>MCP</sub>          | ns  |  |

| SyncOut to SyncIn Delay                                | t <sub>Sync</sub> <sup>3, 4</sup> | _                                 | -    | 2*t <sub>MCP</sub>            | -   | 2*t <sub>MCP</sub>            | _   |  |

<sup>1.</sup> Operation of the R4700 is only guaranteed with the Phase Lock Loop enabled.

<sup>2.</sup> Guaranteed by Design.

<sup>&</sup>lt;sup>2.</sup> Typical integer instruction mix and cache miss rates.

<sup>3.</sup> Guaranteed by design.

<sup>4.</sup> Rise and fall times of the Syncln signal must match those of MasterClock to avoid the introduction of additional clock skew.

## **DC Electrical Characteristics—RV4700**

$(V_{CC} = 3.3\pm5\%, T_{CASE} = 0^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter           | RV470                  | 0 100MHz               | RV470                  | 0 133MHz               | Conditions                |

|---------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|

| Parameter           | Min                    | Max                    | Min                    | Max                    | Conditions                |

| V <sub>OL</sub>     | _                      | 0.1V                   | _                      | 0.1V                   | I <sub>OUT</sub>  = 20uA  |

| V <sub>OH</sub>     | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      |                           |

| V <sub>OL</sub>     | _                      | 0.4V                   | _                      | 0.4V                   | I <sub>OUT</sub>  = 4mA   |

| V <sub>OH</sub>     | 2.4V                   | _                      | 2.4V                   | _                      |                           |

| V <sub>IL</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | _                         |

| V <sub>IH</sub>     | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | _                         |

| I <sub>IN</sub>     | _                      | ±10uA                  | _                      | ±10uA                  | $0 \le V_{IN} \le V_{CC}$ |

| C <sub>IN</sub>     | _                      | 15pF                   | _                      | 15pF                   | _                         |

| C <sub>OUT</sub>    | _                      | 15pF                   | _                      | 15pF                   | _                         |

| I/O <sub>LEAK</sub> | _                      | 20uA                   | _                      | 20uA                   | Input/Output Leakage      |

| Parameter           | RV470                  | 0 150MHz               | RV470                  | 0 175MHz               | RV470                  | 0 200MHz               | Conditions                |

|---------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|

| Parameter           | Min                    | Max                    | Min                    | Max                    | Min                    | Max                    | Conditions                |

| V <sub>OL</sub>     | _                      | 0.1V                   | _                      | 0.1V                   | _                      | 0.1V                   | I <sub>OUT</sub>  = 20uA  |

| V <sub>OH</sub>     | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      | V <sub>CC</sub> - 0.1V | _                      |                           |

| V <sub>OL</sub>     | _                      | 0.4V                   | _                      | 0.4V                   | _                      | 0.4V                   | I <sub>OUT</sub>  = 4mA   |

| V <sub>OH</sub>     | 2.4V                   | _                      | 2.4V                   | _                      | 2.4V                   | _                      |                           |

| V <sub>IL</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | -0.5V                  | 0.2V <sub>CC</sub>     | _                         |

| V <sub>IH</sub>     | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | 0.7V <sub>CC</sub>     | V <sub>CC</sub> + 0.5V | _                         |

| I <sub>IN</sub>     | _                      | ±10uA                  | _                      | ±10uA                  | _                      | ±10uA                  | $0 \le V_{IN} \le V_{CC}$ |

| C <sub>IN</sub>     | _                      | 15pF                   | _                      | 15pF                   | _                      | 15pF                   | _                         |

| C <sub>OUT</sub>    | _                      | 15pF                   | _                      | 15pF                   | -                      | 15pF                   | _                         |

| I/O <sub>LEAK</sub> | _                      | 20uA                   | _                      | 20uA                   | _                      | 20uA                   | Input/Output Leakage      |

## **System Interface Parameters—RV4700**

**Note:** Operation of the R4700 is only guaranteed with the Phase Lock Loop enabled.

| Parameter                | Symbol                | Test Conditions                     | RV4700<br>100MHz |     | RV4700<br>133MHz |     | 100MHz 133MHz 150MHz |     |    |  | Units |

|--------------------------|-----------------------|-------------------------------------|------------------|-----|------------------|-----|----------------------|-----|----|--|-------|

|                          |                       |                                     | Min              | Max | Min              | Max | Min                  | Max |    |  |       |

| Data Output <sup>1</sup> | t <sub>DM</sub> = Min | mode <sub>1413</sub> = 10 (fastest) | 0                | 9   | 0                | 9   | 0                    | 8   | ns |  |       |

|                          | t <sub>DO</sub> = Max | mode <sub>1413</sub> = 01 (slowest) | 0                | 15  | 0                | 12  | 0                    | 12  | ns |  |       |

| Input Data Setup         | t <sub>DS</sub>       | t <sub>rise</sub> = 3ns             | 3.5              | _   | 3.5              | _   | 3.5                  | _   | ns |  |       |

| Input Data Hold          | t <sub>DH</sub>       | t <sub>fall</sub> = 3ns             | 1.5              | _   | 1.5              | _   | 1.5                  | _   | ns |  |       |

<sup>&</sup>lt;sup>1.</sup> Timings are measured from 1.5V of the clock to 1.5V of the signal.

| Parameter                | Symbol                | Test Conditions                     |         | RV4700<br>175MHz |     | RV4700<br>200MHz |    |  |

|--------------------------|-----------------------|-------------------------------------|---------|------------------|-----|------------------|----|--|

|                          |                       |                                     | Min Max | Max              | Min | Max              |    |  |

| Data Output <sup>1</sup> | t <sub>DM</sub> = Min | mode <sub>1413</sub> = 10 (fastest) | 0       | 8                | 0   | 8                | ns |  |

|                          | t <sub>DO</sub> = Max | mode <sub>1413</sub> = 01 (slowest) | 0       | 12               | 0   | 12               | ns |  |

| Input ata Setup          | t <sub>DS</sub>       | t <sub>rise</sub> = 3ns             | 3.5     | _                | 3.5 | _                | ns |  |

| Input Data Hold          | t <sub>DH</sub>       | t <sub>fall</sub> = 3ns             | 1.5     | _                | 1.5 | _                | ns |  |

<sup>&</sup>lt;sup>1.</sup> Capacitive load for all output timings is 50pF.

#### **Boot-Time Interface Parameters—RV4700**

| Parameter       | Symbol          | Test       | RV4700 | 100MHz | RV4700 | 133MHz | RV4700 | 150MHz | Units              |

|-----------------|-----------------|------------|--------|--------|--------|--------|--------|--------|--------------------|

| raiametei       | Cymbol          | Conditions | Min    | Мах    | Min    | Мах    | Min    | Мах    |                    |

| Mode Data Setup | t <sub>DS</sub> | _          | 3      | _      | 3      | _      | 3      | _      | Master Clock Cycle |

| Mode Data Hold  | t <sub>DH</sub> | _          | 0      | _      | 0      | _      | 0      | _      | Master Clock Cycle |

| Parameter       | Symbol          | Test       | RV4700 175MHz |     | RV4700 200MHz |     | Units              |

|-----------------|-----------------|------------|---------------|-----|---------------|-----|--------------------|

| Parameter       |                 | Conditions | Min           | Мах | Min           | Мах | Onits              |

| Mode Data Setup | t <sub>DS</sub> | _          | 3             |     | 3             | _   | Master Clock Cycle |

| Mode Data Hold  | t <sub>DH</sub> | _          | 0             | _   | 0             | _   | Master Clock Cycle |

## **Power Consumption—RV4700**

| Do.              | Parameter | RV4700 100MHz        |                     | RV4700 133MHz        |                     | RV4700 150MHz        |                     | Conditions                                                    |  |

|------------------|-----------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|---------------------------------------------------------------|--|

| Parameter        |           | Typical <sup>1</sup> | Max                 | Typical <sup>1</sup> | Max                 | Typical <sup>1</sup> | Max                 | Conditions                                                    |  |

| System 100/25MHz |           | 133/33MHz            |                     | 150/38MHz            |                     | _                    |                     |                                                               |  |

|                  | standby   | _                    | 125mA <sup>2</sup>  | _                    | 175mA <sup>2</sup>  | _                    | 200mA <sup>2</sup>  | $C_L = 0 pF^3$                                                |  |

|                  |           | _                    | 175mA <sup>2</sup>  | _                    | 225mA <sup>2</sup>  | _                    | 250mA <sup>2</sup>  | C <sub>L</sub> = 50pF                                         |  |

| I <sub>CC</sub>  | active    | 575mA <sup>2</sup>   | 875mA <sup>2</sup>  | 775mA <sup>2</sup>   | 1150mA <sup>2</sup> | 875mA <sup>2</sup>   | 1300mA <sup>2</sup> | C <sub>L</sub> = 0pF, No SysAd activity <sup>3</sup>          |  |

|                  |           | 650mA <sup>2</sup>   | 1100mA <sup>2</sup> | 850mA <sup>2</sup>   | 1375mA <sup>2</sup> | 950mA <sup>2</sup>   | 1550mA <sup>2</sup> | $C_L = 50 pF R4x00$ compatible writes, $T_C = 25 C^3$         |  |

|                  |           | 650mA <sup>2</sup>   | 1275mA <sup>4</sup> | 850mA <sup>2</sup>   | 1525mA <sup>4</sup> | 950mA <sup>2</sup>   | 1725mA <sup>2</sup> | $C_L$ = 50pF Pipelined writes or write re-issue, $T_C$ = 25°C |  |

<sup>1.</sup> Typical integer instruction mix and cache miss rates.

<sup>&</sup>lt;sup>4.</sup> These are the specifications IDT tests to insure compliance.

| Parameter        |         | RV4700 175MHz            |                     | RV4700 200MHz            |                     | Conditions                                                                 |  |

|------------------|---------|--------------------------|---------------------|--------------------------|---------------------|----------------------------------------------------------------------------|--|

|                  |         | Typical <sup>1</sup> Max |                     | Typical <sup>1</sup> Max |                     |                                                                            |  |

| System Condition |         | 175/4                    | 4MHz                | 200/50MHz                |                     | -                                                                          |  |

|                  | standby | _                        | 200mA <sup>2</sup>  | _                        | 200mA <sup>2</sup>  | C <sub>L</sub> = 0pF <sup>3</sup>                                          |  |

|                  |         | _                        | 250mA <sup>2</sup>  | _                        | 250mA <sup>2</sup>  | C <sub>L</sub> = 50pF                                                      |  |

| $I_{CC}$         | active  | 1025mA <sup>2</sup>      | 1500mA <sup>2</sup> | 1025mA <sup>2</sup>      | 1500mA <sup>2</sup> | C <sub>L</sub> = 0pF, No SysAd activity <sup>3</sup>                       |  |

|                  |         | 1200mA <sup>2</sup>      | 1800mA <sup>2</sup> | 1200mA <sup>2</sup>      | 1800mA <sup>2</sup> | $C_L$ = 50pF R4x00 compatible writes, $T_C$ = 25 $^{\circ}$ C <sup>3</sup> |  |

|                  |         | 1200mA <sup>2</sup>      | 2000mA <sup>4</sup> | 1200mA <sup>2</sup>      | 2000mA <sup>4</sup> | $C_L$ = 50pF Pipelined writes or write re-issue, $T_C$ = 25°C              |  |

<sup>&</sup>lt;sup>2.</sup> These are not tested. They are the result of engineering analysis and are provided for reference only.

<sup>&</sup>lt;sup>3.</sup> Guaranteed by design.

<sup>&</sup>lt;sup>2.</sup> These are not tested. They are the result of engineering analysis and are provided for reference only.

<sup>&</sup>lt;sup>3.</sup> Guaranteed by design.

<sup>&</sup>lt;sup>4.</sup> These are the specifications IDT tests to insure compliance.

# Physical Specifications — 208-pin QFP

#### **Physical Specifications - page 2**

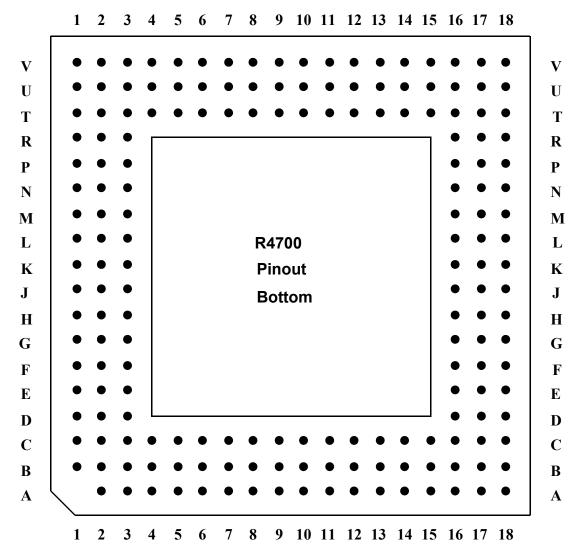

## **RC4700 PGA Package Pin-Out**

**Note:** N.C. pins should be left floating for maximum flexibility and compatibility with future designs.

| Function         | Pin | Function | Pin | Function | Pin |  |

|------------------|-----|----------|-----|----------|-----|--|

| ColdReset*       | T14 | SysAD36  | C3  | VCC      | B18 |  |

| ExtRqst*         | U2  | SysAD37  | B3  | VCC      | C1  |  |

| Fault*           | B16 | SysAD38  | C6  | VCC      | D18 |  |

| Reserved O (NC)  | U10 | SysAD39  | C7  | VCC      | F1  |  |

| Reserved I (Vcc) | T9  | SysAD40  | C10 | VCC      | G18 |  |

| IOIn             | T13 | SysAD41  | C11 | VCC      | H1  |  |

| IOOut            | U12 | SysAD42  | B13 | VCC      | J18 |  |

| Int0             | N2  | SysAD43  | A15 | VCC      | K1  |  |

| Int1             | L3  | SysAD44  | C15 | VCC      | L18 |  |

| Int2             | K3  | SysAD45  | B17 | VCC      | M1  |  |

| Int3             | J3  | SysAD46  | E17 | VCC      | N18 |  |

| Int4             | H3  | SysAD47  | F17 | VCC      | R1  |  |

| Int5             | F2  | SysAD48  | L2  | VCC      | T18 |  |

| MasterClock      | J17 | SysAD49  | M3  | VCC      | U1  |  |

| MasterOut        | P17 | SysAD50  | N3  | VCC      | V3  |  |

| ModeClock        | B4  | SysAD51  | R2  | VCC      | V6  |  |

| Modeln           | U4  | SysAD52  | T3  | VCC      | V8  |  |

| NMI              | U7  | SysAD53  | U3  | VCC      | V10 |  |

| RClock0          | T17 | SysAD54  | T6  | VCC      | V12 |  |

| RClock1          | R16 | SysAD55  | T7  | VCC      | V14 |  |

| RdRdy*           | T5  | SysAD56  | T10 | VCC      | V17 |  |

| Release          | V5  | SysAD57  | T11 | VSS      | A3  |  |

| Reset*           | U16 | SysAD58  | U13 | VSS      | A6  |  |

| SyncIn           | J16 | SysAD59  | V15 | VSS      | A8  |  |

| SyncOut          | P16 | SysAD60  | T15 | VSS      | A10 |  |

| SysAD0           | J2  | SysAD61  | U17 | VSS      | A12 |  |

| SysAD1           | G2  | SysAD62  | N16 | VSS      | A14 |  |

| SysAD2           | E1  | SysAD63  | N17 | VSS      | A17 |  |

| SysAD3           | E3  | SysADC0  | C8  | VSS      | A18 |  |

| SysAD4           | C2  | SysADC1  | G17 | VSS      | B1  |  |

| SysAD5           | C4  | SysADC2  | T8  | VSS      | C18 |  |

| SysAD6           | B5  | SysADC3  | L16 | VSS      | D1  |  |

| SysAD7           | B6  | SysADC4  | B8  | VSS      | F18 |  |

| SysAD8           | B9  | SysADC5  | H16 | VSS      | G1  |  |

| SysAD9           | B11 | SysADC6  | U8  | VSS      | H18 |  |

| SysAD10          | C12 | SysADC7  | L17 | VSS      | J1  |  |

| SysAD11          | B14 | SysCmd0  | E2  | VSS      | K18 |  |

| SysAD12          | B15 | SysCmd1  | D3  | VSS      | L1  |  |

| SysAD13          | C16 | SysCmd2  | B2  | VSS      | M18 |  |

| SysAD14          | D17 | SysCmd3  | A5  | VSS      | N1  |  |

| SysAD15          | E18 | SysCmd4  | B7  | VSS      | P18 |  |

| SysAD16          | K2  | SysCmd5  | C9  | VSS      | R18 |  |

| SysAD17          | M2  | SysCmd6  | B10 | VSS      | T1  |  |

| SysAD18          | P1  | SysCmd7  | B12 | VSS      | U18 |  |

| SysAD19          | P3  | SysCmd8  | C13 | VSS      | V1  |  |

| SysAD20          | T2  | SysCmdP  | C14 | VSS      | V2  |  |