# E·XFL

### NXP USA Inc. - SPC5604BACLL6 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | e200z0h                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 64MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 79                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 64K x 8                                                               |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 28x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bacll6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Block diagram

Table 3 summarizes the functions of all blocks present in the MPC5604B/C series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                                         | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-locked loop (FMPLL)                 | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock                      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                               | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)                           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Power control unit (MC_PCU)                                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)                           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

Table 3. MPC5604B/C series block summary

|          |        | -                                                      |                                                        |                                                  |                             |          | uo                     |                  | Pir              | num      | ber      |                         |

|----------|--------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|-----------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR    | Alternate function <sup>1</sup>                        | Function                                               | Peripheral                                       | I/O direction <sup>2</sup>  | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PA[2]    | PCR[2] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[2]<br>E0UC[2]<br><br>WKPU[3] <sup>4</sup>         | SIUL<br>eMIOS_0<br>—<br>WKPU                     | I/O<br>I/O<br><br>I         | S        | Tristate               | 3                | 3                | 5        | 9        | F2                      |

| PA[3]    | PCR[3] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[3]<br>E0UC[3]<br>—<br>EIRQ[0]                     | SIUL<br>eMIOS_0<br>—<br>SIUL                     | /O<br> /O<br><br>           | S        | Tristate               | 43               | 39               | 68       | 90       | K15                     |

| PA[4]    | PCR[4] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[4]<br>E0UC[4]<br><br>WKPU[9] <sup>4</sup>         | SIUL<br>eMIOS_0<br><br>WKPU                      | I/O<br>I/O<br><br>I         | S        | Tristate               | 20               | 20               | 29       | 43       | N6                      |

| PA[5]    | PCR[5] | AF0<br>AF1<br>AF2<br>AF3                               | GPIO[5]<br>E0UC[5]<br>—<br>—                           | SIUL<br>eMIOS_0<br>—                             | I/O<br>I/O<br>              | М        | Tristate               | 51               | 51               | 79       | 118      | C11                     |

| PA[6]    | PCR[6] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[6]<br>E0UC[6]<br>—<br>EIRQ[1]                     | SIUL<br>eMIOS_0<br>—<br>SIUL                     | /O<br> /O<br><br>           | S        | Tristate               | 52               | 52               | 80       | 119      | D11                     |

| PA[7]    | PCR[7] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[7]<br>E0UC[7]<br>LIN3TX<br>—<br>EIRQ[2]           | SIUL<br>eMIOS_0<br>LINFlex_3<br><br>SIUL         | /O<br> /O<br>0<br>          | S        | Tristate               | 44               | 44               | 71       | 104      | D16                     |

| PA[8]    | PCR[8] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>6</sup><br>— | GPIO[8]<br>E0UC[8]<br>—<br>EIRQ[3]<br>ABS[0]<br>LIN3RX | SIUL<br>eMIOS_0<br>—<br>SIUL<br>BAM<br>LINFlex_3 | /O<br> /O<br><br> <br> <br> | S        | Input, weak<br>pull-up | 45               | 45               | 72       | 105      | C16                     |

| PA[9]    | PCR[9] | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>6</sup>           | GPIO[9]<br>E0UC[9]<br>—<br>—<br>FAB                    | SIUL<br>eMIOS_0<br>—<br>BAM                      | /O<br> /O<br><br>           | S        | Pull-down              | 46               | 46               | 73       | 106      | C15                     |

Table 6. Functional port pin descriptions (continued)

|                     |         | -                               |                                                                           |                                          |                            |          | Ľ                   |                  | Pin              | num      | ber      |                         |

|---------------------|---------|---------------------------------|---------------------------------------------------------------------------|------------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin            | PCR     | Alternate function <sup>1</sup> | Function                                                                  | Peripheral                               | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PD[9]               | PCR[57] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[57]<br>—<br>—<br>—<br>GPI[13]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> -<br>                 | Ι        | Tristate            | _                | _                | 56       | 78       | N15                     |

| PD[10]              | PCR[58] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[58]<br>—<br>—<br>—<br>GPI[14]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> <br> <br>             | Ι        | Tristate            |                  | _                | 57       | 79       | N14                     |

| PD[11]              | PCR[59] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[59]<br>—<br>—<br>—<br>GPI[15]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> -<br>                 | Ι        | Tristate            | _                | _                | 58       | 80       | N16                     |

| PD[12] <sup>8</sup> | PCR[60] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[60]<br>CS5_0<br>E0UC[24]<br><br>ANS[4]                               | SIUL<br>DSPI_0<br>eMIOS_0<br>—<br>ADC    | I/O<br>O<br>I/O<br>I       | J        | Tristate            | _                | _                | 60       | 82       | M15                     |

| PD[13]              | PCR[61] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[61]<br>CS0_1<br>E0UC[25]<br><br>ANS[5]                               | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC    | I/O<br>I/O<br>I/O<br>I     | J        | Tristate            |                  |                  | 62       | 84       | M14                     |

| PD[14]              | PCR[62] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[62]<br>CS1_1<br>E0UC[26]<br>—<br>ANS[6]                              | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC    | I/O<br>O /O<br>I/O<br>-    | J        | Tristate            |                  |                  | 64       | 86       | L15                     |

| PD[15]              | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ANS[7]                              | SIUL<br>DSPI_1<br>eMIOS_0<br><br>ADC     | I/O<br>O<br>I/O<br>I       | J        | Tristate            | —                | —                | 66       | 88       | L14                     |

| PE[0]               | PCR[64] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[64]<br>E0UC[16]<br>—<br>CAN5RX <sup>11</sup><br>WKPU[6] <sup>4</sup> | SIUL<br>eMIOS_0<br><br>FlexCAN_5<br>WKPU | /0<br> /0<br> -<br>        | S        | Tristate            | _                | _                | 6        | 10       | F1                      |

### Table 6. Functional port pin descriptions (continued)

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid applying any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

# 3.10 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 8 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 8. Parameter classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.11 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

For a detailed description of the NVUSRO register, please refer to the device reference manual.

# 3.11.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 9 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

### Table 9. PAD3V5V field description

### 3.13 Recommended operating conditions

| Symbol                           |    | Parameter                                                                                     | Conditions                   | Va                   | lue                  | Unit |

|----------------------------------|----|-----------------------------------------------------------------------------------------------|------------------------------|----------------------|----------------------|------|

| Symbol                           |    | Falameter                                                                                     | Conditions                   | Min                  | Max                  | Unit |

| V <sub>SS</sub>                  | SR | Digital ground on VSS_HV pins                                                                 | —                            | 0                    | 0                    | V    |

| V <sub>DD</sub> <sup>1</sup>     | SR | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | —                            | 3.0                  | 3.6                  | V    |

| V <sub>SS_LV</sub> <sup>2</sup>  | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub> <sup>3</sup>  | SR | Voltage on VDD_BV pin (regulator supply) with                                                 | —                            | 3.0                  | 3.6                  | V    |

|                                  |    | respect to ground (V <sub>SS</sub> )                                                          | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>SS_ADC</sub>              | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )           | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub> <sup>4</sup> | SR | 5 <u> </u>                                                                                    | —                            | 3.0 <sup>5</sup>     | 3.6                  | V    |

|                                  |    | with respect to ground (V <sub>SS</sub> )                                                     | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>IN</sub>                  | SR | Voltage on any GPIO pin with respect to ground                                                | —                            | V <sub>SS</sub> -0.1 | _                    | V    |

|                                  |    | (V <sub>SS</sub> )                                                                            | Relative to $V_{\text{DD}}$  | _                    | V <sub>DD</sub> +0.1 |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during overload condition                                   | —                            | -5                   | 5                    | mA   |

| I <sub>INJSUM</sub>              | SR | Absolute sum of all injected input currents during overload condition                         |                              | -50                  | 50                   |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                 | —                            |                      | 0.25                 | V/µs |

| T <sub>A C-Grade Part</sub>      | SR | Ambient temperature under bias                                                                | $f_{CPU} \le 64 \text{ MHz}$ | -40                  | 85                   | °C   |

| T <sub>J C-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 110                  |      |

| T <sub>A V-Grade Part</sub>      | SR | Ambient temperature under bias                                                                |                              | -40                  | 105                  |      |

| T <sub>J V-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 130                  |      |

| T <sub>A M-Grade Part</sub>      | SR | Ambient temperature under bias                                                                |                              | -40                  | 125                  | 1    |

| T <sub>J M-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 150                  | 1    |

Table 13. Recommended operating conditions (3.3 V)

$^1$  100 nF capacitance needs to be provided between each  $V_{\text{DD}}/V_{\text{SS}}$  pair

$^2~$  330 nF capacitance needs to be provided between each V\_{DD\\_LV}\!/V\_{SS\\_LV} supply pair.

<sup>3</sup> 400 nF capacitance needs to be provided between  $V_{DD_BV}$  and the nearest  $V_{SS_LV}$  (higher value may be needed depending on external regulator characteristics).

$^4$  100 nF capacitance needs to be provided between V\_{DD\_ADC}/V\_{SS\_ADC} pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation

| Sum             | Symbol             | <u>ر</u> | Parameter                              |           | Conditions <sup>1</sup>                                                                |     | Unit |                    |   |

|-----------------|--------------------|----------|----------------------------------------|-----------|----------------------------------------------------------------------------------------|-----|------|--------------------|---|

| Syn             | Symbol C Parameter |          |                                        | Min       | Тур                                                                                    | Max | Unit |                    |   |

| V <sub>OL</sub> | СС                 |          | Output low level<br>FAST configuration | Push Pull | $I_{OL}$ = 14mA,<br>$V_{DD}$ = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended)               | _   |      | 0.1V <sub>DD</sub> | V |

|                 |                    | С        |                                        |           | I <sub>OL</sub> = 7mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>      | _   | _    | 0.1V <sub>DD</sub> |   |

|                 |                    | С        |                                        |           | I <sub>OL</sub> = 11mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | _   | _    | 0.5                |   |

Table 20. FAST configuration output buffer electrical characteristics (continued)

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

# 3.15.4 Output pin transition times

| e.              | mbol | c | Parameter                                |                         | Conditions <sup>1</sup>                    |     | Value | e   | Unit |

|-----------------|------|---|------------------------------------------|-------------------------|--------------------------------------------|-----|-------|-----|------|

| J               |      | C | Falameter                                |                         | Conditions                                 | Min | Тур   | Мах | Unit |

| t <sub>tr</sub> | CC   |   | Output transition time output            | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | —   | —     | 50  | ns   |

|                 |      | Т | pin <sup>2</sup><br>SLOW configuration   | C <sub>L</sub> = 50 pF  |                                            | _   | —     | 100 |      |

|                 |      | D | 0                                        | C <sub>L</sub> = 100 pF |                                            | _   |       | 125 |      |

|                 |      | D |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —   | —     | 50  |      |

|                 |      | Т |                                          | C <sub>L</sub> = 50 pF  |                                            | —   | —     | 100 |      |

|                 |      | D |                                          | C <sub>L</sub> = 100 pF |                                            | —   | —     | 125 |      |

| t <sub>tr</sub> | CC   | D | Output transition time output            | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 V \pm 10\%$ , PAD3V5V = 0    |     | —     | 10  | ns   |

|                 |      | Т | pin <sup>2</sup><br>MEDIUM configuration | C <sub>L</sub> = 50 pF  | -SIUL.PCRx.SRC = 1<br>-                    | —   | —     | 20  |      |

|                 |      | D | 0                                        | C <sub>L</sub> = 100 pF |                                            | —   | —     | 40  |      |

|                 |      | D |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _   |       | 12  |      |

|                 |      | Т |                                          | C <sub>L</sub> = 50 pF  | SIUL.PCRx.SRC = 1                          | _   | —     | 25  | 1    |

|                 |      | D |                                          | C <sub>L</sub> = 100 pF |                                            | —   | —     | 40  |      |

| t <sub>tr</sub> | CC   | D | Output transition time output            | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _   |       | 4   | ns   |

|                 |      |   | pin <sup>2</sup><br>FAST configuration   | C <sub>L</sub> = 50 pF  |                                            | _   |       | 6   |      |

|                 |      |   | Ŭ                                        | C <sub>L</sub> = 100 pF |                                            | —   | —     | 12  |      |

|                 |      |   |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —   | —     | 4   |      |

|                 |      |   |                                          | C <sub>L</sub> = 50 pF  | 1                                          | —   | —     | 7   |      |

|                 |      |   |                                          | C <sub>L</sub> = 100 pF |                                            | —   | —     | 12  |      |

Table 21. Output pin transition times

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

|             |             |                         |        |                      | 144/100 | ) LQFP  |         |         | 64 L    | QFP     |         |

|-------------|-------------|-------------------------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Sup         | ply seg     | ment                    | Pad    | Weigl                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 144<br>LQFP | 100<br>LQFP | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 2           | 2           | 2                       | PB[13] | 10%                  | —       | 12%     |         | 18%     |         | 21%     | _       |

|             |             |                         | PD[14] | 10%                  | _       | 12%     | _       |         |         |         |         |

|             |             | 2                       | PB[14] | 10%                  | —       | 12%     | _       | 18%     |         | 21%     |         |

|             |             |                         | PD[15] | 10%                  | —       | 11%     | —       | —       | _       | —       | —       |

|             |             | 2                       | PB[15] | 9%                   | —       | 11%     | —       | 18%     |         | 21%     | —       |

|             |             |                         | PA[3]  | 9%                   | —       | 11%     | _       | 18%     |         | 21%     | —       |

|             |             |                         | PG[13] | 9%                   | 13%     | 10%     | 11%     | —       | _       | —       | —       |

|             |             |                         | PG[12] | 9%                   | 12%     | 10%     | 11%     | _       | _       | —       | _       |

|             |             |                         | PH[0]  | 5%                   | 8%      | 6%      | 7%      | —       |         | —       | —       |

|             |             |                         | PH[1]  | 5%                   | 7%      | 6%      | 6%      | —       | _       | —       | —       |

|             |             |                         | PH[2]  | 5%                   | 6%      | 5%      | 6%      | _       | _       | —       | —       |

|             |             |                         | PH[3]  | 4%                   | 6%      | 5%      | 5%      | —       |         | —       | —       |

|             |             |                         | PG[1]  | 4%                   | —       | 4%      | —       | —       | _       | —       | —       |

|             |             |                         | PG[0]  | 3%                   | 4%      | 4%      | 4%      | —       |         | —       | —       |

| 3           |             |                         | PF[15] | 3%                   | —       | 4%      | —       | —       |         | —       | —       |

|             |             |                         | PF[14] | 4%                   | 5%      | 5%      | 5%      | —       | _       | —       | —       |

|             |             |                         | PE[13] | 4%                   | —       | 5%      | —       | —       |         | —       | —       |

|             | 3           | 2                       | PA[7]  | 5%                   | —       | 6%      | —       | 16%     |         | 19%     | —       |

|             |             |                         | PA[8]  | 5%                   | —       | 6%      | —       | 16%     | _       | 19%     | —       |

|             |             |                         | PA[9]  | 5%                   | —       | 6%      | —       | 15%     |         | 18%     | —       |

|             |             |                         | PA[10] | 6%                   | _       | 7%      | —       | 15%     | _       | 18%     | —       |

|             |             |                         | PA[11] | 6%                   | —       | 8%      | —       | 14%     | _       | 17%     | —       |

|             |             |                         | PE[12] | 7%                   | _       | 8%      | —       | —       | _       | _       | —       |

|             |             |                         | PG[14] | 7%                   | _       | 8%      | —       | _       | _       | —       | —       |

|             | _           |                         | PG[15] | 7%                   | 10%     | 8%      | 9%      |         | _       | —       | _       |

|             | _           |                         | PE[14] | 7%                   | —       | 8%      | —       | —       |         | —       | —       |

|             | _           |                         | PE[15] | 7%                   | 9%      | 8%      | 8%      | —       |         |         | —       |

|             | _           |                         | PG[10] | 6%                   |         | 8%      |         | _       | _       | —       | —       |

|             | _           |                         | PG[11] | 6%                   | 9%      | 7%      | 8%      | —       |         | —       | —       |

|             | 3           | 2                       | PC[3]  | 6%                   |         | 7%      |         | 7%      | _       | 9%      |         |

|             |             |                         | PC[2]  | 6%                   | 8%      | 7%      | 7%      | 6%      | 9%      | 8%      | 8%      |

# Table 24. I/O weight<sup>1</sup> (continued)

| Symbol                                                                                                                |    | с | Parameter                                                        | Conditions <sup>1</sup>                               |      | Value |                  | Unit  |

|-----------------------------------------------------------------------------------------------------------------------|----|---|------------------------------------------------------------------|-------------------------------------------------------|------|-------|------------------|-------|

| Symbol                                                                                                                |    | C | Falanielei                                                       | Conditions                                            | Min  | Тур   | Max              | Onic  |

| $\frac{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }$ | SR |   | Maximum slope on V <sub>DD</sub> during standby exit             |                                                       | —    |       | 15               | mV/µs |

| V <sub>MREG</sub> CC                                                                                                  |    | Т | Main regulator output voltage                                    | Before exiting from reset                             | _    | 1.32  |                  | V     |

|                                                                                                                       |    | Ρ |                                                                  | After trimming                                        | 1.16 | 1.28  | —                |       |

| I <sub>MREG</sub>                                                                                                     | SR | _ | Main regulator current provided to $V_{DD\_LV}$ domain           | _                                                     | -    |       | 150              | mA    |

| I <sub>MREGINT</sub>                                                                                                  | СС | D | Main regulator module current                                    | I <sub>MREG</sub> = 200 mA                            | _    |       | 2                | mA    |

|                                                                                                                       |    |   | consumption                                                      | I <sub>MREG</sub> = 0 mA                              | _    |       | 1                |       |

| V <sub>LPREG</sub>                                                                                                    | СС | Ρ | Low power regulator output voltage                               | After trimming                                        | 1.16 | 1.28  | _                | V     |

| I <sub>LPREG</sub>                                                                                                    | SR |   | Low power regulator current provided to $V_{DD_LV}$ domain       | _                                                     | —    |       | 15               | mA    |

| I <sub>LPREGINT</sub>                                                                                                 | СС | D | Low power regulator module current consumption                   | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | —    |       | 600              | μA    |

|                                                                                                                       |    |   |                                                                  | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _    | 5     |                  | -     |

| V <sub>ULPREG</sub>                                                                                                   | СС | Ρ | Ultra low power regulator output voltage                         | After trimming                                        | 1.16 | 1.28  | _                | V     |

| IULPREG                                                                                                               | SR | — | Ultra low power regulator current provided to $V_{DD_LV}$ domain | _                                                     | _    |       | 5                | mA    |

| IULPREGINT                                                                                                            | СС | D | Ultra low power regulator module current consumption             | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C | —    |       | 100              | μA    |

|                                                                                                                       |    |   |                                                                  | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C | -    | 2     | _                |       |

| I <sub>DD_BV</sub>                                                                                                    | СС | D | In-rush average current on $V_{DD\_BV}$ during power-up $^{5}$   |                                                       | -    |       | 300 <sup>6</sup> | mA    |

Table 26. Voltage regulator electrical characteristics (continued)

$^1$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified

- $^2$  This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

- $^3\,$  This value is acceptable to guarantee operation from 4.5 V to 5.5 V

- <sup>4</sup> External regulator and capacitance circuitry must be capable of providing I<sub>DD\_BV</sub> while maintaining supply V<sub>DD\_BV</sub> in operating range.

- <sup>5</sup> In-rush average current is seen only for short time (maximum 20 µs) during power-up and on standby exit. It is dependant on the sum of the C<sub>REGn</sub> capacitances.

- <sup>6</sup> The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

The  $|\Delta_{VDD(STDBY)}|$  and dVDD(STDBY)/dt system requirement can be used to define the component used for the V<sub>DD</sub> supply generation. The following two examples describe how to calculate capacitance size:

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

- Software recommendations: The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials: Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring.

### 3.20.2 Electromagnetic interference (EMI)

The product is monitored in terms of emission based on a typical application. This emission test conforms to the IEC 61967-1 standard, which specifies the general conditions for EMI measurements.

| Symbol             |    | С | С                     | с               | Parameter                    | Conditions |      | Unit |          |

|--------------------|----|---|-----------------------|-----------------|------------------------------|------------|------|------|----------|

| Cynis              |    | Ŭ | i urumeter            | Conditions      |                              |            |      |      |          |

|                    | SR |   | Scan range            | _               | 0.150                        | _          | 1000 | MHz  |          |

| f <sub>CPU</sub>   | SR |   | Operating frequency   | _               | —                            | 64         |      | MHz  |          |

| V <sub>DD_LV</sub> | SR |   | LV operating voltages | _               |                              | —          | 1.28 | —    | V        |

| S <sub>EMI</sub>   | СС | Т |                       | LQFP144 package | No PLL frequency modulation  | —          |      | 18   | dBµ<br>V |

|                    |    |   |                       |                 | ±2% PLL frequency modulation | _          | _    | 14   | dBµ<br>V |

Table 34. EMI radiated emission measurement<sup>1,2</sup>

<sup>1</sup> EMI testing and I/O port waveforms per IEC 61967-1, -2, -4

<sup>2</sup> For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

### 3.20.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

### 3.20.3.1 Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

# 3.26 ADC electrical characteristics

### 3.26.1 Introduction

The device provides a 10-bit Successive Approximation Register (SAR) analog-to-digital converter.

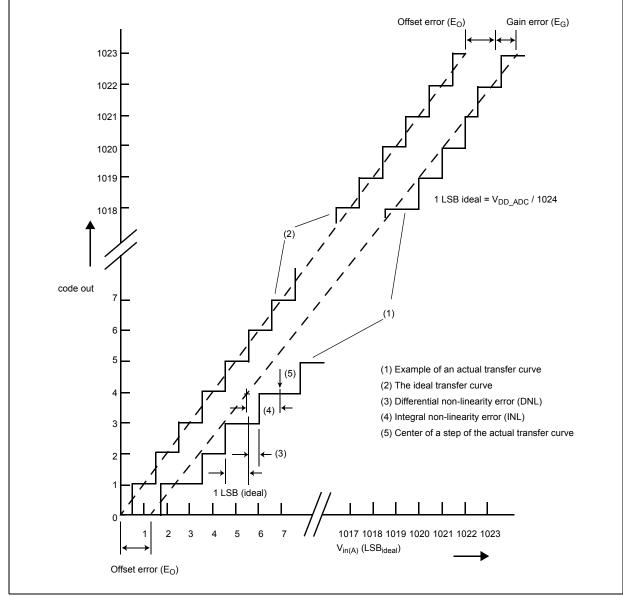

Figure 19. ADC characteristic and error definitions

### 3.26.2 Input impedance and ADC accuracy

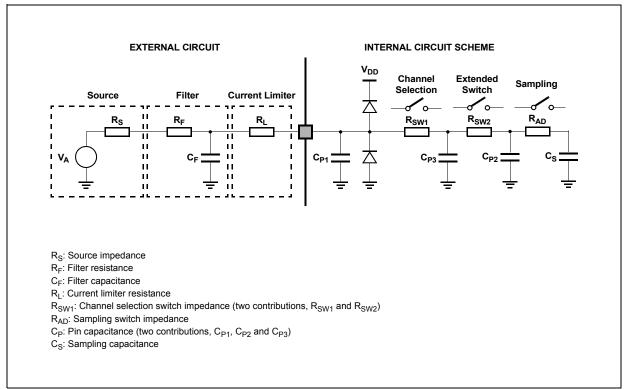

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as

Figure 21. Input equivalent circuit (extended channels)

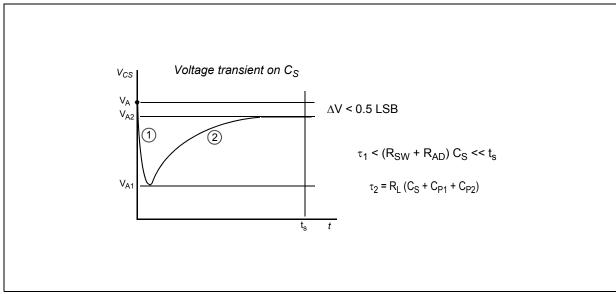

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit in Figure 20): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Figure 22. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

| 0                |                                                 | ~                    | Demonster                                    | Q a se d                                            | tions <sup>1</sup> |     | Value |     |      |

|------------------|-------------------------------------------------|----------------------|----------------------------------------------|-----------------------------------------------------|--------------------|-----|-------|-----|------|

| Symbol           |                                                 | С                    | Parameter                                    | Condi                                               | tions'             | Min | Тур   | Мах | Unit |

| C <sub>P3</sub>  | СС                                              | D                    | ADC input pin<br>capacitance 3               | _                                                   |                    |     | -     | 1   | pF   |

| R <sub>SW1</sub> | СС                                              | D                    | Internal resistance of<br>analog source      | -                                                   | _                  | —   | -     | 3   | kΩ   |

| $R_{SW2}$        | СС                                              | D                    | Internal resistance of<br>analog source      | -                                                   | _                  | —   | -     | 2   | kΩ   |

| R <sub>AD</sub>  | СС                                              | D                    | Internal resistance of<br>analog source      | _                                                   |                    |     | -     | 2   | kΩ   |

| I <sub>INJ</sub> | injection on or<br>ADC input,<br>different from |                      | injection on one                             | V <sub>DD</sub> =<br>3.3 V ± 10%                    | -5                 | -   | 5     | mA  |      |

|                  |                                                 |                      | different from the converted                 | V <sub>DD</sub> =<br>5.0 V ± 10%                    | -5                 | -   | 5     |     |      |

| INL              | СС                                              | Т                    | Absolute value for<br>integral non-linearity | No overload                                         |                    |     | 0.5   | 1.5 | LSB  |

| DNL              | СС                                              | Т                    | Absolute differential non-linearity          | No overload                                         |                    | —   | 0.5   | 1.0 | LSB  |

| E <sub>O</sub>   | СС                                              | Т                    | Absolute offset error                        | -                                                   |                    | —   | 0.5   |     | LSB  |

| E <sub>G</sub>   | СС                                              | Т                    | Absolute gain error                          | _                                                   |                    | —   | 0.6   | —   | LSB  |

| TUEp             | СС                                              | Ρ                    | Total unadjusted error <sup>7</sup>          | Without current injection<br>With current injection |                    | -2  | 0.6   | 2   | LSB  |

|                  |                                                 | Т                    | for precise channels,<br>input only pins     |                                                     |                    | -3  |       | 3   |      |

| TUEx             | СС                                              | Т                    | Total unadjusted error <sup>7</sup>          | Without current injection                           |                    | -3  | 1     | 3   | LSB  |

| T for extended c |                                                 | for extended channel | With current inje                            | ection                                              | -4                 |     | 4     |     |      |

| Table 45. ADC conversion | n characteristics | (continued) |

|--------------------------|-------------------|-------------|

|--------------------------|-------------------|-------------|

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified.

$^2$  Analog and digital V<sub>SS</sub> **must** be common (to be tied together externally).

<sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

<sup>4</sup> Duty cycle is ensured by using system clock without prescaling. When ADCLKSEL = 0, the duty cycle is ensured by internal divider by 2.

<sup>5</sup> During the sampling time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_s$ . After the end of the sampling time  $t_s$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_s$  depend on programming.

<sup>6</sup> This parameter does not include the sampling time t<sub>s</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

<sup>7</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

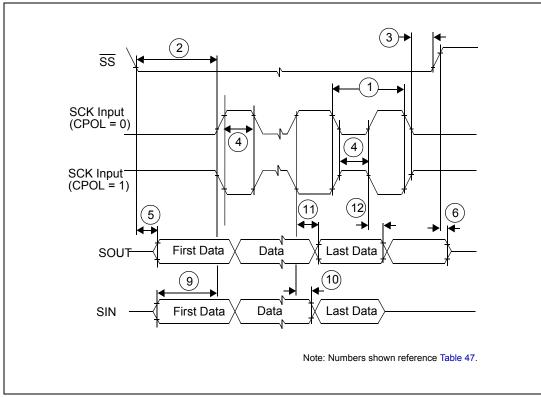

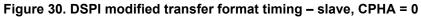

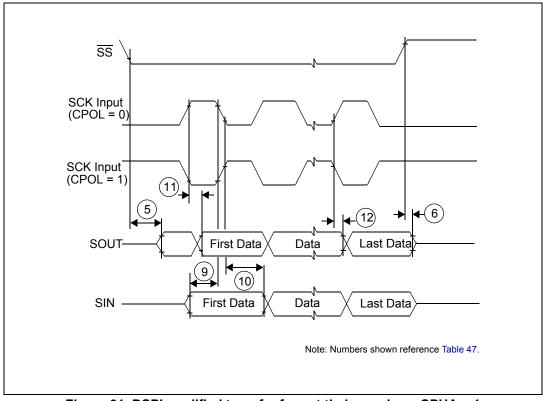

### Table 47. DSPI characteristics<sup>1</sup> (continued)

| No. | Symbo              | Symbol | wmbol |                            | mbol        | umbol          |   | Symbol | с              | Parameter |     | D  | SPI0/DS | PI1 |  | DSPI | 2 | Unit |

|-----|--------------------|--------|-------|----------------------------|-------------|----------------|---|--------|----------------|-----------|-----|----|---------|-----|--|------|---|------|

| NO. | No. Symbo          |        |       | Falameter                  |             | Min Typ Ma     |   | Max    | Min            | Тур       | Мах |    |         |     |  |      |   |      |

| 10  | t <sub>HI</sub>    | SR     | D     | Data hold time for inputs  | Master mode | 0              | — | _      | 0              | —         | —   | ns |         |     |  |      |   |      |

|     |                    |        |       |                            | Slave mode  | 2 <sup>6</sup> | — | _      | 2 <sup>6</sup> | —         | _   |    |         |     |  |      |   |      |

| 11  | t <sub>SUO</sub> 7 | CC     | D     | Data valid after SCK edge  | Master mode | _              | — | 32     | _              | —         | 50  | ns |         |     |  |      |   |      |

|     |                    |        |       |                            | Slave mode  | _              | _ | 52     | _              | —         | 160 | 1  |         |     |  |      |   |      |

| 12  | t <sub>HO</sub> 7  | CC     | D     | Data hold time for outputs | Master mode | 0              | — | _      | 0              | _         | _   | ns |         |     |  |      |   |      |

|     |                    |        |       |                            | Slave mode  | 8              | — | _      | 13             |           | _   | 1  |         |     |  |      |   |      |

Operating conditions:  $C_L$  = 10 to 50 pF, Slew<sub>IN</sub> = 3.5 to 15 ns.

<sup>2</sup> Maximum value is reached when CSn pad is configured as SLOW pad while SCK pad is configured as MEDIUM. A positive value means that SCK starts before CSn is asserted. DSPI2 has only SLOW SCK available.

<sup>3</sup> Maximum value is reached when CSn pad is configured as MEDIUM pad while SCK pad is configured as SLOW. A positive value means that CSn is deasserted before SCK. DSPI0 and DSPI1 have only MEDIUM SCK available.

<sup>4</sup> The t<sub>CSC</sub> delay value is configurable through a register. When configuring t<sub>CSC</sub> (using PCSSCK and CSSCK fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than ∆t<sub>CSC</sub> to ensure positive t<sub>CSCext</sub>.

<sup>5</sup> The t<sub>ASC</sub> delay value is configurable through a register. When configuring t<sub>ASC</sub> (using PASC and ASC fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than ∆t<sub>ASC</sub> to ensure positive t<sub>ASCext</sub>.

<sup>6</sup> This delay value corresponds to SMPL\_PT = 00b which is bit field 9 and 8 of the DSPI\_MCR.

<sup>7</sup> SCK and SOUT configured as MEDIUM pad

Figure 32. DSPI PCS strobe (PCSS) timing

# 3.27.3 Nexus characteristics

| No. | Symbol             |       | с | Parameter                     |     | Unit |     |      |

|-----|--------------------|-------|---|-------------------------------|-----|------|-----|------|

| NO. | Symb               | Зуший |   | Falameter                     | Min | Тур  | Max | Onit |

| 1   | t <sub>TCYC</sub>  | CC    | D | TCK cycle time                | 64  | —    | —   | ns   |

| 2   | t <sub>MCYC</sub>  | CC    | D | MCKO cycle time               | 32  | —    | —   | ns   |

| 3   | t <sub>MDOV</sub>  | CC    | D | MCKO low to MDO data valid    | _   | —    | 8   | ns   |

| 4   | t <sub>MSEOV</sub> | CC    | D | MCKO low to MSEO_b data valid | _   | —    | 8   | ns   |

| 5   | t <sub>EVTOV</sub> | CC    | D | MCKO low to EVTO data valid   | _   | —    | 8   | ns   |

| 10  | t <sub>NTDIS</sub> | CC    | D | TDI data setup time           | 15  | —    | —   | ns   |

|     | t <sub>NTMSS</sub> | CC    | D | TMS data setup time           | 15  | —    | —   | ns   |

| 11  | t <sub>NTDIH</sub> | CC    | D | TDI data hold time            | 5   | —    | —   | ns   |

|     | t <sub>NTMSH</sub> | CC    | D | TMS data hold time            | 5   | —    | —   | ns   |

| 12  | t <sub>TDOV</sub>  | CC    | D | TCK low to TDO data valid     | 35  | —    | _   | ns   |

| 13  | t <sub>TDOI</sub>  | CC    | D | TCK low to TDO data invalid   | 6   | _    | _   | ns   |

| Table 48. Nexu | us characteristics |

|----------------|--------------------|

|----------------|--------------------|

### **Package characteristics**

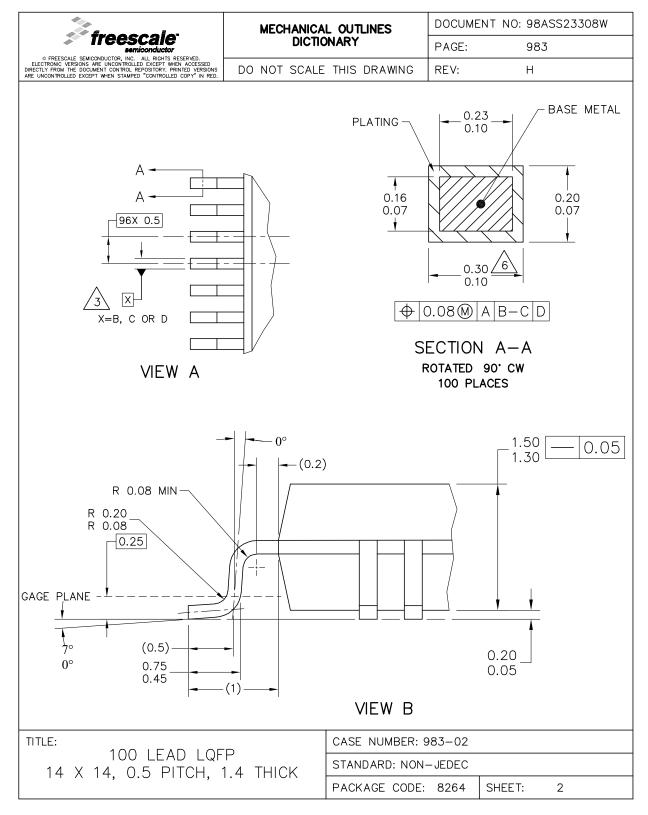

Figure 39. 100 LQFP package mechanical drawing (2 of 3)

### **Document revision history**

| Revision  | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 (cont.) | 06-Mar-2009 | Updated Table 16, Table 17, Table 18, Table 19 and Table 20<br>Added Section 3.15.4, Output pin transition times<br>Updated Table 23<br>Updated Table 25<br>Section 3.17.1, Voltage regulator electrical characteristics: Amended description of<br>LV_PLL<br>Figure 10: Exchanged position of symbols C <sub>DEC1</sub> and C <sub>DEC2</sub><br>Updated Table 26<br>Added Figure 13<br>Updated Table 27 and Table 28<br>Updated Section 3.20, Electromagnetic compatibility (EMC) characteristics<br>Updated Section 3.20, Electromagnetic compatibility (EMC) characteristics<br>Updated Section 3.21, Fast external crystal oscillator (4 to 16 MHz) electrical<br>characteristics<br>Updated Table 41, Table 42 and Table 43<br>Added Section 3.27, On-chip peripherals<br>Added Table 44<br>Updated Table 45<br>Updated Table 47<br>Added Section Appendix A, Abbreviations |

### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 15-Mar-2010 | In the "Introduction" section, relocated a note.<br>In the "MPC5604B/C device comparison" table, added footnote regarding SCI and CAN.<br>In the "Absolute maximum ratings" table, removed the min value of V <sub>IN</sub> relative to V <sub>DD</sub> .<br>In the "Recommended operating conditions (3.3 V)" table:<br>* T <sub>A</sub> C-Grade Part, TJ C-Grade Part, TA V-Grade Part, TJ V-Grade Part, TA M-Grade Part, TJ M-Grade Part;<br>added new rows.<br>* TV <sub>DD</sub> : made single row.<br>In the "LQFP thermal characteristics" table, added more rows.<br>Removed '208 MAPBGA thermal characteristics" table.<br>In the "I/O consumption" table:<br>* Removed I <sub>DVNSEG</sub> row.<br>* Added "I/O weight" table.<br>In the "Voltage regulator electrical characteristics" table:<br>* Updated the values.<br>* Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> .<br>* Added a note about I <sub>DD_BC</sub> .<br>In the "Low voltage monitor electrical characteristics" table:<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>DORH</sub> value.<br>Entirely updated the "Flash power supply DC electrical characteristics" table.<br>In the "Slow external crystal oscillator (32 kHz) electrical characteristics" table.<br>In the "Slow external crystal oscillator (32 kHz) electrical characteristics" table:<br>Nemoved g <sub>INXOSC</sub> row.<br>* Inserted values of I <sub>SXOSCEIAS</sub> .<br>Entirely updated the "Fast internal RC oscillator (16 MHz) electrical characteristics" table:<br>In the "ADC conversion characteristics" table: updated the "DSPI characteristics" table.<br>In the "ADC conversion characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the "DSPI characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the note shout the condition from "Flash read access timing" table<br>Removed the note shout the condition from "Flash read access timing" table<br>Remov |

### Table 50. Revision history (continued)

### **Document revision history**

| Revision | Date         | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9        | 16 June 2011 | Formatting and minor editorial changes throughout<br>Harmonized oscillator nomenclature                                                                                                                                                                                                                                                                                                                                                                                          |

|          |              | Removed all instances of note "All 64 LQFP information is indicative and must be                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |              | confirmed during silicon validation."                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |              | Device comparison table: changed temperature value in footnote 2 from 105 °C to 125 °C MPC560xB LQFP 64-pin configuration and MPC560xC LQFP 64-pin configuration: renamed pin 6 from VPP TEST to VSS HV                                                                                                                                                                                                                                                                          |

|          |              | Removed "Pin Muxing" section; added sections "Pad configuration during reset phases",<br>"Voltage supply pins", "Pad types", "System pins," "Functional ports", and "Nexus 2+<br>pins"                                                                                                                                                                                                                                                                                           |

|          |              | Section "NVUSRO register": edited content to separate configuration into electrical<br>parameters and digital functionality; updated footnote describing default value of '1' in<br>field descriptions NVUSRO[PAD3V5V] and NVUSRO[OSCILLATOR_MARGIN]<br>Added section "NVUSRO[WATCHDOG EN] field description"                                                                                                                                                                    |

|          |              | Recommended operating conditions (3.3 V) and Recommended operating conditions (5.0 V): updated conditions for ambient and junction temperature characteristics I/O input DC electrical characteristics: updated I <sub>LKG</sub> characteristics                                                                                                                                                                                                                                 |

|          |              | Section "I/O pad current specification": removed content referencing the I <sub>DYNSEG</sub> maximum value                                                                                                                                                                                                                                                                                                                                                                       |

|          |              | I/O consumption: replaced instances of "Root medium square" with "Root mean square"<br>I/O weight: replaced instances of bit "SRE" with "SRC"; added pads PH[9] and PH[10];<br>added supply segments; removed weight values in 64-pin LQFP for pads that do not<br>exist in that package                                                                                                                                                                                         |

|          |              | Reset electrical characteristics: updated parameter classification for  I <sub>WPU</sub>  <br>Updated Voltage regulator electrical characteristics                                                                                                                                                                                                                                                                                                                               |

|          |              | Section "Low voltage detector electrical characteristics": changed title (was "Voltage monitor electrical characteristics"); added event status flag names found in RGM chapter of device reference manual to POR module and LVD descriptions; replaced instances of "Low voltage monitor" with "Low voltage detector"; updated values for V <sub>LVDLVBKPL</sub> and V <sub>LVDLVCORL</sub> ; replaced "LVD_DIGBKP" with "LVDLVBKP" in note Updated section "Power consumption" |

|          |              | Fast external crystal oscillator (4 to 16 MHz) electrical characteristics: updated parameter<br>classification for V <sub>FXOSCOP</sub>                                                                                                                                                                                                                                                                                                                                          |

|          |              | Crystal oscillator and resonator connection scheme: added footnote about possibility of adding a series resistor                                                                                                                                                                                                                                                                                                                                                                 |