# E·XFL

## NXP USA Inc. - SPC5604BF2MLL6 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 64MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bf2mll6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Block diagram

Table 3 summarizes the functions of all blocks present in the MPC5604B/C series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                                         | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-locked loop (FMPLL)                 | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock                      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                               | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)                           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Power control unit (MC_PCU)                                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)                           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

Table 3. MPC5604B/C series block summary

| Block                                     | Function                                                                                                                                                                                                                         |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory protection unit (MPU)              | Provides hardware access control for all memory references generated in a device                                                                                                                                                 |

| Nexus development interface<br>(NDI)      | Provides real-time development support capabilities in compliance with the IEEE-ISTO 5001-2003 standard                                                                                                                          |

| Periodic interrupt timer (PIT)            | Produces periodic interrupts and triggers                                                                                                                                                                                        |

| Real-time counter (RTC)                   | A free running counter used for time keeping applications, the RTC can be configured to generate an interrupt at a predefined interval independent of the mode of operation (run mode or low-power mode)                         |

| System integration unit (SIU)             | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| Static random-access memory (SRAM)        | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System status configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                 | Provides a set of output compare events to support AUTOSAR (Automotive Open System Architecture) and operating system tasks                                                                                                      |

| Software watchdog timer (SWT)             | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                        | The wakeup unit supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                         |

| Crossbar (XBAR) switch                    | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.                                                                  |

## **3** Package pinouts and signal descriptions

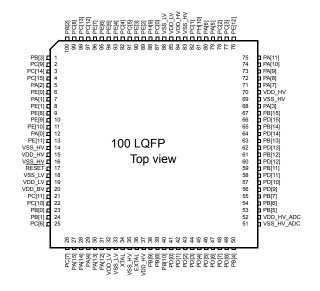

## 3.1 Package pinouts

The available LQFP pinouts and the 208 MAPBGA ballmap are provided in the following figures. For pin signal descriptions, please refer to the device reference manual.

|          |         | -                                  |                                                                              |                                                              |                               |          | uo                  |                  | Pin              | num      | ber      |                         |

|----------|---------|------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                                     | Peripheral                                                   | I/O direction <sup>2</sup>    | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PC[2]    | PCR[34] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[34]<br>SCK_1<br>CAN4TX <sup>11</sup><br>—<br>EIRQ[5]                    | SIUL<br>DSPI_1<br>FlexCAN_4<br><br>SIUL                      | I/O<br>I/O<br>O<br>I          | Μ        | Tristate            | 50               | 50               | 78       | 117      | A11                     |

| PC[3]    | PCR[35] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[35]<br>CS0_1<br>MA[0]<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[6] | SIUL<br>DSPI_1<br>ADC<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | /0<br> /0<br> -<br> <br> <br> | S        | Tristate            | 49               | 49               | 77       | 116      | B11                     |

| PC[4]    | PCR[36] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[36]<br>—<br>—<br>—<br>SIN_1<br>CAN3RX <sup>11</sup>                     | SIUL<br>—<br>—<br>DSPI_1<br>FlexCAN_3                        | I/O<br>—<br>—<br>—<br>—       | Μ        | Tristate            | 62               | 62               | 92       | 131      | B7                      |

| PC[5]    | PCR[37] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[37]<br>SOUT_1<br>CAN3TX <sup>11</sup><br>—<br>EIRQ[7]                   | SIUL<br>DSPI1<br>FlexCAN_3<br><br>SIUL                       | I/O<br>O<br>O<br>I            | Μ        | Tristate            | 61               | 61               | 91       | 130      | A7                      |

| PC[6]    | PCR[38] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[38]<br>LIN1TX<br>—<br>—                                                 | SIUL<br>LINFlex_1<br>—                                       | I/O<br>O<br>                  | S        | Tristate            | 16               | 16               | 25       | 36       | R2                      |

| PC[7]    | PCR[39] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[39]<br>—<br>—<br>LIN1RX<br>WKPU[12] <sup>4</sup>                        | SIUL<br>—<br>—<br>LINFlex_1<br>WKPU                          | I/O<br>   <br>   <br>         | S        | Tristate            | 17               | 17               | 26       | 37       | P3                      |

| PC[8]    | PCR[40] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[40]<br>LIN2TX<br>—<br>—                                                 | SIUL<br>LINFlex_2<br>—                                       | I/O<br>O<br>—                 | S        | Tristate            | 63               | 63               | 99       | 143      | A1                      |

## Table 6. Functional port pin descriptions (continued)

|                     |         | -                               |                                                                           |                                          |                            |          | Ľ                   |                  | Pin              | num      | ber      |                         |

|---------------------|---------|---------------------------------|---------------------------------------------------------------------------|------------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin            | PCR     | Alternate function <sup>1</sup> | Function                                                                  | Peripheral                               | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PD[9]               | PCR[57] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[57]<br>—<br>—<br>—<br>GPI[13]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> -<br>                 | Ι        | Tristate            | _                | _                | 56       | 78       | N15                     |

| PD[10]              | PCR[58] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[58]<br>—<br>—<br>—<br>GPI[14]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> <br> <br>             | Ι        | Tristate            |                  | _                | 57       | 79       | N14                     |

| PD[11]              | PCR[59] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[59]<br>—<br>—<br>—<br>GPI[15]                                        | SIUL<br>—<br>—<br>—<br>ADC               | <br> -<br>                 | Ι        | Tristate            | _                | _                | 58       | 80       | N16                     |

| PD[12] <sup>8</sup> | PCR[60] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[60]<br>CS5_0<br>E0UC[24]<br>—<br>ANS[4]                              | SIUL<br>DSPI_0<br>eMIOS_0<br>—<br>ADC    | I/O<br>O<br>I/O<br>I       | J        | Tristate            | _                | _                | 60       | 82       | M15                     |

| PD[13]              | PCR[61] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[61]<br>CS0_1<br>E0UC[25]<br><br>ANS[5]                               | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC    | I/O<br>I/O<br>I/O<br>I     | J        | Tristate            |                  |                  | 62       | 84       | M14                     |

| PD[14]              | PCR[62] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[62]<br>CS1_1<br>E0UC[26]<br>—<br>ANS[6]                              | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC    | I/O<br>O /O<br>I/O<br>-    | J        | Tristate            |                  |                  | 64       | 86       | L15                     |

| PD[15]              | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ANS[7]                              | SIUL<br>DSPI_1<br>eMIOS_0<br><br>ADC     | I/O<br>O<br>I/O<br>I       | J        | Tristate            | —                | —                | 66       | 88       | L14                     |

| PE[0]               | PCR[64] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[64]<br>E0UC[16]<br>—<br>CAN5RX <sup>11</sup><br>WKPU[6] <sup>4</sup> | SIUL<br>eMIOS_0<br><br>FlexCAN_5<br>WKPU | /0<br> /0<br> -<br>        | S        | Tristate            | _                | _                | 6        | 10       | F1                      |

## Table 6. Functional port pin descriptions (continued)

|          |          | -                               |                                                     |                                       |                            |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|----------|---------------------------------|-----------------------------------------------------|---------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR      | Alternate function <sup>1</sup> | Function                                            | Peripheral                            | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PG[2]    | PCR[98]  | AF0<br>AF1<br>AF2<br>AF3        | GPIO[98]<br>E1UC[11]<br>—<br>—                      | SIUL<br>eMIOS_1<br>                   | I/O<br>I/O<br>             | М        | Tristate            | —                | —                |          | 8        | E4                      |

| PG[3]    | PCR[99]  | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[99]<br>E1UC[12]<br>—<br>WKPU[17] <sup>4</sup>  | SIUL<br>eMIOS_1<br><br>WKPU           | I/O<br>I/O<br>—<br>I       | S        | Tristate            | _                | _                | _        | 7        | E3                      |

| PG[4]    | PCR[100] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[100]<br>E1UC[13]<br>—<br>—                     | SIUL<br>eMIOS_1<br>                   | I/O<br>I/O<br>             | М        | Tristate            |                  | _                |          | 6        | E1                      |

| PG[5]    | PCR[101] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[101]<br>E1UC[14]<br>—<br>WKPU[18] <sup>4</sup> | SIUL<br>eMIOS_1<br><br>WKPU           | /O<br> /O<br><br>          | S        | Tristate            | _                | _                | _        | 5        | E2                      |

| PG[6]    | PCR[102] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[102]<br>E1UC[15]<br>—<br>—                     | SIUL<br>eMIOS_1<br>—                  | I/O<br>I/O<br>—            | М        | Tristate            | —                | —                |          | 30       | M2                      |

| PG[7]    | PCR[103] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[103]<br>E1UC[16]<br>—<br>—                     | SIUL<br>eMIOS_1<br>—                  | I/O<br>I/O<br>—            | М        | Tristate            | _                | _                |          | 29       | M1                      |

| PG[8]    | PCR[104] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[104]<br>E1UC[17]<br>—<br>CS0_2<br>EIRQ[15]     | SIUL<br>eMIOS_1<br><br>DSPI_2<br>SIUL | /O<br> /O<br> /O<br>       | S        | Tristate            | _                |                  | _        | 26       | L2                      |

| PG[9]    | PCR[105] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[105]<br>E1UC[18]<br><br>SCK_2                  | SIUL<br>eMIOS_1<br><br>DSPI_2         | I/O<br>I/O<br><br>I/O      | S        | Tristate            | —                | —                |          | 25       | L1                      |

| PG[10]   | PCR[106] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[106]<br>E0UC[24]<br>—<br>—                     | SIUL<br>eMIOS_0<br>—                  | I/O<br>I/O<br>—            | S        | Tristate            |                  |                  |          | 114      | D13                     |

Table 6. Functional port pin descriptions (continued)

## 3.12 Absolute maximum ratings

Table 12. Absolute maximum ratings

| Symbo                | .1 | Parameter                                                                                     | Conditions                                 | Val                  | lue                  | Unit |

|----------------------|----|-----------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|----------------------|------|

| Symbo                | 1  | Falameter                                                                                     | Conditions                                 | Min                  | Max                  | Unit |

| V <sub>SS</sub>      | SR | Digital ground on VSS_HV pins                                                                 | _                                          | 0                    | 0                    | V    |

| V <sub>DD</sub>      | SR | Voltage on VDD_HV pins with respect to ground ( $V_{SS}$ )                                    | _                                          | -0.3                 | 6.0                  | V    |

| V <sub>SS_LV</sub>   | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _                                          | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub>   | SR | Voltage on VDD_BV pin (regulator                                                              | _                                          | -0.3                 | 6.0                  | V    |

|                      |    | supply) with respect to ground $(V_{SS})$                                                     | Relative to V <sub>DD</sub>                | -0.3                 | V <sub>DD</sub> +0.3 |      |

| V <sub>SS_ADC</sub>  | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )           | _                                          | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub>  | SR | Voltage on VDD_HV_ADC pin (ADC                                                                | —                                          | -0.3                 | 6.0                  | V    |

|                      |    | reference) with respect to ground $(V_{SS})$                                                  | Relative to V <sub>DD</sub>                | V <sub>DD</sub> -0.3 | V <sub>DD</sub> +0.3 |      |

| V <sub>IN</sub>      | SR | Voltage on any GPIO pin with respect to                                                       | _                                          | -0.3                 | 6.0                  | V    |

|                      |    | ground (V <sub>SS</sub> )                                                                     | Relative to V <sub>DD</sub>                |                      | V <sub>DD</sub> +0.3 |      |

| I <sub>INJPAD</sub>  | SR | Injected input current on any pin during overload condition                                   | _                                          | -10                  | 10                   | mA   |

| I <sub>INJSUM</sub>  | SR | Absolute sum of all injected input<br>currents during overload condition                      | _                                          | -50                  | 50                   |      |

| I <sub>AVGSEG</sub>  | SR | Sum of all the static I/O current within a                                                    | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 |                      | 70                   | mA   |

|                      |    | supply segment                                                                                | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |                      | 64                   |      |

| I <sub>CORELV</sub>  | SR | Low voltage static current sink through VDD_BV                                                | _                                          |                      | 150                  | mA   |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                                           | —                                          | -55                  | 150                  | °C   |

## NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

|             |             |                         |        |                      | 144/100 | ) LQFP  |         |         | 64 L    | QFP     |         |

|-------------|-------------|-------------------------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Sup         | ply seg     | ment                    | Pad    | Weigl                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 144<br>LQFP | 100<br>LQFP | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 2           | 2           | 2                       | PB[13] | 10%                  | —       | 12%     |         | 18%     |         | 21%     | _       |

|             |             |                         | PD[14] | 10%                  | _       | 12%     | _       |         |         |         |         |

|             |             | 2                       | PB[14] | 10%                  | —       | 12%     | _       | 18%     |         | 21%     |         |

|             |             |                         | PD[15] | 10%                  | —       | 11%     | —       | —       | _       | —       | —       |

|             |             | 2                       | PB[15] | 9%                   | —       | 11%     | —       | 18%     |         | 21%     | —       |

|             |             |                         | PA[3]  | 9%                   | —       | 11%     | _       | 18%     |         | 21%     | —       |

|             |             |                         | PG[13] | 9%                   | 13%     | 10%     | 11%     | —       | _       | —       | —       |

|             |             |                         | PG[12] | 9%                   | 12%     | 10%     | 11%     | _       | _       | —       | —       |

|             |             |                         | PH[0]  | 5%                   | 8%      | 6%      | 7%      | —       |         | —       | —       |

|             |             |                         | PH[1]  | 5%                   | 7%      | 6%      | 6%      | —       | _       | —       | —       |

|             |             |                         | PH[2]  | 5%                   | 6%      | 5%      | 6%      | _       | _       | —       | —       |

|             |             |                         | PH[3]  | 4%                   | 6%      | 5%      | 5%      | —       |         | —       | —       |

|             |             |                         | PG[1]  | 4%                   | —       | 4%      | —       | —       | _       | —       | —       |

|             |             |                         | PG[0]  | 3%                   | 4%      | 4%      | 4%      | —       |         | —       | —       |

| 3           |             |                         | PF[15] | 3%                   | —       | 4%      | —       | —       |         | —       | —       |

|             |             |                         | PF[14] | 4%                   | 5%      | 5%      | 5%      | —       | _       | —       | —       |

|             |             |                         | PE[13] | 4%                   | —       | 5%      | —       | —       |         | —       | —       |

|             | 3           | 2                       | PA[7]  | 5%                   | —       | 6%      | _       | 16%     |         | 19%     | —       |

|             |             |                         | PA[8]  | 5%                   | —       | 6%      | —       | 16%     | _       | 19%     | —       |

|             |             |                         | PA[9]  | 5%                   | —       | 6%      | —       | 15%     |         | 18%     | —       |

|             |             |                         | PA[10] | 6%                   | _       | 7%      | —       | 15%     | _       | 18%     | —       |

|             |             |                         | PA[11] | 6%                   | —       | 8%      | —       | 14%     | _       | 17%     | —       |

|             |             |                         | PE[12] | 7%                   | _       | 8%      | —       | —       | _       | _       | —       |

|             |             |                         | PG[14] | 7%                   | _       | 8%      | —       | _       | _       | —       | —       |

|             | _           |                         | PG[15] | 7%                   | 10%     | 8%      | 9%      |         | _       | —       | _       |

|             | _           |                         | PE[14] | 7%                   | —       | 8%      | —       | —       |         | —       | —       |

|             | _           |                         | PE[15] | 7%                   | 9%      | 8%      | 8%      | —       |         |         | —       |

|             | _           |                         | PG[10] | 6%                   |         | 8%      |         | _       | _       | —       | —       |

|             | _           |                         | PG[11] | 6%                   | 9%      | 7%      | 8%      | —       |         | —       | —       |

|             | 3           | 2                       | PC[3]  | 6%                   |         | 7%      |         | 7%      | _       | 9%      |         |

|             |             |                         | PC[2]  | 6%                   | 8%      | 7%      | 7%      | 6%      | 9%      | 8%      | 8%      |

## Table 24. I/O weight<sup>1</sup> (continued)

#### Package pinouts and signal descriptions

| •           |             |                         |        |                      | 144/100 | ) LQFP  |         |         | 64 L    | QFP          |         |  |

|-------------|-------------|-------------------------|--------|----------------------|---------|---------|---------|---------|---------|--------------|---------|--|

| Sup         | ply seg     | ment                    | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weight 3.3 V |         |  |

| 144<br>LQFP | 100<br>LQFP | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0      | SRC = 1 |  |

| 3           | 3           | 2                       | PA[5]  | 5%                   | 7%      | 6%      | 6%      | 6%      | 8%      | 7%           | 7%      |  |

|             |             |                         | PA[6]  | 5%                   | —       | 6%      | _       | 5%      | _       | 6%           |         |  |

|             |             |                         | PH[10] | 4%                   | 6%      | 5%      | 5%      | 5%      | 7%      | 6%           | 6%      |  |

|             |             |                         | PC[1]  | 5%                   | —       | 5%      |         | 5%      | —       | 5%           |         |  |

| 4           | 4           | 3                       | PC[0]  | 6%                   | 9%      | 7%      | 8%      | 6%      | 9%      | 7%           | 8%      |  |

|             |             |                         | PH[9]  | 7                    | 7       | 8       | 8       | 7       | 7       | 8            | 8       |  |

|             |             |                         | PE[2]  | 7%                   | 10%     | 9%      | 9%      |         | —       | —            |         |  |

|             |             |                         | PE[3]  | 8%                   | 11%     | 9%      | 9%      | _       | _       |              |         |  |

|             |             | 3                       | PC[5]  | 8%                   | 11%     | 9%      | 10%     | 8%      | 11%     | 9%           | 10%     |  |

|             |             |                         | PC[4]  | 8%                   | 12%     | 10%     | 10%     | 8%      | 12%     | 10%          | 10%     |  |

|             |             |                         | PE[4]  | 8%                   | 12%     | 10%     | 11%     | _       | _       |              |         |  |

|             |             |                         | PE[5]  | 9%                   | 12%     | 10%     | 11%     | _       | —       | —            | _       |  |

|             |             | —                       | PH[4]  | 9%                   | 13%     | 11%     | 11%     | _       | _       | _            | _       |  |

|             |             | _                       | PH[5]  | 9%                   | —       | 11%     | _       | _       | —       | —            | _       |  |

|             |             | _                       | PH[6]  | 9%                   | 13%     | 11%     | 12%     | _       | —       | —            | —       |  |

|             |             | —                       | PH[7]  | 9%                   | 13%     | 11%     | 12%     | _       | _       | _            | _       |  |

|             |             | _                       | PH[8]  | 10%                  | 14%     | 11%     | 12%     | _       | _       |              |         |  |

|             | 4           | _                       | PE[6]  | 10%                  | 14%     | 12%     | 12%     | _       | _       |              |         |  |

|             |             | —                       | PE[7]  | 10%                  | 14%     | 12%     | 12%     |         |         | —            | _       |  |

|             |             | _                       | PC[12] | 10%                  | 14%     | 12%     | 13%     | _       | _       | —            | _       |  |

|             |             | —                       | PC[13] | 10%                  | —       | 12%     | _       |         | —       | —            | _       |  |

|             |             | 3                       | PC[8]  | 10%                  |         | 12%     |         | 10%     |         | 12%          | _       |  |

|             |             |                         | PB[2]  | 10%                  | 15%     | 12%     | 13%     | 10%     | 15%     | 12%          | 13%     |  |

Table 24. I/O weight<sup>1</sup> (continued)

$\overline{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to125 °C, unless otherwise specified

<sup>2</sup> Segments shown apply to MPC560xB devices only

<sup>3</sup> SRC: "Slew Rate Control" bit in SIU\_PCR

## 3.16 **RESET** electrical characteristics

The device implements a dedicated bidirectional RESET pin.

#### Example 1. No regulator (worst case)

The  $|\Delta_{VDD(STDBY)}|$  parameter can be seen as the  $V_{DD}$  voltage drop through the ESR resistance of the regulator stability capacitor when the  $I_{DD_BV}$  current required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the maximum equivalent resistance ESR<sub>STDBY</sub>(MAX) of the total capacitance on the  $V_{DD}$  supply:

$\text{ESR}_{\text{STDBY}}(\text{MAX}) = |\Delta_{\text{VDD}(\text{STDBY})}|/\text{I}_{\text{DD} \text{ BV}} = (30 \text{ mV})/(300 \text{ mA}) = 0.1\Omega^{-1}$

The dVDD(STDBY)/dt parameter can be seen as the  $V_{DD}$  voltage drop at the capacitance pin (excluding ESR drop) while providing the  $I_{DD_BV}$  supply required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the minimum equivalent capacitance  $C_{STDBY}(MIN)$  of the total capacitance on the  $V_{DD}$  supply:

$C_{STDBY}(MIN) = I_{DD BV}/dVDD(STDBY)/dt = (300 mA)/(15 mV/\mu s) = 20 \mu F$

This configuration is a worst case, with the assumption no regulator is available.

#### **Example 2. Simplified regulator**

The regulator should be able to provide significant amount of the current during the standby exit process. For example, in case of an ideal voltage regulator providing 200 mA current, it is possible to recalculate the equivalent  $ESR_{STDBY}(MAX)$  and  $C_{STDBY}(MIN)$  as follows:

$ESR_{STDBY}(MAX) = |\Delta_{VDD(STDBY)}|/(I_{DD BV} - 200 mA) = (30 mV)/(100 mA) = 0.3 \Omega$

$C_{\text{STDBY}}(\text{MIN}) = (I_{\text{DD} BV} - 200 \text{ mA})/d\text{VDD}(\text{STDBY})/dt = (300 \text{ mA} - 200 \text{ mA})/(15 \text{ mV/}\mu\text{s}) = 6.7 \mu\text{F}$

In case optimization is required,  $C_{\text{STDBY}}(\text{MIN})$  and  $\text{ESR}_{\text{STDBY}}(\text{MAX})$  should be calculated based on the regulator characteristics as well as the board  $V_{\text{DD}}$  plane characteristics.

## 3.17.2 Low voltage detector electrical characteristics

The device implements a Power-on Reset (POR) module to ensure correct power-up initialization, as well as four low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD}$  LV voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

## NOTE

When enabled, power domain No. 2 is monitored through LVDLVBKP.

<sup>1.</sup> Based on typical time for standby exit sequence of 20 µs, ESR(MIN) can actually be considered at ~50 kHz.

| Symbo                 | I  | С | Ratings                                               | Class                                                | Max value | Unit          |   |

|-----------------------|----|---|-------------------------------------------------------|------------------------------------------------------|-----------|---------------|---|

| V <sub>ESD(HBM)</sub> | СС |   | Electrostatic discharge voltage<br>(Human Body Model) | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-002 | H1C       | 2000          | V |

| V <sub>ESD(MM)</sub>  | СС |   | Electrostatic discharge voltage<br>(Machine Model)    | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-003 | M2        | 200           |   |

| V <sub>ESD(CDM)</sub> | СС |   | Electrostatic discharge voltage                       | $T_A = 25 \degree C$                                 | C3A       | 500           |   |

|                       |    |   | (Charged Device Model)                                | conforming to AEC-Q100-011                           |           | 750 (corners) |   |

Table 35. ESD absolute maximum ratings<sup>1 2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

## 3.20.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

Table 36. Latch-up results

| Symbol |    | mbol C Parameter |                       | Conditions                                       | Class      |  |

|--------|----|------------------|-----------------------|--------------------------------------------------|------------|--|

| LU     | CC | Т                | Static latch-up class | $T_A = 125 \ ^{\circ}C$<br>conforming to JESD 78 | II level A |  |

# 3.21 Fast external crystal oscillator (4 to 16 MHz) electrical characteristics

The device provides an oscillator/resonator driver. Figure 14 describes a simple model of the internal oscillator driver and provides an example of a connection for an oscillator or a resonator.

Table 37 provides the parameter description of 4 MHz to 16 MHz crystals used for the design simulations.

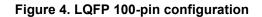

Figure 23. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $t_c$ ). Again the conversion period  $t_c$  is longer than the sampling time  $t_s$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $t_s$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 11 between the ideal and real sampled voltage on  $C_S$ :

$$\frac{V_{A2}}{V_{A}} = \frac{C_{P1} + C_{P2} + C_{F}}{C_{P1} + C_{P2} + C_{F} + C_{S}}$$

Eqn. 11

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

Eqn. 12

$$C_F > 2048 \bullet C_S$$

| 0                |                        | ~ | Demonster                                    | Q a se d                                             |                                  |     | Value |     |      |  |

|------------------|------------------------|---|----------------------------------------------|------------------------------------------------------|----------------------------------|-----|-------|-----|------|--|

| Symbol           |                        | С | Parameter                                    | Conditions <sup>1</sup>                              |                                  | Min | Тур   | Мах | Unit |  |

| C <sub>P3</sub>  | СС                     | D | ADC input pin<br>capacitance 3               | _                                                    |                                  |     | -     | 1   | pF   |  |

| R <sub>SW1</sub> | СС                     | D | Internal resistance of<br>analog source      | -                                                    | _                                | —   | -     | 3   | kΩ   |  |

| $R_{SW2}$        | СС                     | D | Internal resistance of<br>analog source      | -                                                    | _                                | —   | -     | 2   | kΩ   |  |

| R <sub>AD</sub>  | СС                     | D | Internal resistance of<br>analog source      | -                                                    | _                                |     | -     | 2   | kΩ   |  |

| I <sub>INJ</sub> | SR                     | — | Input current Injection                      | Current<br>injection on one                          | V <sub>DD</sub> =<br>3.3 V ± 10% | -5  | -     | 5   | mA   |  |

|                  |                        |   |                                              | ADC input,<br>different from<br>the converted<br>one | V <sub>DD</sub> =<br>5.0 V ± 10% | -5  | -     | 5   |      |  |

| INL              | СС                     | Т | Absolute value for<br>integral non-linearity | No overload                                          |                                  |     | 0.5   | 1.5 | LSB  |  |

| DNL              | СС                     | Т | Absolute differential non-linearity          | No overload                                          |                                  | —   | 0.5   | 1.0 | LSB  |  |

| E <sub>O</sub>   | СС                     | Т | Absolute offset error                        | -                                                    |                                  | —   | 0.5   |     | LSB  |  |

| E <sub>G</sub>   | СС                     | Т | Absolute gain error                          | -                                                    | _                                | —   | 0.6   | —   | LSB  |  |

| TUEp             | СС                     | Ρ | Total unadjusted error <sup>7</sup>          | Without current injection<br>With current injection  |                                  | -2  | 0.6   | 2   | LSB  |  |

|                  |                        | Т | for precise channels,<br>input only pins     |                                                      |                                  | -3  |       | 3   |      |  |

| TUEx             | СС                     | Т | Total unadjusted error <sup>7</sup>          | Without current                                      | injection                        | -3  | 1     | 3   | LSB  |  |

|                  | T for extended channel |   | With current injection                       |                                                      | -4                               |     | 4     |     |      |  |

| Table 45. ADC conversion | n characteristics | (continued) |

|--------------------------|-------------------|-------------|

|--------------------------|-------------------|-------------|

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified.

$^2$  Analog and digital V<sub>SS</sub> **must** be common (to be tied together externally).

<sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

<sup>4</sup> Duty cycle is ensured by using system clock without prescaling. When ADCLKSEL = 0, the duty cycle is ensured by internal divider by 2.

<sup>5</sup> During the sampling time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_s$ . After the end of the sampling time  $t_s$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_s$  depend on programming.

<sup>6</sup> This parameter does not include the sampling time t<sub>s</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

<sup>7</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

#### Package pinouts and signal descriptions

#### MPC5604B/C Microcontroller Data Sheet, Rev. 11

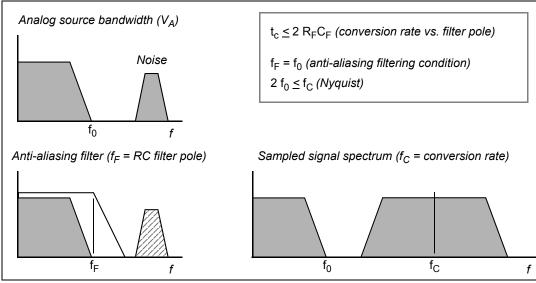

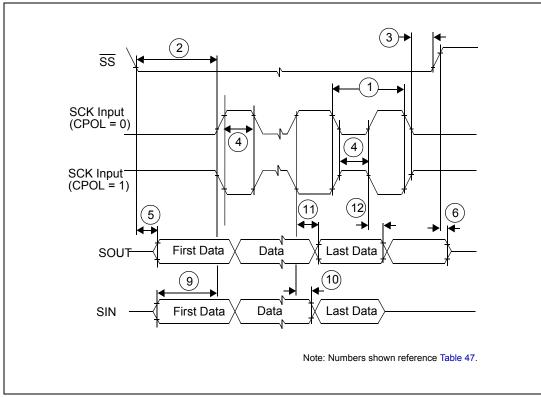

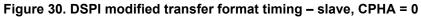

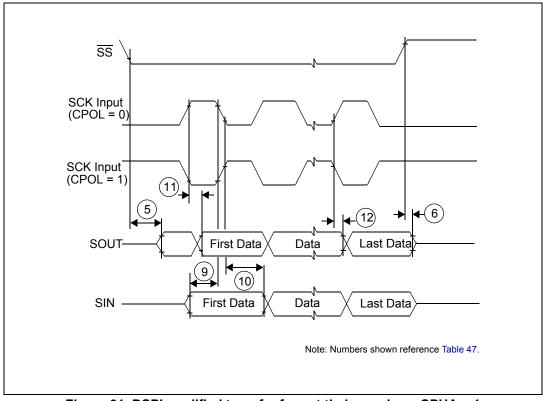

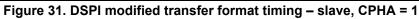

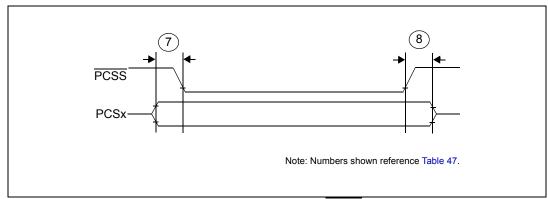

Figure 32. DSPI PCS strobe (PCSS) timing

## 3.27.3 Nexus characteristics

| No. | Symbol             |    | с | Parameter _                   |     | Value |     |        |  |

|-----|--------------------|----|---|-------------------------------|-----|-------|-----|--------|--|

| NO. |                    |    |   |                               | Min | Тур   | Max | - Unit |  |

| 1   | t <sub>TCYC</sub>  | CC | D | TCK cycle time                | 64  | —     | —   | ns     |  |

| 2   | t <sub>MCYC</sub>  | CC | D | MCKO cycle time               | 32  | —     | —   | ns     |  |

| 3   | t <sub>MDOV</sub>  | CC | D | MCKO low to MDO data valid    | _   | —     | 8   | ns     |  |

| 4   | t <sub>MSEOV</sub> | CC | D | MCKO low to MSEO_b data valid | _   | —     | 8   | ns     |  |

| 5   | t <sub>EVTOV</sub> | CC | D | MCKO low to EVTO data valid   | _   | —     | 8   | ns     |  |

| 10  | t <sub>NTDIS</sub> | CC | D | TDI data setup time           | 15  | —     | —   | ns     |  |

|     | t <sub>NTMSS</sub> | CC | D | TMS data setup time           | 15  | —     | —   | ns     |  |

| 11  | t <sub>NTDIH</sub> | CC | D | TDI data hold time            | 5   | —     | —   | ns     |  |

|     | t <sub>NTMSH</sub> | CC | D | TMS data hold time            | 5   | —     | —   | ns     |  |

| 12  | t <sub>TDOV</sub>  | CC | D | TCK low to TDO data valid     | 35  | —     | _   | ns     |  |

| 13  | t <sub>TDOI</sub>  | CC | D | TCK low to TDO data invalid   | 6   | _     | _   | ns     |  |

| Table 48. Nexu | us characteristics |

|----------------|--------------------|

|----------------|--------------------|

## Package characteristics

|                                                                                                                                                                                                                                                        | MECHANICA                                                       | L OUTLINES     | DOCUMENT NO: 98ASS23308W |            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|--------------------------|------------|--|--|--|--|

|                                                                                                                                                                                                                                                        | DICTIONARY                                                      |                | PAGE:                    | 983        |  |  |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPORTIORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE                                                    | THIS DRAWING   | REV:                     | Н          |  |  |  |  |

| NOTES:                                                                                                                                                                                                                                                 |                                                                 |                | •                        |            |  |  |  |  |

| 1. ALL DIMENSIONS ARE IN MILL                                                                                                                                                                                                                          | IMETERS.                                                        |                |                          |            |  |  |  |  |

| 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.                                                                                                                                                                                           |                                                                 |                |                          |            |  |  |  |  |

| 3. DATUMS B, C AND D TO BE                                                                                                                                                                                                                             | $\sqrt{3}$ datums B, C and D to be determined at datum plane H. |                |                          |            |  |  |  |  |

| THE TOP PACKAGE BODY SIZ<br>BY A MAXIMUM OF 0.1 MM.                                                                                                                                                                                                    | E MAY BE SMALL                                                  | ER THAN THE BC | TTOM PA                  | CKAGE SIZE |  |  |  |  |

| 5. DIMENSIONS DO NOT INCLUDE<br>PROTRUSION IS 0.25 mm PE<br>SIZE DIMENSIONS INCLUDING                                                                                                                                                                  | ER SIDE. THE DIMI                                               |                |                          |            |  |  |  |  |

| 6. DIMENSION DOES NOT INCLUE<br>CAUSE THE LEAD WIDTH TO<br>AND AN ADJACENT LEAD SH                                                                                                                                                                     | EXCEED 0.35. MII                                                | NIMUM SPACE BE |                          |            |  |  |  |  |

| 7. dimensions are determined                                                                                                                                                                                                                           | AT THE SEATING                                                  | G PLANE, DATUM | Α.                       |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

|                                                                                                                                                                                                                                                        |                                                                 |                |                          |            |  |  |  |  |

| TITLE:                                                                                                                                                                                                                                                 |                                                                 | CASE NUMBER: S | 983-02                   |            |  |  |  |  |

| 100 LEAD LQF                                                                                                                                                                                                                                           |                                                                 | STANDARD: NON  | -JEDEC                   |            |  |  |  |  |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                    | 1.4 INICK                                                       | PACKAGE CODE:  | 8264                     | SHEET: 3   |  |  |  |  |

## Figure 40. 100 LQFP package mechanical drawing (3 of 3)

MPC5604B/C Microcontroller Data Sheet, Rev. 11

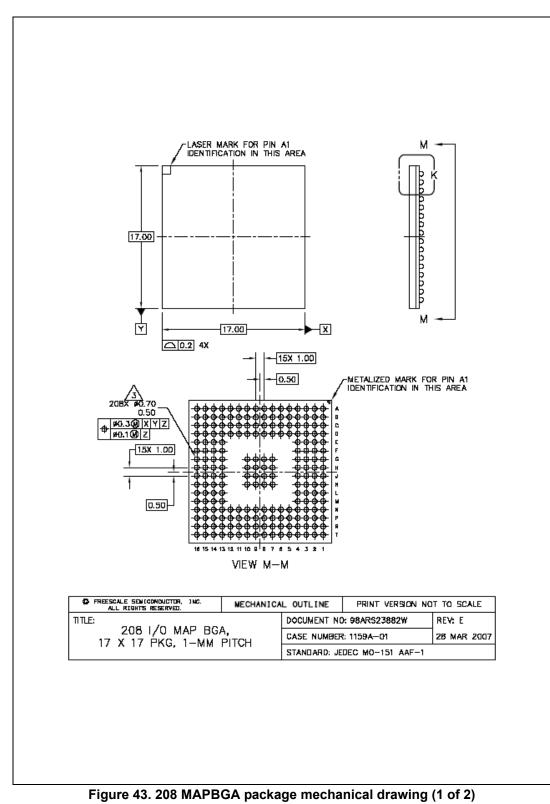

## 4.1.4 208 MAPBGA

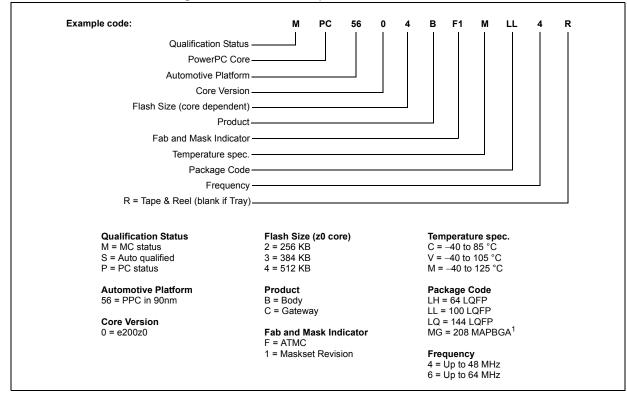

## 5 Ordering information

Figure 45. Commercial product code structure

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

# 6 Document revision history

Table 50 summarizes revisions to this document.

Table 50. Revision history

| Revision | Date        | Description of Changes |

|----------|-------------|------------------------|

| 1        | 04-Apr-2008 | Initial release.       |

## **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 06-Mar-2009 | Made minor editing and formatting changes to improve readability           Harmonized oscillator naming throughout document           Features:           —Replaced 32 KB with 48 KB as max SRAM size           —Updated description of INTC           —Changed max number of GPIO pins from 121 to 123           Updated Section 1.2, Description           Updated Table 2           Added Section 2, Block diagram           Section 3, Package pinouts and signal descriptions: Removed signal descriptions (these are found in the device reference manual)           Updated Figure 5:           —Replaced VPP with VSS_HV on pin 18           —Added MA[1] as AF3 for PC[3] (pin 116)           —Changed description for pin 120 to PH[10] / GPIO[122] / TMS           —Added MA[0] as AF2 for PC[3] (pin 116)           —Changed description for pin 120 to PH[9] / GPIO[121] / TCK           —Replaced VPP with VSS_HV on pin 14           —Added MA[1] as AF3 for PC[3] (pin 77)           —Changed description for pin 81 to PH[10] / GPIO[122] / TMS           —Added MA[1] as AF3 for PC[3] (pin 77)           —Changed description for pin 81 to PH[9] / GPIO[121] / TCK           —Replaced NMI[0] with NMI on pin 7           Updated Figure 6:           —Changed description for ball 85 from TCK to PH[9]           —Changed description for ball 89 from TMS to PH[10]           —Updated Gescription for |

## Table 50. Revision history (continued)

## **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|