# E·XFL

#### NXP USA Inc. - SPC5604BK0CLL6 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 64MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bk0cll6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ω

### Table 1. MPC5604B/C device comparison<sup>1</sup>

Introduction

|                                       |                  |                       |                  |                  |                  |                  |                   | De               | evice            |                  |                  |                  |                  |                  |                  | I                          |  |  |  |  |  |

|---------------------------------------|------------------|-----------------------|------------------|------------------|------------------|------------------|-------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|----------------------------|--|--|--|--|--|

| Feature                               |                  |                       |                  | MPC56<br>02CxLH  |                  |                  |                   |                  |                  |                  |                  |                  |                  |                  |                  | MPC5604<br>BxMG            |  |  |  |  |  |

| CPU                                   |                  |                       |                  |                  |                  |                  |                   | e20              | 00z0h            |                  |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| Execution<br>speed <sup>2</sup>       |                  | Static – up to 64 MHz |                  |                  |                  |                  |                   |                  |                  |                  |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| Code Flash                            |                  |                       | 256 KB           |                  |                  |                  |                   | 384 KB           |                  |                  |                  |                  | 51               | 2 KB             |                  |                            |  |  |  |  |  |

| Data Flash                            |                  |                       |                  |                  |                  |                  |                   | 64 KB (          | 4 × 16 KE        | 3)               |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| RAM                                   | 24 KB 32 KB      |                       |                  |                  |                  |                  | 28 KB 40 KB 32 KB |                  |                  |                  |                  | 48 KB            |                  |                  |                  |                            |  |  |  |  |  |

| MPU                                   |                  |                       |                  |                  |                  |                  |                   | 8-               | entry            |                  |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| ADC (10-bit)                          | 12 ch            | 28 ch                 | 36 ch            | 8 ch             | 28 ch            | 12 ch            | 28 ch             | 36 ch            | 8 ch             | 28 ch            | 12 ch            | 28 ch            | 36 ch            | 8 ch             | 28 ch            | 36 ch                      |  |  |  |  |  |

| CTU                                   |                  |                       |                  | 1                |                  |                  |                   | ```              | Yes              |                  |                  |                  |                  |                  |                  | 1                          |  |  |  |  |  |

| Total timer<br>I/O <sup>3</sup> eMIOS | 12 ch,<br>16-bit | 28 ch,<br>16-bit      | 56 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit  | 56 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 56 ch,<br>16-bit           |  |  |  |  |  |

| • PWM+MC<br>+ IC/OC <sup>4</sup>      | 2 ch             | 5 ch                  | 10 ch            | 2 ch             | 5 ch             | 2 ch             | 5 ch              | 10 ch            | 2 ch             | 5 ch             | 2 ch             | 5 ch             | 10 ch            | 2 ch             | 5 ch             | 10 ch                      |  |  |  |  |  |

| • PWM +<br>IC/OC <sup>4</sup>         | 10 ch            | 20 ch                 | 40 ch            | 10 ch            | 20 ch            | 10 ch            | 20 ch             | 40 ch            | 10 ch            | 20 ch            | 10 ch            | 20 ch            | 40 ch            | 10 ch            | 20 ch            | 40 ch                      |  |  |  |  |  |

| <ul> <li>IC/OC<sup>4</sup></li> </ul> | _                | 3 ch                  | 6 ch             |                  | 3 ch             | _                | 3 ch              | 6 ch             | _                | 3 ch             | _                | 3 ch             | 6 ch             | _                | 3 ch             | 6 ch                       |  |  |  |  |  |

| SCI (LINFlex)                         |                  | 3 <sup>5</sup>        |                  |                  |                  |                  |                   |                  |                  | 4                |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| SPI (DSPI)                            | 2                | :                     | 3                | 2                | 3                | 2                | :                 | 3                | 2                | 3                | 2                | 3                | 3                | 2                |                  | 3                          |  |  |  |  |  |

| CAN<br>(FlexCAN)                      |                  | 2 <sup>6</sup>        |                  | 5                | 6                |                  | 37                |                  | 5                | 6                | 37               |                  |                  | 5                |                  | 6                          |  |  |  |  |  |

| I <sup>2</sup> C                      |                  |                       |                  |                  | L                | L                |                   |                  | 1                |                  |                  |                  |                  | L                |                  |                            |  |  |  |  |  |

| 32 kHz<br>oscillator                  |                  |                       |                  |                  |                  |                  |                   | ``               | Yes              |                  |                  |                  |                  |                  |                  |                            |  |  |  |  |  |

| GPIO <sup>8</sup>                     | 45               | 79                    | 123              | 45               | 79               | 45               | 79                | 123              | 45               | 79               | 45               | 79               | 123              | 45               | 79               | 123                        |  |  |  |  |  |

| Debug                                 |                  |                       | 1                | 1                | 1                | 1                | 1                 | JTAG             | I                |                  |                  |                  |                  | 1                |                  | Nexus2+                    |  |  |  |  |  |

| Package                               | 64<br>LQFP       | 100<br>LQFP           | 144<br>LQFP      | 64<br>LQFP       | 100<br>LQFP      | 64<br>LQFP       | 100<br>LQFP       | 144<br>LQFP      | 64<br>LQFP       | 100<br>LQFP      | 64<br>LQFP       | 100<br>LQFP      | 144<br>LQFP      | 64<br>LQFP       | 100<br>LQFP      | 208<br>MAPBGA <sup>S</sup> |  |  |  |  |  |

MPC5604B/C Microcontroller Data Sheet, Rev. 11

Freescale Semiconductor

#### Table 2. MPC5604B/C device comparison<sup>1</sup>

|                                       |                     |                  |                  |                     |                  | Device              |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

|---------------------------------------|---------------------|------------------|------------------|---------------------|------------------|---------------------|------------------|------------------|---------------------|------------------|-----------------------|--|--|--|--|--|--|--|--|

| Feature                               | SPC560B<br>40L1     | SPC560B<br>40L3  | SPC560B<br>40L5  | SPC560C<br>40L1     | SPC560C<br>40L3  | SPC560B<br>50L1     | SPC560B<br>50L3  | SPC560B<br>50L5  | SPC560C<br>50L1     | SPC560C<br>50L3  | SPC560B<br>50B2       |  |  |  |  |  |  |  |  |

| CPU                                   |                     |                  |                  |                     |                  | e200z0h             |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| Execution speed <sup>2</sup>          |                     |                  |                  |                     | Stat             | tic – up to 64      | MHz              |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| Code Flash                            |                     |                  | 256 KB           |                     |                  |                     |                  | 512              | 2 KB                |                  |                       |  |  |  |  |  |  |  |  |

| Data Flash                            |                     |                  |                  |                     | 64               | KB (4 × 16          | KB)              |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| RAM                                   |                     | 24 KB            |                  | 32                  | KB               |                     | 32 KB            |                  |                     | 48 KB            |                       |  |  |  |  |  |  |  |  |

| MPU                                   |                     |                  |                  | I                   |                  | 8-entry             |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| ADC (10-bit)                          | 12 ch               | 28 ch            | 36 ch            | 8 ch                | 28 ch            | 12 ch               | 28 ch            | 36 ch            | 8 ch                | 28 ch            | 36 ch                 |  |  |  |  |  |  |  |  |

| СТИ                                   |                     | I                | I                | I                   |                  | Yes                 |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| Total timer I/O <sup>3</sup><br>eMIOS | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 56 ch,<br>16-bit      |  |  |  |  |  |  |  |  |

| • PWM + MC +<br>IC/OC <sup>4</sup>    | 2 ch                | 5 ch             | 10 ch            | 2 ch                | 5 ch             | 2 ch                | 5 ch             | 10 ch            | 2 ch                | 5 ch             | 10 ch                 |  |  |  |  |  |  |  |  |

| • PWM + IC/OC <sup>4</sup>            | 10 ch               | 20 ch            | 40 ch            | 10 ch               | 20 ch            | 10 ch               | 20 ch            | 40 ch            | 10 ch               | 20 ch            | 40 ch                 |  |  |  |  |  |  |  |  |

| • IC/OC <sup>4</sup>                  | _                   | 3 ch             | 6 ch             | _                   | 3 ch             | —                   | 3 ch             | 6 ch             | _                   | 3 ch             | 6 ch                  |  |  |  |  |  |  |  |  |

| SCI (LINFlex)                         |                     | 3 <sup>5</sup>   |                  |                     |                  |                     |                  | 4                |                     |                  |                       |  |  |  |  |  |  |  |  |

| SPI (DSPI)                            | 2                   | :                | 3                | 2                   | 3                | 2                   | :                | 3                | 2                   |                  | 3                     |  |  |  |  |  |  |  |  |

| CAN (FlexCAN)                         |                     | 2 <sup>6</sup>   |                  | 5                   | 6                |                     | 3 <sup>7</sup>   |                  | 5                   |                  | 6                     |  |  |  |  |  |  |  |  |

| l <sup>2</sup> C                      |                     |                  |                  |                     |                  | 1                   |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| 32 kHz oscillator                     |                     |                  |                  |                     |                  | Yes                 |                  |                  |                     |                  |                       |  |  |  |  |  |  |  |  |

| GPIO <sup>8</sup>                     | 45                  | 79               | 123              | 45                  | 79               | 45                  | 79               | 123              | 45                  | 79               | 123                   |  |  |  |  |  |  |  |  |

| Debug                                 |                     | <u>l</u>         | 1                | 1                   | JT               | AG                  | 1                | 1                | 1                   | 1                | Nexus2+               |  |  |  |  |  |  |  |  |

| Package                               | LQFP64 <sup>9</sup> | LQFP100          | LQFP144          | LQFP64 <sup>9</sup> | LQFP100          | LQFP64 <sup>9</sup> | LQFP100          | LQFP144          | LQFP64 <sup>9</sup> | LQFP100          | LBGA208 <sup>10</sup> |  |  |  |  |  |  |  |  |

<sup>1</sup> Feature set dependent on selected peripheral multiplexing—table shows example implementation

<sup>2</sup> Based on 125 °C ambient operating temperature

<sup>3</sup> See the eMIOS section of the device reference manual for information on the channel configuration and functions.

<sup>4</sup> IC – Input Capture; OC – Output Compare; PWM – Pulse Width Modulation; MC – Modulus counter

<sup>5</sup> SCI0, SCI1 and SCI2 are available. SCI3 is not available.

Freescale Semiconductor

MPC5604B/C Microcontroller Data Sheet, Rev. 11

Introduction

#### Block diagram

Table 3 summarizes the functions of all blocks present in the MPC5604B/C series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                                         | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-locked loop (FMPLL)                 | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock                      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                               | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)                           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Power control unit (MC_PCU)                                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)                           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

Table 3. MPC5604B/C series block summary

### 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Three dedicated VDD\_LV/VSS\_LV supply pairs are used for 1.2 V regulator stabilization.

|            |                                                                                                                                      |                      | Pin nu                | umber                  |                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------------|---------------------------------------------------------------------------------------|

| Port pin   | Function                                                                                                                             | 64 LQFP <sup>1</sup> | 100 LQFP              | 144 LQFP               | 208<br>MAPBGA <sup>2</sup>                                                            |

| VDD_HV     | Digital supply voltage                                                                                                               | 7, 28, 56            | 15, 37, 70, 84        | 19, 51, 100,<br>123    | C2, D9, E16,<br>G13, H3, N9,<br>R5                                                    |

| VSS_HV     | Digital ground                                                                                                                       | 6, 8, 26, 55         | 14, 16, 35,<br>69, 83 | 18, 20, 49,<br>99, 122 | G7, G8, G9,<br>G10, H1, H7,<br>H8, H9, H10,<br>J7, J8, J9,<br>J10, K7, K8,<br>K9, K10 |

| VDD_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS_LV}$ pin. <sup>3</sup>        | 11, 23, 57           | 19, 32, 85            | 23, 46, 124            | D8, K4, P7                                                                            |

| VSS_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV</sub> pin. <sup>3</sup> | 10, 24, 58           | 18, 33, 86            | 22, 47, 125            | C8, J2, N7                                                                            |

| VDD_BV     | Internal regulator supply voltage                                                                                                    | 12                   | 20                    | 24                     | K3                                                                                    |

| VSS_HV_ADC | Reference ground and analog ground for the ADC                                                                                       | 33                   | 51                    | 73                     | R15                                                                                   |

| VDD_HV_ADC | Reference voltage and analog supply for the ADC                                                                                      | 34                   | 52                    | 74                     | P14                                                                                   |

#### Table 4. Voltage supply pin descriptions

<sup>1</sup> Pin numbers apply to both the MPC560xB and MPC560xC packages.

<sup>2</sup> 208 MAPBGA available only as development package for Nexus2+

<sup>3</sup> A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet for details).

### 3.4 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^1$

$M = Medium^{1 2}$

$$F = Fast^{1/2}$$

I = Input only with analog feature<sup>1</sup>

J = Input/Output ('S' pad) with analog feature

X = Oscillator

<sup>1.</sup> See the I/O pad electrical characteristics in the device datasheet for details.

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium (see PCR.SRC in section Pad Configuration Registers (PCR0–PCR122) in the device reference manual).

## 3.5 System pins

The system pins are listed in Table 5.

|            |                                                                                                                                                                                           |               |          | ation                                       | I                    | Pin nu   | umbe     | r                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|---------------------------------------------|----------------------|----------|----------|-------------------------|

| System pin | Function                                                                                                                                                                                  | I/O direction | Pad type | RESET configuration                         | 64 LQFP <sup>1</sup> | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>2</sup> |

| RESET      | Bidirectional reset with Schmitt-Trigger characteristics and noise filter.                                                                                                                | I/O           | М        | Input, weak<br>pull-up only<br>after PHASE2 | 9                    | 17       | 21       | J1                      |

| EXTAL      | Analog output of the oscillator amplifier circuit, when the oscillator is not in bypass mode.<br>Analog input for the clock generator when the oscillator is in bypass mode. <sup>3</sup> | I/O           | х        | Tristate                                    | 27                   | 36       | 50       | N8                      |

| XTAL       | Analog input of the oscillator amplifier circuit. Needs to be grounded if oscillator is used in bypass mode. <sup>3</sup>                                                                 | Ι             | Х        | Tristate                                    | 25                   | 34       | 48       | P8                      |

| Table \$ | 5. Sy | stem | pin | descr | iptions |

|----------|-------|------|-----|-------|---------|

|----------|-------|------|-----|-------|---------|

<sup>1</sup> Pin numbers apply to both the MPC560xB and MPC560xC packages.

<sup>2</sup> 208 MAPBGA available only as development package for Nexus2+

<sup>3</sup> See the relevant section of the datasheet

### 3.6 Functional ports

The functional port pins are listed in Table 6.

|          |        | +                               |                                                                         |                                      |                            |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|--------|---------------------------------|-------------------------------------------------------------------------|--------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR    | Alternate function <sup>1</sup> | Function                                                                | Peripheral                           | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PA[0]    | PCR[0] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>—<br>WKPU[19] <sup>4</sup>              | SIUL<br>eMIOS_0<br>CGL<br>—<br>WKPU  | /O<br> /O<br>              | Μ        | Tristate            | 5                | 5                | 12       | 16       | G4                      |

| PA[1]    | PCR[1] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[1]<br>E0UC[1]<br>—<br><br>NMI <sup>5</sup><br>WKPU[2] <sup>4</sup> | SIUL<br>eMIOS_0<br>—<br>WKPU<br>WKPU | /O<br> /O<br><br> <br>     | S        | Tristate            | 4                | 4                | 7        | 11       | F3                      |

|          |         | -                               |                                    |                            |                            |          | uo                  |                  | Pir              | num      | ber      |                         |

|----------|---------|---------------------------------|------------------------------------|----------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup> | Function                           | Peripheral                 | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[49]<br>—<br>—<br>GPI[5]       | SIUL<br>—<br>—<br>ADC      | <br> -<br> <br>            | Ι        | Tristate            | _                | _                | 42       | 64       | T12                     |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[50]<br> -<br> -<br>GPI[6]     | SIUL<br>—<br>—<br>ADC      | <br> -<br> <br>            | -        | Tristate            | _                | _                | 43       | 65       | R12                     |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPI0[51]<br>—<br>—<br>GPI[7]       | SIUL<br>—<br>—<br>ADC      | <br> <br> <br>             | Ι        | Tristate            |                  |                  | 44       | 66       | P13                     |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPI0[52]<br>—<br>—<br>—<br>GPI[8]  | SIUL<br>—<br>—<br>ADC      | <br> -<br> -<br>           | I        | Tristate            | _                | _                | 45       | 67       | R13                     |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[53]<br>—<br>—<br>—<br>GPI[9]  | SIUL<br>—<br>—<br>ADC      | <br> -<br> <br>            | Ι        | Tristate            | _                | _                | 46       | 68       | T13                     |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[54]<br><br><br><br>GPI[10]    | SIUL<br>—<br>—<br>—<br>ADC | <br> -<br> -<br>           | I        | Tristate            | _                | _                | 47       | 69       | T14                     |

| PD[7]    | PCR[55] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[55]<br>—<br>—<br>—<br>GPI[11] | SIUL<br>—<br>—<br>—<br>ADC | <br> -<br> -<br>           | I        | Tristate            | _                | _                | 48       | 70       | R14                     |

| PD[8]    | PCR[56] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[56]<br>—<br>—<br>—<br>GPI[12] | SIUL<br>—<br>—<br>ADC      | <br> -<br> <br>            | Ι        | Tristate            |                  |                  | 49       | 71       | T15                     |

#### Table 6. Functional port pin descriptions (continued)

|          |         | -                                  |                                                                  |                                                  |                                   |          | Ľ                   |                  | Pin              | num      | ber      |                         |

|----------|---------|------------------------------------|------------------------------------------------------------------|--------------------------------------------------|-----------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                         | Peripheral                                       | I/O direction <sup>2</sup>        | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PF[10]   | PCR[90] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[90]<br>—<br>—<br>—                                          | SIUL<br>—<br>—<br>—                              | I/O<br>                           | М        | Tristate            | _                |                  |          | 38       | R3                      |

| PF[11]   | PCR[91] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[91]<br>—<br>—<br>—<br>WKPU[15] <sup>4</sup>                 | SIUL<br>—<br>—<br>—<br>WKPU                      | I/O<br> -<br> <br>                | S        | Tristate            | _                | _                | _        | 39       | R4                      |

| PF[12]   | PCR[92] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[92]<br>E1UC[25]<br>—<br>—                                   | SIUL<br>eMIOS_1<br>                              | I/O<br>I/O<br>                    | М        | Tristate            | —                |                  |          | 35       | R1                      |

| PF[13]   | PCR[93] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[93]<br>E1UC[26]<br>—<br>WKPU[16] <sup>4</sup>               | SIUL<br>eMIOS_1<br><br>WKPU                      | I/O<br>I/O<br>                    | S        | Tristate            | _                | _                | _        | 41       | T6                      |

| PF[14]   | PCR[94] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[94]<br>CAN4TX <sup>11</sup><br>E1UC[27]<br>CAN1TX           | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_4        | I/O<br>O<br>I/O<br>O              | М        | Tristate            | _                | 43               |          | 102      | D14                     |

| PF[15]   | PCR[95] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[95]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[13] | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | I/O<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | _                | 42               |          | 101      | E15                     |

| PG[0]    | PCR[96] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[96]<br>CAN5TX <sup>11</sup><br>E1UC[23]<br>—                | SIUL<br>FlexCAN_5<br>eMIOS_1<br>—                | I/O<br>O<br>I/O                   | М        | Tristate            | —                | 41               |          | 98       | E14                     |

| PG[1]    | PCR[97] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[97]<br><br>                                                 | SIUL<br>—<br>eMIOS_1<br>—<br>FlexCAN_5<br>SIUL   | I/O<br><br><br><br>               | S        | Tristate            | _                | 40               |          | 97       | E13                     |

#### Table 6. Functional port pin descriptions (continued)

|          |          | 1                               |                                    |                                |                            |          | u.                  |                  | Pin              | num      | ber      |                         |

|----------|----------|---------------------------------|------------------------------------|--------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR      | Alternate function <sup>1</sup> | Function                           | Peripheral                     | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PG[11]   | PCR[107] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[107]<br>E0UC[25]<br>—<br>—    | SIUL<br>eMIOS_0<br>—           | I/O<br>I/O<br>—            | М        | Tristate            |                  |                  |          | 115      | B12                     |

| PG[12]   | PCR[108] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[108]<br>E0UC[26]<br>—<br>—    | SIUL<br>eMIOS_0<br>—           | I/O<br>I/O<br>—            | М        | Tristate            |                  |                  |          | 92       | K14                     |

| PG[13]   | PCR[109] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[109]<br>E0UC[27]<br>—         | SIUL<br>eMIOS_0<br>—           | I/O<br>I/O<br>—            | М        | Tristate            |                  |                  |          | 91       | K16                     |

| PG[14]   | PCR[110] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[110]<br>E1UC[0]<br>—<br>—     | SIUL<br>eMIOS_1<br>—           | I/O<br>I/O<br>—            | S        | Tristate            |                  |                  |          | 110      | B14                     |

| PG[15]   | PCR[111] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[111]<br>E1UC[1]<br>—<br>—     | SIUL<br>eMIOS_1<br>—           | I/O<br>I/O<br>—            | М        | Tristate            |                  |                  |          | 111      | B13                     |

| PH[0]    | PCR[112] | AF0<br>AF1<br>AF2<br>AF3        | GPI0[112]<br>E1UC[2]<br>—<br>SIN1  | SIUL<br>eMIOS_1<br><br>DSPI_1  | /O<br> /O<br><br>          | Μ        | Tristate            |                  | _                |          | 93       | F13                     |

| PH[1]    | PCR[113] | AF0<br>AF1<br>AF2<br>AF3        | GPI0[113]<br>E1UC[3]<br>SOUT1<br>— | SIUL<br>eMIOS_1<br>DSPI_1<br>— | I/O<br>I/O<br>O            | М        | Tristate            |                  |                  |          | 94       | F14                     |

| PH[2]    | PCR[114] | AF0<br>AF1<br>AF2<br>AF3        | GPI0[114]<br>E1UC[4]<br>SCK_1<br>— | SIUL<br>eMIOS_1<br>DSPI_1<br>— | I/O<br>I/O<br>I/O<br>—     | М        | Tristate            | _                | _                |          | 95       | F16                     |

| PH[3]    | PCR[115] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[115]<br>E1UC[5]<br>CS0_1<br>— | SIUL<br>eMIOS_1<br>DSPI_1<br>— | I/O<br>I/O<br>I/O<br>—     | Μ        | Tristate            |                  |                  |          | 96       | F15                     |

#### Table 6. Functional port pin descriptions (continued)

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid applying any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

### 3.10 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 8 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 8. Parameter classifications

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

### 3.11 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

For a detailed description of the NVUSRO register, please refer to the device reference manual.

### 3.11.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 9 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

#### Table 9. PAD3V5V field description

#### MPC5604B/C Microcontroller Data Sheet, Rev. 11

$^2~$  CL includes device and package capacitances (C\_{PKG} < 5 pF).

### 3.15.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 22.

| Package                 | Supply segment |                 |                 |               |      |           |  |  |  |

|-------------------------|----------------|-----------------|-----------------|---------------|------|-----------|--|--|--|

| T ackage                | 1              | 2               | 3               | 4             | 5    | 6         |  |  |  |

| 208 MAPBGA <sup>1</sup> | Equivale       | ent to 144 LQFP | segment pad dis | tribution     | МСКО | MDOn/MSEO |  |  |  |

| 144 LQFP                | pin20–pin49    | pin51–pin99     | pin100-pin122   | pin 123-pin19 | _    | —         |  |  |  |

| 100 LQFP                | pin16–pin35    | pin37–pin69     | pin70–pin83     | pin 84–pin15  | _    | —         |  |  |  |

| 64 LQFP                 | pin8–pin26     | pin28–pin55     | pin56–pin7      | _             | _    | —         |  |  |  |

Table 22. I/O supply segment

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

Table 23 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{AVGSEG}$  maximum value.

| Symbo                            | ı  | С | Parameter                                       | Condi                          | tions <sup>1</sup>                            |     | Value |     | Unit |

|----------------------------------|----|---|-------------------------------------------------|--------------------------------|-----------------------------------------------|-----|-------|-----|------|

| Symbo                            | 1  | U | Farameter                                       | Cond                           |                                               | Min | Тур   | Мах | Onic |

| I <sub>SWTSLW</sub> ,2           | СС | D | Dynamic I/O current for<br>SLOW configuration   | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     |       | 20  | mA   |

|                                  |    |   |                                                 |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _     | 16  |      |

| I <sub>SWTMED</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>MEDIUM configuration | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | _     | 29  | mA   |

|                                  |    |   |                                                 |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | —     | 17  |      |

| I <sub>SWTFST</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>FAST configuration   | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | —     | 110 | mA   |

|                                  |    |   |                                                 |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | —     | 50  |      |

| I <sub>RMSSLW</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   | _   |       | 2.3 | mA   |

|                                  |    |   | current for SLOW<br>configuration               | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 0                                   | _   | —     | 3.2 |      |

|                                  |    |   | -                                               | C <sub>L</sub> = 100 pF, 2 MHz |                                               | _   | _     | 6.6 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     | —     | 1.6 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 1                                   | _   |       | 2.3 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz |                                               | _   |       | 4.7 |      |

#### Table 23. I/O consumption

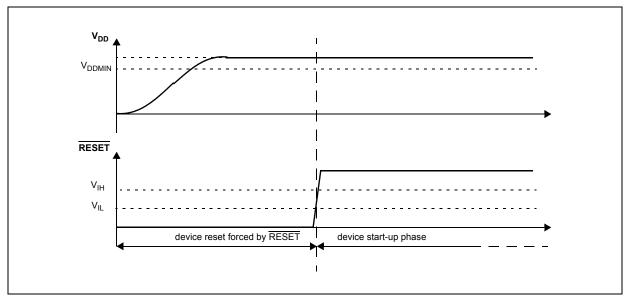

Figure 8. Start-up reset requirements

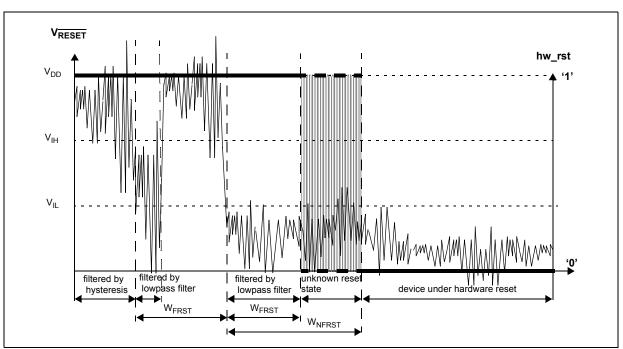

Figure 9. Noise filtering on reset signal

Table 25. Reset electrical characteristics

| Symb            | ol | C Parameter Conditions <sup>1</sup> |                                            | Conditions <sup>1</sup> |                     |         | Unit                 |   |  |

|-----------------|----|-------------------------------------|--------------------------------------------|-------------------------|---------------------|---------|----------------------|---|--|

| Cynio           | 01 | Ŭ                                   | i didinotor                                | Conditione              | Min                 | Typ Max |                      |   |  |

| V <sub>IH</sub> | SR |                                     | Input High Level CMOS<br>(Schmitt Trigger) | _                       | 0.65V <sub>DD</sub> |         | V <sub>DD</sub> +0.4 | V |  |

| Symbol                |    | с | Parameter                        | Conditions <sup>1</sup>     |                         |     | Value |                  | Unit |

|-----------------------|----|---|----------------------------------|-----------------------------|-------------------------|-----|-------|------------------|------|

| Symbol                |    | C | Falameter                        | Conditions                  |                         | Min | Тур   | Мах              | Unit |

| I <sub>DDMAX</sub> 2  | СС | D | RUN mode maximum average current | _                           |                         | _   | 115   | 140 <sup>3</sup> | mA   |

| I <sub>DDRUN</sub> 4  | СС | Т | RUN mode typical                 | f <sub>CPU</sub> = 8 MHz    |                         | _   | 7     | _                | mA   |

|                       |    | Т | average current <sup>5</sup>     | f <sub>CPU</sub> = 16 MHz   |                         | —   | 18    | _                | -    |

|                       |    | Т |                                  | f <sub>CPU</sub> = 32 MHz   |                         |     | 29    |                  |      |

|                       |    | Ρ |                                  | f <sub>CPU</sub> = 48 MHz   |                         | _   | 40    | 100              |      |

|                       |    | Ρ |                                  | f <sub>CPU</sub> = 64 MHz   |                         | _   | 51    | 125              |      |

| I <sub>DDHALT</sub>   | СС | С | HALT mode current <sup>6</sup>   | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 8     | 15               | mA   |

|                       |    | Ρ |                                  | (128 kHz) running           | T <sub>A</sub> = 125 °C | _   | 14    | 25               |      |

| IDDSTOP               | СС | Ρ | STOP mode current <sup>7</sup>   | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 180   | 700 <sup>8</sup> | μA   |

|                       |    | D |                                  |                             | T <sub>A</sub> = 55 °C  | _   | 500   | _                |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | _   | 1     | 6 <sup>8</sup>   | mA   |

|                       |    | D |                                  |                             | T <sub>A</sub> = 105 °C | _   | 2     | 9 <sup>8</sup>   |      |

|                       |    | Ρ |                                  |                             | T <sub>A</sub> = 125 °C | -   | 4.5   | 12 <sup>8</sup>  |      |

| I <sub>DDSTDBY2</sub> | СС | Ρ |                                  | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 30    | 100              | μA   |

|                       |    | D | current <sup>9</sup>             | (128 kHz) running           | T <sub>A</sub> = 55 °C  |     | 75    |                  |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | -   | 180   | 700              |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 105 °C | _   | 315   | 1000             |      |

|                       |    | Ρ |                                  |                             | T <sub>A</sub> = 125 °C |     | 560   | 1700             |      |

| I <sub>DDSTDBY1</sub> | СС | Т |                                  | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | -   | 20    | 60               | μA   |

|                       |    | D | current <sup>10</sup>            | (128 kHz) running           | T <sub>A</sub> = 55 °C  | -   | 45    |                  |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | _   | 100   | 350              |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 105 °C | _   | 165   | 500              |      |

|                       |    | D |                                  |                             | T <sub>A</sub> = 125 °C |     | 280   | 900              |      |

| Table 28. Power consumption on VDD_BV and VDD_HV |

|--------------------------------------------------|

|--------------------------------------------------|

$\frac{1}{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> I<sub>DDMAX</sub> is drawn only from the V<sub>DD\_BV</sub> pin. Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

<sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in rush current on Table 26.

- <sup>4</sup> I<sub>DDRUN</sub> is drawn only from the V<sub>DD\_BV</sub> pin. RUN current measured with typical application with accesses on both flash and RAM.

- <sup>5</sup> Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

| Symbo     | Symbol C |   | Parameter                                                                   | Conditions                               |         | Value   |     | Unit   |

|-----------|----------|---|-----------------------------------------------------------------------------|------------------------------------------|---------|---------|-----|--------|

| Gymbo     |          |   | r arameter                                                                  | Conditions                               | Min     | Тур     | Max | Ome    |

| P/E       | CC       | С | Number of program/erase cycles                                              | 16 KB blocks                             | 100,000 | —       | _   | cycles |

|           |          |   | per block over the operating temperature range (T <sub>1</sub> )            | 32 KB blocks                             | 10,000  | 100,000 | —   |        |

|           |          |   |                                                                             | 128 KB blocks                            | 1,000   | 100,000 | _   |        |

| Retention | СС       | С | Minimum data retention at 85 °C<br>average ambient temperature <sup>1</sup> | Blocks with<br>0–1,000 P/E cycles        | 20      | —       | _   | years  |

|           |          |   |                                                                             | Blocks with<br>1,001–10,000 P/E cycles   | 10      | —       | _   |        |

|           |          |   |                                                                             | Blocks with<br>10,001–100,000 P/E cycles | 5       | —       | —   |        |

#### Table 30. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

ECC circuitry provides correction of single bit faults and is used to improve further automotive reliability results. Some units will experience single bit corrections throughout the life of the product with no impact to product reliability.

#### Table 31. Flash read access timing

| Symb              | Symbol C |   | ol C Parameter                      |               | Max | Unit |

|-------------------|----------|---|-------------------------------------|---------------|-----|------|

| f <sub>READ</sub> | CC       | Ρ | Maximum frequency for Flash reading | 2 wait states | 64  | MHz  |

|                   |          | С |                                     | 1 wait state  | 40  |      |

|                   |          | С |                                     | 0 wait states | 20  |      |

$\frac{1}{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

### 3.19.2 Flash power supply DC characteristics

Table 32 shows the power supply DC characteristics on external supply.

#### Table 32. Flash memory power supply DC electrical characteristics

| Symb                            | Symbol C Parameter |   | Paramotor                                                                                        | Conditions <sup>1</sup>                                                                                      |   |     | Unit |     |

|---------------------------------|--------------------|---|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---|-----|------|-----|

| Cynib                           |                    |   | i didineter                                                                                      |                                                                                                              |   | Тур |      | Мах |

| I <sub>FREAD</sub> <sup>2</sup> | СС                 | D | Sum of the current consumption on VDD_HV and VDD_BV on read access                               | Code flash memory module read<br>f <sub>CPU</sub> = 64 MHz <sup>3</sup>                                      | _ | 15  | 33   | mA  |

|                                 |                    |   |                                                                                                  | Data flash memory module read<br>f <sub>CPU</sub> = 64 MHz <sup>3</sup>                                      | _ | 15  | 33   |     |

| I <sub>FMOD</sub> <sup>2</sup>  | СС                 | D | Sum of the current consumption on<br>VDD_HV and VDD_BV on matrix<br>modification (program/erase) | Program/Erase ongoing while<br>reading code flash memory<br>registers f <sub>CPU</sub> = 64 MHz <sup>3</sup> | — | 15  | 33   | mA  |

|                                 |                    |   |                                                                                                  | Program/Erase ongoing while<br>reading data flash memory<br>registers f <sub>CPU</sub> = 64 MHz <sup>3</sup> |   | 15  | 33   |     |

### 3.26 ADC electrical characteristics

### 3.26.1 Introduction

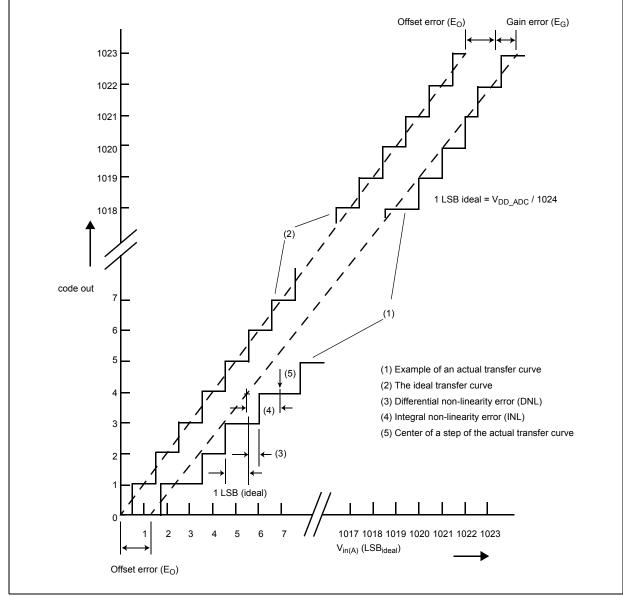

The device provides a 10-bit Successive Approximation Register (SAR) analog-to-digital converter.

Figure 19. ADC characteristic and error definitions

### 3.26.2 Input impedance and ADC accuracy

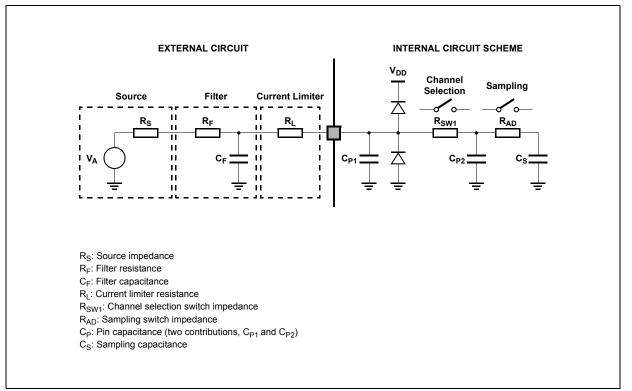

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as

MPC5604B/C Microcontroller Data Sheet, Rev. 11

possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance: being  $C_S$  and  $C_{p2}$  substantially two switched capacitances, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{p2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (f_c \times (C_S+C_{p2}))$ ), where  $f_c$  represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{p2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

Eqn. 4

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Equation 4 generates a constraint for external network design, in particular on a resistive path.

Figure 20. Input equivalent circuit (precise channels)

<sup>3</sup> During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e.,  $(41 + 5) * f_{periph}$ .

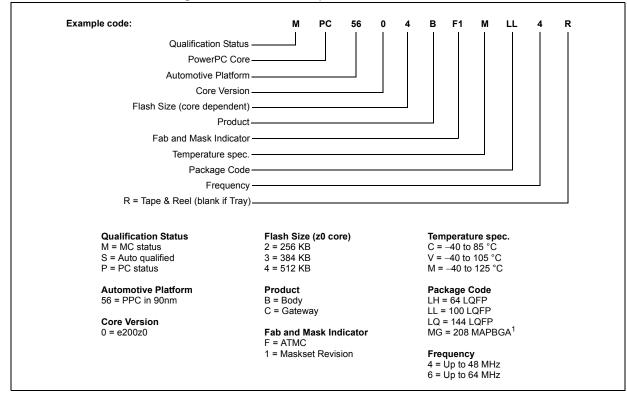

# 5 Ordering information

Figure 45. Commercial product code structure

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

# 6 Document revision history

Table 50 summarizes revisions to this document.

Table 50. Revision history

| Revision | Date        | Description of Changes |

|----------|-------------|------------------------|

| 1        | 04-Apr-2008 | Initial release.       |

#### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 06-Aug-2009 | Updated Figure 6<br>Table 12<br>• V <sub>DD_ADC</sub> : changed min value for "relative to V <sub>DD</sub> " condition<br>• V <sub>IN</sub> : changed min value for "relative to V <sub>DD</sub> " condition<br>• I <sub>CORELV</sub> : added new row<br>Table 14<br>• Ta-C-Grade Part, TJ-C-Grade Part, TA-V-Grade Part, TJ-V-Grade Part, TA-M-Grade Part, TJ-M-Grade Part:<br>added new rows<br>• Changed capacitance value in footnote<br>Table 21<br>• MEDIUM configuration: added condition for PAD3V5V = 0<br>Updated Figure 10<br>Table 26<br>• C <sub>DEC1</sub> : changed min value<br>• I <sub>MREG</sub> : changed max value<br>• I <sub>DD_BV</sub> : added max value<br>• I <sub>DD_BV</sub> : added max value<br>• V <sub>LVDHV3L</sub> : adde max value<br>• V <sub>LVDHV3L</sub> : adde max value<br>• V <sub>LVDHV3L</sub> : adde m |

#### Table 50. Revision history (continued)

#### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |