# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 64MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 45                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bk0mlh6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

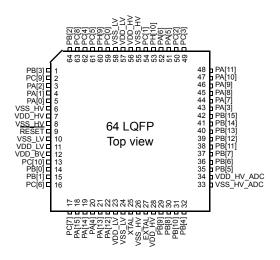

Figure 2. MPC560xB LQFP 64-pin configuration

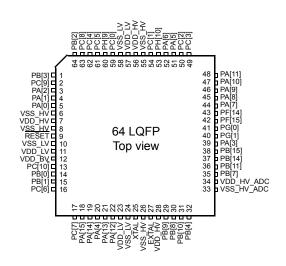

Figure 3. MPC560xC LQFP 64-pin configuration

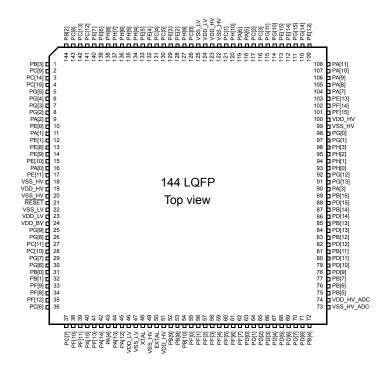

Note: Availability of port pin alternate functions depends on product selection.

|          |         | -                               |                                                           |                                       |                              |          | ų                   |                  | Pin              | n num    | ber      |                         |

|----------|---------|---------------------------------|-----------------------------------------------------------|---------------------------------------|------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup> | Function                                                  | Peripheral                            | I/O direction <sup>2</sup>   | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[10]<br>E0UC[10]<br>SDA<br>—                          | SIUL<br>eMIOS_0<br>I2C_0<br>—         | I/O<br>I/O<br>I/O            | S        | Tristate            | 47               | 47               | 74       | 107      | B16                     |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[11]<br>E0UC[11]<br>SCL<br>—                          | SIUL<br>eMIOS_0<br>I2C_0<br>—         | I/O<br>I/O<br>I/O            | S        | Tristate            | 48               | 48               | 75       | 108      | B15                     |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[12]<br>—<br>—<br>SIN_0                               | SIUL<br>—<br>—<br>—<br>DSPI0          | I/O<br>—<br>—<br>—<br>—      | S        | Tristate            | 22               | 22               | 31       | 45       | T7                      |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[13]<br>SOUT_0<br>—                                   | SIUL<br>DSPI_0<br>—<br>—              | I/O<br>O<br>                 | М        | Tristate            | 21               | 21               | 30       | 44       | R7                      |

| PA[14]   | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[14]<br>SCK_0<br>CS0_0<br>—<br>EIRQ[4]                | SIUL<br>DSPI_0<br>DSPI_0<br>—<br>SIUL | /0<br> /0<br> /0<br>         | Μ        | Tristate            | 19               | 19               | 28       | 42       | P6                      |

| PA[15]   | PCR[15] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[15]<br>CS0_0<br>SCK_0<br>—<br>WKPU[10] <sup>4</sup>  | SIUL<br>DSPI_0<br>DSPI_0<br>—<br>WKPU | /0<br> /0<br> /0<br>         | Μ        | Tristate            | 18               | 18               | 27       | 40       | R6                      |

| PB[0]    | PCR[16] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[16]<br>CAN0TX<br>—<br>—                              | SIUL<br>FlexCAN_0<br>                 | I/O<br>O<br>—                | М        | Tristate            | 14               | 14               | 23       | 31       | N3                      |

| PB[1]    | PCR[17] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[17]<br>—<br>—<br>—<br>WKPU[4] <sup>4</sup><br>CAN0RX | SIUL<br>—<br>—<br>WKPU<br>FlexCAN_0   | I/O<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | 15               | 15               | 24       | 32       | N1                      |

| PB[2]    | PCR[18] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[18]<br>LIN0TX<br>SDA<br>—                            | SIUL<br>LINFlex_0<br>I2C_0<br>—       | I/O<br>O<br>I/O<br>—         | М        | Tristate            | 64               | 64               | 100      | 144      | B2                      |

### 3.12 Absolute maximum ratings

Table 12. Absolute maximum ratings

| Symbo                | .1 | Parameter                                                                                             | Conditions                                 | Val                  | lue                  | Unit |

|----------------------|----|-------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|----------------------|------|

| Symbo                | 1  | Falameter                                                                                             | Conditions                                 | Min                  | Max                  | Unit |

| V <sub>SS</sub>      | SR | Digital ground on VSS_HV pins                                                                         | _                                          | 0                    | 0                    | V    |

| V <sub>DD</sub>      | SR | Voltage on VDD_HV pins with respect to ground ( $V_{SS}$ )                                            | _                                          | -0.3                 | 6.0                  | V    |

| V <sub>SS_LV</sub>   | SR | Voltage on VSS_LV (low voltage digital v<br>supply) pins with respect to ground<br>(V <sub>SS</sub> ) |                                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub>   | SR | Voltage on VDD_BV pin (regulator                                                                      | —                                          | -0.3                 | 6.0                  | V    |

|                      |    | supply) with respect to ground $(V_{SS})$                                                             | Relative to V <sub>DD</sub>                | -0.3                 | V <sub>DD</sub> +0.3 |      |

| V <sub>SS_ADC</sub>  | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )                   |                                            |                      | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub>  | SR | Voltage on VDD_HV_ADC pin (ADC                                                                        | _                                          | -0.3                 | 6.0                  | V    |

|                      |    | reference) with respect to ground $(V_{SS})$                                                          | Relative to V <sub>DD</sub>                | V <sub>DD</sub> -0.3 | V <sub>DD</sub> +0.3 |      |

| V <sub>IN</sub>      | SR | Voltage on any GPIO pin with respect to                                                               | _                                          | -0.3                 | 6.0                  | V    |

|                      |    | ground (V <sub>SS</sub> )                                                                             | Relative to V <sub>DD</sub>                |                      | V <sub>DD</sub> +0.3 |      |

| I <sub>INJPAD</sub>  | SR | Injected input current on any pin during overload condition                                           | _                                          | -10                  | 10                   | mA   |

| I <sub>INJSUM</sub>  | SR | Absolute sum of all injected input<br>currents during overload condition                              |                                            |                      | 50                   |      |

| I <sub>AVGSEG</sub>  | SR | Sum of all the static I/O current within a                                                            | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 |                      | 70                   | mA   |

|                      |    | supply segment                                                                                        | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 |                      | 64                   |      |

| I <sub>CORELV</sub>  | SR | Low voltage static current sink through VDD_BV                                                        | _                                          |                      | 150                  | mA   |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                                                   | —                                          | -55                  | 150                  | °C   |

### NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

| Sum             | Symbol C Para |   | Parameter Conditions <sup>1</sup>      | Conditions <sup>1</sup> |                                                                                        | Unit |     |                    |      |

|-----------------|---------------|---|----------------------------------------|-------------------------|----------------------------------------------------------------------------------------|------|-----|--------------------|------|

| Syn             |               |   | Farameter                              |                         | Conditions                                                                             | Min  | Тур | Max                | Unit |

| V <sub>OL</sub> | СС            |   | Output low level<br>FAST configuration | Push Pull               | $I_{OL}$ = 14mA,<br>$V_{DD}$ = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended)               | _    |     | 0.1V <sub>DD</sub> | V    |

|                 |               | С |                                        |                         | I <sub>OL</sub> = 7mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>      | _    | _   | 0.1V <sub>DD</sub> |      |

|                 |               | С |                                        |                         | I <sub>OL</sub> = 11mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | _    | _   | 0.5                |      |

Table 20. FAST configuration output buffer electrical characteristics (continued)

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

### 3.15.4 Output pin transition times

| e.              | Symbol |   | Parameter                                |                         | Conditions <sup>1</sup>                                |     | Value | e   | Unit |

|-----------------|--------|---|------------------------------------------|-------------------------|--------------------------------------------------------|-----|-------|-----|------|

| J               |        | C | Falameter                                |                         | Conditions                                             | Min | Тур   | Мах |      |

| t <sub>tr</sub> | CC     |   | Output transition time output            | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0             | —   | —     | 50  | ns   |

|                 |        | Т | pin <sup>2</sup><br>SLOW configuration   | C <sub>L</sub> = 50 pF  |                                                        | _   | —     | 100 |      |

|                 |        | D |                                          | C <sub>L</sub> = 100 pF |                                                        | _   |       | 125 |      |

|                 |        | D |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1             | —   | —     | 50  |      |

|                 |        | Т |                                          | C <sub>L</sub> = 50 pF  |                                                        | —   | —     | 100 |      |

|                 |        | D |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 125 |      |

| t <sub>tr</sub> | CC     | D | Output transition time output            | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ | —   | —     | 10  | ns   |

|                 |        | Т | pin <sup>2</sup><br>MEDIUM configuration | C <sub>L</sub> = 50 pF  | SIUL.PCRx.SRC = 1                                      | —   | —     | 20  |      |

|                 |        | D | 0                                        | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 40  |      |

|                 |        | D |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1             | _   |       | 12  |      |

|                 |        | Т |                                          | C <sub>L</sub> = 50 pF  | SIUL.PCRx.SRC = 1                                      | _   | —     | 25  |      |

|                 |        | D |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 40  |      |

| t <sub>tr</sub> | CC     | D | Output transition time output            | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0             | _   |       | 4   | ns   |

|                 |        |   | pin <sup>2</sup><br>FAST configuration   | C <sub>L</sub> = 50 pF  |                                                        | _   |       | 6   |      |

|                 |        |   | Ŭ                                        | $C_L = 100 \text{ pF}$  | —                                                      | —   | 12    |     |      |

|                 |        |   |                                          | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1             | —   | —     | 4   |      |

|                 |        |   |                                          | C <sub>L</sub> = 50 pF  | 1                                                      | —   | —     | 7   |      |

|                 |        |   |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 12  |      |

Table 21. Output pin transition times

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

| Cumh               | - 1 | с | Deveneter                                         | Conditions <sup>1</sup>                                                                          |                    | Value |                     | 11   |

|--------------------|-----|---|---------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------|-------|---------------------|------|

| Symbo              | 01  | C | Parameter                                         | Conditions                                                                                       | Min                | Тур   | Мах                 | Unit |

| V <sub>IL</sub>    | SR  | Ρ | Input low Level CMOS<br>(Schmitt Trigger)         | _                                                                                                | -0.4               | —     | 0.35V <sub>DD</sub> | V    |

| V <sub>HYS</sub>   | СС  | С | Input hysteresis CMOS<br>(Schmitt Trigger)        | _                                                                                                | 0.1V <sub>DD</sub> | _     | -                   | V    |

| V <sub>OL</sub>    | СС  | Ρ | Output low level                                  | Push Pull, I <sub>OL</sub> = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                  | _     | 0.1V <sub>DD</sub>  | V    |

|                    |     | С |                                                   | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>            | —                  | _     | 0.1V <sub>DD</sub>  |      |

|                    |     | С |                                                   | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)        | —                  | _     | 0.5                 |      |

| t <sub>tr</sub>    | СС  | D | Output transition time<br>output pin <sup>3</sup> | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | —                  | _     | 10                  | ns   |

|                    |     |   |                                                   | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | —                  |       | 20                  |      |

|                    |     |   |                                                   | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                            | —                  |       | 40                  |      |

|                    |     |   |                                                   | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                             | —                  | —     | 12                  |      |

|                    |     |   |                                                   | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                             | —                  | _     | 25                  |      |

|                    |     |   |                                                   | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                            | —                  | _     | 40                  |      |

| W <sub>FRST</sub>  | SR  | Ρ | RESET input filtered pulse                        | _                                                                                                | —                  | _     | 40                  | ns   |

| W <sub>NFRST</sub> | SR  | Ρ | RESET input not filtered pulse                    | _                                                                                                | _                  | -     | ns                  |      |

| I <sub>WPU</sub>   | СС  | Ρ | Weak pull-up current                              | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                                       | 10                 | _     | 150                 | μA   |

|                    |     | D | absolute value                                    | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                                                       | 10                 | _     | 150                 | ]    |

|                    |     | Ρ |                                                   | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>                                          | 10                 |       | 250                 |      |

Table 25. Reset electrical characteristics (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

<sup>2</sup> This transient configuration does not occurs when device is used in the V<sub>DD</sub> =  $3.3 \text{ V} \pm 10\%$  range.

$^3$  C<sub>L</sub> includes device and package capacitance (C<sub>PKG</sub> < 5 pF).

### 3.17 Power management electrical characteristics

### 3.17.1 Voltage regulator electrical characteristics

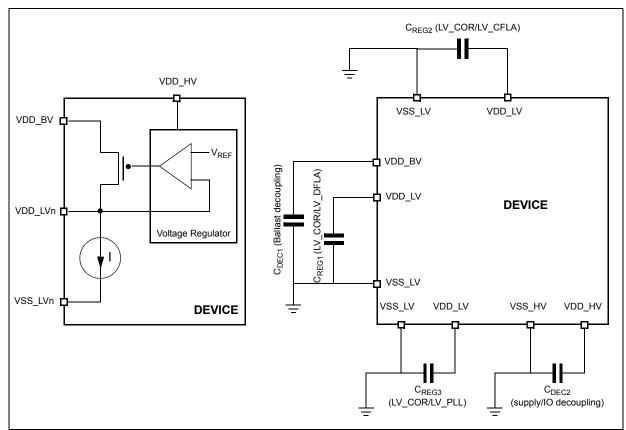

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD\_LV}$  from the high voltage ballast supply  $V_{DD\_BV}$ . The regulator itself is supplied by the common I/O supply  $V_{DD}$ . The following supplies are involved:

- HV—High voltage external power supply for voltage regulator module. This must be provided externally through VDD\_HV power pin.

- BV—High voltage external power supply for internal ballast module. This must be provided externally through VDD\_BV power pin. Voltage values should be aligned with V<sub>DD</sub>.

- LV—Low voltage internal power supply for core, FMPLL and flash digital logic. This is generated by the internal voltage regulator but provided outside to connect stability capacitor. It is further split into four main domains to ensure noise isolation between critical LV modules within the device:

- LV\_COR—Low voltage supply for the core. It is also used to provide supply for FMPLL through double bonding.

- LV\_CFLA—Low voltage supply for code flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA—Low voltage supply for data flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL-Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 10. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see Section 3.13, Recommended operating conditions).

The internal voltage regulator requires a controlled slew rate of both V<sub>DD HV</sub> and V<sub>DD BV</sub> as described in Figure 11.

| Symbol                          |    | с | Parameter                        | Conditions <sup>1</sup>     |                         |     | Unit |                  |      |

|---------------------------------|----|---|----------------------------------|-----------------------------|-------------------------|-----|------|------------------|------|

| Symbol                          |    | C | Falameter                        | Conditions                  |                         | Min | Тур  | Мах              | Unit |

| I <sub>DDMAX</sub> <sup>2</sup> | СС | D | RUN mode maximum average current | _                           |                         | _   | 115  | 140 <sup>3</sup> | mA   |

| I <sub>DDRUN</sub> 4            | СС | Т | RUN mode typical                 | f <sub>CPU</sub> = 8 MHz    |                         | _   | 7    | _                | mA   |

|                                 |    | Т | average current <sup>5</sup>     | f <sub>CPU</sub> = 16 MHz   |                         | —   | 18   | _                | -    |

|                                 |    | Т |                                  | f <sub>CPU</sub> = 32 MHz   |                         |     | 29   |                  |      |

|                                 |    | Ρ |                                  | f <sub>CPU</sub> = 48 MHz   | _                       | 40  | 100  |                  |      |

|                                 |    | Ρ |                                  | f <sub>CPU</sub> = 64 MHz   |                         | _   | 51   | 125              |      |

| I <sub>DDHALT</sub>             | СС | С | HALT mode current <sup>6</sup>   | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 8    | 15               | mA   |

|                                 |    | Ρ |                                  | (128 kHz) running           | T <sub>A</sub> = 125 °C | _   | 14   | 25               |      |

| IDDSTOP                         | СС | Ρ | STOP mode current <sup>7</sup>   | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 180  | 700 <sup>8</sup> | μA   |

|                                 |    | D |                                  | (128 kHz) running           | T <sub>A</sub> = 55 °C  | _   | 500  | _                |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | _   | 1    | 6 <sup>8</sup>   | mA   |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 105 °C | _   | 2    | 9 <sup>8</sup>   |      |

|                                 |    | Ρ |                                  |                             | T <sub>A</sub> = 125 °C | -   | 4.5  | 12 <sup>8</sup>  |      |

| I <sub>DDSTDBY2</sub>           | СС | Ρ |                                  | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 30   | 100              | μA   |

|                                 |    | D | current <sup>9</sup>             | (128 kHz) running           | T <sub>A</sub> = 55 °C  | -   | 75   |                  |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | -   | 180  | 700              |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 105 °C | -   | 315  | 1000             |      |

|                                 |    | Ρ |                                  |                             | T <sub>A</sub> = 125 °C | -   | 560  | 1700             |      |

| I <sub>DDSTDBY1</sub>           | СС | Т |                                  | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | -   | 20   | 60               | μA   |

|                                 |    | D | current <sup>10</sup>            | (128 kHz) running           | T <sub>A</sub> = 55 °C  | -   | 45   |                  |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 85 °C  | _   | 100  | 350              |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 105 °C | _   | 165  | 500              |      |

|                                 |    | D |                                  |                             | T <sub>A</sub> = 125 °C |     | 280  | 900              |      |

| Table 28. Power consumption on VDD_BV and VDD_HV |

|--------------------------------------------------|

|--------------------------------------------------|

$\frac{1}{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> I<sub>DDMAX</sub> is drawn only from the V<sub>DD\_BV</sub> pin. Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

<sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in rush current on Table 26.

- <sup>4</sup> I<sub>DDRUN</sub> is drawn only from the V<sub>DD\_BV</sub> pin. RUN current measured with typical application with accesses on both flash and RAM.

- <sup>5</sup> Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data Flash Power Down. Code Flash in Low Power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: instances: 0, 1, 2 ON (clocked but not reception or transmission), instances: 4, 5, 6 clock gated. LINFlex: instances: 0, 1, 2 ON (clocked but not reception or transmission), instance: 3 clock gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON. PIT ON. STM ON. ADC ON but not conversion except 2 analog watchdog.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPvreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPreg on, HP/LPVreg off, 32 KB RAM on, device configured for minimum consumption, all possible modules switched off.

- <sup>10</sup> ULPreg on, HP/LPVreg off, 8 KB RAM on, device configured for minimum consumption, all possible modules switched off.

### 3.19 Flash memory electrical characteristics

### 3.19.1 **Program/Erase characteristics**

Table 29 shows the program and erase characteristics.

### Table 29. Program and erase specifications

|                          |    |   |                                                 |     | Value            |                             |                  |      |  |  |

|--------------------------|----|---|-------------------------------------------------|-----|------------------|-----------------------------|------------------|------|--|--|

| Symbol                   |    | С | Parameter                                       | Min | Typ <sup>1</sup> | Initial<br>max <sup>2</sup> | Max <sup>3</sup> | Unit |  |  |

| T <sub>dwprogram</sub>   | СС | С | Double word (64 bits) program time <sup>4</sup> | _   | 22               | 50                          | 500              | μs   |  |  |

| T <sub>16Kpperase</sub>  |    |   | 16 KB block preprogram and erase time           |     | 300              | 500                         | 5000             | ms   |  |  |

| T <sub>32Kpperase</sub>  |    |   | 32 KB block preprogram and erase time           |     | 400              | 600                         | 5000             | ms   |  |  |

| T <sub>128Kpperase</sub> |    |   | 128 KB block preprogram and erase time          | _   | 800              | 1300                        | 7500             | ms   |  |  |

| T <sub>esus</sub>        | СС | D | Erase suspend latency                           | _   | —                | 30                          | 30               | μs   |  |  |

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

### 3.26 ADC electrical characteristics

### 3.26.1 Introduction

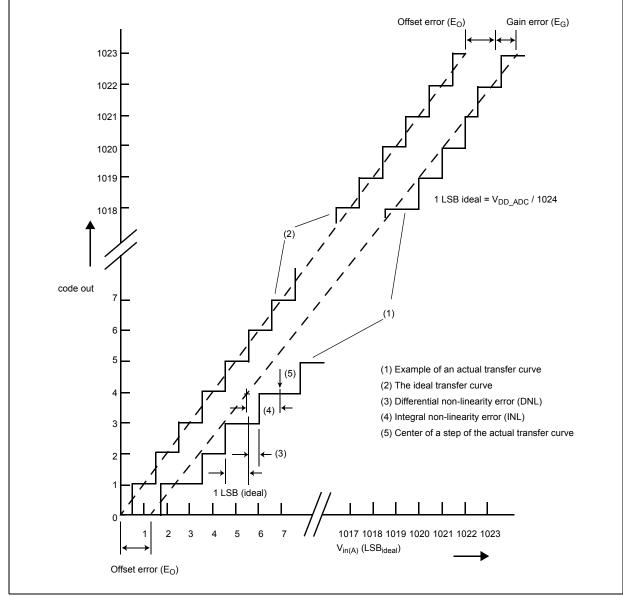

The device provides a 10-bit Successive Approximation Register (SAR) analog-to-digital converter.

Figure 19. ADC characteristic and error definitions

### 3.26.2 Input impedance and ADC accuracy

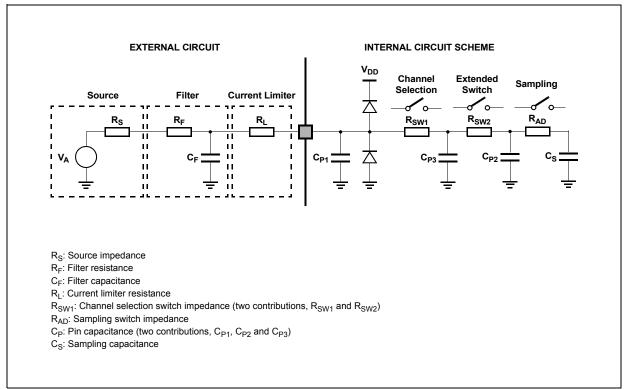

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as

Figure 21. Input equivalent circuit (extended channels)

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit in Figure 20): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

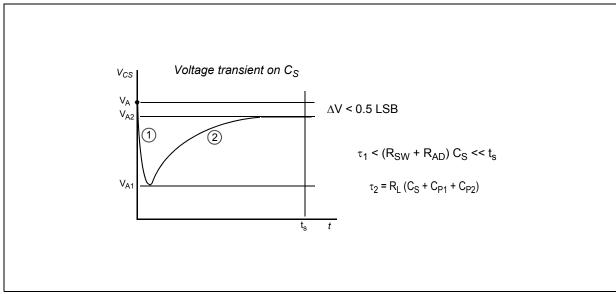

Figure 22. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

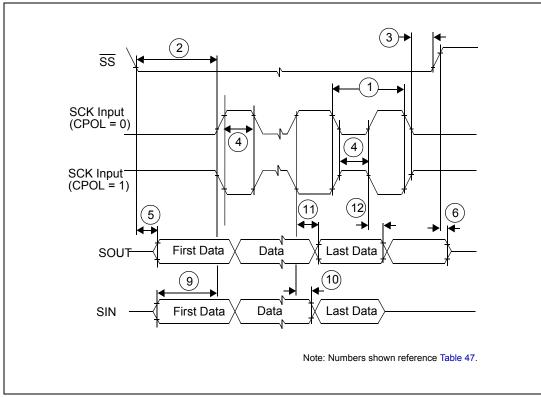

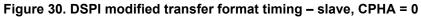

### Table 47. DSPI characteristics<sup>1</sup> (continued)

| No. | Symbo              | Symbol C |   | ol C Parameter             |             | D              | SPI0/DS | PI1 | DSPI2          |     |     |      |

|-----|--------------------|----------|---|----------------------------|-------------|----------------|---------|-----|----------------|-----|-----|------|

| NO. | Symbo              | 01       |   |                            |             | Min            | Тур     | Max | Min            | Тур | Мах | Unit |

| 10  | t <sub>HI</sub>    | SR       | D | Data hold time for inputs  | Master mode | 0              | —       | _   | 0              | —   | —   | ns   |

|     |                    |          |   |                            | Slave mode  | 2 <sup>6</sup> | —       | _   | 2 <sup>6</sup> | —   | _   |      |

| 11  | t <sub>SUO</sub> 7 | СС       | D | Data valid after SCK edge  | Master mode | _              | —       | 32  | _              | —   | 50  | ns   |

|     |                    |          |   |                            | Slave mode  | _              | _       | 52  | _              | —   | 160 | 1    |

| 12  | t <sub>HO</sub> 7  | СС       | D | Data hold time for outputs | Master mode | 0              | —       | _   | 0              | _   | _   | ns   |

|     |                    |          |   |                            | Slave mode  | 8              | —       | _   | 13             |     | _   | 1    |

Operating conditions:  $C_L$  = 10 to 50 pF, Slew<sub>IN</sub> = 3.5 to 15 ns.

<sup>2</sup> Maximum value is reached when CSn pad is configured as SLOW pad while SCK pad is configured as MEDIUM. A positive value means that SCK starts before CSn is asserted. DSPI2 has only SLOW SCK available.

<sup>3</sup> Maximum value is reached when CSn pad is configured as MEDIUM pad while SCK pad is configured as SLOW. A positive value means that CSn is deasserted before SCK. DSPI0 and DSPI1 have only MEDIUM SCK available.

<sup>4</sup> The t<sub>CSC</sub> delay value is configurable through a register. When configuring t<sub>CSC</sub> (using PCSSCK and CSSCK fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than ∆t<sub>CSC</sub> to ensure positive t<sub>CSCext</sub>.

<sup>5</sup> The t<sub>ASC</sub> delay value is configurable through a register. When configuring t<sub>ASC</sub> (using PASC and ASC fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than ∆t<sub>ASC</sub> to ensure positive t<sub>ASCext</sub>.

<sup>6</sup> This delay value corresponds to SMPL\_PT = 00b which is bit field 9 and 8 of the DSPI\_MCR.

<sup>7</sup> SCK and SOUT configured as MEDIUM pad

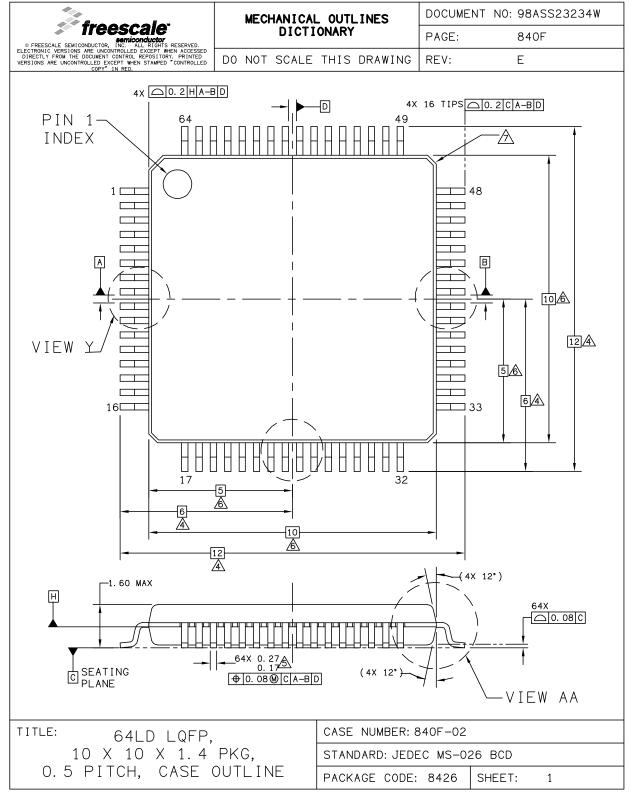

### 4.1.1 64 LQFP

Figure 35. 64 LQFP package mechanical drawing (1 of 3)

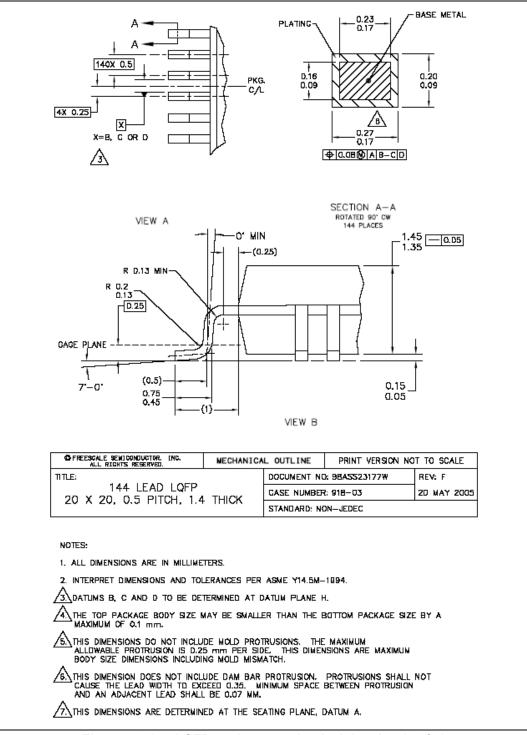

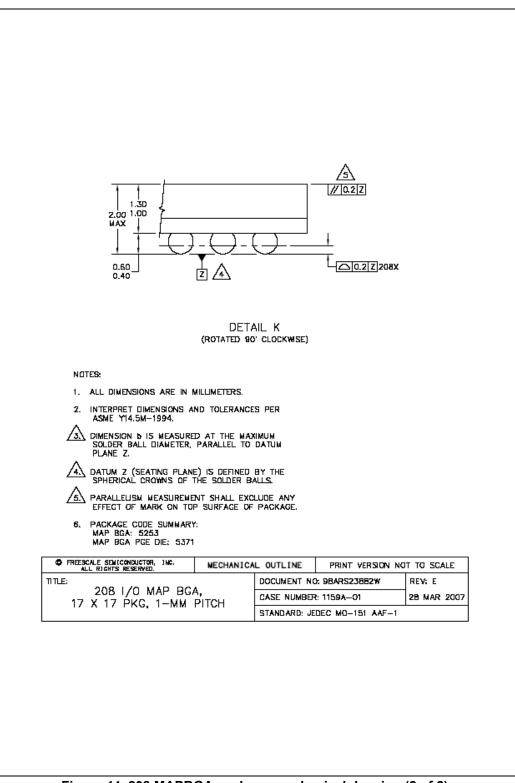

Package characteristics

Figure 44. 208 MAPBGA package mechanical drawing (2 of 2)

### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 06-Aug-2009 | Updated Figure 6<br>Table 12<br>• V <sub>DD_ADC</sub> : changed min value for "relative to V <sub>DD</sub> " condition<br>• V <sub>IN</sub> : changed min value for "relative to V <sub>DD</sub> " condition<br>• I <sub>CORELV</sub> : added new row<br>Table 14<br>• Ta-C-Grade Part, TJ-C-Grade Part, TA-V-Grade Part, TJ-V-Grade Part, TA-M-Grade Part, TJ-M-Grade Part:<br>added new rows<br>• Changed capacitance value in footnote<br>Table 21<br>• MEDIUM configuration: added condition for PAD3V5V = 0<br>Updated Figure 10<br>Table 26<br>• C <sub>DEC1</sub> : changed min value<br>• I <sub>MREG</sub> : changed max value<br>• I <sub>DD_BV</sub> : added max value<br>• I <sub>DD_BV</sub> : added max value<br>• V <sub>LVDHV3L</sub> : adde max value<br>• V <sub>LVDHV3L</sub> : adde max value<br>• V <sub>LVDHV3L</sub> : adde m |

### Table 50. Revision history (continued)

### **Document revision history**

| Table 50 | . Revision | history | (continued) |

|----------|------------|---------|-------------|

|----------|------------|---------|-------------|

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7        | 05-Jul-2010 | Added 64 LQFP package information<br>Updated the "Features" section.<br>Figures "LQFP 100-pin configuration" and "LQFP 100-pin configuration": removed<br>alternate function information<br>Added "Functional port pin descriptions" table<br>Added eDMA block in the "MPC5604B/C series block diagram" figure<br>Deleted the "NVUSRO[WATCHDOG_EN] field description" section<br>In the "Recommended operating conditions (3.3 V)" and "Recommended operating<br>conditions (5.0 V)" tables, deleted the conditions of T <sub>A C-Grade Part</sub> , T <sub>A V-Grade Part</sub> , T <sub>A</sub><br>M-Grade Part<br>In the "LQFP thermal characteristics" table, rounded the values.<br>In the "I/Q FP thermal characteristics" section, replaced "nRSTIN" with "RESET".<br>In the "I/Q input DC electrical characteristics" table:<br>• $W_{FI}$ : inserted a footnote<br>In the "Low voltage monitor electrical characteristics" table:<br>• changed min value $V_{LVDHV3L}$ , from 2.7 to 2.6<br>• Inserted max value of $V_{LVDLVCORL}$<br>In the "FMPLL electrical characteristics" table, rounded the values of $f_{VCO}$ .<br>In the "Deleteristics" table:<br>• Added $\Delta_{ASC}$ row<br>• Update values of $t_A$<br>In the "ADC conversion characteristics" table, added "I <sub>ADCRUN</sub> " rows<br>Removed "Orderable part number summary" table. |

| 8        | 25-Nov-2010 | <ul> <li>Editorial changes and improvements.</li> <li>In the "MPC5604B/C device comparison" table, changed the temperature value from 105 to 125 °C, in the footnote regarding "Execution speed".</li> <li>In the "Recommended operating conditions (3.3 V)" and "Recommended operating conditions (5.0 V)" tables, restored the conditions of T<sub>A C-Grade Part</sub>, T<sub>A V-Grade Part</sub>, T<sub>A</sub></li> <li>M-Grade Part</li> <li>In the "LQFP thermal characteristics" table, added values concerning 64 LQFP package.</li> <li>In the "MEDIUM configuration output buffer electrical characteristics" table: fixed a typo in last row of conditions column, there was I<sub>OH</sub> that now is I<sub>OL</sub>.</li> <li>In the "Reset electrical characteristics" table, changed the parameter classification tag for V<sub>OL</sub> and  I<sub>WPU</sub> .</li> <li>In the "Low voltage monitor electrical characteristics" table, changed the max value of V<sub>LVDLVCORL</sub> from 1.5V to 1.15V.</li> <li>In the "FMPLL electrical characteristics" table, changed the parameter classification tag for f<sub>VCO</sub>.</li> </ul>                                                                                                                                                                                                     |

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | 15 Oct 2012 | <ul> <li>Table 1 (MPC5604B/C device comparison), added footnote for MPC5603BxLH and MPC5604BxLH about FlexCAN availability.</li> <li>Table 3 (MPC5604B/C series block summary), replaced "System watchdog timer" with "Software watchdog timer" and specified AUTOSAR (Automotive Open System Architecture)</li> <li>Table 6 (Functional port pin descriptions): replaced footnote "Available only on MPC560xC versions and MPC5604B 208 MAPBGA devices" with "Available only on MPC560xC versions, MPC5604B 208 MAPBGA devices", replaced VDD with VDD_HV</li> <li>Figure 10 (Voltage regulator capacitance connection), updated pin name apperence</li> <li>Renamed Figure 11 (V<sub>DD_HV</sub> and V<sub>DD_BV</sub> maximum slope) (was "VDD and VDD_BV maximum slope")</li> <li>Renamed Figure 12 (V<sub>DD_HV</sub> and V<sub>DD_BV</sub> supply constraints during STANDBY mode exit) (was "VDD and VDD_BV supply constraints during STANDBY mode exit)</li> <li>Table 13 (Recommended operating conditions (3.3 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Table 14 (Recommended operating conditions (5.0 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Section 3.17.1, "Voltage regulator electrical characteristics: replaced "slew rate of V<sub>DD</sub>/V<sub>DD_BV</sub>" with "slew rate of both V<sub>DD_HV</sub> and V<sub>DD_BV</sub>" replaced "When STANDBY mode is used, further constraints apply to the V<sub>DD</sub>/V<sub>DD_BV</sub> in order to guarantee correct regulator functionality during STANDBY exit." with "When STANDBY mode is used, further constraints apply to the V<sub>DD_HV</sub> and V<sub>DD_BV</sub> in order to guarantee correct regulator function during STANDBY exit."</li> <li>Table 28 (Power consumption on VDD_BV and VDD_HV), updated footnotes of I<sub>DDMAX</sub> and I<sub>DDRUN</sub> stating that both currents are drawn only from the V<sub>DD_BV</sub> pin.</li> <li>Table 24 (Con-chip peripherals current consumption), in the paremeter column replaced V<sub>DD_BV</sub> and V<sub>DD_HV</sub> respectively with VDD_BV and VDD_HV.</li> <li>Table 46 (On-chip peripherals current consumption), in the paremeter column replaced V<sub>DD_BV</sub> and V<sub>DD_HV</sub> respecti</li></ul> |

| 11       | 14 Nov 2012 | In the cover feature list:<br>added "and ECC" at the end of "Up to 512 KB on-chip code flash supported with the<br>flash controller"<br>added "with ECC" at the end of "Up to 48 KB on-chip SRAM"<br>Table 13 (Recommended operating conditions (3.3 V)), removed minimum value of $T_{VDD}$<br>and relative footnote.<br>Table 14 (Recommended operating conditions (5.0 V)), removed minimum value of $T_{VDD}$<br>and relative footnote.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Appendix A Abbreviations

Table A-1 lists abbreviations used but not defined elsewhere in this document.

### Table A-1. Abbreviations

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| CMOS         | Complementary metal-oxide-semiconductor |

| СРНА         | Clock phase                             |

| CPOL         | Clock polarity                          |

| CS           | Peripheral chip select                  |

| EVTO         | Event out                               |

| МСКО         | Message clock out                       |

| MDO          | Message data out                        |

| MSEO         | Message start/end out                   |

| MTFE         | Modified timing format enable           |

| SCK          | Serial communications clock             |

| SOUT         | Serial data out                         |

| TBD          | To be defined                           |

| ТСК          | Test clock input                        |

| TDI          | Test data input                         |

| TDO          | Test data output                        |

| TMS          | Test mode select                        |