# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                              |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 79                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bk0mll6r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. MPC5604B/C device comparison<sup>1</sup>

|                                       |                                                                                                                                                     |                   |                  |                     |                  | Device              |                  |                  |                     |                  |                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|---------------------|------------------|---------------------|------------------|------------------|---------------------|------------------|-----------------------|

| Feature                               | SPC560B<br>40L1                                                                                                                                     | SPC560B<br>40L3   | SPC560B<br>40L5  | SPC560C<br>40L1     | SPC560C<br>40L3  | SPC560B<br>50L1     | SPC560B<br>50L3  | SPC560B<br>50L5  | SPC560C<br>50L1     | SPC560C<br>50L3  | SPC560B<br>50B2       |

| CPU                                   |                                                                                                                                                     |                   |                  |                     |                  | e200z0h             |                  |                  |                     |                  |                       |

| Execution speed <sup>2</sup>          |                                                                                                                                                     |                   |                  |                     | Stat             | tic – up to 64      | MHz              |                  |                     |                  |                       |

| Code Flash                            | 256 KB 512 KB                                                                                                                                       |                   |                  |                     |                  |                     |                  |                  |                     |                  |                       |

| Data Flash                            |                                                                                                                                                     | 64 KB (4 × 16 KB) |                  |                     |                  |                     |                  |                  |                     |                  |                       |

| RAM                                   | 24 KB                                                                                                                                               |                   |                  | 32                  | KB               |                     | 32 KB            |                  |                     | 48 KB            |                       |

| MPU                                   | 8-entry           12 ch         28 ch         36 ch         8 ch         28 ch         12 ch         28 ch         36 ch         8 ch         28 ch |                   |                  |                     |                  |                     |                  |                  |                     |                  |                       |

| ADC (10-bit)                          | 12 ch                                                                                                                                               | 28 ch             | 36 ch            | 8 ch                | 28 ch            | 12 ch               | 28 ch            | 36 ch            | 8 ch                | 28 ch            | 36 ch                 |

| СТИ                                   |                                                                                                                                                     | I                 | I                | I                   |                  | Yes                 |                  |                  |                     |                  |                       |

| Total timer I/O <sup>3</sup><br>eMIOS | 12 ch, 28 ch,<br>16-bit 16-bit                                                                                                                      |                   | 56 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit    | 28 ch,<br>16-bit | 56 ch,<br>16-bit      |

| • PWM + MC +<br>IC/OC <sup>4</sup>    | 2 ch                                                                                                                                                | 5 ch              | 10 ch            | 2 ch                | 5 ch             | 2 ch                | 5 ch             | 10 ch            | 2 ch                | 5 ch             | 10 ch                 |

| • PWM + IC/OC <sup>4</sup>            | 10 ch                                                                                                                                               | 20 ch             | 40 ch            | 10 ch               | 20 ch            | 10 ch               | 20 ch            | 40 ch            | 10 ch               | 20 ch            | 40 ch                 |

| • IC/OC <sup>4</sup>                  | _                                                                                                                                                   | 3 ch              | 6 ch             | _                   | 3 ch             | —                   | 3 ch             | 6 ch             | _                   | 3 ch             | 6 ch                  |

| SCI (LINFlex)                         |                                                                                                                                                     | 3 <sup>5</sup>    |                  |                     |                  |                     |                  | 4                |                     |                  |                       |

| SPI (DSPI)                            | 2                                                                                                                                                   | :                 | 3                | 2                   | 3                | 2                   | :                | 3                | 2                   |                  | 3                     |

| CAN (FlexCAN)                         |                                                                                                                                                     | 2 <sup>6</sup>    |                  | 5                   | 6                |                     | 3 <sup>7</sup>   |                  | 5                   |                  | 6                     |

| l <sup>2</sup> C                      |                                                                                                                                                     |                   |                  |                     |                  | 1                   |                  |                  |                     |                  |                       |

| 32 kHz oscillator                     |                                                                                                                                                     |                   |                  |                     |                  | Yes                 |                  |                  |                     |                  |                       |

| GPIO <sup>8</sup>                     | 45                                                                                                                                                  | 79                | 123              | 45                  | 79               | 45                  | 79               | 123              | 45                  | 79               | 123                   |

| Debug                                 |                                                                                                                                                     | <u>l</u>          | <u>I</u>         | <u>I</u>            | JT               | AG                  | 1                | 1                | 1                   | 1                | Nexus2+               |

| Package                               | LQFP64 <sup>9</sup>                                                                                                                                 | LQFP100           | LQFP144          | LQFP64 <sup>9</sup> | LQFP100          | LQFP64 <sup>9</sup> | LQFP100          | LQFP144          | LQFP64 <sup>9</sup> | LQFP100          | LBGA208 <sup>10</sup> |

<sup>1</sup> Feature set dependent on selected peripheral multiplexing—table shows example implementation

<sup>2</sup> Based on 125 °C ambient operating temperature

<sup>3</sup> See the eMIOS section of the device reference manual for information on the channel configuration and functions.

<sup>4</sup> IC – Input Capture; OC – Output Compare; PWM – Pulse Width Modulation; MC – Modulus counter

<sup>5</sup> SCI0, SCI1 and SCI2 are available. SCI3 is not available.

Freescale Semiconductor

MPC5604B/C Microcontroller Data Sheet, Rev. 11

Introduction

| Block                                     | Function                                                                                                                                                                                                                         |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory protection unit (MPU)              | Provides hardware access control for all memory references generated in a device                                                                                                                                                 |

| Nexus development interface<br>(NDI)      | Provides real-time development support capabilities in compliance with the IEEE-ISTO 5001-2003 standard                                                                                                                          |

| Periodic interrupt timer (PIT)            | Produces periodic interrupts and triggers                                                                                                                                                                                        |

| Real-time counter (RTC)                   | A free running counter used for time keeping applications, the RTC can be configured to generate an interrupt at a predefined interval independent of the mode of operation (run mode or low-power mode)                         |

| System integration unit (SIU)             | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| Static random-access memory (SRAM)        | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System status configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                 | Provides a set of output compare events to support AUTOSAR (Automotive Open System Architecture) and operating system tasks                                                                                                      |

| Software watchdog timer (SWT)             | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                        | The wakeup unit supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                         |

| Crossbar (XBAR) switch                    | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.                                                                  |

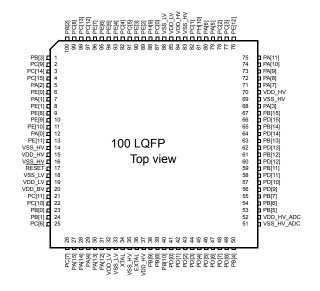

## 3.1 Package pinouts

The available LQFP pinouts and the 208 MAPBGA ballmap are provided in the following figures. For pin signal descriptions, please refer to the device reference manual.

|          |         | -                                  |                                                                              |                                                  |                                             |          | u                   |                  | Pin              | num      | ber                                                                                             |                         |

|----------|---------|------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|----------|---------------------|------------------|------------------|----------|-------------------------------------------------------------------------------------------------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                                     | Peripheral                                       | I/O direction <sup>2</sup>                  | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | dJ01 PPL         2         28         27         141         142         3         4         63 | 208 MAPBGA <sup>3</sup> |

| PC[9]    | PCR[41] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[41]<br>—<br>—<br>LIN2RX<br>WKPU[13] <sup>4</sup>                        | SIUL<br>—<br>—<br>LINFlex_2<br>WKPU              | I/O<br>—<br>—<br>—<br>—<br>—                | S        | Tristate            | 2                | 2                | 2        | 2                                                                                               | B1                      |

| PC[10]   | PCR[42] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[42]<br>CAN1TX<br>CAN4TX <sup>11</sup><br>MA[1]                          | SIUL<br>FlexCAN_1<br>FlexCAN_4<br>ADC            | I/O<br>O<br>O                               | М        | Tristate            | 13               | 13               | 22       | 28                                                                                              | M3                      |

| PC[11]   | PCR[43] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[43]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>WKPU[5] <sup>4</sup> | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>WKPU | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            |                  |                  | 21       | 27                                                                                              | M4                      |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[44]<br>E0UC[12]<br><br>SIN_2                                            | SIUL<br>eMIOS_0<br>—<br>DSPI_2                   | /0<br> /0<br>                               | Μ        | Tristate            |                  |                  | 97       | 141                                                                                             | B4                      |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[45]<br>E0UC[13]<br>SOUT_2<br>—                                          | SIUL<br>eMIOS_0<br>DSPI_2<br>—                   | I/O<br>I/O<br>O                             | S        | Tristate            | _                | _                | 98       | 142                                                                                             | A2                      |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[46]<br>E0UC[14]<br>SCK_2<br>—<br>EIRQ[8]                                | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL           | /0<br> /0<br> /0<br>                        | S        | Tristate            | _                | _                | 3        | 3                                                                                               | C1                      |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[47]<br>E0UC[15]<br>CS0_2<br>—                                           | SIUL<br>eMIOS_0<br>DSPI_2<br>—                   | I/O<br>I/O<br>I/O                           | М        | Tristate            | —                | —                | 4        | 4                                                                                               | D3                      |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[48]<br><br><br>GPI[4]                                                   | SIUL<br>—<br>—<br>ADC                            | <br> -<br>                                  | I        | Tristate            | —                | —                | 41       | 63                                                                                              | P12                     |

#### Table 6. Functional port pin descriptions (continued)

|          |         | -                                  |                                                                  |                                                  |                                        |          | Ľ                   |                  | Pin              | num      | ber      |                         |

|----------|---------|------------------------------------|------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                         | Peripheral                                       | I/O direction <sup>2</sup>             | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PF[10]   | PCR[90] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[90]<br>—<br>—<br>—                                          | SIUL<br>—<br>—<br>—                              | I/O<br>                                | М        | Tristate            | _                |                  |          | 38       | R3                      |

| PF[11]   | PCR[91] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[91]<br>—<br>—<br>—<br>WKPU[15] <sup>4</sup>                 | SIUL<br>—<br>—<br>—<br>WKPU                      | I/O<br> -<br> <br>                     | S        | Tristate            | _                | _                | _        | 39       | R4                      |

| PF[12]   | PCR[92] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[92]<br>E1UC[25]<br>—<br>—                                   | SIUL<br>eMIOS_1<br>                              | I/O<br>I/O<br>                         | М        | Tristate            | —                | _                |          | 35       | R1                      |

| PF[13]   | PCR[93] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[93]<br>E1UC[26]<br>—<br>WKPU[16] <sup>4</sup>               | SIUL<br>eMIOS_1<br><br>WKPU                      | I/O<br>I/O<br>                         | S        | Tristate            | _                | _                | _        | 41       | T6                      |

| PF[14]   | PCR[94] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[94]<br>CAN4TX <sup>11</sup><br>E1UC[27]<br>CAN1TX           | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_4        | I/O<br>O<br>I/O<br>O                   | М        | Tristate            | _                | 43               |          | 102      | D14                     |

| PF[15]   | PCR[95] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[95]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[13] | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | _                | 42               |          | 101      | E15                     |

| PG[0]    | PCR[96] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[96]<br>CAN5TX <sup>11</sup><br>E1UC[23]<br>—                | SIUL<br>FlexCAN_5<br>eMIOS_1<br>—                | I/O<br>O<br>I/O                        | М        | Tristate            | —                | 41               |          | 98       | E14                     |

| PG[1]    | PCR[97] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[97]<br><br>                                                 | SIUL<br>—<br>eMIOS_1<br>—<br>FlexCAN_5<br>SIUL   | I/O<br><br><br><br>                    | S        | Tristate            | _                | 40               |          | 97       | E13                     |

#### Table 6. Functional port pin descriptions (continued)

### 3.13 Recommended operating conditions

| Symbol                           |    | Parameter                                                                                     | Conditions                   | Va                   | lue                  | Unit |

|----------------------------------|----|-----------------------------------------------------------------------------------------------|------------------------------|----------------------|----------------------|------|

| Symbol                           |    | Falameter                                                                                     | Conditions                   | Min                  | Max                  | Unit |

| V <sub>SS</sub>                  | SR | Digital ground on VSS_HV pins                                                                 | —                            | 0                    | 0                    | V    |

| V <sub>DD</sub> <sup>1</sup>     | SR | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | —                            | 3.0                  | 3.6                  | V    |

| V <sub>SS_LV</sub> <sup>2</sup>  | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub> <sup>3</sup>  | SR | Voltage on VDD_BV pin (regulator supply) with                                                 | —                            | 3.0                  | 3.6                  | V    |

|                                  |    | respect to ground (V <sub>SS</sub> )                                                          | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>SS_ADC</sub>              | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )           | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub> <sup>4</sup> | SR | 5 <u> </u>                                                                                    | —                            | 3.0 <sup>5</sup>     | 3.6                  | V    |

|                                  |    | with respect to ground (V <sub>SS</sub> )                                                     | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>IN</sub>                  | SR | Voltage on any GPIO pin with respect to ground                                                | —                            | V <sub>SS</sub> -0.1 | _                    | V    |

|                                  |    | (V <sub>SS</sub> )                                                                            | Relative to $V_{\text{DD}}$  | _                    | V <sub>DD</sub> +0.1 |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during overload condition                                   | —                            | -5                   | 5                    | mA   |

| I <sub>INJSUM</sub>              | SR | Absolute sum of all injected input currents during overload condition                         |                              | -50                  | 50                   |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                 | —                            |                      | 0.25                 | V/µs |

| T <sub>A C-Grade Part</sub>      | SR | Ambient temperature under bias                                                                | $f_{CPU} \le 64 \text{ MHz}$ | -40                  | 85                   | °C   |

| T <sub>J C-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 110                  |      |

| T <sub>A V-Grade Part</sub>      | SR | Ambient temperature under bias                                                                |                              | -40                  | 105                  |      |

| T <sub>J V-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 130                  |      |

| T <sub>A M-Grade Part</sub>      | SR | Ambient temperature under bias                                                                |                              | -40                  | 125                  | 1    |

| T <sub>J M-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                              | -40                  | 150                  | 1    |

Table 13. Recommended operating conditions (3.3 V)

$^1$  100 nF capacitance needs to be provided between each  $V_{\text{DD}}/V_{\text{SS}}$  pair

$^2~$  330 nF capacitance needs to be provided between each V\_{DD\\_LV}\!/V\_{SS\\_LV} supply pair.

<sup>3</sup> 400 nF capacitance needs to be provided between  $V_{DD_BV}$  and the nearest  $V_{SS_LV}$  (higher value may be needed depending on external regulator characteristics).

$^4$  100 nF capacitance needs to be provided between V\_{DD\_ADC}/V\_{SS\_ADC} pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation

| Sum             | Symbol |   | Paramotor                                 |           | Conditions <sup>1</sup>                                                                              | \<br>\               |     | Unit               |      |

|-----------------|--------|---|-------------------------------------------|-----------|------------------------------------------------------------------------------------------------------|----------------------|-----|--------------------|------|

| J               |        |   |                                           |           | Conditions                                                                                           | Min                  | Тур | Max                | Unit |

| V <sub>OH</sub> | СС     | С | Output high level<br>MEDIUM configuration | Push Pull | I <sub>OH</sub> = -3.8 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 0.8V <sub>DD</sub>   |     |                    | V    |

|                 |        | Ρ |                                           |           | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>   |     | _                  |      |

|                 |        | С |                                           |           | I <sub>OH</sub> = –1 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>                  | 0.8V <sub>DD</sub>   | -   | —                  |      |

|                 |        | С |                                           |           | I <sub>OH</sub> = -1 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)              | V <sub>DD</sub> -0.8 |     | _                  |      |

|                 |        | С |                                           |           | I <sub>OH</sub> = –100 μΑ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 0.8V <sub>DD</sub>   | -   | —                  |      |

| V <sub>OL</sub> | СС     | С | Output low level<br>MEDIUM configuration  | Push Pull | I <sub>OL</sub> = 3.8 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                              | _                    |     | 0.2V <sub>DD</sub> | V    |

|                 |        | Ρ |                                           |           | I <sub>OL</sub> = 2 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended)               | _                    |     | 0.1V <sub>DD</sub> |      |

|                 |        | С |                                           |           | I <sub>OL</sub> = 1 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>                   | _                    | -   | 0.1V <sub>DD</sub> |      |

|                 |        | С |                                           |           | $I_{OL}$ = 1 mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)                      | —                    |     | 0.5                |      |

|                 |        | С |                                           |           | I <sub>OL</sub> = 100 μA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                              | —                    |     | 0.1V <sub>DD</sub> |      |

<sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

| Svn             | Symbol | C | Parameter                               |           | Conditions <sup>1</sup>                                                                 |                      | Unit |     |   |

|-----------------|--------|---|-----------------------------------------|-----------|-----------------------------------------------------------------------------------------|----------------------|------|-----|---|

| Symbol          |        | ľ | i arameter                              |           | Conditions                                                                              | Min                  | Тур  | Max |   |

| V <sub>OH</sub> | СС     |   | Output high level<br>FAST configuration | Push Pull | $I_{OH} = -14$ mA,<br>$V_{DD} = 5.0$ V ± 10%, PAD3V5V = 0<br>(recommended)              | 0.8V <sub>DD</sub>   | _    | _   | V |

|                 |        | С |                                         |           | I <sub>OH</sub> = -7mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>      | 0.8V <sub>DD</sub>   |      | _   |   |

|                 |        | С |                                         |           | I <sub>OH</sub> = -11mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | V <sub>DD</sub> -0.8 |      | _   |   |

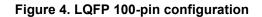

- HV—High voltage external power supply for voltage regulator module. This must be provided externally through VDD\_HV power pin.

- BV—High voltage external power supply for internal ballast module. This must be provided externally through VDD\_BV power pin. Voltage values should be aligned with V<sub>DD</sub>.

- LV—Low voltage internal power supply for core, FMPLL and flash digital logic. This is generated by the internal voltage regulator but provided outside to connect stability capacitor. It is further split into four main domains to ensure noise isolation between critical LV modules within the device:

- LV\_COR—Low voltage supply for the core. It is also used to provide supply for FMPLL through double bonding.

- LV\_CFLA—Low voltage supply for code flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA—Low voltage supply for data flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL-Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 10. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see Section 3.13, Recommended operating conditions).

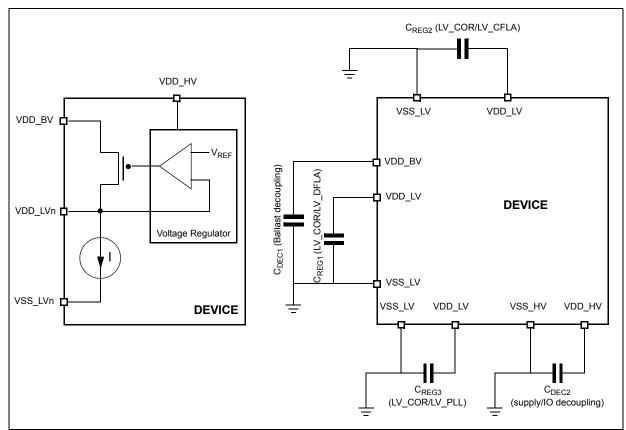

The internal voltage regulator requires a controlled slew rate of both V<sub>DD HV</sub> and V<sub>DD BV</sub> as described in Figure 11.

MPC5604B/C Microcontroller Data Sheet, Rev. 11

| Table 26. | Voltage regul | ator electrica | l characteristics |  |

|-----------|---------------|----------------|-------------------|--|

|           |               |                |                   |  |

| Symbol                              |    | с | Parameter                                                           | Conditions <sup>1</sup>                                                             |                  | Value            |     | Unit  |

|-------------------------------------|----|---|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|-----|-------|

| Symbol                              |    | C | Faiametei                                                           | Conditions                                                                          | Min              | Тур              | Max | Onic  |

| C <sub>REGn</sub>                   | SR |   | Internal voltage regulator external capacitance                     | —                                                                                   | 200              | _                | 500 | nF    |

| R <sub>REG</sub>                    | SR |   | Stability capacitor equivalent serial resistance                    | Range:<br>10 kHz to 20 MHz                                                          | _                |                  | 0.2 | Ω     |

| C <sub>DEC1</sub>                   | SR |   | Decoupling capacitance <sup>2</sup> ballast                         | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 4.5 V to 5.5 V | 100 <sup>3</sup> | 470 <sup>4</sup> |     | nF    |

|                                     |    |   |                                                                     | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 3 V to 3.6 V   | 400              |                  |     |       |

| C <sub>DEC2</sub>                   | SR |   | Decoupling capacitance regulator supply                             | V <sub>DD</sub> /V <sub>SS</sub> pair                                               | 10               | 100              | _   | nF    |

| $\frac{\mathrm{d}}{\mathrm{d}t}VDD$ | SR | — | Maximum slope on V <sub>DD</sub>                                    |                                                                                     |                  | _                | 250 | mV/µs |

| $ \Delta_{VDD(STDBY)} $             | SR |   | Maximum instant variation on V <sub>DD</sub><br>during standby exit |                                                                                     |                  |                  | 30  | mV    |

| Symbol                                                                                                                |    | C Parameter |                                                                  | Conditions <sup>1</sup>                               |      | Value |                  | Unit  |

|-----------------------------------------------------------------------------------------------------------------------|----|-------------|------------------------------------------------------------------|-------------------------------------------------------|------|-------|------------------|-------|

|                                                                                                                       |    | C           | Falameter                                                        | Conditions                                            | Min  | Тур   | Max              | Onic  |

| $\frac{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }$ | SR |             | Maximum slope on V <sub>DD</sub> during standby exit             |                                                       | —    |       | 15               | mV/µs |

| V <sub>MREG</sub>                                                                                                     | СС | Т           | Main regulator output voltage                                    | Before exiting from reset                             | _    | 1.32  |                  | V     |

|                                                                                                                       |    | Ρ           | -                                                                | After trimming                                        | 1.16 | 1.28  | —                |       |

| I <sub>MREG</sub>                                                                                                     | SR |             | Main regulator current provided to $V_{DD_LV}$ domain            | _                                                     | _    |       | 150              | mA    |

| I <sub>MREGINT</sub>                                                                                                  | СС | D           |                                                                  | I <sub>MREG</sub> = 200 mA                            | _    |       | 2                | mA    |

|                                                                                                                       |    |             | consumption                                                      | I <sub>MREG</sub> = 0 mA                              | _    |       | 1                |       |

| V <sub>LPREG</sub>                                                                                                    | СС | Ρ           | Low power regulator output voltage                               | After trimming                                        | 1.16 | 1.28  | _                | V     |

| I <sub>LPREG</sub>                                                                                                    | SR |             | Low power regulator current provided to $V_{DD_LV}$ domain       | _                                                     | —    |       | 15               | mA    |

| I <sub>LPREGINT</sub>                                                                                                 | СС | D           | Low power regulator module current consumption                   | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | —    |       | 600              | μA    |

|                                                                                                                       |    |             |                                                                  | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _    | 5     |                  | -     |

| V <sub>ULPREG</sub>                                                                                                   | СС | Ρ           | Ultra low power regulator output voltage                         | After trimming                                        | 1.16 | 1.28  | _                | V     |

| IULPREG                                                                                                               | SR | —           | Ultra low power regulator current provided to $V_{DD_LV}$ domain | _                                                     | _    |       | 5                | mA    |

| IULPREGINT                                                                                                            | СС | D           | Ultra low power regulator module current consumption             | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C | —    | —     | 100              | μA    |

|                                                                                                                       |    |             |                                                                  | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C | -    | 2     | _                |       |

| I <sub>DD_BV</sub>                                                                                                    | СС | D           | In-rush average current on $V_{DD\_BV}$ during power-up $^{5}$   | _                                                     | -    | —     | 300 <sup>6</sup> | mA    |

Table 26. Voltage regulator electrical characteristics (continued)

$^1$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified

- $^2$  This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

- $^3\,$  This value is acceptable to guarantee operation from 4.5 V to 5.5 V

- <sup>4</sup> External regulator and capacitance circuitry must be capable of providing I<sub>DD\_BV</sub> while maintaining supply V<sub>DD\_BV</sub> in operating range.

- <sup>5</sup> In-rush average current is seen only for short time (maximum 20 µs) during power-up and on standby exit. It is dependant on the sum of the C<sub>REGn</sub> capacitances.

- <sup>6</sup> The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

The  $|\Delta_{VDD(STDBY)}|$  and dVDD(STDBY)/dt system requirement can be used to define the component used for the V<sub>DD</sub> supply generation. The following two examples describe how to calculate capacitance size:

| Symbol                          |    | c | C Parameter Conditions <sup>1</sup> |                             |                         |   |     |                  | Unit |

|---------------------------------|----|---|-------------------------------------|-----------------------------|-------------------------|---|-----|------------------|------|

| Symbol                          |    | C | Falameter                           | Conditions '                |                         |   | Тур | Мах              | Unit |

| I <sub>DDMAX</sub> <sup>2</sup> | СС | D | RUN mode maximum average current    | _                           |                         | _ | 115 | 140 <sup>3</sup> | mA   |

| I <sub>DDRUN</sub> 4            | СС | Т | RUN mode typical                    | f <sub>CPU</sub> = 8 MHz    |                         | _ | 7   | _                | mA   |

|                                 |    | Т | average current <sup>5</sup>        | f <sub>CPU</sub> = 16 MHz   |                         | — | 18  | _                | -    |

|                                 |    | Т |                                     | f <sub>CPU</sub> = 32 MHz   |                         |   | 29  |                  |      |

|                                 |    | Ρ |                                     | f <sub>CPU</sub> = 48 MHz   |                         | _ | 40  | 100              |      |

|                                 |    | Ρ |                                     | f <sub>CPU</sub> = 64 MHz   |                         | _ | 51  | 125              |      |

| I <sub>DDHALT</sub>             | СС | С | HALT mode current <sup>6</sup>      | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _ | 8   | 15               | mA   |

|                                 |    | Ρ |                                     | (128 kHz) running           | T <sub>A</sub> = 125 °C | _ | 14  | 25               |      |

| IDDSTOP                         | СС | Ρ | STOP mode current <sup>7</sup>      | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _ | 180 | 700 <sup>8</sup> | μA   |

|                                 |    | D |                                     | (128 kHz) running           | T <sub>A</sub> = 55 °C  | _ | 500 | _                |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 85 °C  | _ | 1   | 6 <sup>8</sup>   | mA   |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 105 °C | _ | 2   | 9 <sup>8</sup>   |      |

|                                 |    | Ρ |                                     |                             | T <sub>A</sub> = 125 °C | - | 4.5 | 12 <sup>8</sup>  |      |

| I <sub>DDSTDBY2</sub>           | СС | Ρ |                                     | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _ | 30  | 100              | μA   |

|                                 |    | D | current <sup>9</sup>                | (128 kHz) running           | T <sub>A</sub> = 55 °C  | - | 75  |                  |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 85 °C  | - | 180 | 700              |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 105 °C | _ | 315 | 1000             |      |

|                                 |    | Ρ |                                     |                             | T <sub>A</sub> = 125 °C | - | 560 | 1700             |      |

| I <sub>DDSTDBY1</sub>           | СС | Т |                                     | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | - | 20  | 60               | μA   |

|                                 |    | D | current <sup>10</sup>               | (128 kHz) running           | T <sub>A</sub> = 55 °C  | - | 45  |                  |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 85 °C  | _ | 100 | 350              |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 105 °C | _ | 165 | 500              |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 125 °C |   | 280 | 900              |      |

| Table 28. Power consumption on VDD_BV and VDD_HV |

|--------------------------------------------------|

|--------------------------------------------------|

$\frac{1}{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> I<sub>DDMAX</sub> is drawn only from the V<sub>DD\_BV</sub> pin. Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

<sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in rush current on Table 26.

- <sup>4</sup> I<sub>DDRUN</sub> is drawn only from the V<sub>DD\_BV</sub> pin. RUN current measured with typical application with accesses on both flash and RAM.

- <sup>5</sup> Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

| Symbo               | Symbol |   | Parameter Conditions <sup>1</sup>             |                                                                                       |     | Unit |     |      |

|---------------------|--------|---|-----------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

| Symbo               | וכ     | С | Parameter Conditions                          |                                                                                       | Min | Тур  | Max | Unit |

| f <sub>PLLIN</sub>  | SR     |   | FMPLL reference clock <sup>2</sup>            | —                                                                                     | 4   |      | 64  | MHz  |

| $\Delta_{PLLIN}$    | SR     | _ | FMPLL reference clock duty cycle <sup>2</sup> | _                                                                                     | 40  | _    | 60  | %    |

| f <sub>PLLOUT</sub> | CC     | D | FMPLL output clock frequency                  | —                                                                                     | 16  | —    | 64  | MHz  |

| f <sub>VCO</sub> 3  | СС     |   | VCO frequency without<br>frequency modulation | _                                                                                     | 256 | _    | 512 | MHz  |

|                     |        | С | VCO frequency with frequency modulation       | _                                                                                     | 245 | _    | 533 |      |

| f <sub>CPU</sub>    | SR     |   | System clock frequency                        | —                                                                                     | —   |      | 64  | MHz  |

| f <sub>FREE</sub>   | СС     | Ρ | Free-running frequency                        | _                                                                                     | 20  | _    | 150 | MHz  |

| t <sub>LOCK</sub>   | CC     | Ρ | FMPLL lock time                               | Stable oscillator (f <sub>PLLIN</sub> = 16 MHz)                                       | _   | 40   | 100 | μs   |

| $\Delta t_{STJIT}$  | CC     |   | FMPLL short term jitter <sup>4</sup>          | f <sub>sys</sub> maximum                                                              | -4  |      | 4   | %    |

| $\Delta t_{LTJIT}$  | СС     | _ | FMPLL long term jitter                        | f <sub>PLLIN</sub> = 16 MHz (resonator),<br>f <sub>PLLCLK</sub> @ 64 MHz, 4000 cycles | _   | _    | 10  | ns   |

| I <sub>PLL</sub>    | СС     | С | FMPLL consumption                             | T <sub>A</sub> = 25 °C                                                                | _   |      | 4   | mA   |

#### Table 41. FMPLL electrical characteristics

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> PLLIN clock retrieved directly from FXOSC clock. Input characteristics are granted when oscillator is used in functional mode. When bypass mode is used, oscillator input clock should verify  $f_{PLLIN}$  and  $\Delta_{PLLIN}$ .

<sup>3</sup> Frequency modulation is considered ±4%

<sup>4</sup> Short term jitter is measured on the clock rising edge at cycle n and n+4.

# 3.24 Fast internal RC oscillator (16 MHz) electrical characteristics

The device provides a 16 MHz fast internal RC oscillator. This is used as the default clock at the power-up of the device.

| Symbo                              |    | С | Parameter                                                                   | Conditions <sup>1</sup>         |     | Unit |     |      |

|------------------------------------|----|---|-----------------------------------------------------------------------------|---------------------------------|-----|------|-----|------|

| Gymbo                              |    |   | i didineter                                                                 | Conditions                      | Min | Тур  | Мах | Onne |

| f <sub>FIRC</sub>                  | СС |   | Fast internal RC oscillator high                                            | T <sub>A</sub> = 25 °C, trimmed | _   | 16   |     | MHz  |

|                                    | SR | _ | frequency                                                                   | _                               | 12  |      | 20  |      |

| I <sub>FIRCRUN</sub> <sup>2,</sup> | СС | Т | Fast internal RC oscillator high<br>frequency current in running mode       | T <sub>A</sub> = 25 °C, trimmed | _   |      | 200 | μA   |

| I <sub>FIRCPWD</sub>               | CC |   | Fast internal RC oscillator high<br>frequency current in power down<br>mode | T <sub>A</sub> = 125 °C         |     |      | 10  | μA   |

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics

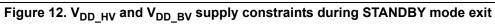

Figure 23. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $t_c$ ). Again the conversion period  $t_c$  is longer than the sampling time  $t_s$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $t_s$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 11 between the ideal and real sampled voltage on  $C_S$ :

$$\frac{V_{A2}}{V_{A}} = \frac{C_{P1} + C_{P2} + C_{F}}{C_{P1} + C_{P2} + C_{F} + C_{S}}$$

Eqn. 11

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

Eqn. 12

$$C_F > 2048 \bullet C_S$$

#### **On-chip peripherals** 3.27

#### **Current consumption** 3.27.1

| Symbol                     |    | С | Parameter                                              |                                                                                                                                                                                                    | Conditions                                                            | Typical value <sup>2</sup>                                   | Unit |

|----------------------------|----|---|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------|------|

| IDD_BV(CAN)                | CC | Т | CAN (FlexCAN) supply<br>current on VDD_BV              | Bitrate:<br>500 Kbyte/s<br>Bitrate:<br>125 Kbyte/s<br>Consumption:<br>• FlexCAN in loop-back<br>mode<br>• XTAL @ 8 MHz used as<br>CAN engine clock source<br>• Message sending period<br>is 580 µs |                                                                       | 8 * f <sub>periph</sub> + 85<br>8 * f <sub>periph</sub> + 27 | μA   |

| I <sub>DD_BV(eMIOS)</sub>  | СС | Т | eMIOS supply current on VDD_BV                         | Static consu<br>• eMIOS ch<br>• Global pre<br>Dynamic cor                                                                                                                                          | annel OFF<br>escaler enabled                                          | 29 * f <sub>periph</sub><br>3                                | μA   |

|                            |    |   |                                                        | <ul> <li>It does not</li> </ul>                                                                                                                                                                    | t change varying the (0.003 mA)                                       | Ū.                                                           |      |

| I <sub>DD_BV(SCI)</sub>    | СС | Т | SCI (LINFlex) supply<br>current on VDD_BV              | Total (static<br>• LIN mode<br>• Baudrate:                                                                                                                                                         |                                                                       | 5 * f <sub>periph</sub> + 31                                 | μA   |

| I <sub>DD_BV(SPI)</sub>    | СС | Т | SPI (DSPI) supply current                              | Ballast static                                                                                                                                                                                     | consumption (only clocked)                                            | 1                                                            | μA   |

|                            |    |   | on VDD_BV                                              | (continuous <ul> <li>Baudrate:</li> </ul>                                                                                                                                                          | sion every 8 µs                                                       | 16 * f <sub>periph</sub>                                     |      |

| I <sub>DD_BV(ADC)</sub>    | СС | Т | ADC supply current on VDD_BV                           | V <sub>DD</sub> = 5.5 V                                                                                                                                                                            | V <sub>DD</sub> = 5.5 V Ballast static consumption<br>(no conversion) |                                                              | μA   |

|                            |    |   |                                                        | Ballast dynamic<br>consumption<br>(continuous conversion) <sup>3</sup>                                                                                                                             |                                                                       | 5 * f <sub>periph</sub>                                      |      |

| IDD_HV_ADC(ADC)            | СС | Т | ADC supply current on<br>VDD_HV_ADC                    | V <sub>DD</sub> = 5.5 V Analog static consumption<br>(no conversion)                                                                                                                               |                                                                       | 2 * f <sub>periph</sub>                                      | μA   |

|                            |    |   |                                                        | Analog dynamic<br>consumption<br>(continuous conversion)                                                                                                                                           |                                                                       | 75 * f <sub>periph</sub> + 32                                |      |

| I <sub>DD_HV</sub> (FLASH) | СС | Т | Code Flash + Data Flash<br>supply current on<br>VDD_HV | V <sub>DD</sub> = 5.5 V                                                                                                                                                                            | _                                                                     | 8.21                                                         | mA   |

| I <sub>DD_HV</sub> (PLL)   | СС | Т | PLL supply current on VDD_HV                           | V <sub>DD</sub> = 5.5 V                                                                                                                                                                            | _                                                                     | 30 * f <sub>periph</sub>                                     | μA   |

#### Table 46. On-chip peripherals current consumption<sup>1</sup>

<sup>1</sup> Operating conditions:  $T_A = 25 \text{ °C}$ ,  $f_{periph} = 8 \text{ MHz}$  to 64 MHz <sup>2</sup>  $f_{periph}$  is an absolute value.

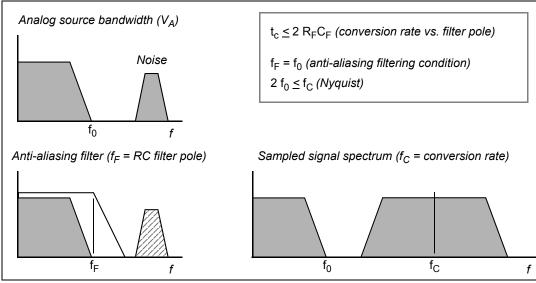

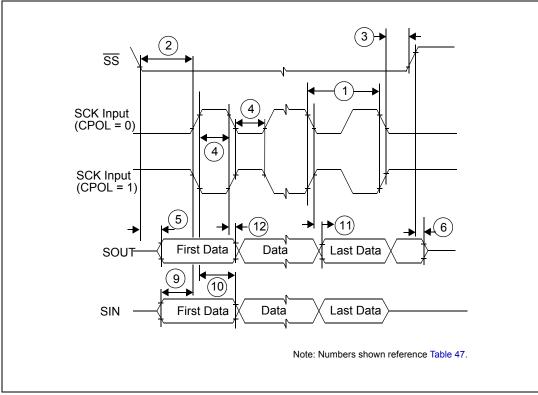

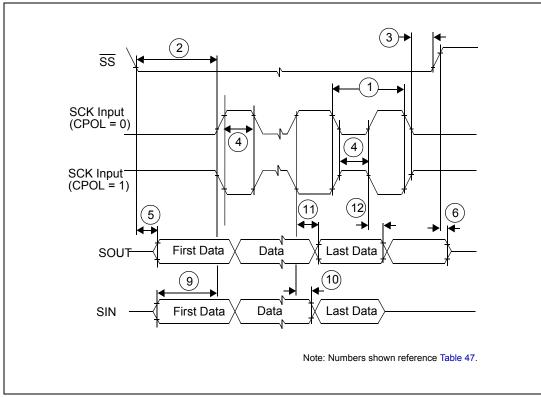

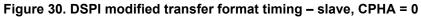

Figure 27. DSPI classic SPI timing – slave, CPHA = 1

MPC5604B/C Microcontroller Data Sheet, Rev. 11

#### MPC5604B/C Microcontroller Data Sheet, Rev. 11

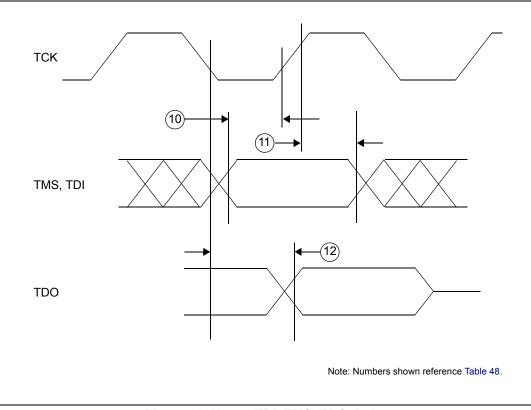

Figure 33. Nexus TDI, TMS, TDO timing

### 3.27.4 JTAG characteristics

#### Table 49. JTAG characteristics

| No. | Symb              |    | с | Parameter              |     | Value |     | Unit |

|-----|-------------------|----|---|------------------------|-----|-------|-----|------|

| NO. | Synn              |    | C | Falameter              | Min | Тур   | Мах | onit |

| 1   | t <sub>JCYC</sub> | CC | D | TCK cycle time         | 64  | _     | _   | ns   |

| 2   | t <sub>TDIS</sub> | СС | D | TDI setup time         | 15  | _     | —   | ns   |

| 3   | t <sub>TDIH</sub> | CC | D | TDI hold time          | 5   | _     | —   | ns   |

| 4   | t <sub>TMSS</sub> | СС | D | TMS setup time         | 15  | _     | —   | ns   |

| 5   | t <sub>TMSH</sub> | CC | D | TMS hold time          | 5   | _     | —   | ns   |

| 6   | t <sub>TDOV</sub> | CC | D | TCK low to TDO valid   | —   | _     | 33  | ns   |

| 7   | t <sub>TDOI</sub> | CC | D | TCK low to TDO invalid | 6   | —     | —   | ns   |

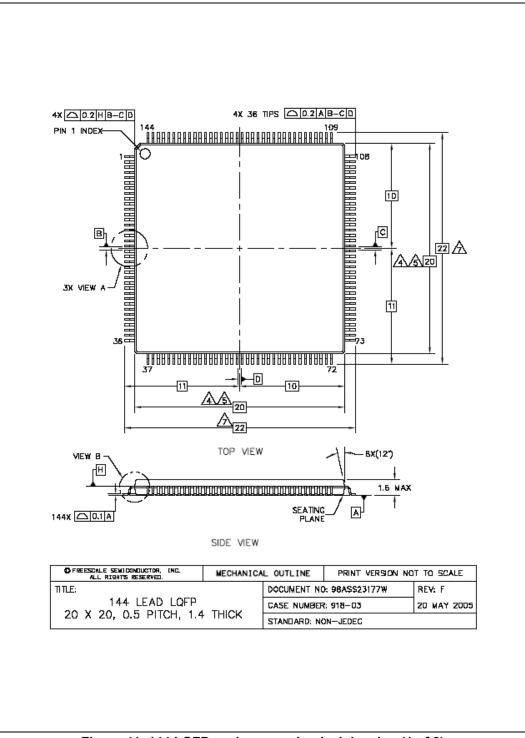

### 4.1.3 144 LQFP

Figure 41. 144 LQFP package mechanical drawing (1 of 2)

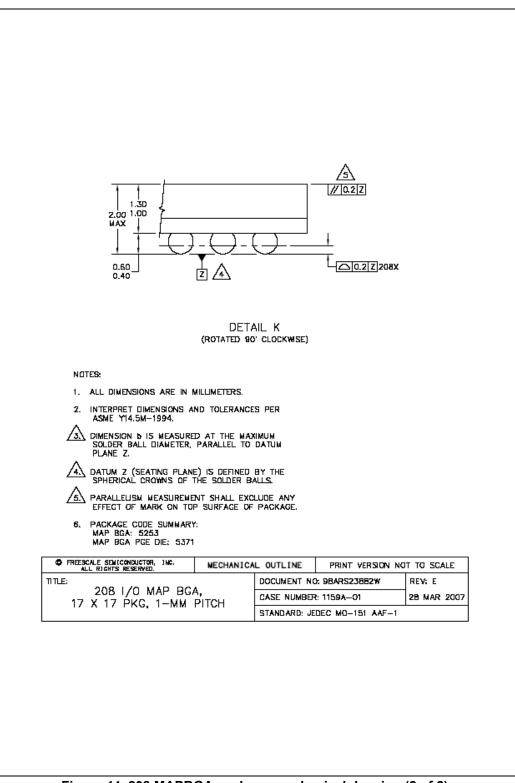

Figure 44. 208 MAPBGA package mechanical drawing (2 of 2)

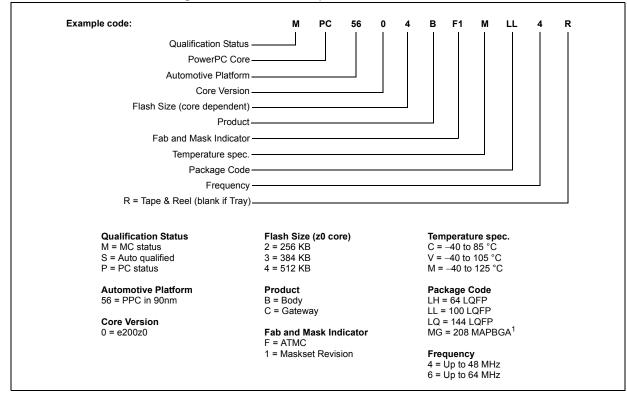

# 5 Ordering information

Figure 45. Commercial product code structure

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

# 6 Document revision history

Table 50 summarizes revisions to this document.

Table 50. Revision history

| Revision | Date        | Description of Changes |

|----------|-------------|------------------------|

| 1        | 04-Apr-2008 | Initial release.       |