# E·XFL

#### NXP USA Inc. - SPC5604BK0VLL6 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 64MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604bk0vll6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device. To ensure a complete understanding of the device functionality, refer also to the device reference manual and errata sheet.

# 1.2 Description

The MPC5604B/C is a family of next generation microcontrollers built on the Power Architecture<sup>®</sup> embedded category.

The MPC5604B/C family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle. The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category and only implements the VLE (variable-length encoding) APU, providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

#### Block diagram

Table 3 summarizes the functions of all blocks present in the MPC5604B/C series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                                         | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-locked loop (FMPLL)                 | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock                      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                               | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)                           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Power control unit (MC_PCU)                                   | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)                           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

Table 3. MPC5604B/C series block summary

# 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Three dedicated VDD\_LV/VSS\_LV supply pairs are used for 1.2 V regulator stabilization.

|            |                                                                                                                                      | Pin number           |                       |                        |                                                                                       |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Port pin   | Function                                                                                                                             | 64 LQFP <sup>1</sup> | 100 LQFP              | 144 LQFP               | 208<br>MAPBGA <sup>2</sup>                                                            |  |  |  |  |

| VDD_HV     | Digital supply voltage                                                                                                               | 7, 28, 56            | 15, 37, 70, 84        | 19, 51, 100,<br>123    | C2, D9, E16,<br>G13, H3, N9,<br>R5                                                    |  |  |  |  |

| VSS_HV     | Digital ground                                                                                                                       | 6, 8, 26, 55         | 14, 16, 35,<br>69, 83 | 18, 20, 49,<br>99, 122 | G7, G8, G9,<br>G10, H1, H7,<br>H8, H9, H10,<br>J7, J8, J9,<br>J10, K7, K8,<br>K9, K10 |  |  |  |  |

| VDD_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS_LV}$ pin. <sup>3</sup>        | 11, 23, 57           | 19, 32, 85            | 23, 46, 124            | D8, K4, P7                                                                            |  |  |  |  |

| VSS_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV</sub> pin. <sup>3</sup> | 10, 24, 58           | 18, 33, 86            | 22, 47, 125            | C8, J2, N7                                                                            |  |  |  |  |

| VDD_BV     | Internal regulator supply voltage                                                                                                    | 12                   | 20                    | 24                     | K3                                                                                    |  |  |  |  |

| VSS_HV_ADC | Reference ground and analog ground for the ADC                                                                                       | 33                   | 51                    | 73                     | R15                                                                                   |  |  |  |  |

| VDD_HV_ADC | Reference voltage and analog supply for the ADC                                                                                      | 34                   | 52                    | 74                     | P14                                                                                   |  |  |  |  |

#### Table 4. Voltage supply pin descriptions

<sup>1</sup> Pin numbers apply to both the MPC560xB and MPC560xC packages.

<sup>2</sup> 208 MAPBGA available only as development package for Nexus2+

<sup>3</sup> A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet for details).

### 3.4 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^1$

$M = Medium^{1 2}$

$$F = Fast^{1/2}$$

I = Input only with analog feature<sup>1</sup>

J = Input/Output ('S' pad) with analog feature

X = Oscillator

<sup>1.</sup> See the I/O pad electrical characteristics in the device datasheet for details.

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium (see PCR.SRC in section Pad Configuration Registers (PCR0–PCR122) in the device reference manual).

|          |         | -                               |                                                           |                                       |                              |          | ų                   |                  | Pin              | n num    | ber      |                         |

|----------|---------|---------------------------------|-----------------------------------------------------------|---------------------------------------|------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup> | Function                                                  | Peripheral                            | I/O direction <sup>2</sup>   | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[10]<br>E0UC[10]<br>SDA<br>—                          | SIUL<br>eMIOS_0<br>I2C_0<br>—         | I/O<br>I/O<br>I/O            | S        | Tristate            | 47               | 47               | 74       | 107      | B16                     |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[11]<br>E0UC[11]<br>SCL<br>—                          | SIUL<br>eMIOS_0<br>I2C_0<br>—         | I/O<br>I/O<br>I/O            | S        | Tristate            | 48               | 48               | 75       | 108      | B15                     |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[12]<br>—<br>—<br>SIN_0                               | SIUL<br>—<br>—<br>—<br>DSPI0          | I/O<br>—<br>—<br>—<br>—      | S        | Tristate            | 22               | 22               | 31       | 45       | T7                      |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[13]<br>SOUT_0<br>—                                   | SIUL<br>DSPI_0<br>—<br>—              | I/O<br>O<br>                 | М        | Tristate            | 21               | 21               | 30       | 44       | R7                      |

| PA[14]   | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[14]<br>SCK_0<br>CS0_0<br>—<br>EIRQ[4]                | SIUL<br>DSPI_0<br>DSPI_0<br>—<br>SIUL | /0<br> /0<br> /0<br>         | Μ        | Tristate            | 19               | 19               | 28       | 42       | P6                      |

| PA[15]   | PCR[15] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[15]<br>CS0_0<br>SCK_0<br>—<br>WKPU[10] <sup>4</sup>  | SIUL<br>DSPI_0<br>DSPI_0<br>—<br>WKPU | /0<br> /0<br> /0<br>         | Μ        | Tristate            | 18               | 18               | 27       | 40       | R6                      |

| PB[0]    | PCR[16] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[16]<br>CAN0TX<br>—<br>—                              | SIUL<br>FlexCAN_0<br>                 | I/O<br>O<br>—                | М        | Tristate            | 14               | 14               | 23       | 31       | N3                      |

| PB[1]    | PCR[17] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[17]<br>—<br>—<br>—<br>WKPU[4] <sup>4</sup><br>CAN0RX | SIUL<br>—<br>—<br>WKPU<br>FlexCAN_0   | I/O<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | 15               | 15               | 24       | 32       | N1                      |

| PB[2]    | PCR[18] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[18]<br>LIN0TX<br>SDA<br>—                            | SIUL<br>LINFlex_0<br>I2C_0<br>—       | I/O<br>O<br>I/O<br>—         | М        | Tristate            | 64               | 64               | 100      | 144      | B2                      |

MPC5604B/C Microcontroller Data Sheet, Rev. 11

|          |         |                                 |                                                                             |                                                  |                              |          | uo                  |                  | Pir              | n num    | ber      |                         |

|----------|---------|---------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup> | Function                                                                    | Peripheral                                       | I/O direction <sup>2</sup>   | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PF[2]    | PCR[82] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[82]<br>E0UC[12]<br>CS0_2<br>—<br>ANS[10]                               | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC            | I/O<br>I/O<br>I/O<br>I       | J        | Tristate            |                  |                  |          | 57       | T10                     |

| PF[3]    | PCR[83] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[83]<br>E0UC[13]<br>CS1_2<br>—<br>ANS[11]                               | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC            | /O<br> /O<br>0<br>           | J        | Tristate            | _                | —                | _        | 58       | R10                     |

| PF[4]    | PCR[84] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[84]<br>E0UC[14]<br>CS2_2<br>—<br>ANS[12]                               | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC            | I/O<br>I/O<br>O<br>I         | J        | Tristate            | _                | _                | _        | 59       | N11                     |

| PF[5]    | PCR[85] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[85]<br>E0UC[22]<br>CS3_2<br>—<br>ANS[13]                               | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>ADC            | I/O<br>I/O<br>O<br>I         | J        | Tristate            | _                | _                | _        | 60       | P11                     |

| PF[6]    | PCR[86] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[86]<br>E0UC[23]<br>—<br><br>ANS[14]                                    | SIUL<br>eMIOS_0<br>—<br>ADC                      | /O<br> /O<br><br>            | J        | Tristate            | _                | _                | _        | 61       | T11                     |

| PF[7]    | PCR[87] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[87]<br>—<br>—<br>—<br>ANS[15]                                          | SIUL<br>—<br>—<br>—<br>ADC                       | I/O<br>—<br>—<br>—<br>I      | J        | Tristate            | _                | —                | _        | 62       | R11                     |

| PF[8]    | PCR[88] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[88]<br>CAN3TX <sup>14</sup><br>CS4_0<br>CAN2TX <sup>15</sup>           | SIUL<br>FlexCAN_3<br>DSPI_0<br>FlexCAN_2         | I/O<br>O<br>O                | М        | Tristate            |                  | _                |          | 34       | P1                      |

| PF[9]    | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[89]<br>—<br>CS5_0<br>—<br>CAN2RX <sup>15</sup><br>CAN3RX <sup>14</sup> | SIUL<br><br>DSPI_0<br><br>FlexCAN_2<br>FlexCAN_3 | I/O<br>—<br>0<br>—<br>I<br>I | S        | Tristate            |                  |                  |          | 33       | N2                      |

#### Table 6. Functional port pin descriptions (continued)

|                     |          | -                               |                                         |                                  |                            |          | u                      |                  | Pin              | num      | ber      |                         |

|---------------------|----------|---------------------------------|-----------------------------------------|----------------------------------|----------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin            | PCR      | Alternate function <sup>1</sup> | Function                                | Peripheral                       | I/O direction <sup>2</sup> | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PH[4]               | PCR[116] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[116]<br>E1UC[6]<br>—<br>—          | SIUL<br>eMIOS_1<br>—             | I/O<br>I/O<br>             | Μ        | Tristate               |                  |                  |          | 134      | A6                      |

| PH[5]               | PCR[117] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[117]<br>E1UC[7]<br>—<br>—          | SIUL<br>eMIOS_1<br>              | I/O<br>I/O<br>—            | S        | Tristate               |                  |                  |          | 135      | B6                      |

| PH[6]               | PCR[118] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[118]<br>E1UC[8]<br>—<br>MA[2]      | SIUL<br>eMIOS_1<br><br>ADC       | I/O<br>I/O<br>—<br>O       | М        | Tristate               |                  |                  |          | 136      | D5                      |

| PH[7]               | PCR[119] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[119]<br>E1UC[9]<br>CS3_2<br>MA[1]  | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | Μ        | Tristate               |                  |                  |          | 137      | C5                      |

| PH[8]               | PCR[120] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[120]<br>E1UC[10]<br>CS2_2<br>MA[0] | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | М        | Tristate               | l                | _                |          | 138      | A5                      |

| PH[9] <sup>9</sup>  | PCR[121] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[121]<br>—<br>TCK<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br><br>                | S        | Input, weak<br>pull-up | 60               | 60               | 88       | 127      | B8                      |

| PH[10] <sup>9</sup> | PCR[122] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[122]<br>—<br>TMS<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—         | S        | Input, weak<br>pull-up | 53               | 53               | 81       | 120      | B9                      |

| Table 6. F | unctional | port pin | descriptions | (continued) |

|------------|-----------|----------|--------------|-------------|

|            |           |          |              | (           |

<sup>1</sup> Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 00 → AF0; PCR.PA = 01 → AF1; PCR.PA = 10 → AF2; PCR.PA = 11 → AF3. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

<sup>2</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

<sup>3</sup> 208 MAPBGA available only as development package for Nexus2+

<sup>4</sup> All WKPU pins also support external interrupt capability. See wakeup unit chapter for further details.

<sup>5</sup> NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

<sup>6</sup> "Not applicable" because these functions are available only while the device is booting. Refer to BAM chapter of the reference manual for details.

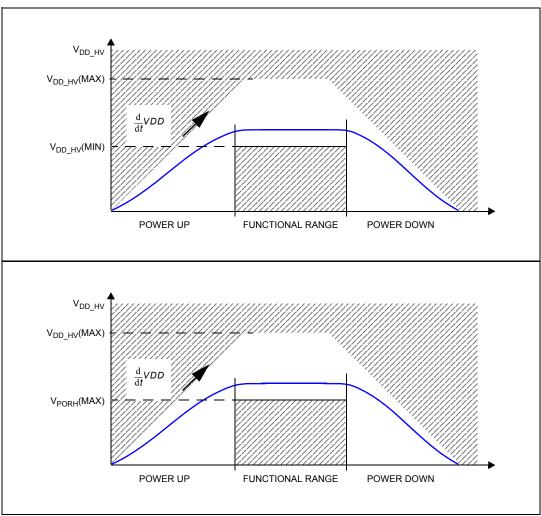

Figure 11.  $V_{DD HV}$  and  $V_{DD BV}$  maximum slope

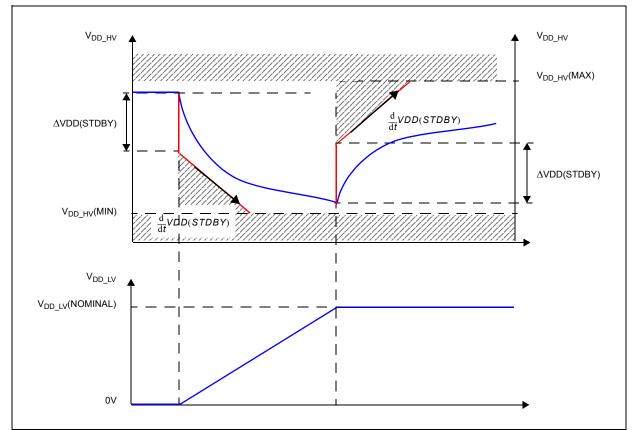

When STANDBY mode is used, further constraints are applied to the both  $V_{DD_HV}$  and  $V_{DD_BV}$  in order to guarantee correct regulator function during STANDBY exit. This is described on Figure 12.

STANDBY regulator constraints should normally be guaranteed by implementing equivalent of CSTDBY capacitance on application board (capacitance and ESR typical values), but would actually depend on exact characteristics of application external regulator.

| Table 26. | Voltage regul | lator electrica | l characteristics |

|-----------|---------------|-----------------|-------------------|

|           |               |                 |                   |

| Symbol                              |    | с | Parameter                                                           | Conditions <sup>1</sup>                                                             |                  |                  | Unit |       |  |

|-------------------------------------|----|---|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|------|-------|--|

| Symbol                              |    | C | Faiametei                                                           | Conditions                                                                          | Min              | Тур              | Max  |       |  |

| C <sub>REGn</sub>                   | SR |   | Internal voltage regulator external capacitance                     | —                                                                                   | 200              | _                | 500  | nF    |  |

| R <sub>REG</sub>                    | SR |   | Stability capacitor equivalent serial resistance                    | Range:<br>10 kHz to 20 MHz                                                          | _                |                  | 0.2  | Ω     |  |

| C <sub>DEC1</sub>                   | SR |   | Decoupling capacitance <sup>2</sup> ballast                         | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 4.5 V to 5.5 V | 100 <sup>3</sup> | 470 <sup>4</sup> |      | nF    |  |

|                                     |    |   |                                                                     | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 3 V to 3.6 V   | 400              |                  |      |       |  |

| C <sub>DEC2</sub>                   | SR |   | Decoupling capacitance regulator supply                             | V <sub>DD</sub> /V <sub>SS</sub> pair                                               | 10               | 100              | _    | nF    |  |

| $\frac{\mathrm{d}}{\mathrm{d}t}VDD$ | SR | — | Maximum slope on V <sub>DD</sub>                                    |                                                                                     |                  | _                | 250  | mV/µs |  |

| $ \Delta_{VDD(STDBY)} $             | SR |   | Maximum instant variation on V <sub>DD</sub><br>during standby exit |                                                                                     |                  |                  | 30   | mV    |  |

| Symbol                                                                                                                |    | с | Parameter                                                        | Conditions <sup>1</sup>                               |      | Value |                  | Unit  |

|-----------------------------------------------------------------------------------------------------------------------|----|---|------------------------------------------------------------------|-------------------------------------------------------|------|-------|------------------|-------|

| Cymbol                                                                                                                |    | C | Falanielei                                                       | Conditions                                            | Min  | Тур   | Max              | Onic  |

| $\frac{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }{\left \frac{\mathrm{d}}{\mathrm{d}t}VDD(STDBY)\right }$ | SR |   | Maximum slope on V <sub>DD</sub> during standby exit             |                                                       | —    |       | 15               | mV/µs |

| V <sub>MREG</sub>                                                                                                     | СС | Т | Main regulator output voltage                                    | Before exiting from reset                             | _    | 1.32  |                  | V     |

|                                                                                                                       |    | Ρ |                                                                  | After trimming                                        | 1.16 | 1.28  | —                |       |

| I <sub>MREG</sub>                                                                                                     | SR | _ | Main regulator current provided to $V_{DD\_LV}$ domain           | _                                                     | -    |       | 150              | mA    |

| I <sub>MREGINT</sub>                                                                                                  | СС | D | Main regulator module current                                    | I <sub>MREG</sub> = 200 mA                            | _    |       | 2                | mA    |

|                                                                                                                       |    |   | consumption                                                      | I <sub>MREG</sub> = 0 mA                              | _    |       | 1                |       |

| V <sub>LPREG</sub>                                                                                                    | СС | Ρ | Low power regulator output voltage                               | After trimming                                        | 1.16 | 1.28  | _                | V     |

| I <sub>LPREG</sub>                                                                                                    | SR |   | Low power regulator current provided to $V_{DD_LV}$ domain       | _                                                     | —    |       | 15               | mA    |

| I <sub>LPREGINT</sub>                                                                                                 | СС | D | Low power regulator module current consumption                   | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | —    |       | 600              | μA    |

|                                                                                                                       |    |   |                                                                  | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _    | 5     |                  | -     |

| V <sub>ULPREG</sub>                                                                                                   | СС | Ρ | Ultra low power regulator output voltage                         | After trimming                                        | 1.16 | 1.28  | _                | V     |

| IULPREG                                                                                                               | SR | — | Ultra low power regulator current provided to $V_{DD_LV}$ domain | _                                                     | _    |       | 5                | mA    |

| IULPREGINT                                                                                                            | СС | D | Ultra low power regulator module current consumption             | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C | —    |       | 100              | μA    |

|                                                                                                                       |    |   |                                                                  | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C | -    | 2     | _                |       |

| I <sub>DD_BV</sub>                                                                                                    | СС | D | In-rush average current on $V_{DD\_BV}$ during power-up $^{5}$   |                                                       | -    |       | 300 <sup>6</sup> | mA    |

Table 26. Voltage regulator electrical characteristics (continued)

$^1$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified

- $^2$  This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

- $^3\,$  This value is acceptable to guarantee operation from 4.5 V to 5.5 V

- <sup>4</sup> External regulator and capacitance circuitry must be capable of providing I<sub>DD\_BV</sub> while maintaining supply V<sub>DD\_BV</sub> in operating range.

- <sup>5</sup> In-rush average current is seen only for short time (maximum 20 µs) during power-up and on standby exit. It is dependant on the sum of the C<sub>REGn</sub> capacitances.

- <sup>6</sup> The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

The  $|\Delta_{VDD(STDBY)}|$  and dVDD(STDBY)/dt system requirement can be used to define the component used for the V<sub>DD</sub> supply generation. The following two examples describe how to calculate capacitance size:

#### Example 1. No regulator (worst case)

The  $|\Delta_{VDD(STDBY)}|$  parameter can be seen as the  $V_{DD}$  voltage drop through the ESR resistance of the regulator stability capacitor when the  $I_{DD_BV}$  current required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the maximum equivalent resistance ESR<sub>STDBY</sub>(MAX) of the total capacitance on the  $V_{DD}$  supply:

$\text{ESR}_{\text{STDBY}}(\text{MAX}) = |\Delta_{\text{VDD}(\text{STDBY})}|/\text{I}_{\text{DD} \text{ BV}} = (30 \text{ mV})/(300 \text{ mA}) = 0.1\Omega^{-1}$

The dVDD(STDBY)/dt parameter can be seen as the  $V_{DD}$  voltage drop at the capacitance pin (excluding ESR drop) while providing the  $I_{DD_BV}$  supply required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the minimum equivalent capacitance  $C_{STDBY}(MIN)$  of the total capacitance on the  $V_{DD}$  supply:

$C_{STDBY}(MIN) = I_{DD BV}/dVDD(STDBY)/dt = (300 mA)/(15 mV/\mu s) = 20 \mu F$

This configuration is a worst case, with the assumption no regulator is available.

#### **Example 2. Simplified regulator**

The regulator should be able to provide significant amount of the current during the standby exit process. For example, in case of an ideal voltage regulator providing 200 mA current, it is possible to recalculate the equivalent  $ESR_{STDBY}(MAX)$  and  $C_{STDBY}(MIN)$  as follows:

$ESR_{STDBY}(MAX) = |\Delta_{VDD(STDBY)}|/(I_{DD BV} - 200 mA) = (30 mV)/(100 mA) = 0.3 \Omega$

$C_{\text{STDBY}}(\text{MIN}) = (I_{\text{DD} BV} - 200 \text{ mA})/d\text{VDD}(\text{STDBY})/dt = (300 \text{ mA} - 200 \text{ mA})/(15 \text{ mV/}\mu\text{s}) = 6.7 \mu\text{F}$

In case optimization is required,  $C_{\text{STDBY}}(\text{MIN})$  and  $\text{ESR}_{\text{STDBY}}(\text{MAX})$  should be calculated based on the regulator characteristics as well as the board  $V_{\text{DD}}$  plane characteristics.

### 3.17.2 Low voltage detector electrical characteristics

The device implements a Power-on Reset (POR) module to ensure correct power-up initialization, as well as four low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD}$  LV voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

#### NOTE

When enabled, power domain No. 2 is monitored through LVDLVBKP.

<sup>1.</sup> Based on typical time for standby exit sequence of 20 µs, ESR(MIN) can actually be considered at ~50 kHz.

| Symbo     | Symbol |   | Parameter                                                                   | Conditions                               |         | Value   |     | Unit   |

|-----------|--------|---|-----------------------------------------------------------------------------|------------------------------------------|---------|---------|-----|--------|

| Gymbo     | ,,     | С | r arameter                                                                  |                                          |         | Max     | Ome |        |

| P/E       | CC     | С | Number of program/erase cycles                                              | 16 KB blocks                             | 100,000 | —       | _   | cycles |

|           |        |   | per block over the operating temperature range (T <sub>1</sub> )            | 32 KB blocks                             | 10,000  | 100,000 | —   |        |

|           |        |   |                                                                             | 128 KB blocks                            | 1,000   | 100,000 | _   |        |

| Retention | СС     | С | Minimum data retention at 85 °C<br>average ambient temperature <sup>1</sup> | Blocks with<br>0–1,000 P/E cycles        | 20      | —       | _   | years  |

|           |        |   |                                                                             | Blocks with<br>1,001–10,000 P/E cycles   | 10      | —       | _   |        |

|           |        |   |                                                                             | Blocks with<br>10,001–100,000 P/E cycles | 5       | —       | —   |        |

#### Table 30. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

ECC circuitry provides correction of single bit faults and is used to improve further automotive reliability results. Some units will experience single bit corrections throughout the life of the product with no impact to product reliability.

#### Table 31. Flash read access timing

| Symbol            |    | С | Parameter                           | Conditions <sup>1</sup> | Мах | Unit |

|-------------------|----|---|-------------------------------------|-------------------------|-----|------|

| f <sub>READ</sub> | СС | Ρ | Maximum frequency for Flash reading | 2 wait states           | 64  | MHz  |

|                   |    | С |                                     | 1 wait state            | 40  |      |

|                   |    | С |                                     | 0 wait states           | 20  |      |

$1 V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

### 3.19.2 Flash power supply DC characteristics

Table 32 shows the power supply DC characteristics on external supply.

#### Table 32. Flash memory power supply DC electrical characteristics

| Symb                            | Symbol |   | Parameter Conditions <sup>1</sup>                                                                |                                                                                                              | Value |     |     | Unit |  |

|---------------------------------|--------|---|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|--|

| Symbol                          |        | С | i didineter                                                                                      | Conditions                                                                                                   | Min   | Тур | Max | onic |  |

| I <sub>FREAD</sub> <sup>2</sup> | CC     | D | Sum of the current consumption on VDD_HV and VDD_BV on read access                               | Code flash memory module read $f_{CPU} = 64 \text{ MHz}^3$                                                   | _     | 15  | 33  | mA   |  |

|                                 |        |   |                                                                                                  | Data flash memory module read<br>f <sub>CPU</sub> = 64 MHz <sup>3</sup>                                      |       | 15  | 33  |      |  |

| I <sub>FMOD</sub> <sup>2</sup>  | СС     |   | Sum of the current consumption on<br>VDD_HV and VDD_BV on matrix<br>modification (program/erase) | Program/Erase ongoing while<br>reading code flash memory<br>registers f <sub>CPU</sub> = 64 MHz <sup>3</sup> | _     | 15  | 33  | mA   |  |

|                                 |        |   |                                                                                                  | Program/Erase ongoing while<br>reading data flash memory<br>registers f <sub>CPU</sub> = 64 MHz <sup>3</sup> |       | 15  | 33  |      |  |

| Cumha                            |    | с           | Dovoroator                                        | Conditions <sup>1</sup>                                                |                     | Value |                      | Unit |

|----------------------------------|----|-------------|---------------------------------------------------|------------------------------------------------------------------------|---------------------|-------|----------------------|------|

| Symbo                            | 1  | C Parameter |                                                   | Conditions                                                             | Min Typ Max         |       | Max                  |      |

| f <sub>FXOSC</sub>               | SR |             | Fast external crystal<br>oscillator frequency     | _                                                                      | 4.0                 | —     | 16.0                 | MHz  |

| 9 <sub>mFXOSC</sub>              | СС | С           | Fast external crystal oscillator transconductance | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>OSCILLATOR_MARGIN = 0 | 2.2                 | _     | 8.2                  | mA/V |

|                                  | СС | Ρ           | *                                                 | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0<br>OSCILLATOR_MARGIN = 0 | 2.0                 | _     | 7.4                  |      |

|                                  | СС | С           | *                                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>OSCILLATOR_MARGIN = 1 | 2.7                 | _     | 9.7                  |      |

|                                  | СС | С           | *                                                 | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0<br>OSCILLATOR_MARGIN = 1 | 2.5                 | _     | 9.2                  |      |

| V <sub>FXOSC</sub>               | СС | Т           | Oscillation amplitude at EXTAL                    | f <sub>OSC</sub> = 4 MHz,<br>OSCILLATOR_MARGIN = 0                     | 1.3                 | —     | —                    | V    |

|                                  |    |             |                                                   | f <sub>OSC</sub> = 16 MHz,<br>OSCILLATOR_MARGIN = 1                    | 1.3                 | —     | —                    |      |

| V <sub>FXOSCOP</sub>             | СС | С           | Oscillation operating point                       | —                                                                      | —                   | 0.95  | —                    | V    |

| I <sub>FXOSC</sub> <sup>,2</sup> | СС | Т           | Fast external crystal oscillator consumption      | _                                                                      | —                   | 2     | 3                    | mA   |

| t <sub>FXOSCSU</sub>             | СС | Т           | Fast external crystal<br>oscillator start-up time | f <sub>OSC</sub> = 4 MHz,<br>OSCILLATOR_MARGIN = 0                     | —                   | _     | 6                    | ms   |

|                                  |    |             |                                                   | f <sub>OSC</sub> = 16 MHz,<br>OSCILLATOR_MARGIN = 1                    | —                   |       | 1.8                  |      |

| V <sub>IH</sub>                  | SR | Ρ           | Input high level CMOS<br>(Schmitt Trigger)        | Oscillator bypass mode                                                 | 0.65V <sub>DD</sub> | —     | V <sub>DD</sub> +0.4 | V    |

| V <sub>IL</sub>                  | SR | Ρ           | Input low level CMOS<br>(Schmitt Trigger)         | Oscillator bypass mode                                                 | -0.4                | _     | 0.35V <sub>DD</sub>  | V    |

| Table 38. Fast extern | nal crystal oscillator | (4 to 16 MHz | ) electrical characteristics |

|-----------------------|------------------------|--------------|------------------------------|

|                       | iai orgotar ocomator   | (+           |                              |

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

<sup>2</sup> Stated values take into account only analog module consumption but not the digital contributor (clock tree and enabled peripherals)

## 3.22 Slow external crystal oscillator (32 kHz) electrical characteristics

The device provides a low power oscillator/resonator driver.

- $V_{DD} = 3.3 \text{ V} \pm 10\% \text{ / } 5.0 \text{ V} \pm 10\%, \text{ } T_{A} = -40 \text{ to } 125 \text{ °C}, \text{ unless otherwise specified.}$   $T_{his} \text{ does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is }$ ON.

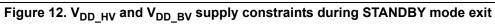

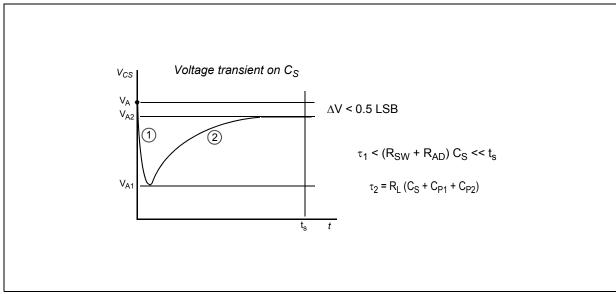

Figure 21. Input equivalent circuit (extended channels)

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit in Figure 20): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Figure 22. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

MPC5604B/C Microcontroller Data Sheet, Rev. 11

| Symbol           |    | ~                            | Demonster                                    | Conditional                                           |        |     | Value     |     |      |

|------------------|----|------------------------------|----------------------------------------------|-------------------------------------------------------|--------|-----|-----------|-----|------|

|                  |    | C Parameter                  |                                              | Conditions <sup>1</sup>                               |        | Min | n Typ Max |     | Unit |

| C <sub>P3</sub>  | СС | D                            | ADC input pin<br>capacitance 3               | _                                                     |        |     | -         | 1   | pF   |

| R <sub>SW1</sub> | СС | D                            | Internal resistance of<br>analog source      | _                                                     |        | —   | -         | 3   | kΩ   |

| $R_{SW2}$        | СС | D                            | Internal resistance of<br>analog source      |                                                       |        | —   | -         | 2   | kΩ   |

| R <sub>AD</sub>  | СС | D                            | Internal resistance of<br>analog source      | —                                                     |        |     | -         | 2   | kΩ   |

| I <sub>INJ</sub> |    | injection on one             | V <sub>DD</sub> =<br>3.3 V ± 10%             | -5                                                    | -      | 5   | mA        |     |      |

|                  |    | different from the converted | V <sub>DD</sub> =<br>5.0 V ± 10%             | -5                                                    | -      | 5   |           |     |      |

| INL              | СС | Т                            | Absolute value for<br>integral non-linearity | No overload                                           |        |     | 0.5       | 1.5 | LSB  |

| DNL              | СС | Т                            | Absolute differential non-linearity          | No overload                                           |        | —   | 0.5       | 1.0 | LSB  |

| E <sub>O</sub>   | СС | Т                            | Absolute offset error                        | -                                                     |        | —   | 0.5       |     | LSB  |

| E <sub>G</sub>   | СС | Т                            | Absolute gain error                          | -                                                     | _      | —   | 0.6       | —   | LSB  |

| TUEp             | СС | Ρ                            | Total unadjusted error <sup>7</sup>          | 7 Without current injection<br>With current injection |        | -2  | 0.6       | 2   | LSB  |

|                  |    | Т                            | for precise channels,<br>input only pins     |                                                       |        | -3  |           | 3   |      |

| TUEx             |    |                              | injection                                    | -3                                                    | 1      | 3   | LSB       |     |      |

|                  |    | Т                            | for extended channel                         | With current inje                                     | ection | -4  |           | 4   |      |

| Table 45. ADC conversion | n characteristics | (continued) |

|--------------------------|-------------------|-------------|

|--------------------------|-------------------|-------------|

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 to 125 °C, unless otherwise specified.

$^2$  Analog and digital V<sub>SS</sub> **must** be common (to be tied together externally).

<sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

<sup>4</sup> Duty cycle is ensured by using system clock without prescaling. When ADCLKSEL = 0, the duty cycle is ensured by internal divider by 2.

<sup>5</sup> During the sampling time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_s$ . After the end of the sampling time  $t_s$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_s$  depend on programming.

<sup>6</sup> This parameter does not include the sampling time t<sub>s</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

<sup>7</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

<sup>3</sup> During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e.,  $(41 + 5) * f_{periph}$ .

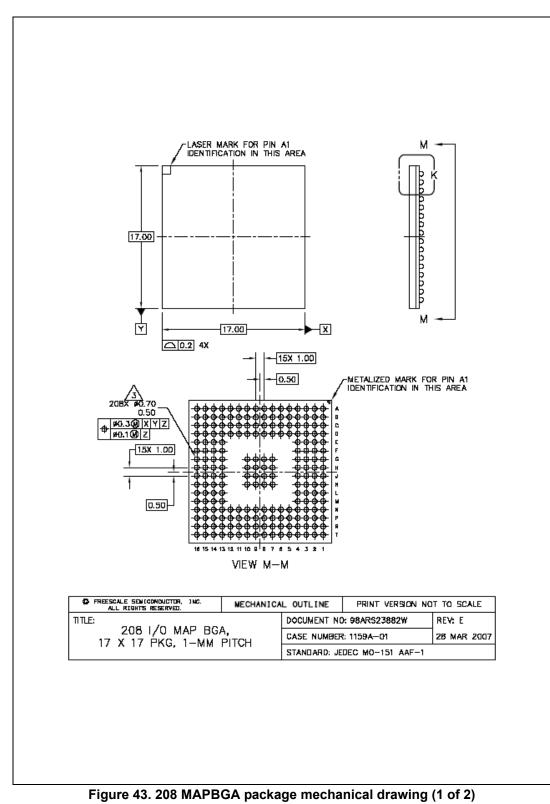

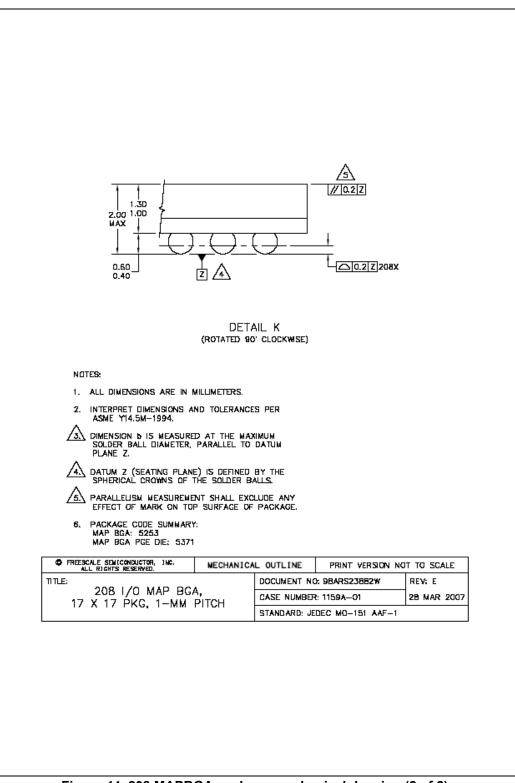

### 4.1.4 208 MAPBGA

Figure 44. 208 MAPBGA package mechanical drawing (2 of 2)

#### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 15-Mar-2010 | In the "Introduction" section, relocated a note.<br>In the "MPC5604B/C device comparison" table, added footnote regarding SCI and CAN.<br>In the "Absolute maximum ratings" table, removed the min value of V <sub>IN</sub> relative to V <sub>DD</sub> .<br>In the "Recommended operating conditions (3.3 V)" table:<br>* T <sub>A</sub> C-Grade Part, TJ C-Grade Part, TA V-Grade Part, TJ V-Grade Part, TA M-Grade Part, TJ M-Grade Part;<br>added new rows.<br>* TV <sub>DD</sub> : made single row.<br>In the "LQFP thermal characteristics" table, added more rows.<br>Removed '208 MAPBGA thermal characteristics" table.<br>In the "I/O consumption" table:<br>* Removed I <sub>DVNSEG</sub> row.<br>* Added "I/O weight" table.<br>In the "Voltage regulator electrical characteristics" table:<br>* Updated the values.<br>* Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> .<br>* Added a note about I <sub>DD_BC</sub> .<br>In the "Low voltage monitor electrical characteristics" table:<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>DORH</sub> value.<br>Entirely updated the "Flash power supply DC electrical characteristics" table.<br>In the "Slow external crystal oscillator (32 kHz) electrical characteristics" table.<br>In the "Slow external crystal oscillator (32 kHz) electrical characteristics" table:<br>Nemoved g <sub>INXOSC</sub> row.<br>* Inserted values of I <sub>SXOSCEIAS</sub> .<br>Entirely updated the "Fast internal RC oscillator (16 MHz) electrical characteristics" table:<br>In the "ADC conversion characteristics" table: updated the "DSPI characteristics" table.<br>In the "ADC conversion characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the "DSPI characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the note shout the condition from "Flash read access timing" table<br>Removed the note shout the condition from "Flash read access timing" table<br>Remov |

#### Table 50. Revision history (continued)

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | 15 Oct 2012 | <ul> <li>Table 1 (MPC5604B/C device comparison), added footnote for MPC5603BxLH and MPC5604BxLH about FlexCAN availability.</li> <li>Table 3 (MPC5604B/C series block summary), replaced "System watchdog timer" with "Software watchdog timer" and specified AUTOSAR (Automotive Open System Architecture)</li> <li>Table 6 (Functional port pin descriptions): replaced footnote "Available only on MPC560xC versions and MPC5604B 208 MAPBGA devices" with "Available only on MPC560xC versions, MPC5604B 208 MAPBGA devices", replaced VDD with VDD_HV</li> <li>Figure 10 (Voltage regulator capacitance connection), updated pin name apperence</li> <li>Renamed Figure 11 (V<sub>DD_HV</sub> and V<sub>DD_BV</sub> maximum slope) (was "VDD and VDD_BV maximum slope")</li> <li>Renamed Figure 12 (V<sub>DD_HV</sub> and V<sub>DD_BV</sub> supply constraints during STANDBY mode exit) (was "VDD and VDD_BV supply constraints during STANDBY mode exit)</li> <li>Table 13 (Recommended operating conditions (3.3 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Table 14 (Recommended operating conditions (5.0 V)), added minimum value of T<sub>VDD</sub> and footnote about it.</li> <li>Section 3.17.1, "Voltage regulator electrical characteristics: replaced "slew rate of V<sub>DD</sub>/V<sub>DD_BV</sub>" with "slew rate of both V<sub>DD_HV</sub> and V<sub>DD_BV</sub> in order to guarantee correct regulator functionality during STANDBY exit." with "When STANDBY mode is used, further constraints apply to the V<sub>DD</sub>/N<sub>D_BV</sub> in order to guarantee correct regulator function during STANDBY exit."</li> <li>Table 28 (Power consumption on VDD_BV and VDD_HV), updated footnotes of I<sub>DDMAX</sub> and I<sub>DDRUN</sub> stating that both currents are drawn only from the V<sub>DD_BV</sub> pin.</li> <li>Table 46 (On-chip peripherals current consumption), in the paremeter column replaced V<sub>DD_BV</sub> and V<sub>DD_HV</sub> respectively with VDD_BV and VDD_HV.</li> <li>Table 46 (On-chip peripherals current consumption), in the paremeter column replaced V<sub>DD_BV</sub> and V<sub>DD_HV</sub> respectively with VDD_BV and VDD_HV.</li> </ul> |

| 11       | 14 Nov 2012 | In the cover feature list:<br>added "and ECC" at the end of "Up to 512 KB on-chip code flash supported with the<br>flash controller"<br>added "with ECC" at the end of "Up to 48 KB on-chip SRAM"<br>Table 13 (Recommended operating conditions (3.3 V)), removed minimum value of $T_{VDD}$<br>and relative footnote.<br>Table 14 (Recommended operating conditions (5.0 V)), removed minimum value of $T_{VDD}$<br>and relative footnote.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |