Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 10MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | PWM, WDT                                               |

| Number of I/O              | 13                                                     |

| Program Memory Size        | 1KB (1K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 64 x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                     |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8e00110pec |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION** (Continued)

ing real-time tasks such as counting/timing and I/O data communications.

Note: All signals with an overline, "", are active Low\_For example, B/W (WORD is active Low, only); B/W (BYTE is active Low, only). Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | $V_{SS}$        |

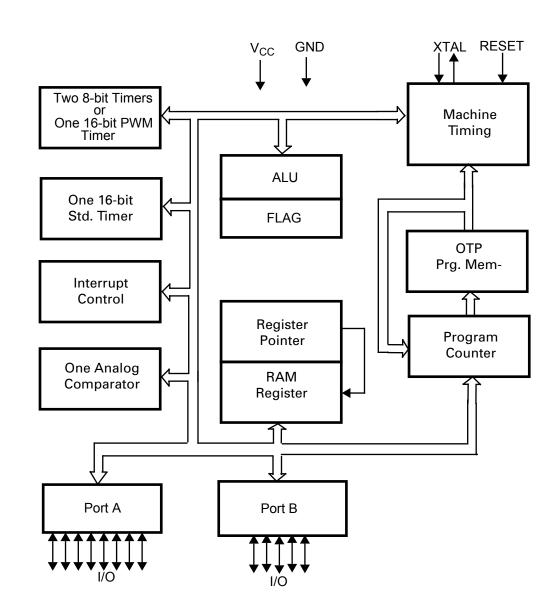

Figure 1. Functional Block Diagram

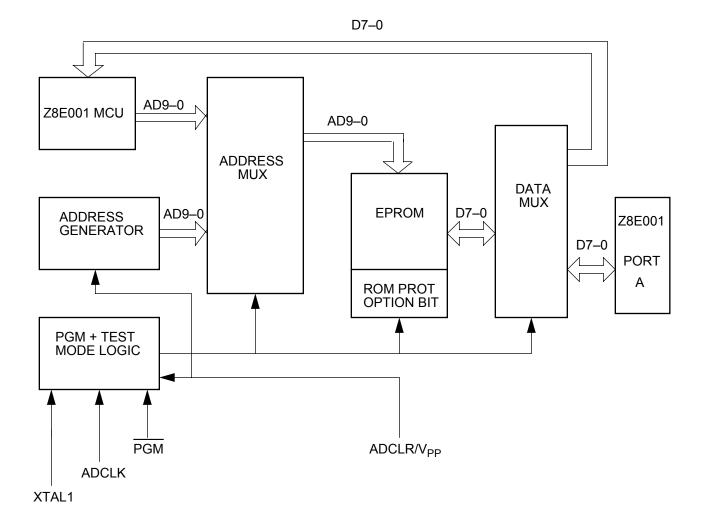

Figure 2. EPROM Programming Mode Block Diagram

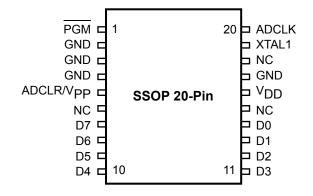

Figure 6. 20-Pin SSOP Pin Identification/EPROM Programming Mode

| EPROM P | rogramming Mode       |                       |              |  |

|---------|-----------------------|-----------------------|--------------|--|

| Pin #   | Symbol                | Function              | Direction    |  |

| 1       | PGM                   | Prog Mode             | Input        |  |

| 2–4     | GND                   | Ground                |              |  |

| 5       | ADCLR/V <sub>PP</sub> | Clear Clk./Prog Volt. | Input        |  |

| 6       | NC                    | No Connection         |              |  |

| 7–10    | D7–D4                 | Data 7,6,5,4          | Input/Output |  |

| 11–14   | D3-D0                 | Data 3,2,1,0          | Input/Output |  |

| 15      | NC                    | No Connection         |              |  |

| 16      | V <sub>DD</sub>       | Power Supply          |              |  |

| 17      | GND                   | Ground                |              |  |

| 18      | NC                    | No Connection         |              |  |

| 19      | XTAL1                 | 1MHz Clock            | Input        |  |

| 20      | ADCLK                 | Address Clock         | Input        |  |

## ABSOLUTE MAXIMUM RATINGS

| Parameter                                               | Min  | Max                | Units | Note |

|---------------------------------------------------------|------|--------------------|-------|------|

| Ambient Temperature under Bias                          | -40  | +105               | С     |      |

| Storage Temperature                                     | -65  | +150               | С     |      |

| Voltage on any Pin with Respect to V <sub>SS</sub>      | -0.6 | +7                 | V     | 1    |

| Voltage on $V_{DD}$ Pin with Respect to $V_{SS}$        | -0.3 | +7                 | V     |      |

| Voltage on RESET Pin with Respect to V <sub>SS</sub>    | -0.6 | V <sub>DD</sub> +1 | V     | 2    |

| Total Power Dissipation                                 |      | 880                | mW    |      |

| Maximum Allowable Current out of V <sub>SS</sub>        |      | 80                 | mA    |      |

| Maximum Allowable Current into V <sub>DD</sub>          |      | 80                 | mA    |      |

| Maximum Allowable Current into an Input Pin             | -600 | +600               | mA    | 3    |

| Maximum Allowable Current into an Open-Drain Pin        | -600 | +600               | mA    | 4    |

| Maximum Allowable Output Current Sunk by Any I/O Pin    |      | 25                 | mA    |      |

| Maximum Allowable Output Current Sourced by Any I/O Pin |      | 25                 | mA    |      |

| Maximum Allowable Output Current Sunk by Port A         |      | 40                 | mA    |      |

| Maximum Allowable Output Current Sourced by Port A      |      | 40                 | mA    |      |

| Maximum Allowable Output Current Sunk by Port B         |      | 40                 | mA    |      |

| Maximum Allowable Output Current Sourced by Port B      |      | 40                 | mA    |      |

Notes:

1. Applies to all pins except the  $\overline{\text{RESET}}$  pin and where otherwise noted.

2. There is no input protection diode from pin to  $V_{\text{DD}}$ .

3. Excludes XTAL pins.

4. Device pin is not at an output Low state.

Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. This rating is a stress rating only. Functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period can affect device reliability. Total power dissipation should not exceed 880 mW for the package. Power dissipation is calculated as follows:

$\begin{array}{l} \mbox{Total Power Dissipation} \ = \ V_{DD} \ x \ [I_{DD} \ - \ (sum \ of \ I_{OH})] \\ \ + \ sum \ of \ [(V_{DD} \ - \ V_{OH}) \ x \ I_{OH}] \\ \ + \ sum \ of \ (V_{0L} \ x \ I_{0L}) \end{array}$

# STANDARD TEST CONDITIONS

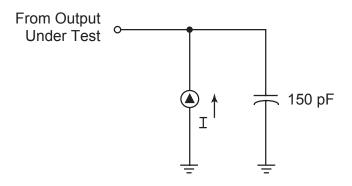

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 7).

Figure 7. Test Load Diagram

# CAPACITANCE

$T_A = 25^{\circ}C$ ,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

## DC ELECTRICAL CHARACTERISTICS

| Table 1. | DC | Electrical | Characteristics |

|----------|----|------------|-----------------|

|          | _  |            |                 |

|                     |                              |                              |                      | C to +70°C<br>emperatures |                                |       |                                       |       |

|---------------------|------------------------------|------------------------------|----------------------|---------------------------|--------------------------------|-------|---------------------------------------|-------|

| Sym                 | Parameter                    | V <sub>CC</sub> <sup>1</sup> | Min                  | Мах                       | Typical <sup>2</sup><br>@ 25°C | Units | Conditions                            | Notes |

| V <sub>CH</sub>     | Clock Input High<br>Voltage  | 3.5V                         | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.3      | 1.3                            | V     | Driven by External<br>Clock Generator |       |

|                     | -                            | 5.5V                         | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.3      | 2.5                            | V     | Driven by External<br>Clock Generator |       |

| V <sub>CL</sub>     | Clock Input Low<br>Voltage   | 3.5V                         | V <sub>SS</sub> -0.3 | 0.2V <sub>CC</sub>        | 0.7                            | V     | Driven by External<br>Clock Generator |       |

|                     |                              | 5.5V                         | V <sub>SS</sub> -0.3 | $0.2V_{CC}$               | 1.5                            | V     | Driven by External<br>Clock Generator |       |

| V <sub>IH</sub>     | Input High Voltage           | 3.5V                         | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.3      | 1.3                            | V     |                                       |       |

|                     | 1 0 0                        | 5.5V                         | 0.7V <sub>CC</sub>   | V <sub>CC</sub> +0.3      | 2.5                            | V     |                                       |       |

| V <sub>IL</sub>     | Input Low Voltage            | 3.5V                         | V <sub>SS</sub> -0.3 | 0.2V <sub>CC</sub>        | 0.7                            | V     |                                       |       |

|                     |                              | 5.5V                         | V <sub>SS</sub> -0.3 | 0.2V <sub>CC</sub>        | 1.5                            | V     |                                       |       |

| V <sub>OH</sub>     | Output High Voltage          | 3.5V                         | V <sub>CC</sub> –0.4 |                           | 3.1                            | V     | I <sub>OH</sub> = –2.0 mA             |       |

|                     |                              | 5.5V                         | V <sub>CC</sub> -0.4 |                           | 4.8                            | V     | I <sub>OH</sub> = -2.0 mA             |       |

| V <sub>OL1</sub>    | Output Low Voltage           | 3.5V                         |                      | 0.6                       | 0.2                            | V     | I <sub>OL</sub> = +4.0 mA             |       |

|                     |                              | 5.5V                         |                      | 0.4                       | 0.1                            | V     | I <sub>OL</sub> = +4.0 mA             |       |

| V <sub>OL2</sub>    | Output Low Voltage           | 3.5V                         |                      | 1.2                       | 0.5                            | V     | I <sub>OL</sub> = +6 mA               |       |

|                     |                              | 5.5V                         |                      | 1.2                       | 0.5                            | V     | I <sub>OL</sub> = +12 mA              |       |

| V <sub>RH</sub>     | Reset Input High             | 3.5V                         | $0.5V_{CC}$          | V <sub>CC</sub>           | 1.1                            | V     |                                       |       |

|                     | Voltage                      | 5.5V                         | $0.5V_{CC}$          | V <sub>CC</sub>           | 2.2                            | V     |                                       |       |

| V <sub>RL</sub>     | Reset Input Low              | 3.5V                         | V <sub>SS</sub> –0.3 | $0.2V_{CC}$               | 0.9                            | V     |                                       |       |

|                     | Voltage                      | 5.5V                         | V <sub>SS</sub> -0.3 | 0.2V <sub>CC</sub>        | 1.4                            | V     |                                       |       |

| V <sub>OFFSET</sub> | Comparator Input             | 3.5V                         |                      | 25.0                      | 10.0                           | mV    |                                       |       |

|                     | Offset Voltage               | 5.5V                         |                      | 25.0                      | 10.0                           | mV    |                                       |       |

| I <sub>IL</sub>     | Input Leakage                | 3.5V                         | -1.0                 | 2.0                       | 0.064                          | mA    | $V_{IN}$ = 0V, $V_{CC}$               |       |

|                     |                              | 5.5V                         | -1.0                 | 2.0                       | 0.064                          | mA    | $V_{IN}$ = 0V, $V_{CC}$               |       |

| I <sub>OL</sub>     | Output Leakage               | 3.5V                         | -1.0                 | 2.0                       | 0.114                          | μA    | $V_{IN} = 0V, V_{CC}$                 |       |

|                     |                              | 5.5V                         | -1.0                 | 2.0                       | 0.114                          | μA    | $V_{IN}$ = 0V, $V_{CC}$               |       |

| V <sub>ICR</sub>    | Comparator Input             | 3.5V                         | V <sub>SS</sub> -0.3 | V <sub>CC</sub> -1.0      |                                | V     |                                       | 3     |

|                     | Common Mode<br>Voltage Range | 5.5V                         | V <sub>SS</sub> -0.3 | V <sub>CC</sub> -1.0      |                                | V     |                                       | 3     |

| I <sub>IR</sub>     | Reset Input Current          | 3.5V                         | -10                  | -60                       | -30                            | μA    |                                       |       |

|                     |                              | 5.5V                         | -20                  | -180                      | -100                           | μA    |                                       |       |

|                     |                              |                              |                      |                           |                                |       |                                       |       |

|                  |                 |                              | ~   | C to +105°C<br>emperatures | Typical <sup>2</sup> |       |                                                             |       |

|------------------|-----------------|------------------------------|-----|----------------------------|----------------------|-------|-------------------------------------------------------------|-------|

| Sym              | Parameter       | V <sub>CC</sub> <sup>1</sup> | Min | Max                        | @ 25°C               | Units | Conditions                                                  | Notes |

| I <sub>CC</sub>  | Supply Current  | 4.5V                         |     | 7.0                        | 4.0                  | mA    | @ 10 MHz                                                    | 4,5   |

|                  |                 | 5.5V                         |     | 7.0                        | 4.0                  | mA    | @ 10 MHz                                                    | 4,5   |

| I <sub>CC1</sub> | Standby Current | 4.5V                         |     | 2.0                        | 1.0                  | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 10 MHz | 4,5   |

|                  |                 | 5.5V                         |     | 2.0                        | 1.0                  | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 10 MHz | 4,5   |

| I <sub>CC2</sub> | Standby Current | 4.5V                         |     | 700                        | 250                  | nA    | STOP Mode V <sub>IN</sub><br>= 0V,V <sub>CC</sub>           | 6     |

|                  |                 | 5.5V                         |     | 700                        | 250                  | nA    | STOP Mode V <sub>IN</sub><br>= 0V,V <sub>CC</sub>           | 6     |

#### Notes:

1. The V<sub>CC</sub> voltage specification of 4.5V and 5.5V guarantees 5.0V ±0.5V. 2. Typical values are measured at V<sub>CC</sub> = 3.3V and V<sub>CC</sub> = 5.0V; V<sub>SS</sub> = 0V = GND.

3. For analog comparator input when analog comparator is enabled.

4. All outputs unloaded and all inputs are at  $V_{CC} \text{ or } V_{SS}$  level.

5. CL1 = CL2 = 22 pF.

6. Same as note 4 except inputs at  $V_{CC}$ .

## **AC ELECTRICAL CHARACTERISTICS**

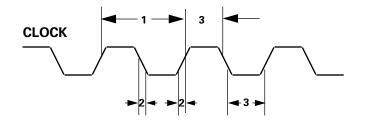

#### Table 3. Additional Timing

|    |         |                                 | T <sub>A</sub> = 0°C to +70°C<br>T <sub>A</sub> = -40°C to +105°C<br>@ 10 MHz |      |      |       |       |  |  |  |  |

|----|---------|---------------------------------|-------------------------------------------------------------------------------|------|------|-------|-------|--|--|--|--|

| No | Symbol  | Parameter                       | V <sub>CC</sub> <sup>1</sup>                                                  | Min  | Мах  | Units | Notes |  |  |  |  |

| 1  | ТрС     | Input Clock Period              | 3.5V                                                                          | 100  | DC   | ns    | 2     |  |  |  |  |

|    |         |                                 | 5.5V                                                                          | 100  | DC   | ns    | 2     |  |  |  |  |

| 2  | TrC,TfC | Clock Input Rise and Fall Times | 3.5V                                                                          |      | 15   | ns    | 2     |  |  |  |  |

|    |         |                                 | 5.5V                                                                          |      | 15   | ns    | 2     |  |  |  |  |

| 3  | TwC     | Input Clock Width               | 3.5V                                                                          | 50   |      | ns    | 2     |  |  |  |  |

|    |         |                                 | 5.5V                                                                          | 50   |      | ns    | 2     |  |  |  |  |

| 4  | TwIL    | Int. Request Input Low Time     | 3.5V                                                                          | 70   |      | ns    | 2     |  |  |  |  |

|    |         |                                 | 5.5V                                                                          | 70   |      | ns    | 2     |  |  |  |  |

| 5  | TwlH    | Int. Request Input High Time    | 3.5V                                                                          | 5TpC |      |       | 2     |  |  |  |  |

|    |         |                                 | 5.5V                                                                          | 5TpC |      |       | 2     |  |  |  |  |

| 6  | Twsm    | STOP Mode Recovery Width        | 3.5V                                                                          | 12   |      | ns    |       |  |  |  |  |

|    |         | Spec.                           | 5.5V                                                                          | 12   |      | ns    |       |  |  |  |  |

| 7  | Tost    | Oscillator Start-Up Time        | 3.5V                                                                          |      | 5TpC |       |       |  |  |  |  |

|    |         |                                 | 5.5V                                                                          |      | 5TpC |       |       |  |  |  |  |

#### Notes:

1. The V<sub>DD</sub> voltage specification of 3.5V guarantees 3.5V. The V<sub>DD</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V. 2. Timing Reference uses 0.7 V<sub>CC</sub> for a logic 1 and 0.2 V<sub>CC</sub> for a logic 0.

The Z8E001 is based on the ZiLOG Z8Plus Core Architecture. This core is capable of addressing up to 64KBytes of program memory and 4KBytes of RAM. Register RAM is accessed as either 8 or 16 bit registers using a combination of 4, 8, and 12 bit addressing modes. The architecture supports up to 15 vectored interrupts from external and internal sources. The processor decodes 44 CISC instructions using six addressing modes. See the Z8Plus User's Manual for more information.

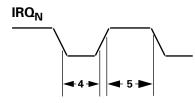

RESET

This section describes the Z8E001 reset conditions, reset timing and register initialization procedures. Baset is gen

timing, and register initialization procedures. Reset is generated by the Reset Pin, Watch-Dog Timer (WDT), and Stop-Mode Recovery (SMR).

A system reset overrides all other operating conditions and puts the Z8E001 into a known state. To initialize the chip's internal logic, the RESET input must be held Low for at least 30 XTAL clock cycles. The control registers and ports

## **RESET PIN OPERATION**

The Z8E001 hardware RESET pin initializes the control and peripheral registers, as shown in Table 4. Specific reset values are shown by 1 or 0, while bits whose states are unchanged or unknown from Power-Up are indicated by the letter U.

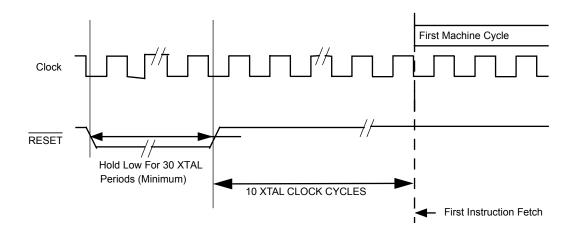

RESET must be held Low until the oscillator stabilizes, for an additional 30 XTAL clock cycles, in order to be sure that the internal reset is complete. The RESET pin has a Schmitt-Trigger input with a trip point. There is no High side protection diode. The user should place an external diode from are <u>reset to</u> their default conditions after a reset from the RESET pin. The control registers and ports are not reset to their default conditions after wakeup from Stop Mode or WDT timeout.

During RESET, the program counter is loaded with 0020H. I/O ports and control registers are configured to their default reset state. Resetting the Z8E001 does not affect the contents of the general-purpose registers.

RESET to  $V_{CC}$ . A pull-up resistor on the RESET pin is approximately 500 K $\Omega$ , typical.

<u>Program</u> execution starts 10 XTAL clock cycles after RE-SET has returned High. The initial instruction fetch is from location 0020H. Figure 9 indicates reset timing.

After a reset, the first routine executed must be one that initializes the TCTLHI control register to the required system configuration, followed by initialization of the remaining control registers.

|                | Bits              |   |   |   |   |   |   |   |   |                                                     |

|----------------|-------------------|---|---|---|---|---|---|---|---|-----------------------------------------------------|

| Register (HEX) | Register Name     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Comments                                            |

| FF             | Stack Pointer     | 0 | 0 | U | U | U | U | U | U | Stack pointer is not affected by RESET              |

| FE             | Reserved          |   |   |   |   |   |   |   |   |                                                     |

| FD             | Register Pointer  | U | U | U | U | 0 | 0 | 0 | 0 | Register pointer is not affected by RESET           |

| FC             | Flags             | U | U | U | U | U | U | * | * | Only WDT & SMR flags are affected by RESET          |

| FB             | Interrupt Mask    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | All interrupts masked by RESET                      |

| FA             | Interrupt Request | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | All interrupt requests cleared by RESET             |

| F9–F0          | Reserved          |   |   |   |   |   |   |   |   |                                                     |

| EF-E0          | Virtual Copy      |   |   |   |   |   |   |   |   | Virtual Copy of the Current Working<br>Register Set |

| DF–D8          | Reserved          |   |   |   |   |   |   |   |   |                                                     |

#### Table 4. Control and Peripheral Registers

| D1 | D0 | Reset Source |  |

|----|----|--------------|--|

| 0  | 0  | RESET Pin    |  |

| 0  | 1  | SMR Recovery |  |

| 1  | 0  | WDT Reset    |  |

| 1  | 1  | Reserved     |  |

## Table 5. Flag Register Bit D1, D0

Figure 10. Example of External Power-On Reset (POR) Circuit

**Note:** The WDT can only be disabled via software if the first instruction out of RESET performs this function. Logic within the Z8E001 detects that it is in the process of executing the first instruction after the part leaves RESET. During the execution of this instruction, the upper five bits of the TCTLHI register can be written. After this first instruction, hardware does not allow the upper five bits of this register to be written.

The TCTLHI bits for control of the WDT are described below:

**WDT Time Select (D6, D5, D4).** Bits 6, 5, and 4 determine the time-out period. Table 6 indicates the range of timeout values that can be obtained. The default values of D6, D5, and D4 are all 1, thus setting the <u>WDT to</u> its maximum timeout period when coming out of RESET.

**WDT During HALT (D7).** This bit determines whether or not the WDT is active during HALT Mode. A 1 indicates active during HALT. A 0 prevents the WDT from resetting the part while halted.Coming out of reset, the WDT is enabled during HALT Mode.

**STOP MODE (D3).** Coming out of RESET, the Z8E001 STOP Mode is disabled. If an application requires use of STOP <u>Mode, bit</u> D3 must be cleared immediately upon leaving RESET. If bit D3 is set, the STOP instruction executes as a NOP. If bit D3 is cleared, the STOP instruction enters Stop Mode. Whenever the Z8E001 wakes up after having been in STOP Mode, the STOP Mode is again disabled.

Bits 2, 1 and 0. These bits are reserved and must be 0.

| D6  | D5 | D4 | Crystal Clocks*<br>to Timeout | Time-Out Using<br>a 10 MHZ Crystal |

|-----|----|----|-------------------------------|------------------------------------|

| 0   | 0  | 0  | Disabled                      | Disabled                           |

| 0   | 0  | 1  | 65,536 TpC                    | 6.55 ms                            |

| 0   | 1  | 0  | 131,072 TpC                   | 13.11 ms                           |

| 0   | 1  | 1  | 262,144 TpC                   | 26.21 ms                           |

| 1   | 0  | 0  | 524,288 TpC                   | 52.43 ms                           |

| 1   | 0  | 1  | 1,048,576 TpC                 | 104.86 ms                          |

| 1   | 1  | 0  | 2,097,152 TpC                 | 209.72 ms                          |

| 1   | 1  | 1  | 4,194,304 TpC                 | 419.43 ms                          |

| Not | e: |    |                               |                                    |

#### Table 6. WDT Time-Out

\*TpC=XTAL clock cycle. The default on reset is D6=D5=D4=1.

## **POWER-DOWN MODES**

In addition to the standard RUN mode, the Z8E001 MCU supports two Power-Down modes to minimize device current consumption. The two modes supported are HALT and STOP.

### HALT MODE OPERATION

The HALT Mode suspends instruction execution and turns off the internal CPU clock. The on-chip oscillator circuit remains active so the internal clock continues to run and is applied to the timers and interrupt logic.

To enter the HALT Mode, the Z8E001 only requires a HALT instruction. It is NOT necessary to execute a NOP instruction immediately before the HALT instruction.

7F HALT ; enter HALT Mode

The HALT Mode can be exited by servicing an interrupt (either externally or internally) generated. Upon completion of the interrupt service routine, the user program continues from the instruction after the HALT instruction.

The HALT Mode can also be exited via a RESET activation or a Watch-Dog Timer (WDT) timeout. In these cases, program execution restarts at the reset restart address 0020H.

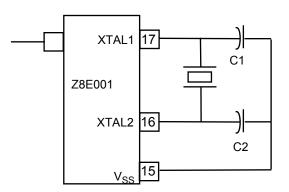

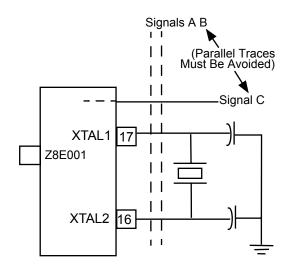

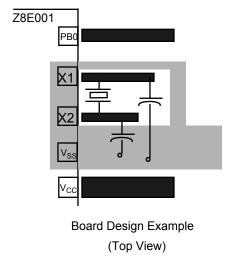

- V<sub>CC</sub> power lines should be separated from the clock oscillator input circuitry.

- Resistivity between XTAL1 or XTAL2 (and the other pins) should be greater than  $10 \text{ M}\Omega$ .

Clock Generator Circuit

## **Crystals and Resonators**

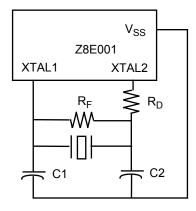

Crystals and ceramic resonators (Figure 16) should have the following characteristics to ensure proper oscillation:

| Crystal Cut         | AT (crystal only)          |

|---------------------|----------------------------|

| Mode                | Parallel, Fundamental Mode |

| Crystal Capacitance | <7pF                       |

| Load Capacitance    | 10pF < CL < 220 pF,        |

|                     | 15 typical                 |

| Resistance          | 100 ohms max               |

|                     |                            |

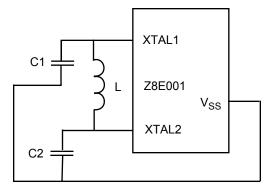

Depending on the operation frequency, the oscillator can require additional capacitors, C1 and C2, as shown in Figure 16 and Figure 17. The capacitance values are dependent on the manufacturer's crystal specifications.

# **OSCILLATOR OPERATION** (Continued)

Figure 16. Crystal/Ceramic Resonator Oscillator

Figure 17. LC Clock

In most cases, the  $R_D$  is 0 Ohms and  $R_F$  is infinite. These specifications are determined and specified by the crys-

tal/ceramic resonator manufacturer. The  $R_D$  can be increased to decrease the amount of drive from the oscillator output to the crystal. It can also be used as an adjustment to avoid clipping of the oscillator signal to reduce noise. The  $R_F$  can be used to improve the start-up of the crystal/ceramic resonator. The Z8E001 oscillator already has an internal shunt resistor in parallel to the crystal/ceramic resonator.

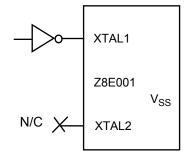

Figure 18. External Clock

Figure 16, Figure 17, and Figure 18 recommend that the load capacitor ground trace connect directly to the  $V_{SS}$  (GND) pin of the Z8E001. This requirement assures that no system noise is injected into the Z8E001 clock. This trace should not be shared with any other components except at the  $V_{SS}$  pin of the Z8E001.

**Note:** A parallel resonant crystal or resonator data sheet specifies a load capacitor value that is a series combination of  $C_1$  and  $C_2$ , including all parasitics (PCB and holder).

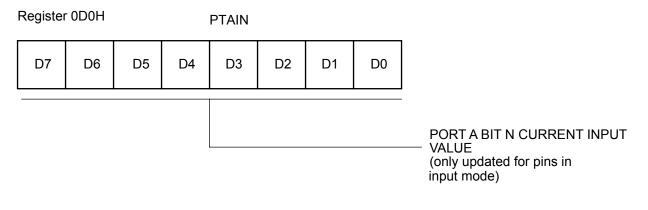

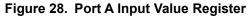

## PORT A REGISTER DIAGRAMS

| Register | 0D1H |    |    | PTAOU | Г  |    |    |                                        |

|----------|------|----|----|-------|----|----|----|----------------------------------------|

| D7       | D6   | D5 | D4 | D3    | D2 | D1 | D0 |                                        |

|          |      |    | I  |       |    | I  |    |                                        |

|          |      |    |    |       |    |    |    | PORT A BIT N CURRENT<br>— OUTPUT VALUE |

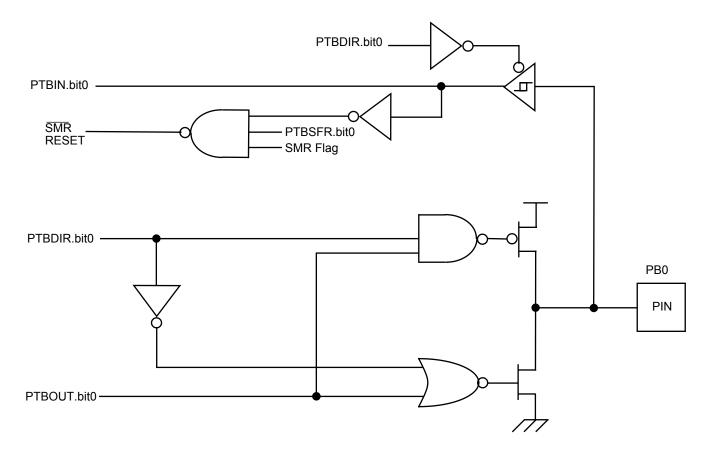

## PORT B-PIN 0 CONFIGURATION

Figure 33. Port B Pin 0 Diagram

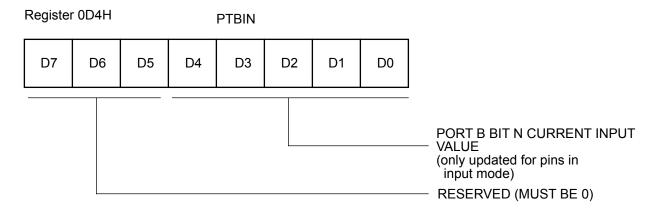

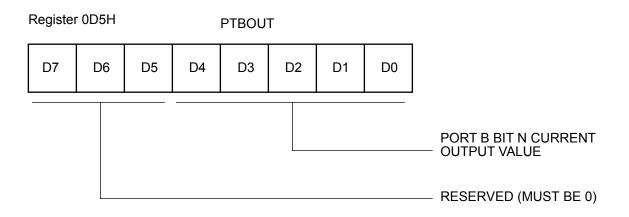

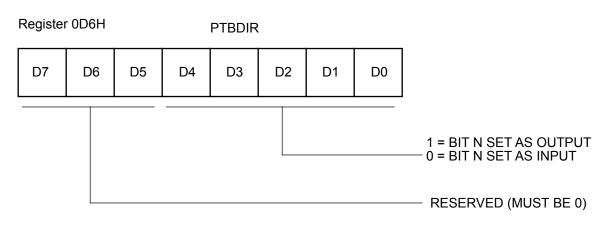

## PORT B CONTROL REGISTERS

## **I/O PORT RESET CONDITIONS**

### **Full Reset**

<u>Port A and Port B output value registers are not affected by RESET.</u>

On RESET, the Port A and Port B directional control registers is cleared to all zeros, which defines all pins in both ports as inputs.

On RESET, the directional control registers redefine all pins as inputs, and the Port A and Port B input value registers

overwrites the previously held data with the current sample of the input pins.

On RESET, the Port A and Port B special function registers is cleared to all zeros, which deactivates all port special functions.

**Note:** The SMR and WDT timeout events are NOT full device resets. The port control registers are not affected by either of these events.

## ANALOG COMPARATOR

The Z8E001 includes one on-chip analog comparator. Pin PB4 has a comparator front end. The comparator reference voltage is on pin PB3.

### **Comparator Description**

The on-chip comparator can process an analog signal on PB4 with reference to the voltage on PB3. The analog function is enabled by programming the Port B Special Function Register bits 3 and 4.

When the analog comparator function is enabled, bit 4 of the input register is defined as holding the synchronized output of the comparator, while bit 3 retains a synchronized sample of the reference input.

If the interrupts for PB4 are enabled when the comparator special function is selected, the output of the comparator generates interrupts.

## **COMPARATOR OPERATION**

The comparator output reflects the relationship between the analog input to the reference input. If the voltage on the analog input is higher than the voltage on the reference input, then the comparator output is at a High state. If the voltage on the analog input is lower than the voltage on the reference input, then the analog output will be at a Low state.

### **Comparator Definitions**

#### **V**ICR

The usable voltage range for the positive input and reference input is called the common mode voltage range ( $V_{ICR}$ ).

**Note:** The comparator is not guaranteed to work if the input is outside of the  $V_{ICR}$  range.

#### VOFFSET

The absolute value of the voltage between the positive input and the reference input required to make the comparator output voltage switch is the input offset voltage ( $V_{OFFSET}$ ).

#### Ι<sub>ΙΟ</sub>

For the CMOS voltage comparator input, the input offset current  $(I_{IO})$  is the leakage current of the CMOS input gate.

### HALT Mode

The analog comparator is functional during HALT Mode. If the interrupts are enabled, an interrupt generated by the comparator will cause a return from HALT Mode.

### **STOP Mode**

The analog comparator is disabled during STOP Mode. The comparator is powered down to prevent it from drawing any current.

#### ZiLOG

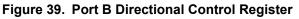

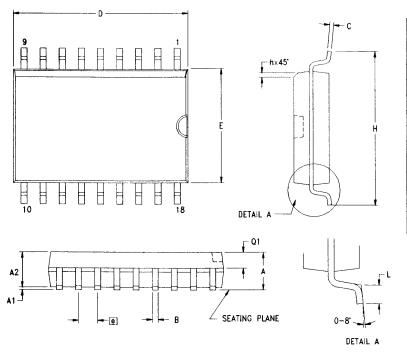

## **PACKAGE INFORMATION**

S

e

- B

| SYMBOL  | MILLI | METER | INCH |      |  |

|---------|-------|-------|------|------|--|

| JIIIDOL | MIN   | MAX   | MIN  | MAX  |  |

| A1      | 0.51  | 0.81  | .020 | .032 |  |

| 5A      | 3.25  | 3.43  | .128 | .135 |  |

| В       | 0.38  | 0.53  | .015 | .021 |  |

| B1      | 1.14  | 1.65  | .045 | .065 |  |

| С       | 0.23  | 0.38  | .009 | .015 |  |

| D       | 22.35 | 23.37 | .880 | .920 |  |

| E       | 7.62  | 8.13  | .300 | .320 |  |

| E1      | 6.22  | 6.48  | .245 | .255 |  |

| e       | 2.54  | TYP   | .100 | TYP  |  |

| eA      | 7.87  | 8.89  | .310 | .350 |  |

| L       | 3.18  | 3.81  | .125 | .150 |  |

| Q1      | 1.52  | 1.65  | .060 | .065 |  |

| S       | 0.89  | 1.65  | .035 | .065 |  |

CONTROLLING DIMENSIONS : INCH

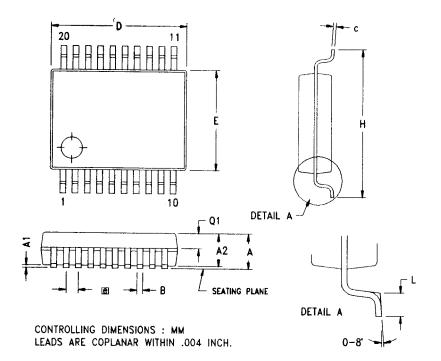

| CYLIDOI | MILLI | METER    | IN    | юн    |

|---------|-------|----------|-------|-------|

| SYMBOL  | MIN   | мах      | MIN   | MAX   |

| A       | 2.40  | 2.65     | 0.094 | 0.104 |

| A1      | 0.10  | 0.30     | 0.004 | 0.012 |

| A2      | 2.24  | 2.44     | 0.088 | 0.096 |

| В       | 0.36  | 0.46     | 0.014 | 0.018 |

| С       | 0.23  | 0.30     | 0.009 | 0.012 |

| D       | 11.40 | 11.75    | 0.449 | 0.463 |

| E       | 7.40  | 7.60     | 0.291 | 0.299 |

| ē       | 1.27  | 1.27 TYP |       | O TYP |

| Н       | 10.00 | 10.65    | 0.394 | 0.419 |

| h       | 0.30  | 0.50     | 0.012 | 0.020 |

| L       | 0.60  | 1.00     | 0.024 | 0.039 |

| Q1      | 0.97  | 1.07     | 0.038 | 0.042 |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

# PACKAGE INFORMATION (Continued)

| SYMBOL    | MILLIMETER |          |      | INCH       |       |       |

|-----------|------------|----------|------|------------|-------|-------|

|           | MIN        | NOM      | MAX  | MIN        | NOM   | MAX   |

| A         | 1.73       | 1.85     | 1.98 | 0.068      | 0.073 | 0.078 |

| <u>A1</u> | 0.05       | 0.13     | 0.21 | 0.002      | 0.005 | 0.008 |

| A2        | 1.68       | 1.73     | 1.83 | 0.066      | 0.068 | 0.072 |

| 8         | 0.25       | 0.30     | 0.38 | 0.010      | 0.012 | 0.015 |

| C         | 0.13       | 0.15     | 0.22 | 0.005      | 0.006 | 0.009 |

| D         | 7.07       | 7.20     | 7.33 | 0.278      | 0.283 | 0.289 |

| E         | 5.20       | 5.30     | 5.38 | 0.205      | 0.209 | 0.212 |

| e         |            | 0.65 TYP |      | 0.0256 TYP |       |       |

| н         | 7.65       | 7.80     | 7.90 | 0.301      | 0.307 | 0.311 |

| L         | 0.56       | 0.75     | 0.94 | 0.022      | 0.030 | 0.037 |

| Q1        | 0.74       | 0.78     | 0.82 | 0.029      | 0.031 | 0.032 |

Figure 45. 20-Pin SSOP Package Diagram

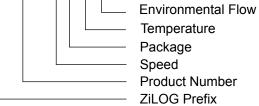

## **ORDERING INFORMATION**

#### **Standard Temperature**

| 18-Pin DIP           | Z8E00110SSC |  |

|----------------------|-------------|--|

| 18-Pin SOIC          | Z8E00110HSC |  |

| 20-Pin SSOP          | Z8E00110PSC |  |

| Extended Temperature |             |  |

| 18-Pin DIP           | Z8E00110PEC |  |

| 18-Pin SOIC          | Z8E00110SEC |  |

| 20-Pin SSOP          | Z8E00110HEC |  |

|                      |             |  |

For fast results, contact your local ZiLOG sales office for assistance in ordering the part(s) required.

| Codes                 |                      |

|-----------------------|----------------------|

| Preferred Package     | P = Plastic DIP      |

| Longer Lead Time      | S = SOIC             |

|                       | H = SSOP             |

| Preferred Temperature | S = 0°C to +70°C     |

|                       | E = -40°C to +105°C  |

| Speed                 | 10 = 10 MHz          |

| Environmental         | C = Plastic Standard |

|                       |                      |

Example:

Z 8E001 10 P S C

is a Z86E001, 10 MHz, DIP, 0° to +70°C, Plastic Standard Flow

Temperature Package

Product Number

ZiLOG Prefix