Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 60MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, SSC, UART/USART, USB                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 28                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3b1128-z1ut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## AT32UC3B

- On-Chip Debug System (JTAG interface)

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

- 64-pin TQFP/QFN (44 GPIO pins), 48-pin TQFP/QFN (28 GPIO pins)

- 5V Input Tolerant I/Os, including 4 high-drive pins

- Single 3.3V Power Supply or Dual 1.8V-3.3V Power Supply

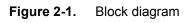

## 2. Overview

## 2.1 Blockdiagram

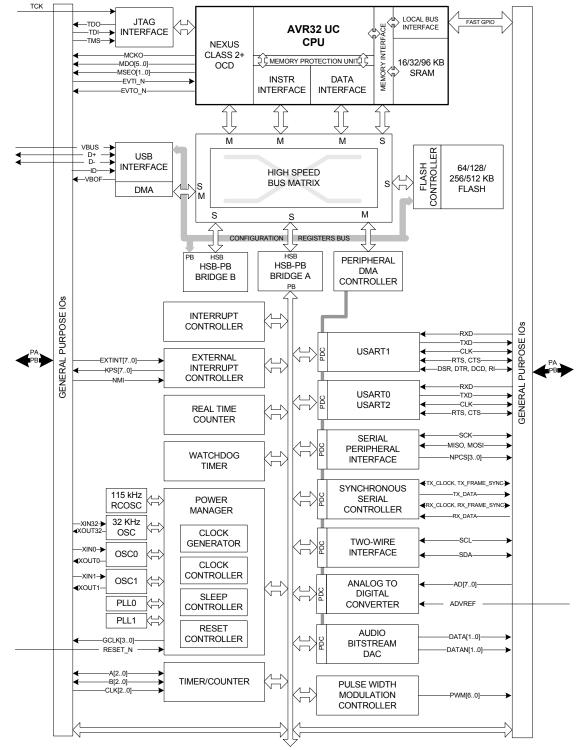

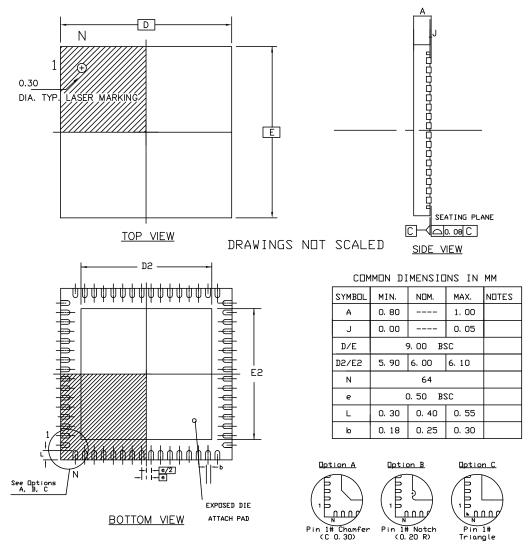

## 4. Package and Pinout

## 4.1 Package

The device pins are multiplexed with peripheral functions as described in the Peripheral Multiplexing on I/O Line section.

# AT32UC3B

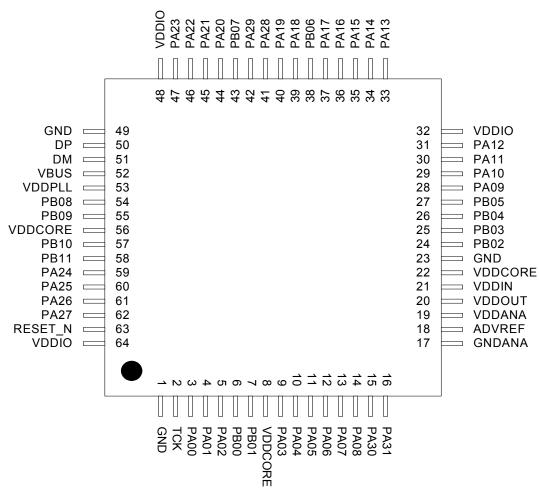

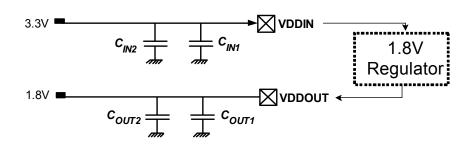

Figure 5-1. Power Supply

#### 5.6.2 Voltage Regulator

#### 5.6.2.1 Single Power Supply

The AT32UC3B embeds a voltage regulator that converts from 3.3V to 1.8V. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDOUT that should be externally connected to the 1.8V domains.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. Two input decoupling capacitors must be placed close to the chip.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel between VDDOUT and GND as close to the chip as possible

Figure 5-2. Supply Decoupling

Refer to Section 9.3 on page 38 for decoupling capacitors values and regulator characteristics.

For decoupling recommendations for VDDIO, VDDANA, VDDCORE and VDDPLL, please refer to the Schematic checklist.

#### 5.6.2.2 Dual Power Supply

In case of dual power supply, VDDIN and VDDOUT should be connected to ground to prevent from leakage current.

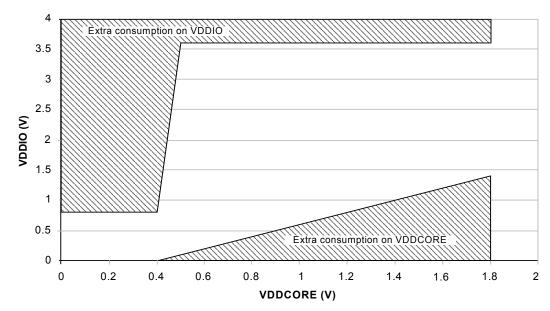

To avoid over consumption during the power up sequence, VDDIO and VDDCORE voltage difference needs to stay in the range given Figure 5-3.

#### Figure 5-3. VDDIO versus VDDCORE during power up sequence

#### 5.6.3 Analog-to-Digital Converter (ADC) reference.

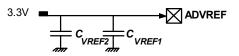

The ADC reference (ADVREF) must be provided from an external source. Two decoupling capacitors must be used to insure proper decoupling.

Figure 5-4. ADVREF Decoupling

Refer to Section 9.4 on page 38 for decoupling capacitors values and electrical characteristics.

In case ADC is not used, the ADVREF pin should be connected to GND to avoid extra consumption.

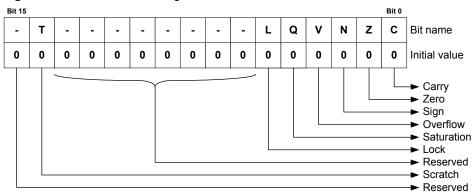

Figure 6-5. The Status Register Low Halfword

#### 6.4.3 Processor States

#### 6.4.3.1 Normal RISC State

The AVR32 processor supports several different execution contexts as shown in Table 6-2 on page 23.

| Priority | Mode                   | Security     | Description                               |

|----------|------------------------|--------------|-------------------------------------------|

| 1        | Non Maskable Interrupt | Privileged   | Non Maskable high priority interrupt mode |

| 2        | Exception              | Privileged   | Execute exceptions                        |

| 3        | Interrupt 3            | Privileged   | General purpose interrupt mode            |

| 4        | Interrupt 2            | Privileged   | General purpose interrupt mode            |

| 5        | Interrupt 1            | Privileged   | General purpose interrupt mode            |

| 6        | Interrupt 0            | Privileged   | General purpose interrupt mode            |

| N/A      | Supervisor             | Privileged   | Runs supervisor calls                     |

| N/A      | Application            | Unprivileged | Normal program execution mode             |

Table 6-2.

Overview of Execution Modes, their Priorities and Privilege Levels.

Mode changes can be made under software control, or can be caused by external interrupts or exception processing. A mode can be interrupted by a higher priority mode, but never by one with lower priority. Nested exceptions can be supported with a minimal software overhead.

When running an operating system on the AVR32, user processes will typically execute in the application mode. The programs executed in this mode are restricted from executing certain instructions. Furthermore, most system registers together with the upper halfword of the status register cannot be accessed. Protected memory areas are also not available. All other operating modes are privileged and are collectively called System Modes. They have full access to all privileged and unprivileged resources. After a reset, the processor will be in supervisor mode.

#### 6.4.3.2 Debug State

The AVR32 can be set in a debug state, which allows implementation of software monitor routines that can read out and alter system information for use during application development. This implies that all system and application registers, including the status registers and program counters, are accessible in debug state. The privileged instructions are also available.

The user must also make sure that the system stack is large enough so that any event is able to push the required registers to stack. If the system stack is full, and an event occurs, the system will enter an UNDEFINED state.

## 6.5.2 Exceptions and Interrupt Requests

When an event other than *scall* or debug request is received by the core, the following actions are performed atomically:

- 1. The pending event will not be accepted if it is masked. The I3M, I2M, I1M, I0M, EM, and GM bits in the Status Register are used to mask different events. Not all events can be masked. A few critical events (NMI, Unrecoverable Exception, TLB Multiple Hit, and Bus Error) can not be masked. When an event is accepted, hardware automatically sets the mask bits corresponding to all sources with equal or lower priority. This inhibits acceptance of other events of the same or lower priority, except for the critical events listed above. Software may choose to clear some or all of these bits after saving the necessary state if other priority schemes are desired. It is the event source's responsability to ensure that their events are left pending until accepted by the CPU.

- 2. When a request is accepted, the Status Register and Program Counter of the current context is stored to the system stack. If the event is an INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also automatically stored to stack. Storing the Status Register ensures that the core is returned to the previous execution mode when the current event handling is completed. When exceptions occur, both the EM and GM bits are set, and the application may manually enable nested exceptions if desired by clearing the appropriate bit. Each exception handler has a dedicated handler address, and this address uniquely identifies the exception source.

- 3. The Mode bits are set to reflect the priority of the accepted event, and the correct register file bank is selected. The address of the event handler, as shown in Table 6-4, is loaded into the Program Counter.

The execution of the event handler routine then continues from the effective address calculated.

The *rete* instruction signals the end of the event. When encountered, the Return Status Register and Return Address Register are popped from the system stack and restored to the Status Register and Program Counter. If the *rete* instruction returns from INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also popped from the system stack. The restored Status Register contains information allowing the core to resume operation in the previous execution mode. This concludes the event handling.

#### 6.5.3 Supervisor Calls

The AVR32 instruction set provides a supervisor mode call instruction. The *scall* instruction is designed so that privileged routines can be called from any context. This facilitates sharing of code between different execution modes. The *scall* mechanism is designed so that a minimal execution cycle overhead is experienced when performing supervisor routine calls from time-critical event handlers.

The *scall* instruction behaves differently depending on which mode it is called from. The behaviour is detailed in the instruction set reference. In order to allow the *scall* routine to return to the correct context, a return from supervisor call instruction, *rets*, is implemented. In the AVR32UC CPU, *scall* and *rets* uses the system stack to store the return address and the status register.

#### 6.5.4 Debug Requests

The AVR32 architecture defines a dedicated Debug mode. When a debug request is received by the core, Debug mode is entered. Entry into Debug mode can be masked by the DM bit in the

## 6.6 Module Configuration

All AT32UC3B parts do not implement the same CPU and Architecture Revision.

| Part Name    | Architecture Revision |

|--------------|-----------------------|

| AT32UC3Bx512 | 2                     |

| AT32UC3Bx256 | 1                     |

| AT32UC3Bx128 | 1                     |

| AT32UC3Bx64  | 1                     |

Table 6-5.

CPU and Architecture Revision

## 7. Memories

## 7.1 Embedded Memories

## Internal High-Speed Flash

- 512KBytes (AT32UC3B0512, AT32UC3B1512)

- 256 KBytes (AT32UC3B0256, AT32UC3B1256)

- 128 KBytes (AT32UC3B0128, AT32UC3B1128)

- 64 KBytes (AT32UC3B064, AT32UC3B164)

- 0 Wait State Access at up to 30 MHz in Worst Case Conditions

- 1 Wait State Access at up to 60 MHz in Worst Case Conditions

- - Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- 100 000 Write Cycles, 15-year Data Retention Capability

- - 4 ms Page Programming Time, 8 ms Chip Erase Time

- Sector Lock Capabilities, Bootloader Protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed

- 96KBytes ((AT32UC3B0512, AT32UC3B1512)

- 32KBytes (AT32UC3B0256, AT32UC3B0128, AT32UC3B1256 and AT32UC3B1128)

- 16KBytes (AT32UC3B064 and AT32UC3B164)

## 7.2 Physical Memory Map

The system bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even in boot. Note that AVR32 UC CPU uses unsegmented translation, as described in the AVR32UC Technical Architecture Manual. The 32-bit physical address space is mapped as follows:

| Device        |                              | Embedded<br>SRAM | Embedded<br>Flash           | USB Data    | HSB-PB<br>Bridge A | HSB-PB<br>Bridge B |

|---------------|------------------------------|------------------|-----------------------------|-------------|--------------------|--------------------|

| Start Address |                              | 0x0000_0000      | 0x8000_0000                 | 0xD000_0000 | 0xFFFF_0000        | 0xFFFE_0000        |

|               | AT32UC3B0512<br>AT32UC3B1512 | 96 Kbytes        | Kbytes 512 Kbytes 64 Kbytes |             | 64 Kbytes          | 64 Kbytes          |

| 0i            | AT32UC3B0256<br>AT32UC3B1256 | 32 Kbytes        | 256 Kbytes                  | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

| Size          | AT32UC3B0128<br>AT32UC3B1128 | 32 Kbytes        | 128 Kbytes                  | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

|               | AT32UC3B064<br>AT32UC3B164   | 16 Kbytes        | 64 Kbytes                   | 64 Kbytes   | 64 Kbytes          | 64 Kbytes          |

## Table 9-7.BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

## 9.4.3 Reset Sequence

## Table 9-8. Electrical Characteristics

| Symbol               | Parameter                                                                                                                                            | Conditions                                                   | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| V <sub>DDRR</sub>    | VDDCORE rise rate to ensure power-<br>on-reset                                                                                                       |                                                              | 2.5  |      |      | V/ms |

| V <sub>DDFR</sub>    | VDDCORE fall rate to ensure power-<br>on-reset                                                                                                       |                                                              | 0.01 |      | 400  | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up<br>to which device is kept under reset by<br>POR on rising VDDCORE                                              | Rising VDDCORE:<br>V <sub>RESTART</sub> -> V <sub>POR+</sub> | 1.4  | 1.55 | 1.65 | V    |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage<br>when POR resets device on falling<br>VDDCORE                                                                   | Falling VDDCORE:<br>1.8V -> V <sub>POR+</sub>                | 1.2  | 1.3  | 1.4  | V    |

| V <sub>RESTART</sub> | On falling VDDCORE, voltage must<br>go down to this value before supply<br>can rise again to ensure reset signal<br>is released at V <sub>POR+</sub> | Falling VDDCORE:<br>1.8V -> V <sub>RESTART</sub>             | -0.1 |      | 0.5  | v    |

| T <sub>POR</sub>     | Minimum time with VDDCORE < V <sub>POR-</sub>                                                                                                        | Falling VDDCORE:<br>1.8V -> 1.1V                             |      | 15   |      | μs   |

| T <sub>RST</sub>     | Time for reset signal to be propagated to system                                                                                                     |                                                              |      | 200  | 400  | μs   |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time<br>for CPU to fetch its first instruction<br>(RCosc not calibrated)                                               |                                                              | 480  |      | 960  | μs   |

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for<br>CPU to fetch its first instruction<br>(RCosc calibrated)                                                    |                                                              |      | 420  |      | μs   |

## 9.6 System Clock Characteristics

These parameters are given in the following conditions:

- V<sub>DDCORE</sub> = 1.8V

- Ambient Temperature = 25°C

## 9.6.1 CPU/HSB Clock Characteristics

## Table 9-13. Core Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPCPU</sub>      | CPU Clock Period    |            | 16.6 |      |      | ns   |

## 9.6.2 PBA Clock Characteristics

## Table 9-14. PBA Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPPBA</sub>      | PBA Clock Period    |            | 16.6 |      |      | ns   |

## 9.6.3 PBB Clock Characteristics

## Table 9-15. PBB Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPPBB</sub>      | PBB Clock Period    |            | 16.6 |      |      | ns   |

## 9.7 Oscillator Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40^{\circ}C$  to 85°C and worst case of power supply, unless otherwise specified.

## 9.7.1 Slow Clock RC Oscillator

## Table 9-16. RC Oscillator Frequency

| Symbol          | Parameter               | Conditions                             | Min. | Тур.  | Max. | Unit |

|-----------------|-------------------------|----------------------------------------|------|-------|------|------|

|                 |                         | Calibration point: $T_A = 85^{\circ}C$ |      | 115.2 | 116  | KHz  |

| F <sub>RC</sub> | RC Oscillator Frequency | T <sub>A</sub> = 25°C                  |      | 112   |      | KHz  |

|                 |                         | $T_A = -40^{\circ}C$                   | 105  | 108   |      | KHz  |

## 9.7.2 32 KHz Oscillator

Table 9-17. 32 KHz Oscillator Characteristics

| Symbol                    | Parameter                            | Conditions                                                                                                                                                           | Min.                | Тур.   | Max.                | Unit |

|---------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|---------------------|------|

| 1// <del>/</del>          | Oppillator Fraguenov                 | External clock on XIN32                                                                                                                                              |                     |        | 30                  | MHz  |

| 1/(t <sub>CP32KHz</sub> ) | Oscillator Frequency                 | Crystal                                                                                                                                                              |                     | 32 768 |                     | Hz   |

| CL                        | Equivalent Load Capacitance          |                                                                                                                                                                      | 6                   |        | 12.5                | pF   |

| ESR                       | Crystal Equivalent Series Resistance |                                                                                                                                                                      |                     |        | 100                 | KΩ   |

| t <sub>st</sub>           | Startup Time                         | $C_L = 6pF^{(1)}$<br>$C_L = 12.5pF^{(1)}$                                                                                                                            |                     |        | 600<br>1200         | ms   |

| t <sub>CH</sub>           | XIN32 Clock High Half-period         |                                                                                                                                                                      | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>           | XIN32 Clock Low Half-period          |                                                                                                                                                                      | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>           | XIN32 Input Capacitance              |                                                                                                                                                                      |                     |        | 5                   | pF   |

| 1                         | Current Concurrentian                | Active mode                                                                                                                                                          |                     |        | 1.8                 | μA   |

| I <sub>OSC</sub>          | Current Consumption                  | valent Series Resistance $C_L = 6pF^{(1)}$<br>$C_L = 12.5pF^{(1)}$ $0.4 t_{CP}$ High Half-period $0.4 t_{CP}$ Low Half-period $0.4 t_{CP}$ Capacitance $Active mode$ |                     | 0.1    | μA                  |      |

Note: 1.  $C_L$  is the equivalent load capacitance.

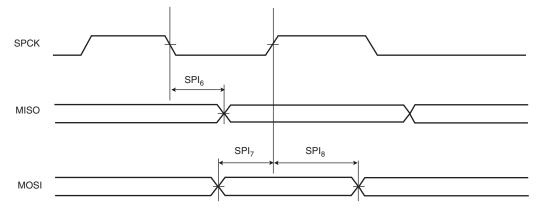

## 9.11 SPI Characteristics

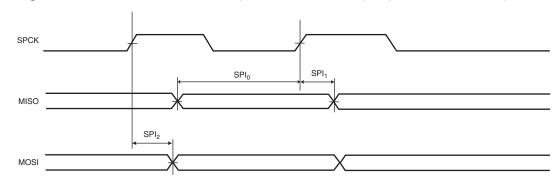

**Figure 9-7.** SPI Master mode with (CPOL = NCPHA = 0) or (CPOL= NCPHA= 1)

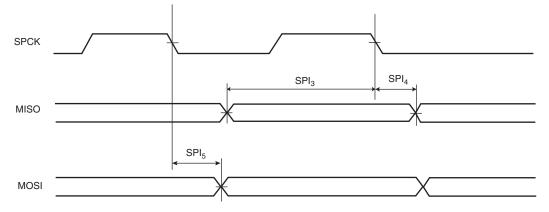

Figure 9-8. SPI Master mode with (CPOL=0 and NCPHA=1) or (CPOL=1 and NCPHA=0)

## **10. Mechanical Characteristics**

## **10.1 Thermal Considerations**

## 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package | Тур  | Unit  |

|----------------------|----------------------------------------|-----------|---------|------|-------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP64  | 49.6 | ·C/W  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP64  | 13.5 | .0/00 |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP48  | 51.1 | CAN   |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP48  | 13.7 | ·C/W  |

## 10.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

**2.**

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1 on page 55.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1 on page 55.

- θ<sub>HEAT SINK</sub> = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 42.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

Compliant JEDEC Standard MD-220 variation VMMD-3

| Table 10-8. | Device and Package Maximum Weight |

|-------------|-----------------------------------|

|             |                                   |

| Weight        |                         | 200 mg               |  |

|---------------|-------------------------|----------------------|--|

| Table 10-9.   | Package Characteristics |                      |  |

| Moisture Sens | itivity Level           | Jedec J-STD-20D-MSL3 |  |

## Table 10-10. Package Reference

| JEDEC Drawing Reference | M0-220 |

|-------------------------|--------|

| JESD97 Classification   | e3     |

## 7. ISO7816 Mode T1: RX impossible after any TX

RX impossible after any TX. **Fix/Workaround** SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

## 8. The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

## Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

## 9. Corruption after receiving too many bits in SPI slave mode

If the USART is in SPI slave mode and receives too much data bits (ex: 9bitsinstead of 8 bits) by the SPI master, an error occurs. After that, the next reception may be corrupted even if the frame is correct and the USART has been disabled, reset by a soft reset and re-enabled.

## Fix/Workaround

None.

10. USART slave synchronous mode external clock must be at least 9 times lower in frequency than CLK\_USART

When the USART is operating in slave synchronous mode with an external clock, the frequency of the signal provided on CLK must be at least 9 times lower than CLK\_USART. **Fix/Workaround**

When the USART is operating in slave synchronous mode with an external clock, provide a signal on CLK that has a frequency at least 9 times lower than CLK\_USART.

## 11. HMATRIX

## 12. In the PRAS and PRBS registers, the MxPR fields are only two bits

In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits. The unused bits are undefined when reading the registers.

## Fix/Workaround

Mask undefined bits when reading PRAS and PRBS.

## - FLASHC

# 1. Reading from on-chip flash may fail after a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands).

After a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), the following flash read access may return corrupted data. This erratum does not affect write operations to regular flash memory.

#### Fix/Workaround

The flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from internal RAM. After the write operation, perform a dummy flash page write operation (FLASHC WP). Content and location of this page is not important

- SSC

## 1. SSC does not trigger RF when data is low

The SSC cannot transmit or receive data when CKS = CKDIV and CKO = none, in TCMR or RCMR respectively.

## Fix/Workaround

Set CKO to a value that is not "none" and bypass the output of the TK/RK pin with the GPIO.

#### - USB

## 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

## Fix/Workaround

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

2. USBFSM and UHADDR1/2/3 registers are not available

Do not use USBFSM register. **Fix/Workaround**

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

- Cycle counter

- CPU Cycle Counter does not reset the COUNT system register on COMPARE match. The device revision B does not reset the COUNT system register on COMPARE match. In this revision, the COUNT register is clocked by the CPU clock, so when the CPU clock stops, so does incrementing of COUNT. Fix/Workaround

None.

```

- ADC

```

## ADC possible miss on DRDY when disabling a channel The ADC does not work properly when more than one channel is enabled. Fix/Workaround

Do not use the ADC with more than one channel enabled at a time.

## ADC OVRE flag sometimes not reset on Status Register read The OVRE flag does not clear properly if read simultaneously to an end of conversion. Fix/Workaround None.

# Sleep Mode activation needs additional A to D conversion If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion. Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

## 13. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

- 13.1 Rev. L- 01/2012

- 1. Updated Mechanical Characteristics section.

## 13.2 Rev. K- 02/2011

- Updated USB section.

Updated Configuration Summary section.

Updated Electrical Characteristics section.

- 4. Updated Errata section.

## 13.3 Rev. J– 12/2010

- 1. Updated USB section.

- 2. Updated USART section.

- 3. Updated TWI section.

- 4. Updated PWM section.

- 5. Updated Electrical Characteristics section.

## 13.4 Rev. I – 06/2010

- 1. Updated SPI section.

- 2 Updated Electrical Characteristics section.

## 13.5 Rev. H - 10/2009

- 1. Update datasheet architecture.

- 2 Add AT32UC3B0512 and AT32UC3B1512 devices description.

## **Table of Contents**

| 1 | Descr                                                                                                     | iption                                                                                                                                                                                                                                                                                | 3                                                                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Overv                                                                                                     | iew                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                         |

|   | 2.1                                                                                                       | Blockdiagram                                                                                                                                                                                                                                                                          | 4                                                                                                                                                         |

| 3 | Config                                                                                                    | guration Summary                                                                                                                                                                                                                                                                      | 5                                                                                                                                                         |

| 4 | Packa                                                                                                     | ge and Pinout                                                                                                                                                                                                                                                                         | 6                                                                                                                                                         |

|   | 4.1                                                                                                       | Package                                                                                                                                                                                                                                                                               | 6                                                                                                                                                         |

|   | 4.2                                                                                                       | Peripheral Multiplexing on I/O lines                                                                                                                                                                                                                                                  | 7                                                                                                                                                         |

|   | 4.3                                                                                                       | High Drive Current GPIO                                                                                                                                                                                                                                                               | 10                                                                                                                                                        |

| 5 | Signal                                                                                                    | Is Description                                                                                                                                                                                                                                                                        | 10                                                                                                                                                        |

|   | 5.1                                                                                                       | JTAG pins                                                                                                                                                                                                                                                                             | 13                                                                                                                                                        |

|   | 5.2                                                                                                       | RESET_N pin                                                                                                                                                                                                                                                                           | 14                                                                                                                                                        |

|   | 5.3                                                                                                       | TWI pins                                                                                                                                                                                                                                                                              | 14                                                                                                                                                        |

|   | 5.4                                                                                                       | GPIO pins                                                                                                                                                                                                                                                                             | 14                                                                                                                                                        |

|   | 5.5                                                                                                       | High drive pins                                                                                                                                                                                                                                                                       | 14                                                                                                                                                        |

|   | 5.6                                                                                                       | Power Considerations                                                                                                                                                                                                                                                                  | 14                                                                                                                                                        |

| 6 | Proce                                                                                                     | ssor and Architecture                                                                                                                                                                                                                                                                 | 17                                                                                                                                                        |

|   | 6.1                                                                                                       | Features                                                                                                                                                                                                                                                                              | 17                                                                                                                                                        |

|   | 0.1                                                                                                       | reatures                                                                                                                                                                                                                                                                              |                                                                                                                                                           |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    |                                                                                                                                                           |

|   | -                                                                                                         |                                                                                                                                                                                                                                                                                       | 17                                                                                                                                                        |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18                                                                                                                                                  |

|   | 6.2<br>6.3                                                                                                | AVR32 Architecture<br>The AVR32UC CPU                                                                                                                                                                                                                                                 | 17<br>18<br>22                                                                                                                                            |

|   | 6.2<br>6.3<br>6.4                                                                                         | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model                                                                                                                                                                                                                            | 17<br>18<br>22<br>26                                                                                                                                      |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts                                                                                                                                                                                               | 17<br>18<br>22<br>26<br>30                                                                                                                                |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b>                                                                                                                   |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b>                                                            | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b><br><b>31</b>                                                                                                      |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1                                                     | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31                                                                                                             |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2                                              | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31                                                                                                 |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>32<br>33                                                                               |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31                                                                          |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b>               | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>rries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping                           | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>32<br>33<br>34                                                 |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b><br>8.1<br>8.2 | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>ries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping         Starting of clocks | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33<br>34<br>34 |

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof AVR<sup>®</sup>, Qtouch<sup>®</sup>, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.