Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 60MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, SSC, UART/USART, USB                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 28                                                                          |

| Program Memory Size        | 256KB (256K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 6x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3b1256-z1ut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Configuration Summary

The table below lists all AT32UC3B memory and package configurations:

| Feature                          | AT32UC3B0512                                                                                                                               | AT32UC3B0256/128/64 | AT32UC3B1512 | AT32UC3B1256/128/64 |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|---------------------|

| Flash                            | 512 KB                                                                                                                                     | 256/128/64 KB       | 512 KB       | 256/128/64 KB       |

| SRAM                             | 96KB                                                                                                                                       | 32/32/16KB          | 96KB         | 32/16/16KB          |

| GPIO                             |                                                                                                                                            | 44                  |              | 28                  |

| External Interrupts              |                                                                                                                                            | 8                   |              | 6                   |

| TWI                              |                                                                                                                                            | 1                   |              |                     |

| USART                            |                                                                                                                                            | 3                   |              |                     |

| Peripheral DMA Channels          |                                                                                                                                            | 7                   |              |                     |

| SPI                              |                                                                                                                                            | 1                   |              |                     |

| Full Speed USB                   | Mini-Ho                                                                                                                                    | st + Device         | D            | evice               |

| SSC                              |                                                                                                                                            | 1                   |              | 0                   |

| Audio Bitstream DAC              | 1                                                                                                                                          | 0                   | 1            | 0                   |

| Timer/Counter Channels           |                                                                                                                                            | 3                   |              |                     |

| PWM Channels                     |                                                                                                                                            | 7                   |              |                     |

| Watchdog Timer                   |                                                                                                                                            | 1                   |              |                     |

| Real-Time Clock Timer            |                                                                                                                                            | 1                   |              |                     |

| Power Manager                    |                                                                                                                                            | 1                   |              |                     |

| Oscillators                      | PLL 80-240 MHz (PLL0/PLL1)<br>Crystal Oscillators 0.4-20 MHz (OSC0)<br>Crystal Oscillator 32 KHz (OSC32K)<br>RC Oscillator 115 kHz (RCSYS) |                     |              |                     |

|                                  | Crystal Oscillators 0.4-20 MHz (OSC1)                                                                                                      |                     |              |                     |

| 10-bit ADC<br>number of channels | 8                                                                                                                                          |                     |              | 6                   |

| JTAG                             |                                                                                                                                            | 1                   |              |                     |

| Max Frequency                    |                                                                                                                                            | 60 M                | Hz           |                     |

| Package                          | TQFP6                                                                                                                                      | 64, QFN64           | TQFP         | 48, QFN48           |

Table 3-1.Configuration Summary

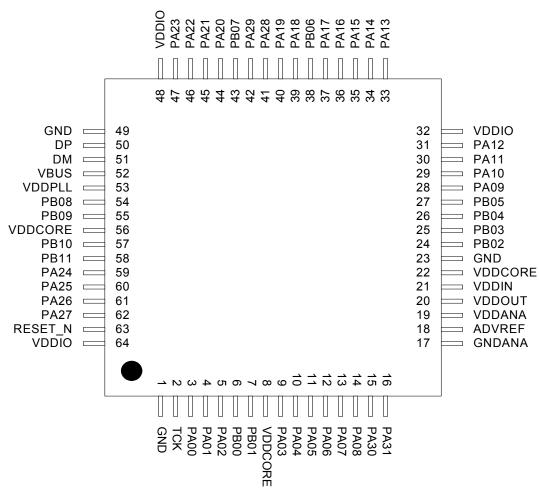

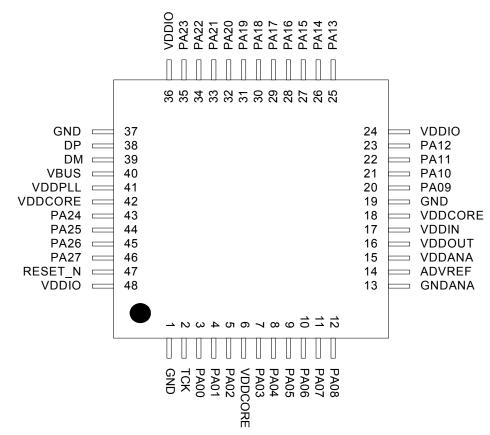

# 4. Package and Pinout

# 4.1 Package

The device pins are multiplexed with peripheral functions as described in the Peripheral Multiplexing on I/O Line section.

Figure 4-2. TQFP48 / QFN48 Pinout

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

# 4.2 Peripheral Multiplexing on I/O lines

### 4.2.1 Multiplexed signals

Each GPIO line can be assigned to one of 4 peripheral functions; A, B, C or D (D is only available for UC3Bx512 parts). The following table define how the I/O lines on the peripherals A, B,C or D are multiplexed by the GPIO.

| 48-pin | 64-pin | PIN  | GPIO Pin | Function A      | Function B   | Function C      | Function D<br>(only for UC3Bx512) |

|--------|--------|------|----------|-----------------|--------------|-----------------|-----------------------------------|

| 3      | 3      | PA00 | GPIO 0   |                 |              |                 |                                   |

| 4      | 4      | PA01 | GPIO 1   |                 |              |                 |                                   |

| 5      | 5      | PA02 | GPIO 2   |                 |              |                 |                                   |

| 7      | 9      | PA03 | GPIO 3   | ADC - AD[0]     | PM - GCLK[0] | USBB - USB_ID   | ABDAC - DATA[0]                   |

| 8      | 10     | PA04 | GPIO 4   | ADC - AD[1]     | PM - GCLK[1] | USBB - USB_VBOF | ABDAC - DATAN[0]                  |

| 9      | 11     | PA05 | GPIO 5   | EIC - EXTINT[0] | ADC - AD[2]  | USART1 - DCD    | ABDAC - DATA[1]                   |

Table 4-1.

GPIO Controller Function Multiplexing

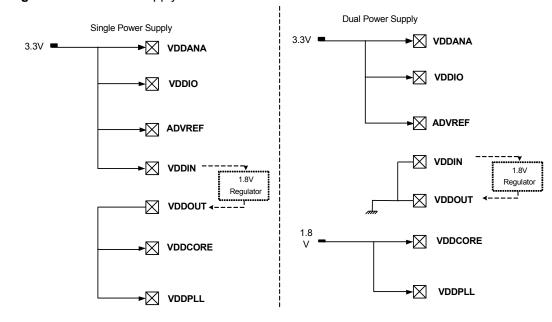

# AT32UC3B

Figure 5-1. Power Supply

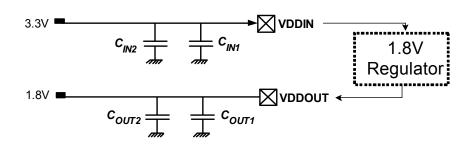

### 5.6.2 Voltage Regulator

### 5.6.2.1 Single Power Supply

The AT32UC3B embeds a voltage regulator that converts from 3.3V to 1.8V. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDOUT that should be externally connected to the 1.8V domains.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. Two input decoupling capacitors must be placed close to the chip.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel between VDDOUT and GND as close to the chip as possible

Figure 5-2. Supply Decoupling

# 6. Processor and Architecture

Rev: 1.0.0.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the *AVR32 Architecture Manual* and the *AVR32UC Technical Reference Manual*.

# 6.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- · 3-stage pipeline allows one instruction per clock cycle for most instructions

- Byte, halfword, word and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

# 6.2 AVR32 Architecture

AVR32 is a high-performance 32-bit RISC microprocessor architecture, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

The user must also make sure that the system stack is large enough so that any event is able to push the required registers to stack. If the system stack is full, and an event occurs, the system will enter an UNDEFINED state.

### 6.5.2 Exceptions and Interrupt Requests

When an event other than *scall* or debug request is received by the core, the following actions are performed atomically:

- 1. The pending event will not be accepted if it is masked. The I3M, I2M, I1M, I0M, EM, and GM bits in the Status Register are used to mask different events. Not all events can be masked. A few critical events (NMI, Unrecoverable Exception, TLB Multiple Hit, and Bus Error) can not be masked. When an event is accepted, hardware automatically sets the mask bits corresponding to all sources with equal or lower priority. This inhibits acceptance of other events of the same or lower priority, except for the critical events listed above. Software may choose to clear some or all of these bits after saving the necessary state if other priority schemes are desired. It is the event source's responsability to ensure that their events are left pending until accepted by the CPU.

- 2. When a request is accepted, the Status Register and Program Counter of the current context is stored to the system stack. If the event is an INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also automatically stored to stack. Storing the Status Register ensures that the core is returned to the previous execution mode when the current event handling is completed. When exceptions occur, both the EM and GM bits are set, and the application may manually enable nested exceptions if desired by clearing the appropriate bit. Each exception handler has a dedicated handler address, and this address uniquely identifies the exception source.

- 3. The Mode bits are set to reflect the priority of the accepted event, and the correct register file bank is selected. The address of the event handler, as shown in Table 6-4, is loaded into the Program Counter.

The execution of the event handler routine then continues from the effective address calculated.

The *rete* instruction signals the end of the event. When encountered, the Return Status Register and Return Address Register are popped from the system stack and restored to the Status Register and Program Counter. If the *rete* instruction returns from INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also popped from the system stack. The restored Status Register contains information allowing the core to resume operation in the previous execution mode. This concludes the event handling.

### 6.5.3 Supervisor Calls

The AVR32 instruction set provides a supervisor mode call instruction. The *scall* instruction is designed so that privileged routines can be called from any context. This facilitates sharing of code between different execution modes. The *scall* mechanism is designed so that a minimal execution cycle overhead is experienced when performing supervisor routine calls from time-critical event handlers.

The *scall* instruction behaves differently depending on which mode it is called from. The behaviour is detailed in the instruction set reference. In order to allow the *scall* routine to return to the correct context, a return from supervisor call instruction, *rets*, is implemented. In the AVR32UC CPU, *scall* and *rets* uses the system stack to store the return address and the status register.

### 6.5.4 Debug Requests

The AVR32 architecture defines a dedicated Debug mode. When a debug request is received by the core, Debug mode is entered. Entry into Debug mode can be masked by the DM bit in the

AT32UC3B

# 9.2 DC Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40^{\circ}C$  to 85°C, unless otherwise specified and are certified for a junction temperature up to  $T_J = 100^{\circ}C$ .

| Symbol                                    | Parameter                                         | Conditions                                                                                                                       |                                                                                                                                  | Min. | Тур. | Max. | Unit |

|-------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>VDDCORE</sub>                      | DC Supply Core                                    |                                                                                                                                  |                                                                                                                                  | 1.65 |      | 1.95 | V    |

| V <sub>VDDPLL</sub>                       | DC Supply PLL                                     |                                                                                                                                  |                                                                                                                                  | 1.65 |      | 1.95 | V    |

| V <sub>VDDIO</sub>                        | DC Supply Peripheral I/Os                         |                                                                                                                                  |                                                                                                                                  | 3.0  |      | 3.6  | V    |

| V <sub>IL</sub>                           | Input Low-level Voltage                           |                                                                                                                                  |                                                                                                                                  | -0.3 |      | +0.8 | V    |

|                                           |                                                   | AT32UC3B064<br>AT32UC3B0128<br>AT32UC3B0256                                                                                      | All I/O pins except TCK,<br>RESET_N, PA03, PA04,<br>PA05, PA06, PA07, PA08,<br>PA11, PA12, PA18, PA19,<br>PA28, PA29, PA30, PA31 | 2.0  |      | 5.5  | V    |

| V <sub>IH</sub> Input High-level Voltage  | AT32UC3B164<br>AT32UC3B1128<br>AT32UC3B1256       | TCK, RESET_N, PA03,<br>PA04, PA05, PA06, PA07,<br>PA08, PA11, PA12, PA18,<br>PA19, PA28, PA29, PA30,<br>PA31                     | 2.0                                                                                                                              |      | 3.6  | V    |      |

|                                           | AT32UC3B0512                                      | All I/O pins except TCK,<br>RESET_N, PA03, PA04,<br>PA05, PA06, PA07, PA08,<br>PA11, PA12, PA18, PA19,<br>PA28, PA29, PA30, PA31 | 2.0                                                                                                                              |      | 5.5  | V    |      |

|                                           | AT32UC3B1512                                      | TCK, RESET_N                                                                                                                     | 2.5                                                                                                                              |      | 3.6  | V    |      |

|                                           |                                                   | PA03, PA04, PA05, PA06,<br>PA07, PA08, PA11, PA12,<br>PA18, PA19, PA28, PA29,<br>PA30, PA31                                      | 2.0                                                                                                                              |      | 3.6  | V    |      |

| V <sub>OL</sub>                           | Output Low-level Voltage                          | I <sub>OL</sub> = -4mA for all I/<br>PA23                                                                                        | O except PA20, PA21, PA22,                                                                                                       |      |      | 0.4  | V    |

|                                           | I <sub>OL</sub> = -8mA for PA20, PA21, PA22, PA23 |                                                                                                                                  |                                                                                                                                  |      | 0.4  | V    |      |

| V <sub>OH</sub> Output High-level Voltage | I <sub>OL</sub> = -4mA for all I/<br>PA23         | O except PA20, PA21, PA22,                                                                                                       | V <sub>VDDIO</sub><br>-0.4                                                                                                       |      |      | v    |      |

|                                           | I <sub>OL</sub> = -8mA for PA20, PA21, PA22, PA23 |                                                                                                                                  | V <sub>VDDIO</sub><br>-0.4                                                                                                       |      |      | v    |      |

| 1                                         |                                                   | All I/O pins except PA20, PA21, PA22, PA23                                                                                       |                                                                                                                                  |      |      | -4   | mA   |

| I <sub>OL</sub>                           | Output Low-level Current                          | PA20, PA21, PA22, PA23                                                                                                           |                                                                                                                                  |      |      | -8   | mA   |

| Output High-level Current                 | All I/O pins except for PA20, PA21, PA22, PA23    |                                                                                                                                  |                                                                                                                                  |      | 4    | mA   |      |

|                                           |                                                   | PA20, PA21, PA22                                                                                                                 | 2, PA23                                                                                                                          |      |      | 8    | mA   |

| I <sub>LEAK</sub>                         | Input Leakage Current                             | Pullup resistors di                                                                                                              | sabled                                                                                                                           |      |      | 1    | μA   |

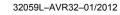

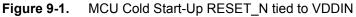

VDDCORE

In dual supply configuration, the power up sequence must be carefully managed to ensure a safe startup of the device in all conditions.

The power up sequence must ensure that the internal logic is safely powered when the internal reset (Power On Reset) is released and that the internal Flash logic is safely powered when the CPU fetch the first instructions.

# **10. Mechanical Characteristics**

# **10.1 Thermal Considerations**

# 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package | Тур  | Unit  |

|----------------------|----------------------------------------|-----------|---------|------|-------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP64  | 49.6 | ·C/W  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP64  | 13.5 | .0/00 |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP48  | 51.1 | C 141 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP48  | 13.7 | ·C/W  |

### 10.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

**2.**

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1 on page 55.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1 on page 55.

- θ<sub>HEAT SINK</sub> = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 42.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

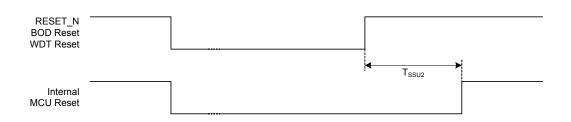

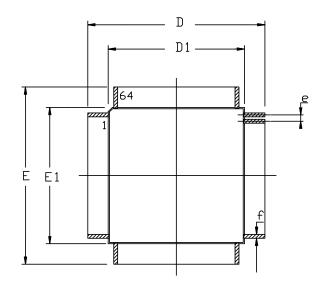

# 10.2 Package Drawings

Figure 10-1. TQFP-64 package drawing

#### COMMON DIMENSIONS IN MM

| SYMBOL | Min   | Max   | NDTES |

|--------|-------|-------|-------|

| A      |       | 1. 20 |       |

| A1     | 0, 95 | 1. 05 |       |

| С      | 0, 09 | 0, 20 |       |

| D      | 12. 0 | O BSC |       |

| D1     | 10. 0 | O BSC |       |

| E      | 12. 0 | O BSC |       |

| E1     | 10. 0 | O BSC |       |

| J      | 0, 05 | 0.15  |       |

| L      | 0.45  | 0, 75 |       |

| e      | 0. 5  | O BSC |       |

| f      | 0, 17 | 0, 27 |       |

<u>0° to 7°</u>

# Table 10-2. Device and Package Maximum Weight

|--|

# Table 10-3. Package Characteristics

Moisture Sensitivity Level

Jedec J-STD-20D-MSL3

# Table 10-4.Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | e3     |

# 10.3 Soldering Profile

Table 10-14 gives the recommended soldering profile from J-STD-20.

| Table 10-14. | Soldering Profile |

|--------------|-------------------|

|--------------|-------------------|

| Profile Feature                            | Green Package          |

|--------------------------------------------|------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/s                  |

| Preheat Temperature 175°C ±25°C            | Min. 150°C, Max. 200°C |

| Temperature Maintained Above 217°C         | 60-150s                |

| Time within 5.C of Actual Peak Temperature | 30s                    |

| Peak Temperature Range                     | 260°C                  |

| Ramp-down Rate                             | 6°C/s                  |

| Time 25 C to Peak Temperature              | Max. 8mn               |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

- PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

2. Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

# Fix/Workaround

Disable and then enable the peripheral after the transfer error.

- 3. TWI

- 4. The TWI RXRDY flag in SR register is not reset when a software reset is performed The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

# 5. TWI in master mode will continue to read data

TWI in master mode will continue to read data on the line even if the shift register and the RHR register are full. This will generate an overrun error. **Fix/Workaround**

To prevent this, read the RHR register as soon as a new RX data is ready.

6. TWI slave behaves improperly if master acknowledges the last transmitted data byte before a STOP condition

In I2C slave transmitter mode, if the master acknowledges the last data byte before a STOP condition (what the master is not supposed to do), the following TWI slave receiver mode frame may contain an inappropriate clock stretch. This clock stretch can only be stopped by resetting the TWI.

### Fix/Workaround

If the TWI is used as a slave transmitter with a master that acknowledges the last data byte before a STOP condition, it is necessary to reset the TWI before entering slave receiver mode.

# 7. TC

# 8. Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

# Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

# - DSP Operations

# 1. Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

Fix/Workaround

Place breakpoints on earlier or later instructions.

# 12.2.3 Rev. F

- PWM

# 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

# Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

# 2. PWN counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

# Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period.

- Consecutive periods are 0x0001, 0x0002, ..., period.

# 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

# Fix/Workaround

Do not update the PWM\_CUPD register with a value equal to 0.

# 4. SPI

# 5. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

# Fix/Workaround

For PDCA transfer: none.

# 6. SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

# 7. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

# Fix/Workaround

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

### 8. SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode. Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

### 9. SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

### 10. Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

### 11. Power Manager

### 12. If the BOD level is higher than VDDCORE, the part is constantly reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

### Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

### 3. When the main clock is RCSYS, TIMER CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER CLOCK5 is equal to PBA Clock and not PBA Clock / 128. Fix/Workaround

None.

13. Clock sources will not be stopped in STATIC sleep mode if the difference between CPU and PBx division factor is too high

If the division factor between the CPU/HSB and PBx frequencies is more than 4 when going to a sleep mode where the system RC oscillator is turned off, then high speed clock sources will not be turned off. This will result in a significantly higher power consumption during the sleep mode.

### Fix/Workaround

Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.

### 14. Increased Power Consumption in VDDIO in sleep modes

If the OSC0 is enabled in crystal mode when entering a sleep mode where the OSC0 is disabled, this will lead to an increased power consumption in VDDIO.

### Fix/Workaround

Disable the OSC0 through the System Control Interface (SCIF) before going to any sleep mode where the OSC0 is disabled, or pull down or up XIN0 and XOUT0 with 1 Mohm resistor.

### 2. Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

Fix/Workaround

Disable and then enable the peripheral after the transfer error.

- 3. TWI

- 4. The TWI RXRDY flag in SR register is not reset when a software reset is performed The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

### 5. TWI in master mode will continue to read data

TWI in master mode will continue to read data on the line even if the shift register and the RHR register are full. This will generate an overrun error. **Fix/Workaround**

To prevent this, read the RHR register as soon as a new RX data is ready.

6. TWI slave behaves improperly if master acknowledges the last transmitted data byte before a STOP condition

In I2C slave transmitter mode, if the master acknowledges the last data byte before a STOP condition (what the master is not supposed to do), the following TWI slave receiver mode frame may contain an inappropriate clock stretch. This clock stretch can only be stopped by resetting the TWI.

# Fix/Workaround

If the TWI is used as a slave transmitter with a master that acknowledges the last data byte before a STOP condition, it is necessary to reset the TWI before entering slave receiver mode.

# 7. GPIO

8. PA29 (TWI SDA) and PA30 (TWI SCL) GPIO VIH (input high voltage) is 3.6V max instead of 5V tolerant

The following GPIOs are not 5V tolerant: PA29 and PA30. **Fix/Workaround** None.

# 9. Some GPIO VIH (input high voltage) are 3.6V max instead of 5V tolerant

Only 11 GPIOs remain 5V tolerant (VIHmax=5V):PB01, PB02, PB03, PB10, PB19, PB20, PB21, PB22, PB23, PB27, PB28. Fix/Workaround None.

# 10. TC

### 11. Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

### Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the

# 7. ISO7816 Mode T1: RX impossible after any TX

RX impossible after any TX. **Fix/Workaround** SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

### 8. The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

# **Fix/Workaround**

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

### 9. Corruption after receiving too many bits in SPI slave mode

If the USART is in SPI slave mode and receives too much data bits (ex: 9bitsinstead of 8 bits) by the SPI master, an error occurs. After that, the next reception may be corrupted even if the frame is correct and the USART has been disabled, reset by a soft reset and re-enabled.

### Fix/Workaround

None.

10. USART slave synchronous mode external clock must be at least 9 times lower in frequency than CLK\_USART

When the USART is operating in slave synchronous mode with an external clock, the frequency of the signal provided on CLK must be at least 9 times lower than CLK\_USART. **Fix/Workaround**

When the USART is operating in slave synchronous mode with an external clock, provide a signal on CLK that has a frequency at least 9 times lower than CLK\_USART.

# 11. HMATRIX

# 12. In the PRAS and PRBS registers, the MxPR fields are only two bits

In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits. The unused bits are undefined when reading the registers.

# Fix/Workaround

Mask undefined bits when reading PRAS and PRBS.

# - FLASHC

# 1. Reading from on-chip flash may fail after a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands).

After a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), the following flash read access may return corrupted data. This erratum does not affect write operations to regular flash memory.

### Fix/Workaround

The flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from internal RAM. After the write operation, perform a dummy flash page write operation (FLASHC WP). Content and location of this page is not important

# 13.6 Rev. G - 06/2009

|       | 1.<br>2          | Open Drain Mode removed from GPIO section.<br>Updated Errata section. |

|-------|------------------|-----------------------------------------------------------------------|

| 13.7  | Rev. F – 04/2008 |                                                                       |

|       | 1.               | Updated Errata section.                                               |

| 13.8  | Rev. E – 12/2007 |                                                                       |

|       | 1.               | Updated Memory Protection section.                                    |

| 13.9  | Rev. D – 11/2007 |                                                                       |

|       | 1.               | Updated Processor Architecture section.                               |

|       | 2.               | Updated Electrical Characteristics section.                           |

| 13.10 | Rev. C – 10/2007 |                                                                       |

|       | 1.               | Updated Features sections.                                            |

|       | 2.               | Updated block diagram with local bus figure                           |

|       | 3.               | Add schematic for HMatrix master/slave connection.                    |

|       | 4.               | Updated Features sections with local bus.                             |

|       | 5.               | Added SPI feature to USART section.                                   |

|       | 6.               | Updated USBB section.                                                 |

|       | 7.               | Updated ADC trigger selection in ADC section.                         |

|       | 8.               | Updated JTAG and Boundary Scan section with programming procedure.    |

|       | 9.               | Add description for silicon revision D                                |

| 13.11 | Rev. B – 07/2007 |                                                                       |

- 1. Updated registered trademarks

- 2. Updated address page.

# **Table of Contents**

| 1 | Descr                                                                                                     | iption                                                                                                                                                                                                                                                                                | 3                                                                                                                                                               |

|---|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Overview                                                                                                  |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |

|   | 2.1                                                                                                       | Blockdiagram                                                                                                                                                                                                                                                                          | 4                                                                                                                                                               |

| 3 | Config                                                                                                    | guration Summary                                                                                                                                                                                                                                                                      | 5                                                                                                                                                               |

| 4 | Package and Pinout                                                                                        |                                                                                                                                                                                                                                                                                       | 6                                                                                                                                                               |

|   | 4.1                                                                                                       | Package                                                                                                                                                                                                                                                                               | 6                                                                                                                                                               |

|   | 4.2                                                                                                       | Peripheral Multiplexing on I/O lines                                                                                                                                                                                                                                                  | 7                                                                                                                                                               |

|   | 4.3                                                                                                       | High Drive Current GPIO                                                                                                                                                                                                                                                               | 10                                                                                                                                                              |

| 5 | Signal                                                                                                    | Is Description                                                                                                                                                                                                                                                                        | 10                                                                                                                                                              |

|   | 5.1                                                                                                       | JTAG pins                                                                                                                                                                                                                                                                             | 13                                                                                                                                                              |

|   | 5.2                                                                                                       | RESET_N pin                                                                                                                                                                                                                                                                           | 14                                                                                                                                                              |

|   | 5.3                                                                                                       | TWI pins                                                                                                                                                                                                                                                                              | 14                                                                                                                                                              |

|   | 5.4                                                                                                       | GPIO pins                                                                                                                                                                                                                                                                             | 14                                                                                                                                                              |

|   | 5.5                                                                                                       | High drive pins                                                                                                                                                                                                                                                                       | 14                                                                                                                                                              |

|   | 5.6                                                                                                       | Power Considerations                                                                                                                                                                                                                                                                  | 14                                                                                                                                                              |

| 6 | Proce                                                                                                     | ssor and Architecture                                                                                                                                                                                                                                                                 | 17                                                                                                                                                              |

|   | 6.1                                                                                                       | Features                                                                                                                                                                                                                                                                              | 17                                                                                                                                                              |

|   | 0.1                                                                                                       | reatures                                                                                                                                                                                                                                                                              |                                                                                                                                                                 |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    |                                                                                                                                                                 |

|   | -                                                                                                         |                                                                                                                                                                                                                                                                                       | 17                                                                                                                                                              |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18                                                                                                                                                        |

|   | 6.2<br>6.3                                                                                                | AVR32 Architecture<br>The AVR32UC CPU                                                                                                                                                                                                                                                 | 17<br>18<br>22                                                                                                                                                  |

|   | 6.2<br>6.3<br>6.4                                                                                         | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model                                                                                                                                                                                                                            | 17<br>18<br>22<br>26                                                                                                                                            |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts                                                                                                                                                                                               | 17<br>18<br>22<br>26<br>30                                                                                                                                      |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b>                                                                                                                         |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b>                                                            | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b><br><b>31</b>                                                                                                            |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1                                                     | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31                                                                                                                   |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2                                              | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31                                                                                                       |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>32<br>33                                                                                     |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31                                                                          |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b>               | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>rries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping                           | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>32<br>33<br>34                                                       |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b><br>8.1<br>8.2 | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>ries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping         Starting of clocks | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33<br>34<br>34 |

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof AVR<sup>®</sup>, Qtouch<sup>®</sup>, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.