#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

**IXF**

| 2 014110                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 60MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, SSC, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 28                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                              |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-TQFP                                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3b164-aur |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

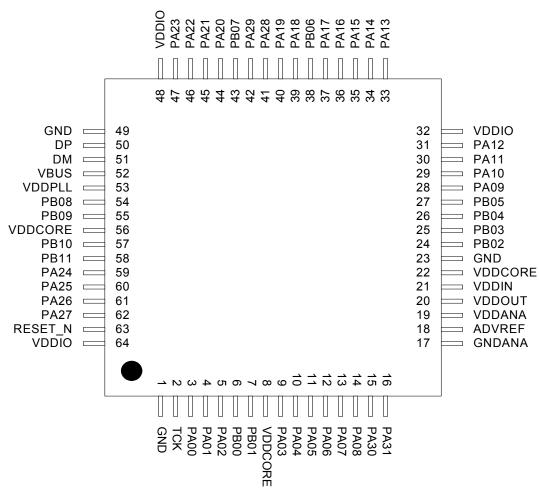

# 4. Package and Pinout

## 4.1 Package

The device pins are multiplexed with peripheral functions as described in the Peripheral Multiplexing on I/O Line section.

## Table 5-1. Signal Description List (Continued)

| Signal Name   | Function                                | Туре            | Active<br>Level | Comments       |

|---------------|-----------------------------------------|-----------------|-----------------|----------------|

|               | Serial Peripheral In                    | terface - SPI0  | ·               | ·              |

| MISO          | Master In Slave Out                     | I/O             |                 |                |

| MOSI          | Master Out Slave In                     | I/O             |                 |                |

| NPCS0 - NPCS3 | SPI Peripheral Chip Select              | I/O             | Low             |                |

| SCK           | Clock                                   | Output          |                 |                |

|               | Synchronous Serial C                    | Controller - SS | С               |                |

| RX_CLOCK      | SSC Receive Clock                       | I/O             |                 |                |

| RX_DATA       | SSC Receive Data                        | Input           |                 |                |

| RX_FRAME_SYNC | SSC Receive Frame Sync                  | I/O             |                 |                |

| TX_CLOCK      | SSC Transmit Clock                      | I/O             |                 |                |

| TX_DATA       | SSC Transmit Data                       | Output          |                 |                |

| TX_FRAME_SYNC | SSC Transmit Frame Sync                 | I/O             |                 |                |

|               | Timer/Counter                           | - TIMER         | •               |                |

| A0            | Channel 0 Line A                        | I/O             |                 |                |

| A1            | Channel 1 Line A                        | I/O             |                 |                |

| A2            | Channel 2 Line A                        | I/O             |                 |                |

| В0            | Channel 0 Line B                        | I/O             |                 |                |

| B1            | Channel 1 Line B                        | I/O             |                 |                |

| B2            | Channel 2 Line B                        | I/O             |                 |                |

| CLK0          | Channel 0 External Clock Input          | Input           |                 |                |

| CLK1          | Channel 1 External Clock Input          | Input           |                 |                |

| CLK2          | Channel 2 External Clock Input          | Input           |                 |                |

|               | Two-wire Interf                         | ace - TWI       |                 |                |

| SCL           | Serial Clock                            | I/O             |                 |                |

| SDA           | Serial Data                             | I/O             |                 |                |

| Uni           | versal Synchronous Asynchronous Receive | r Transmitter - | USART0, U       | ISART1, USART2 |

| CLK           | Clock                                   | I/O             |                 |                |

| СТЅ           | Clear To Send                           | Input           |                 |                |

# 9.6 System Clock Characteristics

These parameters are given in the following conditions:

- V<sub>DDCORE</sub> = 1.8V

- Ambient Temperature = 25°C

#### 9.6.1 CPU/HSB Clock Characteristics

#### Table 9-13. Core Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPCPU</sub>      | CPU Clock Period    |            | 16.6 |      |      | ns   |

#### 9.6.2 PBA Clock Characteristics

#### Table 9-14. PBA Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPPBA</sub>      | PBA Clock Period    |            | 16.6 |      |      | ns   |

#### 9.6.3 PBB Clock Characteristics

#### Table 9-15. PBB Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------|------|------|------|------|

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency |            |      |      | 60   | MHz  |

| t <sub>CPPBB</sub>      | PBB Clock Period    |            | 16.6 |      |      | ns   |

Table 9-23.

Transfer Characteristics in 8-bit Mode

| Parameter                  | Conditions        | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------|------|------|------|------|

| Differential Nen linearity | ADC Clock = 5 MHz |      | 0.3  | 0.5  | LSB  |

| Differential Non-linearity | ADC Clock = 8 MHz |      | 0.5  | 1.0  | LSB  |

| Offset Error               | ADC Clock = 5 MHz | -0.5 |      | 0.5  | LSB  |

| Gain Error                 | ADC Clock = 5 MHz | -0.5 |      | 0.5  | LSB  |

Table 9-24.

Transfer Characteristics in 10-bit Mode

| Parameter                  | Conditions          | Min. | Тур. | Max. | Unit |

|----------------------------|---------------------|------|------|------|------|

| Resolution                 |                     |      | 10   |      | Bit  |

| Absolute Accuracy          | ADC Clock = 5 MHz   |      |      | 3    | LSB  |

| Integral Non-linearity     | ADC Clock = 5 MHz   |      | 1.5  | 2    | LSB  |

| Differential New linearity | ADC Clock = 5 MHz   |      | 1    | 2    | LSB  |

| Differential Non-linearity | ADC Clock = 2.5 MHz |      | 0.6  | 1    | LSB  |

| Offset Error               | ADC Clock = 5 MHz   | -2   |      | 2    | LSB  |

| Gain Error                 | ADC Clock = 5MHz    | -2   |      | 2    | LSB  |

# **10. Mechanical Characteristics**

## **10.1 Thermal Considerations**

#### 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package | Тур  | Unit  |

|----------------------|----------------------------------------|-----------|---------|------|-------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP64  | 49.6 | ·C/W  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP64  | 13.5 | .0/00 |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP48  | 51.1 | CAN   |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP48  | 13.7 | ·C/W  |

#### 10.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

**2.**

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1 on page 55.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1 on page 55.

- θ<sub>HEAT SINK</sub> = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 42.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

# 11. Ordering Information

| Device       | Ordering Code      | Package | Conditioning | Temperature Operating<br>Range |

|--------------|--------------------|---------|--------------|--------------------------------|

| AT32UC3B0512 | AT32UC3B0512-A2UES | TQFP 64 | -            | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0512-A2UR  | TQFP 64 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0512-A2UT  | TQFP 64 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0512-Z2UES | QFN 64  | -            | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0512-Z2UR  | QFN 64  | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0512-Z2UT  | QFN 64  | Tray         | Industrial (-40°C to 85°C)     |

| AT32UC3B0256 | AT32UC3B0256-A2UT  | TQFP 64 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0256-A2UR  | TQFP 64 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0256-Z2UT  | QFN 64  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0256-Z2UR  | QFN 64  | Reel         | Industrial (-40°C to 85°C)     |

| AT32UC3B0128 | AT32UC3B0128-A2UT  | TQFP 64 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0128-A2UR  | TQFP 64 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0128-Z2UT  | QFN 64  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B0128-Z2UR  | QFN 64  | Reel         | Industrial (-40°C to 85°C)     |

| AT32UC3B064  | AT32UC3B064-A2UT   | TQFP 64 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B064-A2UR   | TQFP 64 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B064-Z2UT   | QFN 64  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B064-Z2UR   | QFN 64  | Reel         | Industrial (-40°C to 85°C)     |

| AT32UC3B1512 | AT32UC3B1512-Z1UT  | QFN 48  | -            | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1512-Z1UR  | QFN 48  | -            | Industrial (-40°C to 85°C)     |

| AT32UC3B1256 | AT32UC3B1256-AUT   | TQFP 48 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1256-AUR   | TQFP 48 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1256-Z1UT  | QFN 48  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1256-Z1UR  | QFN 48  | Reel         | Industrial (-40°C to 85°C)     |

| AT32UC3B1128 | AT32UC3B1128-AUT   | TQFP 48 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1128-AUR   | TQFP 48 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1128-Z1UT  | QFN 48  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B1128-Z1UR  | QFN 48  | Reel         | Industrial (-40°C to 85°C)     |

| AT32UC3B164  | AT32UC3B164-AUT    | TQFP 48 | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B164-AUR    | TQFP 48 | Reel         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B164-Z1UT   | QFN 48  | Tray         | Industrial (-40°C to 85°C)     |

|              | AT32UC3B164-Z1UR   | QFN 48  | Reel         | Industrial (-40°C to 85°C)     |

#### 20. USB

#### 21. UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1 ms (Full Speed), or every 125uS (High Speed).

#### Fix/Workaround

For higher polling time, the software must freeze the pipe for the desired period in order to prevent any "extra" token.

#### - ADC

#### 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

#### - PDCA

## 1. Wrong PDCA behavior when using two PDCA channels with the same PID Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

#### 2. Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface. Fix/Workaround

Disable and then enable the peripheral after the transfer error.

#### 3. TWI

4. The TWI RXRDY flag in SR register is not reset when a software reset is performed The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

#### 5. TWI in master mode will continue to read data

TWI in master mode will continue to read data on the line even if the shift register and the RHR register are full. This will generate an overrun error.

#### Fix/Workaround

To prevent this, read the RHR register as soon as a new RX data is ready.

#### 6. TWI slave behaves improperly if master acknowledges the last transmitted data byte before a STOP condition

In I2C slave transmitter mode, if the master acknowledges the last data byte before a STOP condition (what the master is not supposed to do), the following TWI slave receiver mode frame may contain an inappropriate clock stretch. This clock stretch can only be stopped by resetting the TWI.

#### Fix/Workaround

If the TWI is used as a slave transmitter with a master that acknowledges the last data byte before a STOP condition, it is necessary to reset the TWI before entering slave receiver mode.

#### 12.1.2 Rev C

- PWM

#### 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

# Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

#### 2. PWN counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

## Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period.

- Consecutive periods are 0x0001, 0x0002, ..., period.

#### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### Fix/Workaround

Do not update the PWM\_CUPD register with a value equal to 0.

#### 4. SPI

#### 5. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

## Fix/Workaround

For PDCA transfer: none.

# 6. SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

# 7. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### Fix/Workaround

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### - Processor and Architecture

- LDM instruction with PC in the register list and without ++ increments Rp For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. Fix/Workaround None.

- 2. RETE instruction does not clear SREG[L] from interrupts The RETE instruction clears SREG[L] as expected from exceptions. Fix/Workaround

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

3. Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

#### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 4. Flash

#### 5. Reset vector is 80000020h rather than 8000000h

Reset vector is 80000020h rather than 80000000h. **Fix/Workaround** The flash program code must start at the address 80000020h. The flash memory range 80000000h-80000020h must be programmed with 00000000h.

#### - USART

- ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None.

- ISO7816 Mode T1: RX impossible after any TX RX impossible after any TX.

Fix/Workaround SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

- 3. The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA trans-

fer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

#### 4. Corruption after receiving too many bits in SPI slave mode

If the USART is in SPI slave mode and receives too much data bits (ex: 9bitsinstead of 8 bits) by the SPI master, an error occurs. After that, the next reception may be corrupted even if the frame is correct and the USART has been disabled, reset by a soft reset and reenabled.

Fix/Workaround

None.

5. USART slave synchronous mode external clock must be at least 9 times lower in frequency than CLK\_USART

When the USART is operating in slave synchronous mode with an external clock, the frequency of the signal provided on CLK must be at least 9 times lower than CLK\_USART. **Fix/Workaround**

When the USART is operating in slave synchronous mode with an external clock, provide a signal on CLK that has a frequency at least 9 times lower than CLK\_USART.

#### 6. HMATRIX

#### 7. In the PRAS and PRBS registers, the MxPR fields are only two bits

In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits. The unused bits are undefined when reading the registers. **Fix/Workaround**

Mask undefined bits when reading PRAS and PRBS.

#### - DSP Operations

#### 1. Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### Fix/Workaround

Place breakpoints on earlier or later instructions.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### 8. SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

#### Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

#### 9. SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

#### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### 10. Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

#### 11. Power Manager

#### 12. If the BOD level is higher than VDDCORE, the part is constantly reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

#### 1. When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128.

#### Fix/Workaround

None.

13. Clock sources will not be stopped in STATIC sleep mode if the difference between CPU and PBx division factor is too high

If the division factor between the CPU/HSB and PBx frequencies is more than 4 when going to a sleep mode where the system RC oscillator is turned off, then high speed clock sources will not be turned off. This will result in a significantly higher power consumption during the sleep mode.

#### Fix/Workaround

Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.

even if the frame is correct and the USART has been disabled, reset by a soft reset and reenabled.

**Fix/Workaround** None.

9. USART slave synchronous mode external clock must be at least 9 times lower in frequency than CLK\_USART

When the USART is operating in slave synchronous mode with an external clock, the frequency of the signal provided on CLK must be at least 9 times lower than CLK\_USART. **Fix/Workaround**

When the USART is operating in slave synchronous mode with an external clock, provide a signal on CLK that has a frequency at least 9 times lower than CLK\_USART.

#### **10. HMATRIX**

#### 11. In the PRAS and PRBS registers, the MxPR fields are only two bits

In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits. The unused bits are undefined when reading the registers. **Fix/Workaround**

Mask undefined bits when reading PRAS and PRBS.

#### - FLASHC

1. Reading from on-chip flash may fail after a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands).

After a flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), the following flash read access may return corrupted data. This erratum does not affect write operations to regular flash memory.

#### Fix/Workaround

The flash fuse write operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from internal RAM. After the write operation, perform a dummy flash page write operation (FLASHC WP). Content and location of this page is not important and filling the write buffer with all one (FFh) will leave the current flash content unchanged. It is then safe to read and fetch code from the flash.

#### - DSP Operations

#### 1. Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### **Fix/Workaround**

Place breakpoints on earlier or later instructions.

15. SSC

#### 16. Additional delay on TD output

A delay from 2 to 3 system clock cycles is added to TD output when: TCMR.START = Receive Start, TCMR.STTDLY = more than ZERO, RCMR.START = Start on falling edge / Start on Rising edge / Start on any edge, RFMR.FSOS = None (input).

Fix/Workaround

None.

#### 17. TF output is not correct

TF output is not correct (at least emitted one serial clock cycle later than expected) when: TFMR.FSOS = Driven Low during data transfer/ Driven High during data transfer TCMR.START = Receive start RFMR.FSOS = None (Input) RCMR.START = any on RF (edge/level) **Fix/Workaround** None.

#### 18. Frame Synchro and Frame Synchro Data are delayed by one clock cycle

The frame synchro and the frame synchro data are delayed from 1 SSC\_CLOCK when:

- Clock is CKDIV

- The START is selected on either a frame synchro edge or a level

- Frame synchro data is enabled

- Transmit clock is gated on output (through CKO field)

#### Fix/Workaround

Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.

#### 19. USB

#### 20. UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed).

#### Fix/Workaround

For higher polling time, the software must freeze the pipe for the desired period in order to prevent any "extra" token.

- ADC

#### 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion. **Fix/Workaround**

Activate the sleep mode in the mode register and then perform an AD conversion.

- PDCA

#### 1. Wrong PDCA behavior when using two PDCA channels with the same PID Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

and filling the write buffer with all one (FFh) will leave the current flash content unchanged. It is then safe to read and fetch code from the flash.

- DSP Operations

#### 1. Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

Fix/Workaround

Place breakpoints on earlier or later instructions.

#### 12.2.4 Rev. B

- PWM

#### 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

# Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

#### 2. PWN counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

#### Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period.

- Consecutive periods are 0x0001, 0x0002, ..., period.

#### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### Fix/Workaround

Do not update the PWM\_CUPD register with a value equal to 0.

#### 4. PWM channel status may be wrong if disabled before a period has elapsed

Before a PWM period has elapsed, the read channel status may be wrong. The CHIDx-bit for a PWM channel in the PWM Enable Register will read '1' for one full PWM period even if the channel was disabled before the period elapsed. It will then read '0' as expected. **Fix/Workaround**

Reading the PWM channel status of a disabled channel is only correct after a PWM period has elapsed.

# 5. The following alternate C functions PWM[4] on PA16 and PWM[6] on PA31 are not available on Rev B

The following alternate C functions PWM[4] on PA16 and PWM[6] on PA31 are not available on Rev B.

#### **Fix/Workaround**

Do not use these PWM alternate functions on these pins.

#### 6. SPI

#### 7. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission. **Fix/Workaround**

For PDCA transfer: none.

# 8. SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

# 9. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### Fix/Workaround

1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### 10. SPI CSNAAT bit 2 in register CSR0...CSR3 is not available

SPI CSNAAT bit 2 in register CSR0...CSR3 is not available. Fix/Workaround Do not use this bit.

#### 11. SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode. **Fix/Workaround**

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

#### - Power Manager

1. PLL Lock control does not work

PLL lock Control does not work. Fix/Workaround

In PLL Control register, the bit 7 should be set in order to prevent unexpected behavior.

#### 2. Wrong reset causes when BOD is activated

Setting the BOD enable fuse will cause the Reset Cause Register to list BOD reset as the reset source even though the part was reset by another source. **Fix/Workaround**

Do not set the BOD enable fuse, but activate the BOD as soon as your program starts.

# System Timer mask (Bit 16) of the PM CPUMASK register is not available System Timer mask (Bit 16) of the PM CPUMASK register is not available. Fix/Workaround

Do not use this bit.

- SSC

#### 1. SSC does not trigger RF when data is low

The SSC cannot transmit or receive data when CKS = CKDIV and CKO = none, in TCMR or RCMR respectively.

#### Fix/Workaround

Set CKO to a value that is not "none" and bypass the output of the TK/RK pin with the GPIO.

#### - USB

#### 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

#### Fix/Workaround

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

2. USBFSM and UHADDR1/2/3 registers are not available

Do not use USBFSM register. **Fix/Workaround**

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

- Cycle counter

- CPU Cycle Counter does not reset the COUNT system register on COMPARE match. The device revision B does not reset the COUNT system register on COMPARE match. In this revision, the COUNT register is clocked by the CPU clock, so when the CPU clock stops, so does incrementing of COUNT. Fix/Workaround

None.

```

- ADC

```

#### ADC possible miss on DRDY when disabling a channel The ADC does not work properly when more than one channel is enabled. Fix/Workaround

Do not use the ADC with more than one channel enabled at a time.

#### ADC OVRE flag sometimes not reset on Status Register read The OVRE flag does not clear properly if read simultaneously to an end of conversion. Fix/Workaround None.

# Sleep Mode activation needs additional A to D conversion If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion. Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

# 13.6 Rev. G - 06/2009

|       | 1.<br>2          | Open Drain Mode removed from GPIO section.<br>Updated Errata section. |

|-------|------------------|-----------------------------------------------------------------------|

| 13.7  | Rev. F – 04/2008 |                                                                       |

|       | 1.               | Updated Errata section.                                               |

| 13.8  | Rev. E – 12/2007 |                                                                       |

|       | 1.               | Updated Memory Protection section.                                    |

| 13.9  | Rev. D – 11/2007 |                                                                       |

|       | 1.               | Updated Processor Architecture section.                               |

|       | 2.               | Updated Electrical Characteristics section.                           |

| 13.10 | Rev. C – 10/2007 |                                                                       |

|       | 1.               | Updated Features sections.                                            |

|       | 2.               | Updated block diagram with local bus figure                           |

|       | 3.               | Add schematic for HMatrix master/slave connection.                    |

|       | 4.               | Updated Features sections with local bus.                             |

|       | 5.               | Added SPI feature to USART section.                                   |

|       | 6.               | Updated USBB section.                                                 |

|       | 7.               | Updated ADC trigger selection in ADC section.                         |

|       | 8.               | Updated JTAG and Boundary Scan section with programming procedure.    |

|       | 9.               | Add description for silicon revision D                                |

| 13.11 | Rev. B – 07/2007 |                                                                       |

- 1. Updated registered trademarks

- 2. Updated address page.

#### 13.12 Rev. A - 05/2007

1. Initial revision.

# **Table of Contents**

| 1 | Descr                                                                                                     | iption                                                                                                                                                                                                                                                                                | 3                                                                                                                                                               |

|---|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Overv                                                                                                     | iew                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                               |

|   | 2.1                                                                                                       | Blockdiagram                                                                                                                                                                                                                                                                          | 4                                                                                                                                                               |

| 3 | Config                                                                                                    | guration Summary                                                                                                                                                                                                                                                                      | 5                                                                                                                                                               |

| 4 | Packa                                                                                                     | ge and Pinout                                                                                                                                                                                                                                                                         | 6                                                                                                                                                               |

|   | 4.1                                                                                                       | Package                                                                                                                                                                                                                                                                               | 6                                                                                                                                                               |

|   | 4.2                                                                                                       | Peripheral Multiplexing on I/O lines                                                                                                                                                                                                                                                  | 7                                                                                                                                                               |

|   | 4.3                                                                                                       | High Drive Current GPIO                                                                                                                                                                                                                                                               | 10                                                                                                                                                              |

| 5 | Signal                                                                                                    | Is Description                                                                                                                                                                                                                                                                        | 10                                                                                                                                                              |

|   | 5.1                                                                                                       | JTAG pins                                                                                                                                                                                                                                                                             | 13                                                                                                                                                              |

|   | 5.2                                                                                                       | RESET_N pin                                                                                                                                                                                                                                                                           | 14                                                                                                                                                              |

|   | 5.3                                                                                                       | TWI pins                                                                                                                                                                                                                                                                              | 14                                                                                                                                                              |

|   | 5.4                                                                                                       | GPIO pins                                                                                                                                                                                                                                                                             | 14                                                                                                                                                              |

|   | 5.5                                                                                                       | High drive pins                                                                                                                                                                                                                                                                       | 14                                                                                                                                                              |

|   | 5.6                                                                                                       | Power Considerations                                                                                                                                                                                                                                                                  | 14                                                                                                                                                              |

| 6 | Proce                                                                                                     | ssor and Architecture                                                                                                                                                                                                                                                                 | 17                                                                                                                                                              |

|   | 6.1                                                                                                       | Features                                                                                                                                                                                                                                                                              | 17                                                                                                                                                              |

|   | 0.1                                                                                                       | reatures                                                                                                                                                                                                                                                                              |                                                                                                                                                                 |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    |                                                                                                                                                                 |

|   | -                                                                                                         |                                                                                                                                                                                                                                                                                       | 17                                                                                                                                                              |

|   | 6.2                                                                                                       | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18                                                                                                                                                        |

|   | 6.2<br>6.3                                                                                                | AVR32 Architecture<br>The AVR32UC CPU                                                                                                                                                                                                                                                 | 17<br>18<br>22                                                                                                                                                  |

|   | 6.2<br>6.3<br>6.4                                                                                         | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model                                                                                                                                                                                                                            | 17<br>18<br>22<br>26                                                                                                                                            |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts                                                                                                                                                                                               | 17<br>18<br>22<br>26<br>30                                                                                                                                      |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                           | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b>                                                                                                                         |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b>                                                            | AVR32 Architecture<br>The AVR32UC CPU<br>Programming Model<br>Exceptions and Interrupts<br>Module Configuration                                                                                                                                                                       | 17<br>18<br>22<br>26<br>30<br><b>31</b><br><b>31</b>                                                                                                            |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1                                                     | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31                                                                                                                   |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2                                              | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31                                                                                                       |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>32<br>33                                                                                     |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4                                | AVR32 Architecture                                                                                                                                                                                                                                                                    | 17<br>18<br>22<br>26<br>30<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31                                                                          |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b>               | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>rries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping                           | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>32<br>33<br>34                                                       |

| - | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Memo</b><br>7.1<br>7.2<br>7.3<br>7.4<br><b>Boot S</b><br>8.1<br>8.2 | AVR32 Architecture         The AVR32UC CPU         Programming Model         Exceptions and Interrupts         Module Configuration <i>ries</i> Embedded Memories         Physical Memory Map         Peripheral Address Map         CPU Local Bus Mapping         Starting of clocks | 17<br>18<br>22<br>26<br>30<br><b>31</b><br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33<br>34<br>34 |