#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 60MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, SSC, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 28                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                              |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-TQFP                                                                   |

| Supplier Device Package    | 48-TQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3b164-aut |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

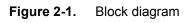

# 2. Overview

# 2.1 Blockdiagram

| Table 4-1. | GPIC | Contro | lier Functio | on Multiplexing        |                |                 |                        |

|------------|------|--------|--------------|------------------------|----------------|-----------------|------------------------|

| 10         | 12   | PA06   | GPIO 6       | EIC - EXTINT[1]        | ADC - AD[3]    | USART1 - DSR    | ABDAC - DATAN[1]       |

| 11         | 13   | PA07   | GPIO 7       | PWM - PWM[0]           | ADC - AD[4]    | USART1 - DTR    | SSC -<br>RX_FRAME_SYNC |

| 12         | 14   | PA08   | GPIO 8       | PWM - PWM[1]           | ADC - AD[5]    | USART1 - RI     | SSC - RX_CLOCK         |

| 20         | 28   | PA09   | GPIO 9       | TWI - SCL              | SPI0 - NPCS[2] | USART1 - CTS    |                        |

| 21         | 29   | PA10   | GPIO 10      | TWI - SDA              | SPI0 - NPCS[3] | USART1 - RTS    |                        |

| 22         | 30   | PA11   | GPIO 11      | USART0 - RTS           | TC - A2        | PWM - PWM[0]    | SSC - RX_DATA          |

| 23         | 31   | PA12   | GPIO 12      | USART0 - CTS           | TC - B2        | PWM - PWM[1]    | USART1 - TXD           |

| 25         | 33   | PA13   | GPIO 13      | EIC - NMI              | PWM - PWM[2]   | USART0 - CLK    | SSC - RX_CLOCK         |

| 26         | 34   | PA14   | GPIO 14      | SPI0 - MOSI            | PWM - PWM[3]   | EIC - EXTINT[2] | PM - GCLK[2]           |

| 27         | 35   | PA15   | GPIO 15      | SPI0 - SCK             | PWM - PWM[4]   | USART2 - CLK    |                        |

| 28         | 36   | PA16   | GPIO 16      | SPI0 - NPCS[0]         | TC - CLK1      | PWM - PWM[4]    |                        |

| 29         | 37   | PA17   | GPIO 17      | SPI0 - NPCS[1]         | TC - CLK2      | SPI0 - SCK      | USART1 - RXD           |

| 30         | 39   | PA18   | GPIO 18      | USART0 - RXD           | PWM - PWM[5]   | SPI0 - MISO     | SSC -<br>RX_FRAME_SYNC |

| 31         | 40   | PA19   | GPIO 19      | USART0 - TXD           | PWM - PWM[6]   | SPI0 - MOSI     | SSC - TX_CLOCK         |

| 32         | 44   | PA20   | GPIO 20      | USART1 - CLK           | TC - CLK0      | USART2 - RXD    | SSC - TX_DATA          |

| 33         | 45   | PA21   | GPIO 21      | PWM - PWM[2]           | TC - A1        | USART2 - TXD    | SSC -<br>TX_FRAME_SYNC |

| 34         | 46   | PA22   | GPIO 22      | PWM - PWM[6]           | TC - B1        | ADC - TRIGGER   | ABDAC - DATA[0]        |

| 35         | 47   | PA23   | GPIO 23      | USART1 - TXD           | SPI0 - NPCS[1] | EIC - EXTINT[3] | PWM - PWM[0]           |

| 43         | 59   | PA24   | GPIO 24      | USART1 - RXD           | SPI0 - NPCS[0] | EIC - EXTINT[4] | PWM - PWM[1]           |

| 44         | 60   | PA25   | GPIO 25      | SPI0 - MISO            | PWM - PWM[3]   | EIC - EXTINT[5] |                        |

| 45         | 61   | PA26   | GPIO 26      | USBB - USB_ID          | USART2 - TXD   | TC - A0         | ABDAC - DATA[1]        |

| 46         | 62   | PA27   | GPIO 27      | USBB - USB_VBOF        | USART2 - RXD   | TC - B0         | ABDAC - DATAN[1]       |

|            | 41   | PA28   | GPIO 28      | USART0 - CLK           | PWM - PWM[4]   | SPI0 - MISO     | ABDAC - DATAN[0]       |

|            | 42   | PA29   | GPIO 29      | TC - CLK0              | TC - CLK1      | SPI0 - MOSI     |                        |

|            | 15   | PA30   | GPIO 30      | ADC - AD[6]            | EIC - SCAN[0]  | PM - GCLK[2]    |                        |

|            | 16   | PA31   | GPIO 31      | ADC - AD[7]            | EIC - SCAN[1]  | PWM - PWM[6]    |                        |

|            | 6    | PB00   | GPIO 32      | TC - A0                | EIC - SCAN[2]  | USART2 - CTS    |                        |

|            | 7    | PB01   | GPIO 33      | TC - B0                | EIC - SCAN[3]  | USART2 - RTS    |                        |

|            | 24   | PB02   | GPIO 34      | EIC - EXTINT[6]        | TC - A1        | USART1 - TXD    |                        |

|            | 25   | PB03   | GPIO 35      | EIC - EXTINT[7]        | TC - B1        | USART1 - RXD    |                        |

|            | 26   | PB04   | GPIO 36      | USART1 - CTS           | SPI0 - NPCS[3] | TC - CLK2       |                        |

|            | 27   | PB05   | GPIO 37      | USART1 - RTS           | SPI0 - NPCS[2] | PWM - PWM[5]    |                        |

|            | 38   | PB06   | GPIO 38      | SSC - RX_CLOCK         | USART1 - DCD   | EIC - SCAN[4]   | ABDAC - DATA[0]        |

|            | 43   | PB07   | GPIO 39      | SSC - RX_DATA          | USART1 - DSR   | EIC - SCAN[5]   | ABDAC - DATAN[0]       |

|            | 54   | PB08   | GPIO 40      | SSC -<br>RX_FRAME_SYNC | USART1 - DTR   | EIC - SCAN[6]   | ABDAC - DATA[1]        |

Table 4-1.

GPIO Controller Function Multiplexing

# Table 5-1. Signal Description List (Continued)

| Signal Name   | Function                                | Туре            | Active<br>Level | Comments       |

|---------------|-----------------------------------------|-----------------|-----------------|----------------|

|               | Serial Peripheral In                    | terface - SPI0  | ·               | ·              |

| MISO          | Master In Slave Out                     | I/O             |                 |                |

| MOSI          | Master Out Slave In                     | I/O             |                 |                |

| NPCS0 - NPCS3 | SPI Peripheral Chip Select              | I/O             | Low             |                |

| SCK           | Clock                                   | Output          |                 |                |

|               | Synchronous Serial C                    | Controller - SS | С               |                |

| RX_CLOCK      | SSC Receive Clock                       | I/O             |                 |                |

| RX_DATA       | SSC Receive Data                        | Input           |                 |                |

| RX_FRAME_SYNC | SSC Receive Frame Sync                  | I/O             |                 |                |

| TX_CLOCK      | SSC Transmit Clock                      | I/O             |                 |                |

| TX_DATA       | SSC Transmit Data                       | Output          |                 |                |

| TX_FRAME_SYNC | SSC Transmit Frame Sync                 | I/O             |                 |                |

|               | Timer/Counter                           | - TIMER         | •               |                |

| A0            | Channel 0 Line A                        | I/O             |                 |                |

| A1            | Channel 1 Line A                        | I/O             |                 |                |

| A2            | Channel 2 Line A                        | I/O             |                 |                |

| В0            | Channel 0 Line B                        | I/O             |                 |                |

| B1            | Channel 1 Line B                        | I/O             |                 |                |

| B2            | Channel 2 Line B                        | I/O             |                 |                |

| CLK0          | Channel 0 External Clock Input          | Input           |                 |                |

| CLK1          | Channel 1 External Clock Input          | Input           |                 |                |

| CLK2          | Channel 2 External Clock Input          | Input           |                 |                |

|               | Two-wire Interf                         | ace - TWI       |                 |                |

| SCL           | Serial Clock                            | I/O             |                 |                |

| SDA           | Serial Data                             | I/O             |                 |                |

| Uni           | versal Synchronous Asynchronous Receive | r Transmitter - | USART0, U       | ISART1, USART2 |

| CLK           | Clock                                   | I/O             |                 |                |

| СТЅ           | Clear To Send                           | Input           |                 |                |

# 5.2 RESET\_N pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As the product integrates a power-on reset cell, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

# 5.3 TWI pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

# 5.4 GPIO pins

All the I/O lines integrate a pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up resistors disabled, except when indicated otherwise in the column "Reset Value" of the GPIO Controller user interface table.

# 5.5 High drive pins

The four pins PA20, PA21, PA22, PA23 have high drive output capabilities.

# 5.6 Power Considerations

#### 5.6.1 Power Supplies

The AT32UC3B has several types of power supply pins:

- VDDIO: Powers I/O lines. Voltage is 3.3V nominal.

- VDDANA: Powers the ADC Voltage is 3.3V nominal.

- VDDIN: Input voltage for the voltage regulator. Voltage is 3.3V nominal.

- VDDCORE: Powers the core, memories, and peripherals. Voltage is 1.8V nominal.

- VDDPLL: Powers the PLL. Voltage is 1.8V nominal.

The ground pins GND are common to VDDCORE, VDDIO and VDDPLL. The ground pin for VDDANA is GNDANA.

Refer to Electrical Characteristics section for power consumption on the various supply pins.

The main requirement for power supplies connection is to respect a star topology for all electrical connection.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 6-1.** Instructions with Unaligned Reference Support

| Instruction | Supported alignment |

|-------------|---------------------|

| ld.d        | Word                |

| st.d        | Word                |

## 6.3.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- · All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- tlbr, tlbs, tlbw

- cache

#### 6.3.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

| Table 6-3.         System Registers (Continued) |         |          |                                        |  |  |

|-------------------------------------------------|---------|----------|----------------------------------------|--|--|

| Reg #                                           | Address | Name     | Function                               |  |  |

| 26                                              | 104     | JAVA_LV3 | Unused in AVR32UC                      |  |  |

| 27                                              | 108     | JAVA_LV4 | Unused in AVR32UC                      |  |  |

| 28                                              | 112     | JAVA_LV5 | Unused in AVR32UC                      |  |  |

| 29                                              | 116     | JAVA_LV6 | Unused in AVR32UC                      |  |  |

| 30                                              | 120     | JAVA_LV7 | Unused in AVR32UC                      |  |  |

| 31                                              | 124     | JTBA     | Unused in AVR32UC                      |  |  |

| 32                                              | 128     | JBCR     | Unused in AVR32UC                      |  |  |

| 33-63                                           | 132-252 | Reserved | Reserved for future use                |  |  |

| 64                                              | 256     | CONFIG0  | Configuration register 0               |  |  |

| 65                                              | 260     | CONFIG1  | Configuration register 1               |  |  |

| 66                                              | 264     | COUNT    | Cycle Counter register                 |  |  |

| 67                                              | 268     | COMPARE  | Compare register                       |  |  |

| 68                                              | 272     | TLBEHI   | Unused in AVR32UC                      |  |  |

| 69                                              | 276     | TLBELO   | Unused in AVR32UC                      |  |  |

| 70                                              | 280     | PTBR     | Unused in AVR32UC                      |  |  |

| 71                                              | 284     | TLBEAR   | Unused in AVR32UC                      |  |  |

| 72                                              | 288     | MMUCR    | Unused in AVR32UC                      |  |  |

| 73                                              | 292     | TLBARLO  | Unused in AVR32UC                      |  |  |

| 74                                              | 296     | TLBARHI  | Unused in AVR32UC                      |  |  |

| 75                                              | 300     | PCCNT    | Unused in AVR32UC                      |  |  |

| 76                                              | 304     | PCNT0    | Unused in AVR32UC                      |  |  |

| 77                                              | 308     | PCNT1    | Unused in AVR32UC                      |  |  |

| 78                                              | 312     | PCCR     | Unused in AVR32UC                      |  |  |

| 79                                              | 316     | BEAR     | Bus Error Address Register             |  |  |

| 80                                              | 320     | MPUAR0   | MPU Address Register region 0          |  |  |

| 81                                              | 324     | MPUAR1   | MPU Address Register region 1          |  |  |

| 82                                              | 328     | MPUAR2   | MPU Address Register region 2          |  |  |

| 83                                              | 332     | MPUAR3   | MPU Address Register region 3          |  |  |

| 84                                              | 336     | MPUAR4   | MPU Address Register region 4          |  |  |

| 85                                              | 340     | MPUAR5   | MPU Address Register region 5          |  |  |

| 86                                              | 344     | MPUAR6   | MPU Address Register region 6          |  |  |

| 87                                              | 348     | MPUAR7   | MPU Address Register region 7          |  |  |

| 88                                              | 352     | MPUPSR0  | MPU Privilege Select Register region 0 |  |  |

| 89                                              | 356     | MPUPSR1  | MPU Privilege Select Register region 1 |  |  |

| 90                                              | 360     | MPUPSR2  | MPU Privilege Select Register region 2 |  |  |

| 91                                              | 364     | MPUPSR3  | MPU Privilege Select Register region 3 |  |  |

Table 6-3.

System Registers (Continued)

# 9.7 Oscillator Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40^{\circ}C$  to 85°C and worst case of power supply, unless otherwise specified.

# 9.7.1 Slow Clock RC Oscillator

# Table 9-16. RC Oscillator Frequency

| Symbol          | Parameter               | Conditions                             | Min. | Тур.  | Max. | Unit |

|-----------------|-------------------------|----------------------------------------|------|-------|------|------|

|                 |                         | Calibration point: $T_A = 85^{\circ}C$ |      | 115.2 | 116  | KHz  |

| F <sub>RC</sub> | RC Oscillator Frequency | T <sub>A</sub> = 25°C                  |      | 112   |      | KHz  |

|                 |                         | $T_A = -40^{\circ}C$                   | 105  | 108   |      | KHz  |

# 9.7.2 32 KHz Oscillator

Table 9-17. 32 KHz Oscillator Characteristics

| Symbol                    | Parameter                            | Conditions                                | Min.                | Тур.   | Max.                | Unit |

|---------------------------|--------------------------------------|-------------------------------------------|---------------------|--------|---------------------|------|

| 1// <del>/</del>          | Oppillator Fraguenov                 | External clock on XIN32                   |                     |        | 30                  | MHz  |

| 1/(t <sub>CP32KHz</sub> ) | Oscillator Frequency                 | Crystal                                   |                     | 32 768 |                     | Hz   |

| CL                        | Equivalent Load Capacitance          |                                           | 6                   |        | 12.5                | pF   |

| ESR                       | Crystal Equivalent Series Resistance |                                           |                     |        | 100                 | KΩ   |

| t <sub>st</sub>           | Startup Time                         | $C_L = 6pF^{(1)}$<br>$C_L = 12.5pF^{(1)}$ |                     |        | 600<br>1200         | ms   |

| t <sub>CH</sub>           | XIN32 Clock High Half-period         |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>           | XIN32 Clock Low Half-period          |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>           | XIN32 Input Capacitance              |                                           |                     |        | 5                   | pF   |

| 1                         | Current Concurrentian                | Active mode                               |                     |        | 1.8                 | μA   |

| I <sub>OSC</sub>          | Current Consumption                  | Standby mode                              |                     |        | 0.1                 | μA   |

Note: 1.  $C_L$  is the equivalent load capacitance.

# 9.8 ADC Characteristics

| Table 9-20.         Channel Conversion Time and ADC Clock |  |

|-----------------------------------------------------------|--|

|-----------------------------------------------------------|--|

| Parameter                       | Conditions             | Min. | Тур. | Max.               | Unit |

|---------------------------------|------------------------|------|------|--------------------|------|

| ADC Clock Frequency             | 10-bit resolution mode |      |      | 5                  | MHz  |

| ADC Clock Frequency             | 8-bit resolution mode  |      |      | 8                  | MHz  |

| Startup Time                    | Return from Idle Mode  |      |      | 20                 | μs   |

| Track and Hold Acquisition Time |                        | 600  |      |                    | ns   |

| Track and Hold Input Resistor   |                        |      | 350  |                    | Ω    |

| Track and Hold Capacitor        |                        |      | 12   |                    | pF   |

| Oranian Time                    | ADC Clock = 5 MHz      |      |      | 2                  | μs   |

| Conversion Time                 | ADC Clock = 8 MHz      |      |      | 1.25               | μs   |

| The she (Date                   | ADC Clock = 5 MHz      |      |      | 384 <sup>(1)</sup> | kSPS |

| Throughput Rate                 | ADC Clock = 8 MHz      |      |      | 533 <sup>(2)</sup> | kSPS |

Notes: 1. Corresponds to 13 clock cycles: 3 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

2. Corresponds to 15 clock cycles: 5 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

| Table 9-21. | External Voltage Reference Input |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Parameter                     | Conditions                           | Min. | Тур. | Max.   | Unit |

|-------------------------------|--------------------------------------|------|------|--------|------|

| ADVREF Input Voltage Range    | (1)                                  | 2.6  |      | VDDANA | V    |

| ADVREF Average Current        | On 13 samples with ADC Clock = 5 MHz |      | 200  | 250    | μA   |

| Current Consumption on VDDANA | On 13 samples with ADC Clock = 5 MHz |      |      | 1      | mA   |

Note: 1. ADVREF should be connected to GND to avoid extra consumption in case ADC is not used.

#### Table 9-22.Analog Inputs

| Parameter             | Conditions | Min. | Тур. | Max.                | Unit |

|-----------------------|------------|------|------|---------------------|------|

| Input Voltage Range   |            | 0    |      | V <sub>ADVREF</sub> | V    |

| Input Leakage Current |            |      |      | 1                   | μA   |

| Input Capacitance     |            |      | 7    |                     | pF   |

|  | Table 9-23. | Transfer Characteristics in 8-bit Mode | e |

|--|-------------|----------------------------------------|---|

|--|-------------|----------------------------------------|---|

| Parameter              | Conditions        | Min. | Тур. | Max. | Unit |

|------------------------|-------------------|------|------|------|------|

| Resolution             |                   |      | 8    |      | Bit  |

|                        | ADC Clock = 5 MHz |      |      | 0.8  | LSB  |

| Absolute Accuracy      | ADC Clock = 8 MHz |      |      | 1.5  | LSB  |

|                        | ADC Clock = 5 MHz |      | 0.35 | 0.5  | LSB  |

| Integral Non-linearity | ADC Clock = 8 MHz |      | 0.5  | 1.0  | LSB  |

# 9.9 USB Transceiver Characteristics

# 9.9.1 Electrical Characteristics

# Table 9-25. Electrical Parameters

| Symbol           | Parameter                                | Conditions                                 | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------|--------------------------------------------|------|------|------|------|

| R <sub>EXT</sub> | Recommended external USB series resistor | In series with each USB pin with $\pm 5\%$ |      | 39   |      | Ω    |

The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

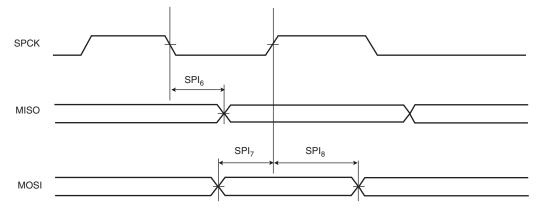

# 9.11 SPI Characteristics

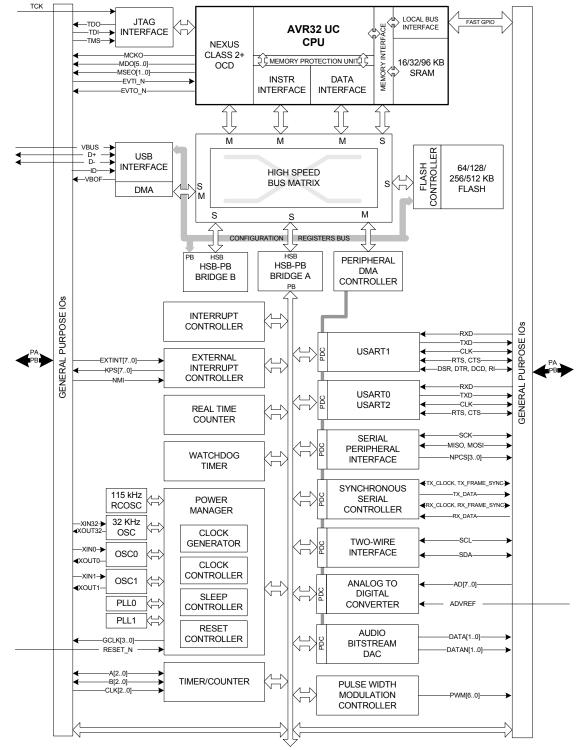

**Figure 9-7.** SPI Master mode with (CPOL = NCPHA = 0) or (CPOL= NCPHA= 1)

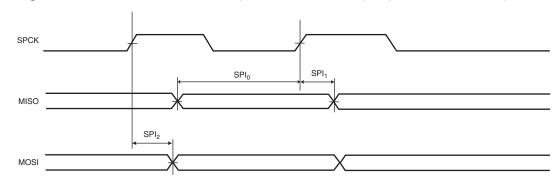

Figure 9-8. SPI Master mode with (CPOL=0 and NCPHA=1) or (CPOL=1 and NCPHA=0)

# 10.3 Soldering Profile

Table 10-14 gives the recommended soldering profile from J-STD-20.

| Table 10-14. | Soldering Profile |

|--------------|-------------------|

|--------------|-------------------|

| Profile Feature                            | Green Package          |

|--------------------------------------------|------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/s                  |

| Preheat Temperature 175°C ±25°C            | Min. 150°C, Max. 200°C |

| Temperature Maintained Above 217°C         | 60-150s                |

| Time within 5.C of Actual Peak Temperature | 30s                    |

| Peak Temperature Range                     | 260°C                  |

| Ramp-down Rate                             | 6°C/s                  |

| Time 25 C to Peak Temperature              | Max. 8mn               |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

7. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

# Fix/Workaround

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### 8. SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

# Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

# 9. SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

# Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### 10. Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### **Fix/Workaround**

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

# 11. Power Manager

# 12. If the BOD level is higher than VDDCORE, the part is constantly reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

# Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

#### 13. When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128. **Fix/Workaround**

None.

14. Clock sources will not be stopped in STATIC sleep mode if the difference between CPU and PBx division factor is too high

If the division factor between the CPU/HSB and PBx frequencies is more than 4 when going to a sleep mode where the system RC oscillator is turned off, then high speed clock sources

# 7. TC

# 8. Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

#### Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### - Processor and Architecture

# 1. LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

#### None.

#### RETE instruction does not clear SREG[L] from interrupts The RETE instruction clears SREG[L] as expected from exceptions. Fix/Workaround

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

3. Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

## Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

- 4. USART

- ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None.

- ISO7816 Mode T1: RX impossible after any TX RX impossible after any TX.

Fix/Workaround SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

- 7. The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when

- PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

2. Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

# Fix/Workaround

Disable and then enable the peripheral after the transfer error.

- 3. TWI

- 4. The TWI RXRDY flag in SR register is not reset when a software reset is performed The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

# 5. TWI in master mode will continue to read data

TWI in master mode will continue to read data on the line even if the shift register and the RHR register are full. This will generate an overrun error. **Fix/Workaround**

To prevent this, read the RHR register as soon as a new RX data is ready.

6. TWI slave behaves improperly if master acknowledges the last transmitted data byte before a STOP condition

In I2C slave transmitter mode, if the master acknowledges the last data byte before a STOP condition (what the master is not supposed to do), the following TWI slave receiver mode frame may contain an inappropriate clock stretch. This clock stretch can only be stopped by resetting the TWI.

#### Fix/Workaround

If the TWI is used as a slave transmitter with a master that acknowledges the last data byte before a STOP condition, it is necessary to reset the TWI before entering slave receiver mode.

# 7. TC

# 8. Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

# Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### - Processor and Architecture

- LDM instruction with PC in the register list and without ++ increments Rp For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. Fix/Workaround None.

- RETE instruction does not clear SREG[L] from interrupts

The RETE instruction clears SREG[L] as expected from exceptions.

Fix/Workaround

When using the STCOND instruction, clear SREC[L] in the stacked value of

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

3. Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

#### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

- 4. USART

- ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None.

- ISO7816 Mode T1: RX impossible after any TX RX impossible after any TX.

Fix/Workaround SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

#### 7. The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

#### 8. Corruption after receiving too many bits in SPI slave mode

If the USART is in SPI slave mode and receives too much data bits (ex: 9bitsinstead of 8 bits) by the SPI master, an error occurs. After that, the next reception may be corrupted

# 12.2.3 Rev. F

- PWM

# 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

# Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

# 2. PWN counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

# Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period.

- Consecutive periods are 0x0001, 0x0002, ..., period.

# 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

# Fix/Workaround

Do not update the PWM\_CUPD register with a value equal to 0.

# 4. SPI

# 5. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

# Fix/Workaround

For PDCA transfer: none.

# 6. SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

# 7. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

# Fix/Workaround

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### 2. Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

Fix/Workaround

Disable and then enable the peripheral after the transfer error.

- 3. TWI

- 4. The TWI RXRDY flag in SR register is not reset when a software reset is performed The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

#### 5. TWI in master mode will continue to read data

TWI in master mode will continue to read data on the line even if the shift register and the RHR register are full. This will generate an overrun error. **Fix/Workaround**

To prevent this, read the RHR register as soon as a new RX data is ready.

6. TWI slave behaves improperly if master acknowledges the last transmitted data byte before a STOP condition

In I2C slave transmitter mode, if the master acknowledges the last data byte before a STOP condition (what the master is not supposed to do), the following TWI slave receiver mode frame may contain an inappropriate clock stretch. This clock stretch can only be stopped by resetting the TWI.

# Fix/Workaround

If the TWI is used as a slave transmitter with a master that acknowledges the last data byte before a STOP condition, it is necessary to reset the TWI before entering slave receiver mode.

# 7. GPIO

8. PA29 (TWI SDA) and PA30 (TWI SCL) GPIO VIH (input high voltage) is 3.6V max instead of 5V tolerant

The following GPIOs are not 5V tolerant: PA29 and PA30. **Fix/Workaround** None.

# 9. Some GPIO VIH (input high voltage) are 3.6V max instead of 5V tolerant

Only 11 GPIOs remain 5V tolerant (VIHmax=5V):PB01, PB02, PB03, PB10, PB19, PB20, PB21, PB22, PB23, PB27, PB28. Fix/Workaround None.

# 10. TC

#### 11. Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

#### Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the

and filling the write buffer with all one (FFh) will leave the current flash content unchanged. It is then safe to read and fetch code from the flash.

- DSP Operations

## 1. Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

Fix/Workaround

Place breakpoints on earlier or later instructions.

# 8. SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

## Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

# 9. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

# Fix/Workaround

1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now begin and RXREADY will now behave as expected.

#### 10. SPI CSNAAT bit 2 in register CSR0...CSR3 is not available

SPI CSNAAT bit 2 in register CSR0...CSR3 is not available. Fix/Workaround Do not use this bit.

# 11. SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode. **Fix/Workaround**

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

#### - Power Manager

1. PLL Lock control does not work

PLL lock Control does not work. Fix/Workaround

In PLL Control register, the bit 7 should be set in order to prevent unexpected behavior.

#### 2. Wrong reset causes when BOD is activated

Setting the BOD enable fuse will cause the Reset Cause Register to list BOD reset as the reset source even though the part was reset by another source. **Fix/Workaround**

Do not set the BOD enable fuse, but activate the BOD as soon as your program starts.

# System Timer mask (Bit 16) of the PM CPUMASK register is not available System Timer mask (Bit 16) of the PM CPUMASK register is not available. Fix/Workaround

Do not use this bit.

- USART

- USART Manchester Encoder Not Working Manchester encoding/decoding is not working. Fix/Workaround Do not use manchester encoding.

- USART RXBREAK problem when no timeguard

In asynchronous mode the RXBREAK flag is not correctly handled when the timeguard is 0 and the break character is located just after the stop bit.

Fix/Workaround

If the NBSTOP is 1, timeguard should be different from 0.

- USART Handshaking: 2 characters sent / CTS rises when TX

If CTS switches from 0 to 1 during the TX of a character, if the Holding register is not empty, the TXHOLDING is also transmitted.

Fix/Workaround

None.

- USART PDC and TIMEGUARD not supported in MANCHESTER Manchester encoding/decoding is not working. Fix/Workaround Do not use manchester encoding.

- USART SPI mode is non functional on this revision USART SPI mode is non functional on this revision.

Fix/Workaround

Do not use the USART SPI mode.

- HMATRIX

- HMatrix fixed priority arbitration does not work Fixed priority arbitration does not work.

Fix/Workaround Use Round-Robin arbitration instead.

- Clock characteristic

- PBA max frequency The Peripheral bus A (PBA) max frequency is 30MHz instead of 60MHz. Fix/Workaround Do not set the PBA maximum frequency higher than 30MHz.

- FLASHC

- The address of Flash General Purpose Fuse Register Low (FGPFRLO) is 0xFFFE140C on revB instead of 0xFFFE1410 The address of Flash General Purpose Fuse Register Low (FGPFRLO) is 0xFFFE140C on revB instead of 0xFFFE1410. Fix/Workaround

None.